Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, IrDA, LINbus, UART/USART                                 |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 4x10b, 3x24b                                                                |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-LQFP                                                                         |

| Supplier Device Package    | 80-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10nmgdfb-50 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 4.3.8   | Peripheral I/O redirection register (PIOR0)                                | 113 |

|--------|---------|----------------------------------------------------------------------------|-----|

|        | 4.3.9   | LCD port function registers 0 to 5 (PFSEG0 to PFSEG5)                      | 114 |

|        | 4.3.10  | LCD input switch control register (ISCLCD)                                 | 117 |

| 4.4    | Port F  | unction Operations                                                         | 118 |

|        | 4.4.1   | Writing to I/O port                                                        | 118 |

|        | 4.4.2   | Reading from I/O port                                                      | 118 |

|        | 4.4.3   | Operations on I/O port                                                     | 118 |

|        | 4.4.4   | Connecting to external device with different potential (1.8 V, 2.5 V, 3 V) | 119 |

|        | 4.4.5   | Handling different potential (1.8 V, 2.5 V, 3 V) by using I/O buffers      | 119 |

| 4.5    | Regis   | ter Settings When Using Alternate Function                                 | 121 |

|        | 4.5.1   | Basic concept when using alternate function                                | 121 |

|        | 4.5.2   | Register settings for alternate function whose output function is not used | 122 |

|        | 4.5.3   | Register setting examples for used port and alternate functions            | 123 |

|        | 4.5.4   | Operation of ports that alternately function as SEGxx pins                 | 132 |

|        | 4.5.5   | Operation of ports that alternately function as $V_{L3}$ , CAPL, CAPH pins | 133 |

| 4.6    | Cautio  | ons When Using Port Function                                               | 135 |

|        | 4.6.1   | Cautions on 1-bit manipulation instruction for port register n (Pn)        | 135 |

|        | 4.6.2   | Notes on specifying the pin settings                                       | 136 |

|        |         |                                                                            |     |

| СНАРТЕ | ER 5 OI | PERATION STATE CONTROL                                                     |     |

| 5.1    | Config  | guration of Operation State Control                                        | 137 |

| 5.2    | Regis   | ters Controlling Operation State Control                                   | 139 |

|        | 5.2.1   | Flash operating mode select register (FLMODE)                              | 139 |

|        | 5.2.2   | Flash operating mode protect register (FLMWRP)                             | 141 |

|        | 5.2.3   | Regulator mode control register (PMMC)                                     |     |

| 5.3    | Initial | Setting of Flash Operation Modes                                           | 142 |

| 5.4    | Trans   | itions between Flash Operation Modes                                       | 143 |

| 5.5    | Detail  | s of Flash Operation Modes                                                 | 144 |

|        | 5.5.1   | Details of HS (high-speed main) mode                                       | 144 |

|        | 5.5.2   | Details of LS (low-speed main) mode                                        | 145 |

|        | 5.5.3   | Details of LP (low-power main) mode                                        | 146 |

|        | 5.5.4   | Details on LV (low-voltage main) mode                                      | 147 |

| СНАРТЕ | ER 6 CI | LOCK GENERATOR                                                             | 148 |

| 6.1    | Funct   | ions of Clock Generator                                                    | 148 |

| 6.2    | Config  | guration of Clock Generator                                                | 151 |

| 6.3    | Regis   | ters Controlling Clock Generator                                           | 153 |

|        | 6.3.1   | Clock operation mode control register (CMC)                                | 153 |

|        | 6.3.2   | System clock control register (CKC)                                        | 155 |

|        | 6.3.3   | Clock operation status control register (CSC)                              | 157 |

|        | 6.3.4   | Sub clock operation mode control register (SCMC)                           | 159 |

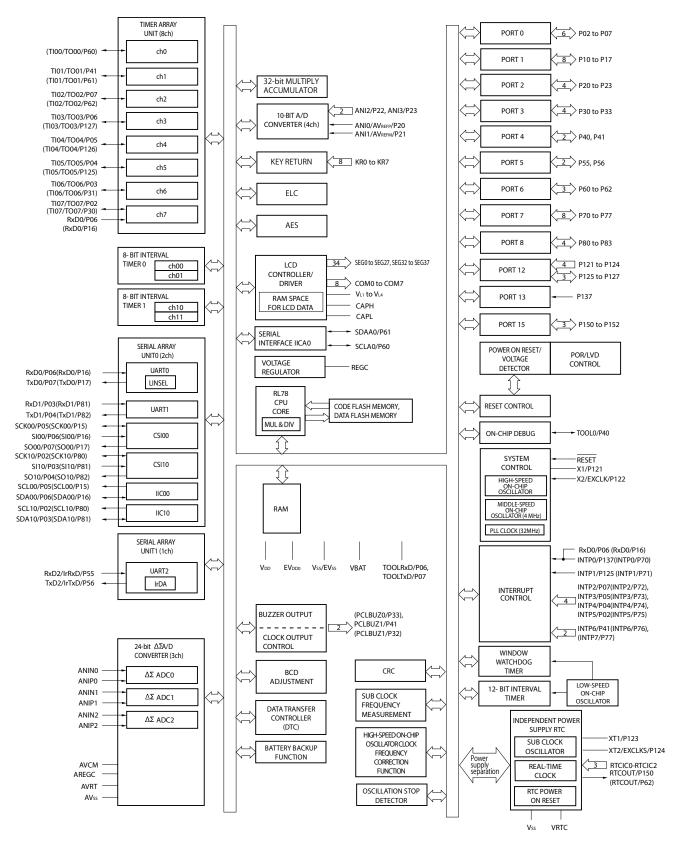

#### 1.5.2 80-pin products

**Remark** Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR0). See **Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR0)**.

# 1.6 Outline of Functions

|   |                      | Item                                                               | 64-                                                                                                                                                                                                                                                                       | -pin                                                                                              |                                                                                                     | 80-pin                                                                                                                                                                                  |                                                                           | 100                     | )-pin                   |  |  |  |

|---|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-------------------------|--|--|--|

|   |                      |                                                                    | R5F10NLEDFB                                                                                                                                                                                                                                                               | R5F10NLGDFB                                                                                       | R5F10NMEDFB                                                                                         | R5F10NMGDFB                                                                                                                                                                             | R5F10NMJDFB                                                               | R5F10NPGDFB             | R5F10NPJDF              |  |  |  |

| ( | Code flash me        | emory (KB)                                                         | 64 KB                                                                                                                                                                                                                                                                     | 128 KB                                                                                            | 64 KB                                                                                               | 128 KB                                                                                                                                                                                  | 256 KB                                                                    | 128 KB                  | 256 KB                  |  |  |  |

| ۱ | Data flash me        | mory (KB)                                                          |                                                                                                                                                                                                                                                                           |                                                                                                   |                                                                                                     | 2 KB                                                                                                                                                                                    |                                                                           |                         |                         |  |  |  |

|   | RAM (KB)             |                                                                    | 6 KB                                                                                                                                                                                                                                                                      | 8 KB <sup>Note 1</sup>                                                                            | 6 KB                                                                                                | 8 KB <sup>Note 1</sup>                                                                                                                                                                  | 16 KB <sup>Note 2</sup>                                                   | 8 KB <sup>Note 1</sup>  | 16 KB <sup>Note 2</sup> |  |  |  |

| , | Address spac         | e                                                                  | 1 MB                                                                                                                                                                                                                                                                      |                                                                                                   |                                                                                                     |                                                                                                                                                                                         |                                                                           |                         |                         |  |  |  |

|   | Main system<br>clock | High-speed system<br>clock                                         | HS (High-spe<br>HS (High-spe<br>HS (High-spe<br>HS (High-spe<br>LS (Low-spe<br>LV (Low-volta                                                                                                                                                                              | eed main) mod<br>eed main) mod<br>eed main) mod<br>eed main) mod<br>ed main) mod<br>age main) mod | e: 1 to 20 MH<br>e: 1 to 16 MH<br>e: 1 to 12 MH<br>e: 1 to 6 MHz<br>e: 1 to 8 MHz<br>le: 1 to 4 MHz | nain system clo<br>z ( $V_{DD} = 2.7$ to<br>z ( $V_{DD} = 2.5$ to<br>z ( $V_{DD} = 2.4$ to<br>( $V_{DD} = 2.1$ to 5<br>( $V_{DD} = 1.9$ to 5<br>( $V_{DD} = 1.7$ to 5<br>= 1.9 to 5.5 V | 5.5 V),<br>5.5 V),<br>5.5 V),<br>5.5 V),<br>5.5 V),<br>5.5 V),<br>5.5 V), | LK)                     |                         |  |  |  |

|   |                      | High -speed on-chip<br>oscillator clock (f⊮)<br>MAX.: 24 MHz       | HS (High-spe<br>HS (High-spe<br>HS (High-spe                                                                                                                                                                                                                              | eed main) mod<br>eed main) mod<br>eed main) mod                                                   | e: 1 to 24 MH<br>e: 1 to 16 MH<br>e: 1 to 12 MH                                                     | z (V <sub>DD</sub> = 2.7 to<br>z (V <sub>DD</sub> = 2.5 to<br>z (V <sub>DD</sub> = 2.4 to                                                                                               | 5.5 V),<br>5.5 V),<br>5.5 V),                                             |                         |                         |  |  |  |

|   |                      | Middle -speed on-<br>chip oscillator clock<br>(fiм)<br>MAX.: 4 MHz | HS (High-speed main) mode: 1 to 6 MHz ( $V_{DD} = 2.1$ to 5.5 V),<br>LS (Low-speed main) mode: 1 to 8 MHz ( $V_{DD} = 1.9$ to 5.5 V),<br>LV (Low-voltage main) mode: 1 to 4 MHz ( $V_{DD} = 1.7$ to 5.5 V),<br>LP (Low-power main) mode: 1 MHz ( $V_{DD} = 1.9$ to 5.5 V) |                                                                                                   |                                                                                                     |                                                                                                                                                                                         |                                                                           |                         |                         |  |  |  |

|   |                      | PLL clock (fpll)                                                   |                                                                                                                                                                                                                                                                           |                                                                                                   | -                                                                                                   |                                                                                                                                                                                         | HS (High-spe<br>(V <sub>DD</sub> = 2.8 to                                 | eed main) moo<br>5.5 V) | le: 32 MHz              |  |  |  |

|   | Subsystem<br>clock   | Subsystem clock<br>oscillator clock<br>(fsx)                       | ,                                                                                                                                                                                                                                                                         | oscillation, ext<br>TYP.): V <sub>DD</sub> = 1                                                    |                                                                                                     | em clock input                                                                                                                                                                          | (EXCLKS)                                                                  |                         |                         |  |  |  |

|   |                      | Low-speed on-chip oscillator clock (fiL)                           | 15 kHz (TYP                                                                                                                                                                                                                                                               | .): Vdd = 1.7 to                                                                                  | 5.5V                                                                                                |                                                                                                                                                                                         |                                                                           |                         |                         |  |  |  |

|   |                      | n-chip oscillator clock<br>rection function                        | Correct the frequency of the high-speed on-chip oscillator clock by the subsystem clock.                                                                                                                                                                                  |                                                                                                   |                                                                                                     |                                                                                                                                                                                         |                                                                           |                         |                         |  |  |  |

| ( | General-purpo        | ose register                                                       | 8 bits × 8 registers × 4 banks                                                                                                                                                                                                                                            |                                                                                                   |                                                                                                     |                                                                                                                                                                                         |                                                                           |                         |                         |  |  |  |

| Ī | Minimum instr        | uction execution time                                              | 0.03125 μs (                                                                                                                                                                                                                                                              | PLL clock: fpll                                                                                   | = 32 MHz sele                                                                                       | ection)                                                                                                                                                                                 |                                                                           |                         |                         |  |  |  |

| l |                      |                                                                    | 0.04167 <i>μ</i> s (l                                                                                                                                                                                                                                                     | High-speed on                                                                                     | -chip oscillator                                                                                    | : fін = 24 MHz                                                                                                                                                                          | operation)                                                                |                         |                         |  |  |  |

| 1 |                      |                                                                    | 30.5 <i>µ</i> s (Sub                                                                                                                                                                                                                                                      | system clock:                                                                                     | fsuв <b>= 32.768 k</b>                                                                              | Hz operation)                                                                                                                                                                           |                                                                           |                         |                         |  |  |  |

|   |                      |                                                                    | 66.6 μs (Low-speed on-chip oscillator: $f_{IL}$ = 15 kHz operation)                                                                                                                                                                                                       |                                                                                                   |                                                                                                     |                                                                                                                                                                                         |                                                                           |                         |                         |  |  |  |

|   | Instruction set      |                                                                    | <ul><li>Adder and</li><li>Multiplication</li><li>Multiplication</li></ul>                                                                                                                                                                                                 | on (16 bits $\times$ 1 on and accum                                                               | ulation (16 bits                                                                                    | (8/16 bits)<br>n (32 bits ÷ 32<br>n × 16 bits + 32<br>n (set, reset, te                                                                                                                 | bits)                                                                     | n operation), e         | etc.                    |  |  |  |

| 1 | I/O port             | Total                                                              | 3                                                                                                                                                                                                                                                                         | 5                                                                                                 |                                                                                                     | 52                                                                                                                                                                                      |                                                                           |                         | 68                      |  |  |  |

|   |                      | CMOS I/O                                                           | 2                                                                                                                                                                                                                                                                         | .7                                                                                                |                                                                                                     | 44                                                                                                                                                                                      |                                                                           |                         | 60                      |  |  |  |

| l |                      | CMOS input                                                         |                                                                                                                                                                                                                                                                           | 5                                                                                                 |                                                                                                     | 5                                                                                                                                                                                       |                                                                           |                         | 5                       |  |  |  |

|   |                      | CMOS output                                                        |                                                                                                                                                                                                                                                                           | -                                                                                                 |                                                                                                     | -                                                                                                                                                                                       |                                                                           |                         | -                       |  |  |  |

|   |                      | N-ch O.D I/O<br>(6 V tolerance)                                    | ;                                                                                                                                                                                                                                                                         | 3                                                                                                 |                                                                                                     | 3                                                                                                                                                                                       |                                                                           |                         | 3                       |  |  |  |

Notes 1. In the case of the 8 KB, this is about 7 KB when the self-programming function is used.

2. In the case of the 16 KB, this is about 15 KB when the self-programming function is used.

## 4.3.3 Pull-up resistor option registers (PUxx)

These registers specify whether the on-chip pull-up resistors are to be used or not. On-chip pull-up resistors can be used in 1-bit units only for the bits set to normal output mode (POMmn = 0) and input mode (PMmn = 1) for the pins to which the use of an on-chip pull-up resistor has been specified in these registers. On-chip pull-up resistors cannot be connected to bits set to output mode and bits used as alternate-function output pins and analog setting (ADPC = 1), regardless of the settings of these registers.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H (PU4 is set to 01H, PU15 is set to 07H).

Caution When a port with the PIMn register is input from different potential device to TTL buffer, pull up to the power supply of the different potential device via an external pull-up resistor by setting PUmn = 0.

| Symbol | 7       | 6       | 5                                                                                           | 4            | 3          | 2            | 1           | 0            | Address | After reset | R/W |  |

|--------|---------|---------|---------------------------------------------------------------------------------------------|--------------|------------|--------------|-------------|--------------|---------|-------------|-----|--|

| PU0    | PU07    | PU06    | PU05                                                                                        | PU04         | PU03       | PU02         | 0           | 0            | F0030H  | 00H         | R/W |  |

|        | -       |         |                                                                                             |              |            |              |             |              |         |             |     |  |

| PU1    | PU17    | PU16    | PU15                                                                                        | PU14         | PU13       | PU12         | PU11        | PU10         | F0031H  | 00H         | R/W |  |

|        |         |         |                                                                                             |              |            | r            |             |              |         |             |     |  |

| PU3    | PU37    | PU36    | PU35                                                                                        | PU34         | PU33       | PU32         | PU31        | PU30         | F0033H  | 00H         | R/W |  |

|        | r       |         |                                                                                             |              |            | 1            |             | 1            |         |             |     |  |

| PU4    | 0       | 0       | 0                                                                                           | 0            | PU43       | PU42         | PU41        | PU40         | F0034H  | 01H         | R/W |  |

|        | <b></b> |         |                                                                                             |              |            |              |             |              |         |             |     |  |

| PU5    | PU57    | PU56    | PU55                                                                                        | PU54         | PU53       | PU52         | PU51        | PU50         | F0035H  | 00H         | R/W |  |

|        | r       | r       | r                                                                                           | r            | r          | r            | r           | 1            |         |             |     |  |

| PU7    | PU77    | PU76    | PU75                                                                                        | PU74         | PU73       | PU72         | PU71        | PU70         | F0037H  | 00H         | R/W |  |

|        | r       | r       | r                                                                                           | r            | r          | r            | r           | 1            |         |             |     |  |

| PU8    | 0       | 0       | PU85                                                                                        | PU84         | PU83       | PU82         | PU81        | PU80         | F0038H  | 00H         | R/W |  |

|        |         |         |                                                                                             |              |            |              |             | 1            |         |             |     |  |

| PU12   | PU127   | PU126   | PU125                                                                                       | 0            | 0          | 0            | 0           | 0            | F003CH  | 00H         | R/W |  |

|        | 1       |         |                                                                                             |              |            |              |             | 1            |         |             |     |  |

| PU15   | 0       | 0       | 0                                                                                           | 0            | 0          | PU152        | PU151       | PU150        | F003FH  | 07H         | R/W |  |

|        | <b></b> |         |                                                                                             |              |            |              |             |              |         |             |     |  |

|        | PUmn    |         | Pmn pin on-chip pull-up resistor selection<br>(m = 0, 1, 3 to 5, 7, 8, 12, 15 ; n = 0 to 7) |              |            |              |             |              |         |             |     |  |

|        | 0       | On-chin | pull-up res                                                                                 | istor not co | `          | , ., 0 10 0, | ., 0, 12, 1 | • , ii = 0 k | /       |             |     |  |

|        | 0       |         |                                                                                             |              | , in colou |              |             |              |         |             |     |  |

#### Figure 4-3. Format of Pull-up Resistor Option Register

Caution Be sure to set bits that are not mounted to their initial values.

On-chip pull-up resistor connected

1

| Pin         | Used             | Function                  | PIOR0×                   | POM×× | PM××   | Pxx    | PFSEG××                             | Alternate Fur          | ction Output            | 64-pin       | 80-pin       | 100-         |

|-------------|------------------|---------------------------|--------------------------|-------|--------|--------|-------------------------------------|------------------------|-------------------------|--------------|--------------|--------------|

| Name        | Function<br>Name | I/O                       |                          |       |        |        | (ISCVL3,<br>ISCCAP) <sup>Note</sup> | SAU Output<br>Function | Other than<br>SAU       |              |              | pin          |

| P30         | P30              | Input                     | -                        | -     | 1      | ×      | 0                                   | -                      | -                       |              |              |              |

|             |                  | Output                    | ×                        | -     | 0      | 0/1    | 0                                   | _                      | (TO07) = 0              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|             | SEG24            | Output                    | ×                        | -     | 0      | 0      | 1                                   | -                      | _                       |              |              |              |

|             | (TI07)           | Input                     | PIOR00 = 1               | -     | 1      | ×      | 0                                   | -                      | -                       | -            | $\checkmark$ | $\checkmark$ |

|             | TI07             | Input                     | PIOR00 = 0               | -     | 1      | ×      | 0                                   | -                      | -                       |              | -            | -            |

|             | (TO07)           | Output                    | PIOR00 = 1               | -     | 0      | 0      | 0                                   | -                      | -                       | -            | $\checkmark$ |              |

|             | TO07             | Output                    | PIOR00 = 0               | -     | 0      | 0      | 0                                   | -                      | -                       |              | -            | -            |

|             | RxD2             | Input                     | ×                        | -     | 1      | ×      | 0                                   | -                      | -                       |              |              |              |

|             | IrRxD            | Input                     | ×<br>PIOR04 = 0          | -     | 1      | ×      | 0                                   | -                      | —                       | $\checkmark$ | -            | -            |

| <b>D</b> 04 | INTP5            | Input                     |                          | -     | 1      | ×      | 0                                   | _                      | -                       |              |              |              |

| P31         | P31              | Input                     | X                        | -     | 0      | 0/1    | 0                                   | -                      | -                       | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|             |                  | Output                    | ^                        | -     |        |        |                                     |                        | (TO06) = 0              |              |              |              |

|             |                  | N-ch open<br>drain output | ×                        | 1     | 0      | 0/1    | 0                                   | TxD2/IrTxD = 1         | _                       | $\checkmark$ | -            | -            |

|             | SEG25            | Output                    | ×                        | -     | 0      | 0      | 1                                   | -                      | _                       | $\checkmark$ | V            | V            |

|             | (TI06)           | Input                     | PIOR00 = 1               | -     | 1      | ×      | 0                                   | -                      | -                       | -            |              | $\checkmark$ |

|             | TI06             | Input                     | PIOR00 = 0 $PIOR00 = 1$  | -     | 1<br>0 | ×<br>0 | 0                                   | —                      | -                       | V            | -            | -            |

|             | (TO06)           | Output                    | PIOR00 = 1<br>PIOR00 = 0 | -     | 0      | 0      | 0                                   | —                      | -                       | _            | V            | V            |

|             | TO06             | Output                    | x                        | - 0/1 | 0      | 1      | 0                                   | -                      | -                       | $\checkmark$ | -            | -            |

|             | TxD2             | Output                    | ×                        | 0/1   | 0      | 1      | 0                                   | -                      | -                       | $\checkmark$ | -            | -            |

| P32         | lrTxD<br>P32     | Output                    |                          |       | 1      | ×      | 0                                   | _                      | _                       |              |              |              |

| P32         | P32              | Input                     | -                        | -     |        | ^      | 0                                   | _                      |                         |              |              |              |

|             |                  | Output                    | ×                        | -     | 0      | 0/1    | 0                                   | -                      | (PCLBUZ1) =<br>0        | -            | $\checkmark$ | $\checkmark$ |

|             | SEG26            | Output                    | ×                        | -     | 0      | 0      | 1                                   | -                      | -                       |              |              |              |

|             | (PCLBUZ1)        | Output                    | PIOR03 = 1               | -     | 0      | 0      | 0                                   | _                      | _                       |              |              |              |

| P33         | P33              | Input                     | -                        | _     | 1      | ×      | 0                                   | _                      | -                       |              |              |              |

|             |                  | Output                    | ×                        | _     | 0      | 0/1    | 0                                   | _                      | (PCLBUZ0) =<br>0        | _            |              | V            |

|             | SEG27            | Output                    | ×                        | _     | 0      | 0      | 1                                   | _                      | _                       |              |              |              |

|             | (PCLBUZ0)        | Output                    | PIOR03 = 1               | _     | 0      | 0      | 0                                   | _                      | _                       |              |              |              |

| P34         | P34              | Input                     | _                        | _     | 1      | ×      | 0                                   | _                      | _                       |              |              |              |

|             |                  | Output                    | _                        | _     | 0      | 0/1    | 0                                   | _                      | -                       | _            | _            | $\checkmark$ |

|             | SEG28            | Output                    | _                        | _     | 0      | 0      | 1                                   | _                      | _                       |              |              |              |

| P35         | P35              | Input                     | _                        | _     | 1      | ×      | 0                                   | _                      | _                       |              |              |              |

|             |                  | Output                    | _                        | _     | 0      | 0/1    | 0                                   | _                      | _                       | _            | _            | $\checkmark$ |

|             | SEG29            | Output                    |                          |       | 0      | 0      | 1                                   | _                      | _                       | _            |              | v            |

| P36         | P36              | Input                     | -                        | -     | 1      | ×      | 0                                   | _                      | _                       |              |              |              |

| 1 00        | 1 00             | Output                    | _                        | -     | 0      | 0/1    | 0                                   | _                      | _                       | _            | _            | $\checkmark$ |

|             | SEG30            | Output                    | -                        | -     | 0      | 0      | 1                                   | _                      | _                       | _            | _            | v            |

| P37         | P37              | Input                     | -                        | -     | 1      | ×      | 0                                   | _                      | _                       |              |              |              |

| F37         | F31              |                           | -                        | -     | 0      | 0/1    | 0                                   |                        |                         |              |              | ,            |

|             | 05004            | Output                    | -                        | -     | 0      | 0      | 1                                   | -                      | -                       | -            | -            | V            |

| <b>D</b> 40 | SEG31            | Output                    | -                        | -     | 1      | ×      |                                     | -                      | -                       |              | <u> </u>     |              |

| P40         | P40              | Input                     | -                        | -     | 0      | 0/1    | -                                   | -                      | -                       | ,            | ,            | ,            |

|             |                  | Output                    | -                        | -     |        |        | -                                   | —                      | -                       | $\checkmark$ | V            | $\checkmark$ |

|             | TOOL0            | I/O                       | _                        | -     | × 1    | ×      | -                                   | -                      | -                       |              |              |              |

| P41         | P41              | Input                     | -                        | -     | 1      | ×      | -                                   | -                      | -                       |              |              |              |

|             |                  | Output                    | ×                        | -     | 0      | 0/1    | _                                   | _                      | TO01 = 0<br>PCLBUZ1 = 0 | -            | V            | V            |

|             | TI01             | Input                     | PIOR00 = 0               | -     | 1      | ×      | -                                   | _                      | -                       | . 1          | . 1          | . 1          |

|             | TO01             | Output                    | PIOR00 = 0               | _     | 0      | 0      | _                                   | -                      | PCLBUZ1 = 0             | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|             | PCLBUZ1          | Output                    | PIOR03 = 0               | _     | 0      | 0      | _                                   | -                      | TO01 = 0                |              | 1            | ı            |

| 1           | INTP6            | Input                     | PIOR04 = 0               | _     | 1      | ×      | _                                   | _                      | _                       | -            | $\checkmark$ | $\checkmark$ |

# Table 4-6. Setting Examples of Registers and Output Latches When Using Alternate Function (5/10)

Note ISCVL3 and ISCCAP are registers that correspond to P125, and P126 and P127, respectively.

| Pin  | Used F                 | unction | CMC Register    | SCMC Register     | P×x | 64-pin       | 80-pin       | 100-pin      |

|------|------------------------|---------|-----------------|-------------------|-----|--------------|--------------|--------------|

| Name | e Function I/O<br>Name |         | (EXCLK, OSCSEL) | (EXCLKS, OSCSELS) |     |              |              |              |

| P121 | P121                   | Input   | 00/10/11        |                   | ×   | 1            | 1            | 1            |

|      | X1                     | -       | 01              |                   | -   | N            | V            | V            |

| P122 | P122                   | Input   | 00/10           | _                 | ×   |              |              |              |

|      | X2                     | -       | 01              |                   | -   | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|      | EXCLK                  | Input   | 11              |                   | -   |              |              |              |

| P123 | P123                   | Input   |                 | 00/10/11          | ×   |              | .1           | .1           |

|      | XT1                    | -       |                 | 01                | -   | V            | V            | N            |

| P124 | P124                   | Input   | -               | 00/10             | ×   |              |              |              |

|      | XT2                    | -       |                 | 01                | -   | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|      | EXCLKS                 | Input   |                 | 11                | -   |              |              |              |

# Table 4-6. Setting Examples of Registers and Output Latches When Using Alternate Function (9/10)

# Table 4-6. Setting Examples of Registers and Output Latches When Using Alternate Function (10/10)

| Pin  | Used F         | unction    | PIOR0×     | POM×× | PM×× | Pxx | PFSEG××                 | Alternate Fur         | Iternate Function Output |              | 80-pin       | 100-         |

|------|----------------|------------|------------|-------|------|-----|-------------------------|-----------------------|--------------------------|--------------|--------------|--------------|

| Name | Function       | I/O        |            |       |      |     | (ISCVL3,                | SAU Output Other than |                          |              |              | pin          |

|      | Name           |            |            |       |      |     | ISCCAP) <sup>Note</sup> | Function              | SAU                      |              |              |              |

| P125 | P125           | Input      | _          | _     | 1    | ×   | 1                       | -                     | -                        |              |              |              |

|      |                | Output     | ×          | _     | 0    | 0/1 | 1                       | _                     | (TO05) = 0               | ,            | ,            | 1            |

|      |                |            | ×          |       | 1    | ×   | 0                       |                       | PCLBUZ1 = 0              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|      | VL3            | _<br>Input | PIOR04 = 0 | _     | 1    | ×   | 1                       | _                     | _                        |              |              |              |

|      | (TI05)         | Input      | PIOR00 = 1 | _     | 1    | ×   | 1                       | _                     | _                        | _            |              | V            |

|      | (1103)<br>TI05 | Input      | PIOR00 = 0 | _     | 1    | ×   | 1                       | _                     | _                        |              | _            |              |

|      | (TO05)         | Output     | PIOR00 = 1 | _     | 0    | 0   | 1                       | _                     | PCLBUZ1 = 0              | _            | √            | √            |

|      | TO05           | Output     | PIOR00 = 0 | _     | 0    | 0   | 1                       | _                     | PCLBUZ1 = 0              |              | ,            |              |

|      | PCLBUZ1        | Output     | PIOR03 = 0 | _     | 0    | 0   | 1                       | _                     | TO05 = 0                 | $\checkmark$ | -            | -            |

| P126 | P126           | Input      | -          | -     | 1    | ×   | 1                       | _                     | _                        |              |              |              |

|      |                | Output     | ×          | _     | 0    | 0/1 | 1                       | -                     | (TO04) = 0               |              |              |              |

|      | CAPL           | _          | ×          | -     | 1    | ×   | 0                       | -                     | _                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|      | (TI04)         | Input      | PIOR00 = 1 | -     | 1    | ×   | 1                       | -                     | -                        |              |              |              |

|      | (TO04)         | Output     | PIOR00 = 1 | -     | 0    | 0   | 1                       | _                     | _                        | 1            |              |              |

| P127 | P127           | Input      | _          | _     | 1    | ×   | 1                       | -                     | -                        |              |              |              |

|      |                | Output     | ×          | -     | 0    | 0/1 | 1                       | _                     | (TO03) = 0               |              |              |              |

|      | CAPH           | -          | ×          | -     | 1    | ×   | 0                       | _                     | -                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|      | (TI03)         | Input      | PIOR00 = 1 | -     | 1    | ×   | 1                       | _                     | _                        |              |              |              |

|      | (TO03)         | Output     | PIOR00 = 1 | -     | 0    | 0   | 1                       | _                     | _                        |              |              |              |

| P137 | P137           | Input      | -          | -     | -    | ×   | -                       | _                     | -                        | $\checkmark$ | $\checkmark$ | ,            |

|      | INTP0          | Input      | PIOR04 = 0 | -     | -    | ×   | -                       | _                     | -                        | N            | N            | $\checkmark$ |

| P150 | P150           | Input      | -          | ×     | 1    | ×   | -                       | -                     | -                        |              |              |              |

|      |                | Output     | ×          | -     | 0    | 0/1 | -                       | -                     | -                        |              | $\checkmark$ |              |

|      | RTCOUT         | Output     | PIOR03 = 0 | -     | 0    | 0   | -                       | —                     | —                        | -            | Ň            | N            |

|      | RTCIC0         | Input      | ×          | -     | 1    | ×   | -                       | -                     | -                        |              |              |              |

| P151 | P151           | Input      | _          | ×     | 1    | ×   | -                       | -                     | _                        |              |              |              |

|      |                | Output     | -          | -     | 0    | 0/1 | -                       | -                     | -                        | -            | $\checkmark$ | $\checkmark$ |

|      | RTCIC1         | Input      | _          | -     | 1    | ×   | -                       | -                     | _                        |              |              |              |

| P152 | P152           | Input      | -          | -     | 1    | ×   | -                       | -                     | -                        |              |              |              |

|      |                | Output     | -          | -     | 0    | 0/1 | -                       | -                     | -                        | -            | $\checkmark$ | $\checkmark$ |

|      | RTCIC2         | Input      | _          | -     | 1    | ×   | _                       | _                     | _                        |              |              |              |

Note ISCVL3 and ISCCAP are registers that correspond to P125, and P126 and P127, respectively.

power consumption oscillation (AMPHS1, AMPHS0 = 1, 0) is selected.

• Configure the circuit of the circuit board, using material with little parasitic capacitance and wiring resistance.

• Place a ground pattern that has the same potential as Vss as much as possible near the XT1 oscillator.

• Be sure that the signal lines between the XT1 and XT2 pins, and the resonators do not cross with the other signal lines. Do not route the wiring near a signal line through which a high fluctuating current flows.

• The impedance between the XT1 and XT2 pins may drop and oscillation may be disturbed due to moisture absorption of the circuit board in a high-humidity environment or dew condensation on the board. When using the circuit board in such an environment, take measures to damp-proof the circuit board, such as by coating.

• When coating the circuit board, use material that does not cause capacitance or leakage between the XT1 and XT2 pins.

Caution 7. Be sure to clear bits 7, 6, 3, and 0 to 0.

#### 15.6.5 Hardware trigger no-wait mode (select mode, sequential conversion mode)

- <1> In the stop status, the ADCE bit of A/D converter mode register 0 (ADM0) is set to 1, and the system enters the A/D conversion standby status.

- <2> After the software counts up to the stabilization wait time (1  $\mu$ s), the ADCS bit of the ADM0 register is set to 1 to place the system in the hardware trigger standby status (and conversion does not start at this stage). Note that, while in this status, A/D conversion does not start even if ADCS is set to 1.

- <3> If a hardware trigger is input while ADCS = 1, A/D conversion is performed on the analog input specified by the analog input channel specification register (ADS).

- <4> When A/D conversion ends, the conversion result is stored in the A/D conversion result register (ADCR, ADCRH), and the A/D conversion end interrupt request signal (INTAD) is generated. After A/D conversion ends, the next A/D conversion immediately starts.

- <5> If a hardware trigger is input during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is discarded.

- <6> When the value of the ADS register is rewritten or overwritten during conversion operation, the current A/D conversion is interrupted, and A/D conversion is performed on the analog input respecified by the ADS register. The partially converted data is discarded.

- <7> When ADCS is overwritten with 1 during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is discarded.

- <8> When ADCS is cleared to 0 during conversion operation, the current A/D conversion is interrupted, and the system enters the A/D conversion standby status. However, the A/D converter does not stop in this status.

- <9> When ADCE is cleared to 0 while in the A/D conversion standby status, the A/D converter enters the stop status. When ADCS = 0, inputting a hardware trigger is ignored and A/D conversion does not start.

# Figure 15-22. Example of Hardware Trigger No-wait Mode (Select Mode, Sequential Conversion Mode) Operation Timing

|                     | <1<br>                | > ADCE is set         | to 1.                       |                                            |                  |                                                                            |                  |                                                                |                  | ADCE                                   | is cleare                         | d to 0. <                     | <u>}&gt;</u>              |

|---------------------|-----------------------|-----------------------|-----------------------------|--------------------------------------------|------------------|----------------------------------------------------------------------------|------------------|----------------------------------------------------------------|------------------|----------------------------------------|-----------------------------------|-------------------------------|---------------------------|

| ADCE                | Ì                     |                       | is set to 1.                |                                            |                  |                                                                            |                  |                                                                |                  |                                        |                                   |                               |                           |

| Hardware<br>trigger |                       |                       | > A hardward<br>is generate |                                            | <5               | <ul> <li>A hardware trig<br/>generated durin<br/>conversion ope</li> </ul> | ng A/D           |                                                                |                  |                                        |                                   |                               |                           |

|                     | The trigge acknowle   | r is not dged.        |                             |                                            |                  |                                                                            |                  | ADCS is over<br>with 1 durin<br>conversion ope                 |                  | ADCS is to 0 du conversion o           | cleared<<br>ring A/D<br>peration. | 8><br>The tr<br>ackn          | igger is not<br>owledged. |

| ADCS                |                       |                       |                             |                                            |                  |                                                                            | <6               | > ADS is rewritten<br>A/D conversion of<br>(from ANI0 to ANIC) | operation        |                                        |                                   |                               |                           |

| ADS                 |                       |                       |                             | Data 0<br>(ANI0)                           |                  |                                                                            |                  |                                                                | Data 1<br>(ANI1) |                                        |                                   |                               |                           |

| A/D                 |                       |                       | <4                          | > A/D convers<br>ends and th<br>conversion | e next           | Conversion is<br>interrupted <                                             |                  | Conversion is<br>interrupted <4<br>and restarts.               | >                | Conversion<br>interrupted<br>restarts. | and                               | Conversion<br>is interrupted. |                           |

|                     | Conversion<br>stopped | Conversion<br>standby | Data 0<br>(ANI0)            | Data 0<br>(ANI0)                           | Data 0<br>(ANI0) | Data 0<br>(ANI0)                                                           | Data 0<br>(ANI0) | Data 1<br>(ANI1)                                               | Data 1<br>(ANI1) | Data 1<br>(ANI1)                       | Data 1<br>(ANI1)                  | Conversion<br>standby         | Conversion<br>stopped     |

|                     | C                     | onversion start       | /                           | <b>D</b> ( 0                               |                  | 2.1.2                                                                      |                  |                                                                |                  |                                        |                                   |                               |                           |

| ADCR,<br>ADCRH      |                       |                       |                             | Data 0<br>(ANI0)                           |                  | Data 0<br>(ANI0)                                                           |                  | Data 0<br>(ANI0)                                               |                  | ata 1<br>NI1)                          |                                   | Data '<br>(ANI1               |                           |

| INTAD               |                       |                       |                             |                                            |                  |                                                                            |                  |                                                                |                  |                                        |                                   |                               |                           |

## 17.2.13 Peripheral clock control register (PCKC)

The PCKC register is used to control peripheral clocks. Set bit 0 to select a clock for the 24-bit  $\Delta\Sigma$  A/D converter. The PCKC register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Figure 17-20. Format of Peripheral Clock Control Register (PCKC)

| Address: F0098H | After rea | set: 00H R/ | W |   |   |   |       |        |

|-----------------|-----------|-------------|---|---|---|---|-------|--------|

| Symbol          | 7         | 6           | 5 | 4 | 3 | 2 | <1>   | <0>    |

| PCKC            | 0         | 0           | 0 | 0 | 0 | 0 | PLLCK | DSADCK |

| DSADCK | Selection of operation clock for 24-bit $\Delta\Sigma$ A/D converter                               |

|--------|----------------------------------------------------------------------------------------------------|

| 0      | Supply high-speed on-chip oscillator clock (fill). (Stop f <sub>MX</sub> supply) <sup>Note 1</sup> |

| 1      | Supply high-speed system clock (f <sub>MX</sub> ) <sup>Note 2</sup>                                |

**Notes 1.** When selecting the high-speed on-chip oscillator clock, be sure to run the high-speed on-chip oscillator clock frequency correction function.

2. Only a 12 MHz crystal oscillator can be used as the high-speed system clock frequency (fmx).

Caution Be sure to clear bits 7 to 2 to "0".

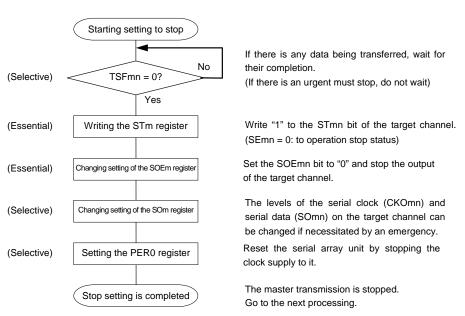

## Figure 18-44. Procedure for Stopping Master Transmission/Reception

## CHAPTER 19 SERIAL INTERFACE IICA

## **19.1 Functions of Serial Interface IICA**

Serial interface IICA has the following three modes.

#### (1) Operation stop mode

This mode is used when serial transfers are not performed. It can therefore be used to reduce power consumption.

#### (2) I<sup>2</sup>C bus mode (multimaster supported)

This mode is used for 8-bit data transfers with several devices via two lines: a serial clock (SCLAn) line and a serial data bus (SDAAn) line.

This mode complies with the l<sup>2</sup>C bus format and the master device can generated "start condition", "address", "transfer direction specification", "data", and "stop condition" data to the slave device, via the serial data bus. The slave device automatically detects these received status and data by hardware. This function can simplify the part of application program that controls the l<sup>2</sup>C bus.

Since the SCLAn and SDAAn pins are used for open drain outputs, serial interface IICA requires pull-up resistors for the serial clock line and the serial data bus line.

#### (3) Wakeup mode

The STOP mode can be released by generating an interrupt request signal (INTIICAn) when an extension code from the master device or a local address has been received while in STOP mode. This can be set by using the WUPn bit of IICA control register n1 (IICCTLn1).

Figure 19-1 shows a block diagram of serial interface IICA.

Remark n = 0

# 19.2 Configuration of Serial Interface IICA

Serial interface IICA includes the following hardware.

| Item              | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers         | IICA shift register n (IICAn)<br>Slave address register n (SVAn)                                                                                                                                                                                                                                                                                                                                                                        |

| Control registers | Peripheral enable register 0 (PER0)<br>Peripheral Reset Control Register 0 (PRR0)<br>IICA control register n0 (IICCTLn0)<br>IICA status register n (IICSn)<br>IICA flag register n (IICFn)<br>IICA control register n1 (IICCTLn1)<br>IICA control register n1 (IICCTLn1)<br>IICA low-level width setting register n (IICWLn)<br>IICA high-level width setting register n (IICWHn)<br>Port mode register 6 (PM6)<br>Port register 6 (P6) |

#### Table 19-1. Configuration of Serial Interface IICA

#### Remark n = 0

## (1) IICA shift register n (IICAn)

The IICAn register is used to convert 8-bit serial data to 8-bit parallel data and vice versa in synchronization with the serial clock. The IICAn register can be used for both transmission and reception.

The actual transmit and receive operations can be controlled by writing and reading operations to the IICAn register.

Cancel the wait state and start data transfer by writing data to the IICAn register during the wait period.

The IICAn register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears IICAn to 00H.

#### Figure 19-3. Format of IICA Shift Register n (IICAn)

Address: FFF50H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|---|---|---|---|---|---|---|

| IICAn  |   |   |   |   |   |   |   |   |

Cautions 1. Do not write data to the IICAn register during data transfer.

- 2. Write or read the IICAn register only during the wait period. Accessing the IICAn register in a communication state other than during the wait period is prohibited. When the device serves as the master, however, the IICAn register can be written only once after the communication trigger bit (STTn) is set to 1.

- 3. When communication is reserved, write data to the IICAn register after the interrupt triggered by a stop condition is detected.

Remark n = 0

(2) When communication reservation function is disabled (bit 0 (IICRSVn) of IICA flag register n (IICFn) = 1)

When bit 1 (STTn) of IICA control register n0 (IICCTLn0) is set to 1 when the bus is not used in a communication during bus communication, this request is rejected and a start condition is not generated. The following two statuses are included in the status where bus is not used.

- When arbitration results in neither master nor slave operation

- When an extension code is received and slave operation is disabled (ACK is not returned and the bus was released by setting bit 6 (LRELn) of the IICCTLn0 register to 1 and saving communication)

To confirm whether the start condition was generated or request was rejected, check STCFn (bit 7 of the IICFn register). It takes up to 5 clocks of  $f_{MCK}$  until the STCFn bit is set to 1 after setting STTn = 1. Therefore, secure the time by software.

**Remark** n = 0

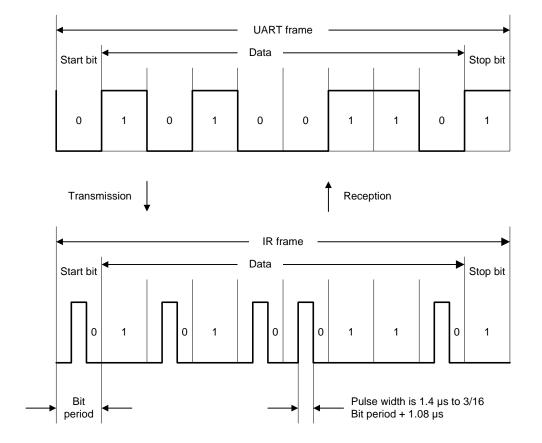

## 20.3.2 Transmission

In transmission, the signals output from the SAU (UART frames) are converted to the IR frame data through the IrDA (see **Figure 20-5**). When IRTXINV bit is 0 and serial data is 0, high-level pulses with the width of 3/16 the bit rate (1-bit width period) are output (initial setting). The high-level pulse width can be changed by using the IRCKS2 to IRCKS0 bits. The standard prescribes that the minimum high-level pulse width should be 1.41  $\mu$ s and the maximum high-level pulse width be (3/16 + 2.5%) × bit rate or (3/16 × bit rate) + 1.08  $\mu$ s.

When the CPU/peripheral hardware clock (fcLk) is 20 MHz, the high-level pulse width can be 1.41  $\mu$ s to 1.6  $\mu$ s. When serial data is 1, no pulses are output.

Figure 20-5. IrDA Transmission/Reception

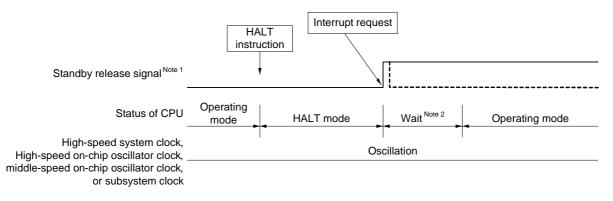

#### (2) HALT mode release

The HALT mode can be released by the following two sources.

(a) Release by unmasked interrupt request

When an unmasked interrupt request is generated, the HALT mode is released. If interrupt acknowledgment is enabled, vectored interrupt servicing is carried out. If interrupt acknowledgment is disabled, the next address instruction is executed.

Note 1. For details of the standby release signal, see Figure 24 - 1 Basic Configuration of Interrupt Function.

Note 2. Wait time for HALT mode release

| When vectored interrupt servicing is   | carried out     |

|----------------------------------------|-----------------|

| Main system clock:                     | 15 to 16 clocks |

| Subsystem clock (RTCLPC = 0):          | 10 to 11 clocks |

| Subsystem clock (RTCLPC = 1):          | 11 to 12 clocks |

| • When vectored interrupt servicing is | not carried out |

| Main system clock:                     | 9 to 10 clocks  |

| Subsystem clock (RTCLPC = 0):          | 4 to 5 clocks   |

| Subsystem clock (RTCLPC = 1):          | 5 to 6 clocks   |

|                                        |                 |

Remark The broken lines indicate the case when the interrupt request which has released the standby mode is acknowledged.

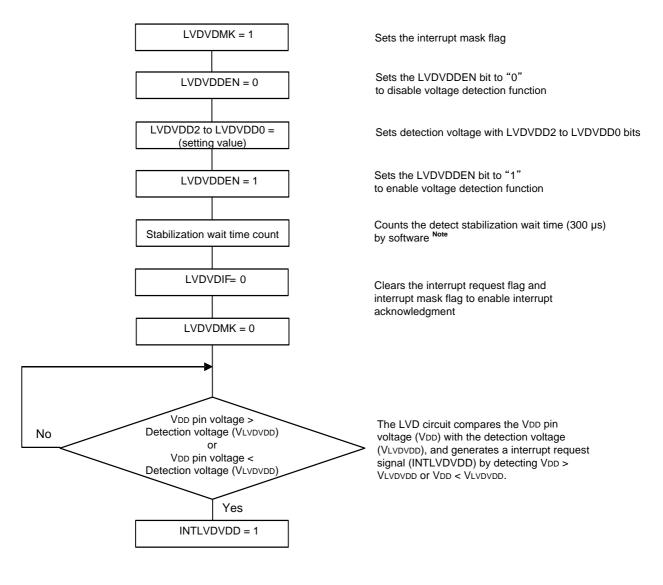

# 29.4.4 Each power supply pin voltage detection setting procedure

(1) Vdd

The setting procedure of VDD pin voltage detection is shown below.

#### Figure 29 - 21 Setting Procedure of VDD Pin Voltage Detection

Caution If other process operating secures the stabilization wait time after setting the LVDVDDEN bit to 1 to enable the voltage detect function operation, the count process isn't required.

## Table 36 - 12 Relationship Between Enabling Security Function and Command

## (1) During serial programming

| Valid Security                          | Executed Command                 |                                   |  |  |

|-----------------------------------------|----------------------------------|-----------------------------------|--|--|