Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I²C, IrDA, LINbus, UART/USART                                              |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 4x10b, 3x24b                                                                |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-LQFP                                                                         |

| Supplier Device Package    | 80-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10nmjdfb-50 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ac               | ddress | Special Function Register (SFR) Name                   | Symbol       | R/W | Mani         | After Reset  |              |                     |

|------------------|--------|--------------------------------------------------------|--------------|-----|--------------|--------------|--------------|---------------------|

|                  |        |                                                        |              |     | 1-bit        | 8-bit        | 16-bit       |                     |

| F0               | 0F0H   | Peripheral enable register 0                           | PER0         | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                 |

| F0               | 0F1H   | Peripheral reset control register 0                    | PRR0         | R/W | $\checkmark$ | $\checkmark$ | _            | 00H                 |

| F0               | 0F2H   | Mid-speed on-chip oscillator frequency select register | MOCODIV      | R/W | _            | $\checkmark$ | _            | 00H                 |

| . F0             | 0F3H   | Subsystem clock supply option control register         | OSMC         | R/W |              | √            | _            | 00H                 |

|                  | 0F5H   | RAM parity error control register                      | RPECTL       | R/W | √            | √<br>√       |              | 00H                 |

|                  | 0F8H   | Regulator mode control register                        | PMMC         | R/W | √            |              | _            | 00H                 |

|                  | 0F9H   | Power-on-reset status register                         | PORSR        | R/W | _            | 1            |              | 00H <sup>Note</sup> |

|                  | 0FAH   | Peripheral enable register 1                           | PER1         | R/W |              | √            | _            | 00H                 |

|                  | 0FBH   | Peripheral reset control register 1                    | PRR1         | R/W | √            | ,<br>√       | _            | 00H                 |

|                  | 0FCH   | Peripheral enable register 2                           | PER2         | R/W | √            | V            | _            | 00H                 |

|                  | 0FDH   | Peripheral reset control register 2                    | PRR2         | R/W | √            | v<br>√       |              | 00H                 |

| F00FEH<br>F0100H |        | BCD adjust result register                             | BCDADJ       | R   |              | V            |              | Undefined           |

|                  |        | Serial status register 00                              | SSR00L SSR00 | R   | _            | v<br>√       |              | 0000H               |

|                  | )101H  |                                                        |              | IX. | _            |              | v            | 000011              |

|                  | )102H  | Serial status register 01                              | SSR01L SSR01 | R   | _            | √            | V            | 0000H               |

|                  | )103H  |                                                        |              |     | _            | _            | ,            | 000011              |

|                  | )104H  | Serial status register 02                              | SSR02L SSR02 | R   | _            | √            |              | 0000H               |

|                  | )105H  |                                                        |              |     |              | _            | •            | 000011              |

|                  | )106H  | Serial status register 03                              | SSR03L SSR03 | R   | _            | $\checkmark$ |              | 0000H               |

| F0               | )107H  |                                                        |              |     | _            | _            |              |                     |

| F0               | 108H   | Serial flag clear trigger register 00                  | SIR00L SIR00 | R/W | _            | $\checkmark$ | $\checkmark$ | 0000H               |

| F0               | 109H   |                                                        | _            |     | _            | -            |              |                     |

| F0               | 10AH   | Serial flag clear trigger register 01                  | SIR01L SIR01 | R/W | _            | $\checkmark$ |              | 0000H               |

| F0               | )10BH  |                                                        | _            |     | -            | -            |              |                     |

| F0               | 10CH   | Serial flag clear trigger register 02                  | SIR02L SIR02 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H               |

| F0               | 10DH   |                                                        | _            |     | -            | -            |              |                     |

| F0               | 10EH   | Serial flag clear trigger register 03                  | SIR03L SIR03 | R/W | -            | $\checkmark$ | $\checkmark$ | 0000H               |

| F0               | 10FH   |                                                        | -            |     | -            | -            |              |                     |

| F0               | )110H  | Serial mode register 00                                | SMR00        | R/W | -            | -            | $\checkmark$ | 0020H               |

| F0               | )111H  |                                                        |              |     |              |              |              |                     |

| F0               | )112H  | Serial mode register 01                                | SMR01        | R/W | -            | -            | $\checkmark$ | 0020H               |

| F0               | )113H  |                                                        |              |     |              |              |              |                     |

| F0               | )114H  | Serial mode register 02                                | SMR02        | R/W | -            | -            | $\checkmark$ | 0020H               |

| F0               | )115H  |                                                        |              |     |              |              |              |                     |

| F0               | )116H  | Serial mode register 03                                | SMR03        | R/W | -            | -            | $\checkmark$ | 0020H               |

| F0               | )117H  |                                                        |              |     |              |              |              |                     |

| F0               | )118H  | Serial communication operation setting register        | SCR00        | R/W | -            | -            | $\checkmark$ | 0087H               |

| F0               | )119H  | 00                                                     |              |     |              |              |              |                     |

Note This register is reset only by a power-on reset.

| Address | : FFFA0H | After reset: 00                           | H R/W                                         |                  |                                      |                 |                      |                  |

|---------|----------|-------------------------------------------|-----------------------------------------------|------------------|--------------------------------------|-----------------|----------------------|------------------|

| Symbol  | 7        | 6                                         | 5                                             | 4                | 3                                    | 2               | 1                    | 0                |

| CMC     | EXCLK    | OSCSEL                                    | 0                                             | XT1SELEN         | 0                                    | 0               | 0                    | AMPH             |

| i       |          |                                           |                                               |                  |                                      |                 |                      |                  |

|         | EXCLK    | OSCSEL                                    | High-speed system clock<br>pin operation mode |                  | X1/P1                                | 21 pin          | X2/EXCL              | K/P122 pin       |

|         | 0        | 0                                         | Input port mod                                | le               | Input port                           |                 |                      |                  |

|         | 0        | 1                                         | X1 oscillation                                | mode             | Crystal/ceramic resonator connection |                 |                      |                  |

|         | 1        | 0                                         | Input port mode                               |                  | Input port                           |                 |                      |                  |

|         | 1        | 1                                         | External clock                                | input mode       | Input port                           |                 | External clock input |                  |

|         |          |                                           | •                                             |                  | •                                    |                 |                      |                  |

|         | XT1SELEN | Permits or pr                             |                                               |                  | cillation clock (f                   | ,               |                      | ck (fexs) as the |

|         | 0        | Prohibited (sw                            | vitching the cloc                             | k by setting the | e CSS bit in the                     | CKC register i  | s disabled).         |                  |

|         | 1        | Permitted (sw                             | itching the cloc                              | k by setting the | CSS bit in the                       | CKC register is | s enabled).          |                  |

|         |          |                                           |                                               |                  |                                      |                 |                      |                  |

|         | AMPH     | Control of X1 clock oscillation frequency |                                               |                  |                                      |                 |                      |                  |

|         | 0        | 1 MHz $\leq$ fx $\leq$ f                  | 10 MHz                                        |                  |                                      |                 |                      |                  |

|         | 1        | 10 MHz < fx ≤                             | 20 MHz                                        |                  |                                      |                 |                      |                  |

#### Figure 6 - 2 Format of Clock operation mode control register (CMC)

**Note 1.** This bit only permits switching the clock by setting the CSS bit in the CKC register. Simply setting this bit does not change the CPU/peripheral hardware clock (fcLK).

- Note 2. Setting this bit is not required if the low-speed on-chip oscillator clock (f<sub>L</sub>) is selected as the CPU/peripheral hardware clock (f<sub>CLK</sub>).

- Note 3. Be sure to write the same value as that of the OSCSELS bit in the SCMC register.

- Caution 1. The CMC register can be written only once after reset release, by an 8-bit memory manipulation instruction. When using the CMC register with its initial value (00H), be sure to set the register to 00H after a reset ends in order to prevent malfunction due to a program loop. Such a malfunction becomes unrecoverable when a value other than 00H is mistakenly written.

- Caution 2. After reset release, set the CMC register before X1 or XT1 oscillation is started as set by the clock operation status control register (CSC) or subsystem clock operation status control register (SCMC).

- Caution 3. Be sure to set the AMPH bit to 1 if the X1 clock oscillation frequency exceeds 10 MHz.

Caution 4. Specify the settings for the AMPH bit while fill is selected as fclk after a reset ends (before fclk is switched to fmx or fsub).

Caution 5. Although the maximum system clock frequency is 32 MHz, the maximum frequency of the X1 oscillator is 20 MHz.

**Remark** fx: X1 clock frequency

- Caution 1. Be sure to set bits 2 and 3 of the CKC register to 0.

- Caution 2. The clock set by the CSS bit is supplied to the CPU and peripheral hardware. If the CPU clock is changed, therefore, the clock supplied to peripheral hardware (except the independent power supply RTC, 12-bit interval timer, clock output/buzzer output, LCD controller/driver, 8-bit interval timer, frequency measurement circuit, oscillation stop detection circuit, and watchdog timer) is also changed at the same time. Consequently, stop each peripheral function when changing the CPU/peripheral hardware clock.

- Caution 3. If the subsystem clock is used as the peripheral hardware clock, the operations of the A/D converter and IICA are not guaranteed. For the operating characteristics of the peripheral hardware, refer to the chapters describing the various peripheral hardware as well as CHAPTER 41 ELECTRICAL SPECIFICATIONS.

power consumption oscillation (AMPHS1, AMPHS0 = 1, 0) is selected.

• Configure the circuit of the circuit board, using material with little parasitic capacitance and wiring resistance.

• Place a ground pattern that has the same potential as Vss as much as possible near the XT1 oscillator.

• Be sure that the signal lines between the XT1 and XT2 pins, and the resonators do not cross with the other signal lines. Do not route the wiring near a signal line through which a high fluctuating current flows.

• The impedance between the XT1 and XT2 pins may drop and oscillation may be disturbed due to moisture absorption of the circuit board in a high-humidity environment or dew condensation on the board. When using the circuit board in such an environment, take measures to damp-proof the circuit board, such as by coating.

• When coating the circuit board, use material that does not cause capacitance or leakage between the XT1 and XT2 pins.

Caution 7. Be sure to clear bits 7, 6, 3, and 0 to 0.

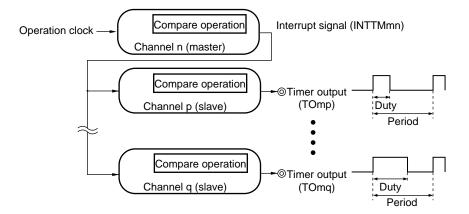

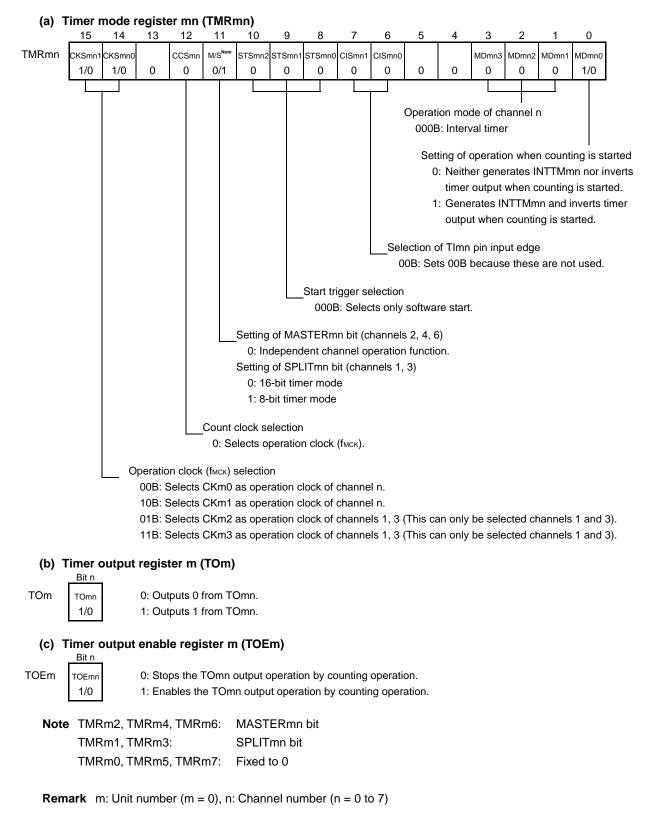

#### (3) Multiple PWM (Pulse Width Modulation) output

By extending the PWM function and using one master channel and two or more slave channels, up to seven types of PWM signals that have a specific period and a specified duty factor can be generated.

# Caution For details about the rules of simultaneous channel operation function, see 8.4.1 Basic rules of simultaneous channel operation function.

**Remark** m: Unit number (m = 0), n: Channel number (n = 0 to 7), p, q: Slave channel number (n \leq 7)

#### 8.1.3 8-bit timer operation function (channels 1 and 3 only)

The 8-bit timer operation function makes it possible to use a 16-bit timer channel in a configuration consisting of two 8bit timer channels. This function can only be used for channels 1 and 3.

Caution There are several rules for using 8-bit timer operation function. For details, see 8.4.2 Basic rules of 8-bit timer operation function (channels 1 and 3 only).

#### Figure 8-47. Example of Set Contents of Registers During Operation as Interval Timer/Square Wave Output (1/2)

|             | Software Operation                                                                                                                                                                                           | Hardware Status                                                                                                                                                             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>stop | To hold the TOmn pin output level<br>Clears the TOmn bit to 0 after the value to<br>be held is set to the port register.<br>When holding the TOmn pin output level is not necessary<br>Setting not required. | The TOmn pin output level is held by port function.                                                                                                                         |

|             | The TAUmEN bit of the PER0 register is cleared to 0.                                                                                                                                                         | Power-off status<br>All circuits are initialized and SFR of each channel is also<br>initialized.<br>(The TOmn bit is cleared to 0 and the TOmn pin is set to<br>port mode.) |

Figure 8-48. Operation Procedure of Interval Timer/Square Wave Output Function (2/2)

**Remark** m: Unit number (m = 0), n: Channel number (n = 0 to 7)

|                               | Software Operation                                                                                                                                                                                                                                                                                                           | Hardware Status                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                                                                                                                              | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                                                                                   |

|                               | Sets the TAUmEN bit of peripheral enable register 0<br>(PER0) to 1.                                                                                                                                                                                                                                                          | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                                                                                      |

|                               | Sets timer clock select register m (TPSm).<br>Determines clock frequencies of CKm0 to CKm3.                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                              |

| Channel<br>default<br>setting | Sets the corresponding bit of the noise filter enable<br>register 1 (NFEN1) to 0 (off) or 1 (on).<br>Sets timer mode register mn (TMRmn) (determines<br>operation mode of channel).<br>Sets number of counts to timer data register mn<br>(TDRmn).<br>Clears the TOEmn bit of timer output enable register m<br>(TOEm) to 0. | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                                                                                  |

| Operation<br>start            | Sets the TSmn bit to 1.<br>The TSmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                                                                                                                           | TEmn = 1, and count operation starts.<br>Value of the TDRmn register is loaded to timer count<br>register mn (TCRmn) and detection of the TImn pin<br>input edge is awaited.                                                                                                                                                                                 |

| During<br>operation           | Set value of the TDRmn register can be changed.<br>The TCRmn register can always be read.<br>The TSRmn register is not used.<br>Set values of the TMRmn register, TOMmn, TOLmn,<br>TOmn, and TOEmn bits cannot be changed.                                                                                                   | Counter (TCRmn) counts down each time input edge of<br>the TImn pin has been detected. When count value<br>reaches 0000H, the value of the TDRmn register is loaded<br>to the TCRmn register again, and the count operation is<br>continued. By detecting TCRmn = 0000H, the INTTMmn<br>output is generated.<br>After that, the above operation is repeated. |

| Operation<br>stop             | The TTmn bit is set to 1.<br>The TTmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                                                                                                                         | TEmn = 0, and count operation stops.<br>The TCRmn register holds count value and stops.                                                                                                                                                                                                                                                                      |

| TAU<br>stop                   | The TAUmEN bit of the PER0 register is cleared to 0.                                                                                                                                                                                                                                                                         | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.                                                                                                                                                                                                                                                             |

| Figure 8-52. | Operation         | Procedure Who | en External I | Event Counter | Function Is Used |

|--------------|-------------------|---------------|---------------|---------------|------------------|

| · .g         | • • • • • • • • • |               |               |               |                  |

**Remark** m: Unit number (m = 0), n: Channel number (n = 0 to 7)

| Pin Name | I/O    | Function                                      |

|----------|--------|-----------------------------------------------|

| XT1      | Input  | Connecting a 32.768-kHz crystal vibrator.     |

| XT2      | Input  | _                                             |

| EXCLKS   | Input  | Connecting a 32.768-kHz external clock input. |

| RTCOUT   | Output | 1 or 64-Hz waveform output pin.               |

| RTCIC0   | Input  | Time capture event input pins                 |

| RTCIC1   | Input  | _                                             |

| RTCIC2   | Input  | —                                             |

Table 9 - 2

Pin Configuration of RTC

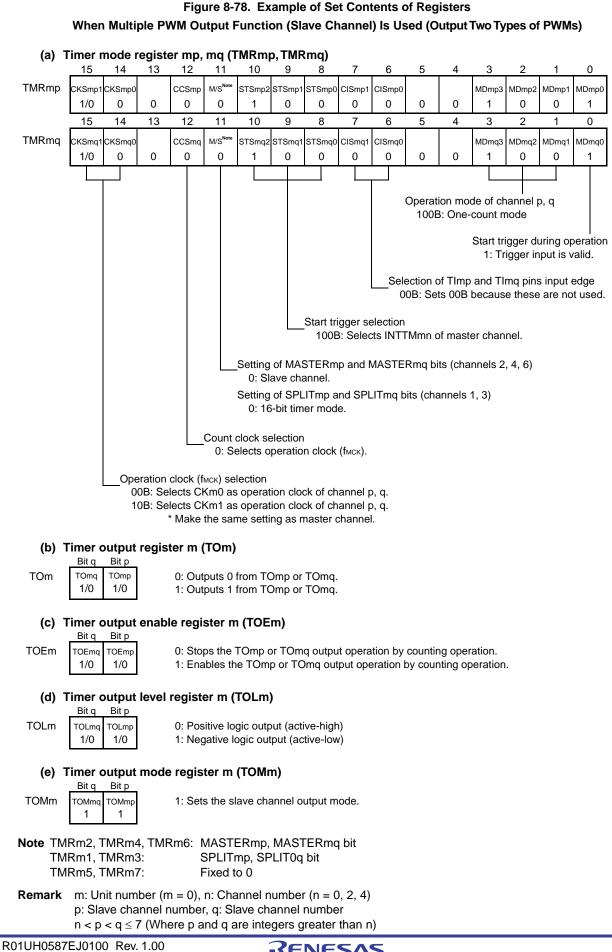

#### 15.6.10 Hardware trigger wait mode (select mode, one-shot conversion mode)

- <1> In the stop status, the ADCE bit of A/D converter mode register 0 (ADM0) is set to 1, and the system enters the hardware trigger standby status.

- <2> If a hardware trigger is input while in the hardware trigger standby status, A/D conversion is performed on the analog input specified by the analog input channel specification register (ADS). The ADCS bit of the ADMO register is automatically set to 1 according to the hardware trigger input.

- <3> When A/D conversion ends, the conversion result is stored in the A/D conversion result register (ADCR, ADCRH), and the A/D conversion end interrupt request signal (INTAD) is generated.

- <4> After A/D conversion ends, the ADCS bit is automatically cleared to 0, and the A/D converter enters the stop status.

- <5> If a hardware trigger is input during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is discarded.

- <6> When the value of the ADS register is rewritten or overwritten during conversion operation, the current A/D conversion is interrupted, and A/D conversion is performed on the analog input respecified by the ADS register. The partially converted data is discarded.

- <7> When ADCS is overwritten with 1 during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is initialized.

- <8> When ADCS is cleared to 0 during conversion operation, the current A/D conversion is interrupted, the system enters the hardware trigger standby status, and the A/D converter enters the stop status. When ADCE = 0, inputting a hardware trigger is ignored and A/D conversion does not start.

# Figure 15-27. Example of Hardware Trigger Wait Mode (Select Mode, One-shot Conversion Mode) Operation Timing

- Notes 1. The number of bits used as the shift register and buffer register differs depending on the unit and channel.

- mn = 00, 01: lower 9 bits

- Other than above: lower 8 bits

- 2. The lower 8 bits of serial data register mn (SDRmn) can be read or written as the following SFR, depending on the communication mode.

- CSIp communication ... SIOp (CSIp data register)

- UARTq reception ... RXDq (UARTq receive data register)

- UARTq transmission ... TXDq (UARTq transmit data register)

- IICr communication ... SIOr (IICr data register)

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), p: CSI number (p = 00, 10, 30), q: UART number (q = 0 to 3), r: IIC number (r = 00, 10, 30), mn = 00 to 03, 10 to 13

| SMRmn<br>Register | SPSm Register |            |            |            |            |            |            |            | Operation C          | Clock (f <sub>MCK</sub> ) <sup>Note</sup> |

|-------------------|---------------|------------|------------|------------|------------|------------|------------|------------|----------------------|-------------------------------------------|

| CKSmn             | PRS<br>m13    | PRS<br>m12 | PRS<br>m11 | PRS<br>m10 | PRS<br>m03 | PRS<br>m02 | PRS<br>m01 | PRS<br>m00 |                      | fclк = 24 MHz                             |

| 0                 | Х             | Х          | Х          | Х          | 0          | 0          | 0          | 0          | fclk                 | 24 MHz                                    |

|                   | Х             | Х          | Х          | Х          | 0          | 0          | 0          | 1          | fclк/2               | 12 MHz                                    |

|                   | Х             | Х          | Х          | Х          | 0          | 0          | 1          | 0          | fclk/2 <sup>2</sup>  | 6 MHz                                     |

|                   | Х             | Х          | Х          | Х          | 0          | 0          | 1          | 1          | fclк/2 <sup>3</sup>  | 3 MHz                                     |

|                   | Х             | Х          | Х          | Х          | 0          | 1          | 0          | 0          | fc∟ĸ/2⁴              | 1.5 MHz                                   |

|                   | Х             | Х          | Х          | Х          | 0          | 1          | 0          | 1          | fc∟ĸ/2⁵              | 750 kHz                                   |

|                   | Х             | Х          | Х          | Х          | 0          | 1          | 1          | 0          | fc∟ĸ/2 <sup>6</sup>  | 375 kHz                                   |

|                   | Х             | Х          | Х          | Х          | 0          | 1          | 1          | 1          | fclk/2 <sup>7</sup>  | 187.5 kHz                                 |

|                   | Х             | Х          | Х          | Х          | 1          | 0          | 0          | 0          | fclk/2 <sup>8</sup>  | 93.8 kHz                                  |

|                   | Х             | Х          | Х          | Х          | 1          | 0          | 0          | 1          | fclк/2 <sup>9</sup>  | 46.9 kHz                                  |

|                   | Х             | Х          | Х          | Х          | 1          | 0          | 1          | 0          | fськ/2 <sup>10</sup> | 23.4 kHz                                  |

|                   | Х             | Х          | Х          | Х          | 1          | 0          | 1          | 1          | fськ/2 <sup>11</sup> | 11.7 kHz                                  |

| 1                 | 0             | 0          | 0          | 0          | Х          | Х          | Х          | Х          | fclк                 | 24 MHz                                    |

|                   | 0             | 0          | 0          | 1          | Х          | Х          | Х          | Х          | fclк/2               | 12 MHz                                    |

|                   | 0             | 0          | 1          | 0          | Х          | Х          | Х          | Х          | fclk/2 <sup>2</sup>  | 6 MHz                                     |

|                   | 0             | 0          | 1          | 1          | Х          | Х          | Х          | Х          | fclĸ/2³              | 3 MHz                                     |

|                   | 0             | 1          | 0          | 0          | Х          | Х          | Х          | Х          | fc∟ĸ/2⁴              | 1.5 MHz                                   |

|                   | 0             | 1          | 0          | 1          | Х          | Х          | Х          | Х          | fclĸ/2⁵              | 750 kHz                                   |

|                   | 0             | 1          | 1          | 0          | Х          | Х          | Х          | Х          | fclk/2 <sup>6</sup>  | 375 kHz                                   |

|                   | 0             | 1          | 1          | 1          | Х          | Х          | Х          | Х          | fclk/2 <sup>7</sup>  | 187.5 kHz                                 |

|                   | 1             | 0          | 0          | 0          | Х          | Х          | Х          | Х          | fclк/2 <sup>8</sup>  | 93.8 kHz                                  |

|                   | 1             | 0          | 0          | 1          | Х          | Х          | Х          | Х          | fclк/2 <sup>9</sup>  | 46.9 kHz                                  |

|                   | 1             | 0          | 1          | 0          | Х          | Х          | Х          | Х          | fськ/2 <sup>10</sup> | 23.4 kHz                                  |

|                   | 1             | 0          | 1          | 1          | Х          | Х          | Х          | Х          | fськ/2 <sup>11</sup> | 11.7 kHz                                  |

|                   |               | (          | Other th   | nan abo    | ove        |            |            |            | Setting prohibited   |                                           |

Table 18-5. Selection of Operation Clock For Simplified I<sup>2</sup>C

**Note** When changing the clock selected for fcLK (by changing the system clock control register (CKC) value), do so after having stopped (serial channel stop register m (STm) = 000FH) the operation of the serial array unit (SAU).

Remarks 1. X: Don't care

**2.** m: Unit number (m = 0, 1), n: Channel number (n = 0, 2), mn = 00, 02, 12

Here is an example of setting an I<sup>2</sup>C transfer rate where  $f_{MCK} = f_{CLK} = 24$  MHz.

| I <sup>2</sup> C Transfer Mode | fclk = 24 MHz          |             |                             |                                     |  |  |  |  |

|--------------------------------|------------------------|-------------|-----------------------------|-------------------------------------|--|--|--|--|

| (Desired Transfer Rate)        | Operation Clock (fmck) | SDRmn[15:9] | Calculated<br>Transfer Rate | Error from Desired Transfer<br>Rate |  |  |  |  |

| 100 kHz                        | fclк/2                 | 59          | 100 kHz                     | 0.0%                                |  |  |  |  |

| 400 kHz                        | fclk                   | 29          | 380 kHz                     | 5.0% <sup>Note</sup>                |  |  |  |  |

| 1 MHz                          | fclĸ                   | 5           | 0.84 MHz                    | 16.0% <sup>Note</sup>               |  |  |  |  |

**Note** The error cannot be set to about 0% because the duty ratio of the SCL signal is 50%.

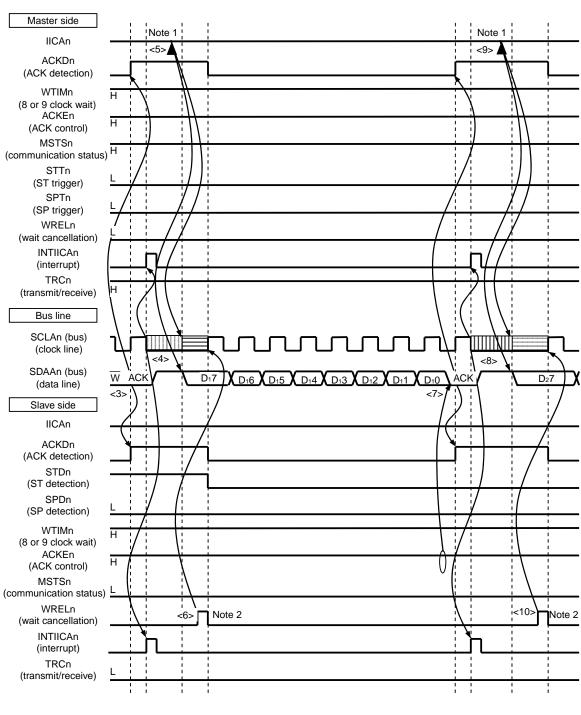

# Figure 19-33. Example of Master to Slave Communication (9-Clock Wait Is Selected for Master, 9-Clock Wait Is Selected for Slave) (2/4)

## (2) Address ~ data ~ data

: Wait state by slave device

: Wait state by master and slave devices

- **Notes 1.** Write data to IICAn, not setting the WRELn bit, in order to cancel a wait state during transmission by a master device.

- 2. For releasing wait state during reception of a slave device, write "FFH" to IICAn or set the WRELn bit.

Remark n = 0

RENESAS

# RL78/I1C

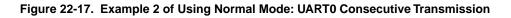

# (2) Example 2 of using normal mode: UART0 consecutive transmission

The DTC is activated by a UART0 transmit buffer empty interrupt and the value of RAM is transferred to the UART0 transmit buffer.

- The vector address is FFB0CH and control data is allocated at FFBC8H to FFBCFH

- Transfers 8 bytes of FFCF8H to FFCFFH of RAM to the UART0 transmit buffer (FFF10H)

The value of the DTRLD17 register is not used because of normal mode, but initialize the register to 00H when parity error resets are enabled (RPERDIS = 0) using the RAM parity error detection function. Start the first UART0 transmission by software. The second and subsequent transmissions are automatically sent when the DTC is activated by a transmit buffer empty interrupt.

# 22.5 Notes on DTC

#### 22.5.1 Setting DTC control data and vector table

- Do not access the DTC SFRs, the DTC control data area, the DTC vector table area, or the general-register (FFEE0H to FFEFFH) space using a DTC transfer.

- Modify the DTC base address register (DTCBAR) while all DTC activation sources are set to activation disabled.

- Do not rewrite the DTC base address register (DTCBAR) twice or more.

- Modify the data of the DTCCRj, DTBLSj, DTCCTj, DTRLDj, DTSARj, or DTDARj register when the corresponding bit among bits DTCENi0 to DTCENi7 in the DTCENi (i = 0 to 4) register is 0 (DTC activation disabled).

- Modify the start address of the DTC control data area to be set in the vector table when the corresponding bit among bits DTCENi0 to DTCENi7 in the DTCENi (i = 0 to 4) register is 0 (DTC activation disabled).

- Do not allocate RAM addresses which are used as a DTC transfer destination/transfer source to the area FFE20H to FFEDFH when performing self-programming and rewriting the data flash memory.

#### 22.5.2 Allocation of DTC control data area and DTC vector table area

The areas where the DTC control data and vector table can be allocated differ.

- It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space as the DTC control data area or DTC vector table area.

- Make sure the stack area, the DTC control data area, and the DTC vector table area do not overlap.

- The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the self-programming and data-flash functions.

R5F10NMJ, R5F10NPJ: FBF00H to FC309H

R5F10NMG, R5F10NLG: FDF00H to FE309H

• The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the on-chip trace function.

R5F10NMJ, R5F10NPJ: FC300H to FC6FFH

R5F10NMG, R5F10NLG: FE300H to FE6FFH

• Initialize the DTRLD register to 00H even in normal mode when parity error resets are enabled (RPERDIS = 0) using the RAM parity error detection function.

#### 22.5.3 DTC pending instruction

Even if a DTC transfer request is generated, data transfer is held pending immediately after the following instructions. Also, the DTC is not activated between PREFIX instruction code and the instruction immediately after that code.

Call/return instruction

< R >

<R>

- Unconditional branch instruction

- Conditional branch instruction

- Read access instruction for code flash memory

- Bit manipulation instructions for IFxx, MKxx, PRxx, and PSW, and an 8-bit manipulation instruction that has the ES register as operand

- Instruction for accessing the data flash memory

- Instruction of Multiply, Divide, Multiply & Accumulate (excluding MULU)

- Cautions 1. When a DTC transfer request is acknowledged, all interrupt requests are held pending until DTC transfer is completed.

- 2. While the DTC is held pending by the DTC pending instruction, all interrupt requests are held pending.

| Register Name | Event Generator (Output Origin of Event Input n)                    | Event Description |

|---------------|---------------------------------------------------------------------|-------------------|

| ELSELR00      | External interrupt edge detection 0                                 | INTP0             |

| ELSELR01      | External interrupt edge detection 1                                 | INTP1             |

| ELSELR02      | External interrupt edge detection 2                                 | INTP2             |

| ELSELR03      | External interrupt edge detection 3                                 | INTP3             |

| ELSELR04      | External interrupt edge detection 4                                 | INTP4             |

| ELSELR05      | External interrupt edge detection 5                                 | INTP5             |

| ELSELR06      | External interrupt edge detection 6                                 | INTP6             |

| ELSELR07      | External interrupt edge detection 7                                 | INTP7             |

| ELSELR08      | Key return signal detection                                         | INTKR             |

| ELSELR09      | 12-bit interval timer interval signal detection                     | INTIT             |

| ELSELR10      | 8-bit interval timer channel 00 compare match or                    | INTIT00           |

|               | 16-bit interval timer channel 0 compare match (cascaded)            |                   |

| ELSELR11      | 8-bit interval timer channel 10 compare match or                    | INTIT10           |

|               | 16-bit interval timer channel 1 compare match (cascaded)            |                   |

| ELSELR12      | Fixed-cycle signal of real-time clock                               | INTRTCPRD         |

| ELSELR13      | TAU channel 00 count end/capture end                                | INTTM00           |

| ELSELR14      | TAU channel 01 count end/capture end                                | INTTM01           |

| ELSELR15      | TAU channel 02 count end/capture end                                | INTTM02           |

| ELSELR16      | TAU channel 03 count end/capture end                                | INTTM03           |

| ELSELR17      | TAU channel 05 count end/capture end                                | INTTM05           |

| ELSELR18      | TAU channel 07 count end/capture end                                | INTTM07           |

| ELSELR19      | 24-bit $\Delta\Sigma$ -type A/D conversion end                      | INTDSAD           |

| ELSELR20      | Zero-cross detection 0 of 24-bit $\Delta\Sigma$ -type A/D converter | INTDSADZC0        |

| ELSELR21      | Zero-cross detection 1 of 24-bit ΔΣ-type A/D converter              | INTDSADZC1        |

# Table 23 - 2 Correspondence Between ELSELRn (n = 00 to 21) Registers and Peripheral Functions

# Figure 29 - 8 Format of User Option Byte (000C1H/010C1H) (1/2)

Address: 000C1H/010C1HNote

| 7     | 6     | 5     | 4 | 3     | 2     | 1       | 0       |

|-------|-------|-------|---|-------|-------|---------|---------|

| VPOC2 | VPOC1 | VPOC0 | 1 | LVIS1 | LVIS0 | LVIMDS1 | LVIMDS0 |

• LVD setting (interrupt & reset mode)

| De     | etection volta | ige     | Option byte Setting Value |              |             |           |       |              |         |

|--------|----------------|---------|---------------------------|--------------|-------------|-----------|-------|--------------|---------|

| VLV    | VDH            | Vlvdl   |                           |              |             |           |       | Mode setting |         |

| Rising | Falling        | Falling | VPOC2                     | VPOC1        | VPOC0       | LVIS1     | LVIS0 | LVIMDS1      | LVIMDS0 |

| edge   | edge           | edge    |                           |              |             |           |       | LVINDST      | LVINDSO |

| 1.77 V | 1.73 V         | 1.63 V  | 0                         | 0            | 0           | 1         | 0     | 1            | 0       |

| 1.88 V | 1.84 V         |         |                           |              |             | 0         | 1     |              |         |

| 2.92 V | 2.86 V         |         |                           |              |             | 0         | 0     |              |         |

| 1.98 V | 1.94 V         | 1.84 V  |                           | 0            | 1           | 1         | 0     |              |         |

| 2.09 V | 2.04 V         |         |                           |              |             | 0         | 1     |              |         |

| 3.13 V | 3.06 V         |         |                           |              |             | 0         | 0     |              |         |

| 2.61 V | 2.55 V         | 2.45 V  |                           | 1            | 0           | 1         | 0     |              |         |

| 2.71 V | 2.65 V         |         |                           |              |             | 0         | 1     |              |         |

| 2.92 V | 2.86 V         | 2.75 V  |                           | 1            | 1           | 1         | 0     | 1            |         |

| 3.02 V | 2.96 V         |         |                           |              |             | 0         | 1     | 1            |         |

|        |                |         | Settings oth              | her than the | above are p | rohibited |       |              |         |

• LVD setting (reset mode)

| Detection voltage |              | Option byte Setting Value |              |             |           |       |              |         |  |

|-------------------|--------------|---------------------------|--------------|-------------|-----------|-------|--------------|---------|--|

| Vlvd              |              | VPOC2                     | VPOC1        | VPOC0       | LVIS1     | LVIS0 | Mode setting |         |  |

| Rising edge       | Falling edge | VF002                     | VFUCI        | VFUCU       | LVIST     | LVISU | LVIMDS1      | LVIMDS0 |  |

| 1.67 V            | 1.63 V       | 0                         | 0            | 0           | 1         | 1     | 1            | 1       |  |

| 1.77 V            | 1.73 V       |                           | 0            | 0           | 1         | 0     |              |         |  |

| 1.88 V            | 1.84 V       |                           | 0            | 1           | 1         | 1     |              |         |  |

| 1.98 V            | 1.94 V       |                           | 0            | 1           | 1         | 0     |              |         |  |

| 2.09 V            | 2.04 V       |                           | 0            | 1           | 0         | 1     |              |         |  |

| 2.50 V            | 2.45 V       |                           | 1            | 0           | 1         | 1     |              |         |  |

| 2.61 V            | 2.55 V       |                           | 1            | 0           | 1         | 0     |              |         |  |

| 2.71 V            | 2.65 V       |                           | 1            | 0           | 0         | 1     |              |         |  |

| 2.81 V            | 2.75 V       |                           | 1            | 1           | 1         | 1     |              |         |  |

| 2.92 V            | 2.86 V       |                           | 1            | 1           | 1         | 0     |              |         |  |

| 3.02 V            | 2.96 V       | 1                         | 1            | 1           | 0         | 1     |              |         |  |

| 3.13 V            | 3.06 V       | 1                         | 0            | 1           | 0         | 0     |              |         |  |

| _                 | ÷<br>—       | Settings oth              | ner than the | above are p | rohibited |       | •            | •       |  |

Note

Set the same value as 000C1H to 010C1H when the boot swap operation is used because 000C1H is replaced by 010C1H.

Remark 1. For details on the LVD circuit, see CHAPTER 29 VOLTAGE DETECTOR.

Remark 2. The detection voltage is a TYP. value. For details, see 41.6.5 LVD circuit characteristics.

(Cautions are listed on the next page.)

# 36.4.3 Selecting communication mode

Communication mode of the RL78 microcontroller as follows.

| Communication Mode                                                                              |      | Ding Lload                                          |           |               |                     |  |

|-------------------------------------------------------------------------------------------------|------|-----------------------------------------------------|-----------|---------------|---------------------|--|

| Communication mode                                                                              | Port | Speed Note 2                                        | Frequency | Multiply Rate | Pins Used           |  |

| 1-line mode<br>(when flash memory<br>programmer is used, or<br>when external device is<br>used) | UART | 115200 bps,<br>250000 bps,<br>500000 bps,<br>1 Mbps | _         | _             | TOOLO               |  |

| Dedicated UART<br>(when external device is<br>used)                                             | UART | 115200 bps,<br>250000 bps,<br>500000 bps,<br>1 Mbps | _         | _             | TOOLTxD,<br>TOOLRxD |  |

# Table 36 - 6 Communication Modes

Note 1. Selection items for Standard settings on GUI of the flash memory programmer.

**Note 2.** Because factors other than the baud rate error, such as the signal waveform slew, also affect UART communication, thoroughly evaluate the slew as well as the baud rate error.

| Items                                    | Symbol                                                                                                  | Conditions                                                                                                            |                                                                              | MIN. | TYP. | MAX.                   | Unit |

|------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------------------------|------|

| Output current,<br>Iow <sup>Note 1</sup> | Iol1                                                                                                    | Per pin for P02 to P07, P10 to P17,<br>P30 to P37, P40 to P43, P50 to P57,<br>P70 to P77, P80 to P85, P125 to<br>P127 |                                                                              |      |      | 20.0 <sup>Note 2</sup> | mA   |

|                                          |                                                                                                         | Per pin for P60 to P62                                                                                                |                                                                              |      |      | 15.0 <sup>Note 2</sup> | mA   |

|                                          | (When duty = 70% <sup>Note 3</sup> )                                                                    | $4.0~V \leq EV_{\text{DD}} \leq 5.5~V$                                                                                |                                                                              |      | 70.0 | mA                     |      |

|                                          |                                                                                                         | $2.7~V \leq EV_{\text{DD}} < 4.0~V$                                                                                   |                                                                              |      | 15.0 | mA                     |      |

|                                          |                                                                                                         | $1.9~V \leq EV_{\text{DD}} < 2.7~V$                                                                                   |                                                                              |      | 9.0  | mA                     |      |

|                                          |                                                                                                         |                                                                                                                       | $1.7~V \leq EV_{\text{DD}} < 1.9~V$                                          |      |      | 4.5                    | mA   |

|                                          |                                                                                                         | Total of P10 to P17, P30 to P37,                                                                                      | $4.0~V \leq EV_{\text{DD}} \leq 5.5~V$                                       |      |      | 80.0                   | mA   |

|                                          | P50 to P57, P60 to P62, P70 to P77,<br>P80 to P85, P125 to P127<br>(When duty = 70% <sup>Note 3</sup> ) | P50 to P57, P60 to P62, P70 to P77,                                                                                   | $2.7~V \leq EV_{\text{DD}} < 4.0~V$                                          |      |      | 35.0                   | mA   |

|                                          |                                                                                                         | $1.9~V \leq EV_{\text{DD}} < 2.7~V$                                                                                   |                                                                              |      | 20.0 | mA                     |      |

|                                          |                                                                                                         |                                                                                                                       | $1.7~V \leq EV_{\text{DD}} < 1.9~V$                                          |      |      | 10.0                   | mA   |

|                                          |                                                                                                         | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                             |                                                                              |      |      | 150.0                  | mA   |

|                                          | IOL2                                                                                                    | Per pin for P20 to P25, P150 to P152                                                                                  | $1.7 \text{ V} \leq \text{V}_{\text{DD}}^{\text{Note 4}} \leq 5.5 \text{ V}$ |      |      | 0.4 <sup>Note 2</sup>  | mA   |

|                                          |                                                                                                         | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                             | $1.7~\text{V} \leq \text{V}_{\text{DD}}^{\text{Note 4}} \leq 5.5~\text{V}$   |      |      | 3.6                    | mA   |

| $(T_A = -40 \text{ to } +85^{\circ}C, 1.7 \text{ V} \le EV_{DD0} = EV_{DD1} \le V_{DD}^{Note 4} \le 5.5 \text{ V}, \text{ Vss} = EV_{SS}$ |

|-------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------|

**Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from an output pin to the EVss and Vss pins.

- 2. However, do not exceed the total current value.

- 3. Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

• Total output current of pins =  $(I_{OL} \times 0.7)/(n \times 0.01)$

<Example> Where n = 80% and  $I_{OL}$  = 10.0 mA

Total output current of pins =  $(10.0 \times 0.7)/(80 \times 0.01) \approx 8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

- 4. Either  $V_{DD}$  or VBAT is selected by the battery backup function.

- **Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.