Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, IrDA, LINbus, UART/USART                                 |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 68                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 6x10b, 4x24b                                                                |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10npgdfb-30 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 16.2   | Registe | ers                                                                                      | 480 |

|--------|---------|------------------------------------------------------------------------------------------|-----|

|        | 16.2.1  | Peripheral enable register 0 (PER0)                                                      | 480 |

|        | 16.2.2  | Temperature sensor control test register (TMPCTL)                                        | 481 |

|        | 16.2.3  | Peripheral reset control register 0 (PRR0)                                               | 481 |

| 16.3   | Setting | Procedures                                                                               | 482 |

|        | 16.3.1  | Starting operation of the temperature sensor                                             | 482 |

|        | 16.3.2  | Switching modes                                                                          | 483 |

|        |         |                                                                                          |     |

| CHAPTE | R 17 24 | 4-BIT ΔΣ A/D CONVERTER                                                                   | 484 |

| 17.1   | Functio | ons of 24-bit $\Delta\Sigma$ A/D Converter                                               | 484 |

|        | 17.1.1  | I/O pins                                                                                 | 487 |

|        | 17.1.2  | Pre-amplifier                                                                            | 487 |

|        | 17.1.3  | $\Delta\Sigma$ A/D converter                                                             | 487 |

|        | 17.1.4  | Reference voltage generator                                                              | 488 |

|        | 17.1.5  | Phase adjustment circuits (PHCn)                                                         | 488 |

|        | 17.1.6  | Digital filter (DF)                                                                      | 488 |

|        | 17.1.7  | Zero-cross detection                                                                     | 488 |

|        | 17.1.8  | High-pass filter (HPF)                                                                   | 488 |

| 17.2   | Registe | ers                                                                                      | 489 |

|        | 17.2.1  | $\Delta\Sigma$ A/D converter mode register (DSADMR)                                      | 490 |

|        | 17.2.2  | $\Delta\Sigma$ A/D converter gain control register 0 (DSADGCR0)                          | 492 |

|        | 17.2.3  | $\Delta\Sigma$ A/D converter gain control register 1 (DSADGCR1)                          | 493 |

|        | 17.2.4  | $\Delta\Sigma$ A/D converter HPF control register (DSADHPFCR)                            | 494 |

|        | 17.2.5  | $\Delta\Sigma$ A/D converter interrupt control register (DSADICR)                        | 495 |

|        | 17.2.6  | $\Delta\Sigma$ A/D converter interrupt clear register (DSADICLR)                         | 498 |

|        | 17.2.7  | $\Delta\Sigma$ A/D converter interrupt status register (DSADISR)                         | 499 |

|        | 17.2.8  | $\Delta\Sigma$ A/D converter phase control register n (DSADPHCRn) (n = 0, 1, 2, 3)       | 500 |

|        | 17.2.9  | $\Delta\Sigma$ A/D converter conversion result register n (DSADCRnL, DSADCRnM, DSADCRnH) |     |

|        |         | (n = 0, 1, 2, 3)                                                                         | 501 |

|        | 17.2.10 | $\Delta\Sigma$ A/D converter conversion result register n (DSADCRn) (n = 0, 1, 2, 3)     | 503 |

|        | 17.2.11 | Peripheral enable register 1 (PER1)                                                      | 504 |

|        | 17.2.12 | Peripheral reset control register 1 (PRR1)                                               | 505 |

|        | 17.2.13 | Peripheral clock control register (PCKC)                                                 | 506 |

| 17.3   | Operat  | ion                                                                                      | 507 |

|        | 17.3.1  | Operation of 24-bit $\Delta\Sigma$ A/D converter                                         | 508 |

|        | 17.3.2  | Procedure for switching from normal operation mode to neutral missing mode               | 510 |

|        | 17.3.3  | Interrupt operation                                                                      |     |

|        |         | 17.3.3.1 Zero-cross detection interrupt operation                                        |     |

|        | 1704    | 17.3.3.2 $\Delta\Sigma$ A/D conversion end interrupt operation                           |     |

| 47 4   | 17.3.4  | Operation in standby state                                                               |     |

| 17.4   | notes ( | on Using 24-Bit $\Delta\Sigma$ A/D Converter                                             | 514 |

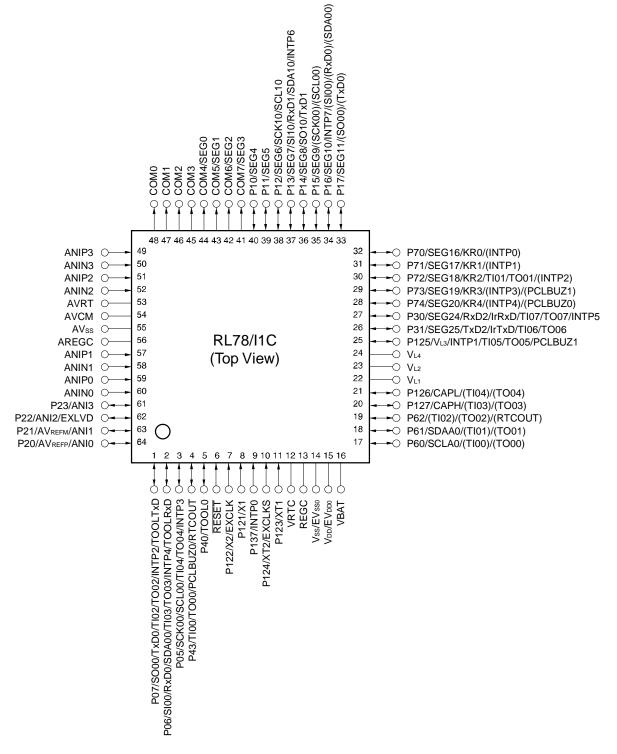

### 1.3 Pin Configuration (Top View)

#### 1.3.1 64-pin products

<R> • 64-pin plastic LFQFP (10 × 10 mm, 0.5 mm pitch)

Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

Remarks 1. For pin identification, see 1.4 Pin Identification.

2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR0). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR0).

(3/3)

|         | Item                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64-                                                                                                                      | -pin                              |                  |                    | 80-pin      |             | 100         | (3/3)<br>)-pin |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|--------------------|-------------|-------------|-------------|----------------|

| <r></r> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R5F10NLEDFB                                                                                                              | R5F10NLGDFB                       | R5F10            | NMEDFB             | R5F10NMGDFB | R5F10NMJDFB | R5F10NPGDFB | R5F10NPJDFB    |

|         | Key interrupt input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          | 5                                 | 5 8              |                    |             |             |             |                |

|         | AES circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Cipher modes of operation: GCM/ECB/CBC                                                                                   |                                   |                  |                    |             |             |             |                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Encryption key length: 128/192/256-bit                                                                                   |                                   |                  |                    |             |             |             |                |

|         | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | et       MCU       • Reset by RESET pin         • Internal reset by watchdog timer       • Internal reset by power-on-reset of internal VDD <sup>Note 1</sup> power supply         • Internal reset by voltage detector of internal VDD <sup>Note 1</sup> power supply       • Internal reset by voltage detector of internal VDD <sup>Note 1</sup> power supply         • Internal reset by illegal instruction execution <sup>Note 2</sup> • Internal reset by RAM parity error         • Internal reset by illegal-memory access       • Internal reset by illegal-memory access |                                                                                                                          |                                   |                  |                    |             |             |             |                |

| <r></r> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RTC circuit                                                                                                              | t reset by RTC                    | Powe             | r-on-rese          | et          |             |             |                |

|         | Power-on-reset circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Internal VDD<br>Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul><li>Power-on-r</li><li>Power-dow</li></ul>                                                                           | reset: 1.51 \<br>vn-reset: 1.50 \ | / (TYP<br>/ (TYP | ,                  |             |             |             |                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VRTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul><li> RTC Powe</li><li> RTC Powe</li></ul>                                                                            | r-on-reset:<br>r-down-reset:      |                  | V (TYP.<br>V (TYP. | ,           |             |             |                |

|         | Voltage detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Internal VDD<br>Note 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>Rising edge: 1.77 V to 4.06 V (13 stages)</li> <li>Falling edge: 1.73 V to 3.98 V (13 stages)</li> </ul>        |                                   |                  |                    |             |             |             |                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Vdd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>Rising edge: 2.54 V to 3.78 V (6 stages)</li> <li>Falling edge: 2.47 V to 3.71 V (6 stages)</li> </ul>          |                                   |                  |                    |             |             |             |                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VBAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>Rising edge: 2.12 V to 2.74 V (7 stages)</li> <li>Falling edge: 2.06 V to 2.68 V (7 stages)</li> </ul>          |                                   |                  |                    |             |             |             |                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VRTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Rising edge                                                                                                              | e: 2.22 V to 2.8                  | 84 V (4          | 4 stages)          | )           |             |             |                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EXLVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>Falling edge: 2.16 V to 2.78 V (4 stages)</li> <li>Rising edge: 1.33 V</li> <li>Falling edge: 1.28 V</li> </ul> |                                   |                  |                    |             |             |             |                |

|         | Battery backup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Palling edg     Vpp/VBAT                                                                                                 | Je. 1.20 V                        |                  |                    |             |             |             |                |

|         | $\frac{\Delta\Sigma}{\Delta D} = \frac{1}{2} \frac{1}{2}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |                                   |                  |                    |             |             |             |                |

|         | RTC VRTC (independent power supply)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |                                   |                  |                    |             |             |             |                |