#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I²C, IrDA, LINbus, UART/USART                                              |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 68                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 6x10b, 4x24b                                                                |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10npjdfb-50 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | 3.2.4                                                                                                                        | Special function registers (SFRs)                                                                                                                        | 64                                    |

|--------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|        | 3.2.5                                                                                                                        | Extended special function registers (2nd SFRs: 2nd Special Function Registers)                                                                           | 69                                    |

| 3.3    | Instruc                                                                                                                      | ction Address Addressing                                                                                                                                 | 81                                    |

|        | 3.3.1                                                                                                                        | Relative addressing                                                                                                                                      | 81                                    |

|        | 3.3.2                                                                                                                        | Immediate addressing                                                                                                                                     | 81                                    |

|        | 3.3.3                                                                                                                        | Table indirect addressing                                                                                                                                | 82                                    |

|        | 3.3.4                                                                                                                        | Register direct addressing                                                                                                                               | 82                                    |

| 3.4    | Addres                                                                                                                       | ssing for Processing Data Addresses                                                                                                                      | 83                                    |

|        | 3.4.1                                                                                                                        | Implied addressing                                                                                                                                       | 83                                    |

|        | 3.4.2                                                                                                                        | Register addressing                                                                                                                                      | 83                                    |

|        | 3.4.3                                                                                                                        | Direct addressing                                                                                                                                        | 84                                    |

|        | 3.4.4                                                                                                                        | Short direct addressing                                                                                                                                  | 85                                    |

|        | 3.4.5                                                                                                                        | SFR addressing                                                                                                                                           | 86                                    |

|        | 3.4.6                                                                                                                        | Register indirect addressing                                                                                                                             | 87                                    |

|        | 3.4.7                                                                                                                        | Based addressing                                                                                                                                         | 88                                    |

|        | 3.4.8                                                                                                                        | Based indexed addressing                                                                                                                                 | 92                                    |

|        | 3.4.9                                                                                                                        | Stack addressing                                                                                                                                         | 93                                    |

|        |                                                                                                                              |                                                                                                                                                          |                                       |

| CHAPTE | R4PC                                                                                                                         | DRT FUNCTIONS                                                                                                                                            | 97                                    |

| 4.1    | Port F                                                                                                                       | unctions                                                                                                                                                 | 97                                    |

| 4.2    | Port C                                                                                                                       | onfiguration                                                                                                                                             | 97                                    |

|        | 4.2.1                                                                                                                        | Port 0                                                                                                                                                   | 98                                    |

|        | 4.2.2                                                                                                                        | Port 1                                                                                                                                                   | 98                                    |

|        | 4.2.3                                                                                                                        | Port 2                                                                                                                                                   | 99                                    |

|        |                                                                                                                              | Port 3                                                                                                                                                   | 99                                    |

|        | 4.2.4                                                                                                                        | POIL 5                                                                                                                                                   |                                       |

|        | 4.2.4<br>4.2.5                                                                                                               | Port 4                                                                                                                                                   |                                       |

|        |                                                                                                                              |                                                                                                                                                          | 99                                    |

|        | 4.2.5                                                                                                                        | Port 4                                                                                                                                                   | 99<br>100                             |

|        | 4.2.5<br>4.2.6                                                                                                               | Port 4<br>Port 5                                                                                                                                         | 99<br>100<br>100                      |

|        | 4.2.5<br>4.2.6<br>4.2.7                                                                                                      | Port 4<br>Port 5<br>Port 6                                                                                                                               | 99<br>100<br>100<br>100               |

|        | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8                                                                                             | Port 4<br>Port 5<br>Port 6<br>Port 7                                                                                                                     | 99<br>100<br>100<br>100<br>100        |

|        | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9                                                                                    | Port 4<br>Port 5<br>Port 6<br>Port 7<br>Port 8                                                                                                           | 99<br>100<br>100<br>100<br>100<br>101 |

|        | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10                                                                          | Port 4                                                                                                                                                   | 99<br>100<br>100<br>100<br>101<br>101 |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12                                                      | Port 4                                                                                                                                                   |                                       |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12                                                      | Port 4                                                                                                                                                   |                                       |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12<br><b>Regist</b>                                     | Port 4         Port 5         Port 6         Port 7         Port 8         Port 12         Port 13         Port 15         ers Controlling Port Function |                                       |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12<br><b>Regist</b><br>4.3.1                            | Port 4                                                                                                                                                   |                                       |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12<br><b>Regist</b><br>4.3.1<br>4.3.2                   | Port 4                                                                                                                                                   |                                       |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12<br><b>Regist</b><br>4.3.1<br>4.3.2<br>4.3.3          | Port 4                                                                                                                                                   |                                       |

| 4.3    | 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12<br><b>Regist</b><br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4 | Port 4         Port 5         Port 6         Port 7         Port 8         Port 12         Port 13         Port 15         ers Controlling Port Function |                                       |

# CHAPTER 3 CPU ARCHITECTURE

# 3.1 Memory Space

Products in the RL78/I1C can access a 1 MB address space. Figures 3-1 and 3-3 show the memory maps.

| Address | Special Function Register (SFR) Name                   | Sym   | ıbol | R/W | Manip        | After Reset  |              |                       |

|---------|--------------------------------------------------------|-------|------|-----|--------------|--------------|--------------|-----------------------|

|         |                                                        |       |      |     | 1-bit        | 8-bit        | 16-bit       |                       |

| FFF90H  | 12-bit interval timer control register                 | ITMC  |      | R/W | _            | _            | $\checkmark$ | 0FFFH                 |

| FFF91H  |                                                        |       |      |     |              |              |              |                       |

| FFFA0H  | Clock operation mode control register                  | CMC   |      | R/W | _            | $\checkmark$ | -            | 00H <sup>Note 1</sup> |

| FFFA1H  | Clock operation status control register                | CSC   |      | R/W | $\checkmark$ | $\checkmark$ | -            | C0H <sup>Note 1</sup> |

| FFFA2H  | Oscillation stabilization time counter status register | OSTC  |      | R   | $\checkmark$ | $\checkmark$ | -            | 00H                   |

| FFFA3H  | Oscillation stabilization time select register         | OSTS  |      | R/W | Ι            | $\checkmark$ | -            | 07H                   |

| FFFA4H  | System clock control register                          | СКС   |      | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                   |

| FFFA5H  | Clock output select register 0                         | CKS0  |      | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                   |

| FFFA6H  | Clock output select register 1                         | CKS1  |      | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                   |

| FFFA7H  | Subsystem clock select resister                        | CKSEL | -    | R/W | $\checkmark$ | $\checkmark$ | -            | 00H                   |

| FFFA8H  | Reset control flag register                            | RESF  |      | R   | _            | $\checkmark$ | -            | Undefined             |

|         |                                                        |       |      |     |              |              |              | Note 2                |

| FFFA9H  | Voltage detection register                             | LVIM  |      | R/W | $\checkmark$ | $\checkmark$ | I            | 00H <sup>Note 2</sup> |

| FFFAAH  | Voltage detection level register                       | LVIS  |      | R/W | $\checkmark$ | $\checkmark$ | -            | 00H/01H/              |

|         |                                                        |       |      |     |              |              |              | 81H <sup>Note 2</sup> |

| FFFABH  | Watchdog timer enable register                         | WDTE  |      | R/W | Ι            | $\checkmark$ | -            | 1AH/9AH               |

|         |                                                        |       |      |     |              |              |              | Note 3                |

| FFFACH  | CRC input register                                     | CRCIN |      | R/W | _            | $\checkmark$ | -            | 00H                   |

| FFFD0H  | Interrupt request flag register 2L                     | IF2L  | IF2  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 00H                   |

| FFFD1H  | Interrupt request flag register 2H                     | IF2H  |      | R/W | $\checkmark$ | $\checkmark$ |              | 00H                   |

| FFFD2H  | Interrupt request flag register 3L                     | IF3L  | IF3  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | 00H                   |

| FFFD4H  | Interrupt mask flag register 2L                        | MK2L  | MK2  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | FFH                   |

| FFFD5H  | Interrupt mask flag register 2H                        | MK2H  |      | R/W | $\checkmark$ | $\checkmark$ |              | FFH                   |

| FFFD6H  | Interrupt mask flag register 3L                        | MK3L  | MK3  | R/W | $\checkmark$ | $\checkmark$ | $\checkmark$ | FFH                   |

Table 3-5. SFR List (3/4)

Notes 1. This register is reset only by a power-on reset.

2. The reset values of the registers vary depending on the reset source as shown below.

| Registe | Reset Source | RESET Input    | Reset by POR | Reset by<br>Execution of<br>Illegal<br>Instruction | Reset by<br>WDT | Reset by RAM<br>Parity Error | Reset by<br>Illegal-Memory<br>Access | Reset by LVD                         |

|---------|--------------|----------------|--------------|----------------------------------------------------|-----------------|------------------------------|--------------------------------------|--------------------------------------|

| RESF    | TRAP         | Cleared (0)    |              | Set (1) Held                                       |                 |                              |                                      | Held                                 |

|         | WDTRF        |                |              | Held                                               | Set (1)         | Held                         |                                      |                                      |

|         | RPERF        |                |              | Held                                               |                 | Set (1)                      | Held                                 |                                      |

|         | IAWRF        |                |              | Held                                               |                 |                              |                                      |                                      |

|         | LVIRF        |                |              | Held                                               |                 |                              |                                      | Set (1)                              |

| LVIM    | LVISEN       | Cleared (0)    |              |                                                    |                 |                              |                                      | Held                                 |

|         | LVIOMSK      | Held           |              |                                                    |                 |                              |                                      |                                      |

|         | LVIF         |                |              |                                                    |                 |                              |                                      |                                      |

| LVIS    |              | Cleared (00H/0 | 1H/81H)      |                                                    |                 |                              |                                      | Clear<br>(00H/81H) <sup>Note 4</sup> |

3. The reset value of the WDTE register is determined by the setting of the option byte.

**4.** When option byte LVIMDS1, LVIMDS0 = 0, 1: LVD reset is not generated.

|    | Address | Special Function Register (SFR) Name    | Sym   | lodr | R/W                   | Manip        | ulable Bit   | After Reset  |                           |

|----|---------|-----------------------------------------|-------|------|-----------------------|--------------|--------------|--------------|---------------------------|

|    |         |                                         |       |      |                       | 1-bit        | 8-bit        | 16-bit       |                           |

| <> | F0154H  | Serial mode register 12                 | SMR12 |      | R/W <sup>Note 1</sup> | _            | _            | $\checkmark$ | 0020H/0000H <sup>№</sup>  |

|    | F0155H  |                                         |       |      |                       |              |              |              |                           |

| <> | F0156H  | Serial mode register 13                 | SMR13 |      | R/W <sup>Note 1</sup> | -            | _            | $\checkmark$ | 0020H/0000H <sup>№</sup>  |

|    | F0157H  |                                         |       |      |                       |              |              |              |                           |

|    | F0158H  | Serial communication operation setting  | SCR10 |      | R/W                   | -            | -            | $\checkmark$ | 0087H                     |

|    | F0159H  | register 10                             |       |      |                       |              |              |              |                           |

|    | F015AH  | Serial communication operation setting  | SCR11 |      | R/W                   | -            | -            | $\checkmark$ | 0087H                     |

|    | F015BH  | register 11                             |       |      |                       |              |              |              |                           |

| ۲> | F015CH  | Serial communication operation setting  | SCR12 |      | R/W <sup>Note 1</sup> | —            | —            | $\checkmark$ | 0087H/0000H <sup>NG</sup> |

|    | F015DH  | register 12                             |       |      |                       |              |              |              |                           |

| ۲> | F015EH  | Serial communication operation setting  | SCR13 |      | R/W <sup>Note 1</sup> | —            | —            | $\checkmark$ | 0087H/0000H <sup>№</sup>  |

|    | F015FH  | register 13                             |       | -    |                       |              |              |              |                           |

|    | F0160H  | Serial channel enable status register 1 | SE1L  | SE1  | R                     | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H                     |

|    | F0161H  |                                         | -     |      |                       | -            | -            |              |                           |

|    | F0162H  | Serial channel start register 1         | SS1L  | SS1  | R/W                   |              | $\checkmark$ | $\checkmark$ | 0000H                     |

|    | F0163H  |                                         | —     |      |                       | -            | -            |              |                           |

|    | F0164H  | Serial channel stop register 1          | ST1L  | ST1  | R/W                   |              | $\checkmark$ | $\checkmark$ | 0000H                     |

|    | F0165H  |                                         | -     |      |                       | -            | -            |              |                           |

|    | F0166H  | Serial clock select register 1          | SPS1L | SPS1 | R/W                   | -            | $\checkmark$ | $\checkmark$ | 0000H                     |

|    | F0167H  |                                         | -     |      |                       | -            | -            |              |                           |

|    | F0168H  | Serial output register 1                | SO1   |      | R/W                   | -            | -            | $\checkmark$ | 0F0FH/0303HN              |

|    | F0169H  |                                         |       |      |                       |              |              |              |                           |

|    | F016AH  | Serial output enable register 1         | SOE1L | SOE1 | R/W                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | 0000H                     |

|    | F016BH  |                                         | -     |      |                       | -            | -            |              |                           |

|    | F0174H  | Serial output level register 1          | SOL1L | SOL1 | R/W                   | -            | $\checkmark$ | $\checkmark$ | 0000H                     |

|    | F0175H  |                                         | -     |      |                       | -            | -            |              |                           |

|    | F0180H  | Timer counter register 00               | TCR00 |      | R                     | -            | -            | $\checkmark$ | FFFFH                     |

|    | F0181H  |                                         |       |      |                       |              |              |              |                           |

|    | F0182H  | Timer counter register 01               | TCR01 |      | R                     | -            | -            | $\checkmark$ | FFFFH                     |

|    | F0183H  |                                         |       |      |                       |              |              |              |                           |

|    | F0184H  | Timer counter register 02               | TCR02 |      | R                     | -            | -            | $\checkmark$ | FFFFH                     |

|    | F0185H  |                                         |       |      |                       |              |              |              |                           |

|    | F0186H  | Timer counter register 03               | TCR03 |      | R                     | -            | -            | $\checkmark$ | FFFFH                     |

|    | F0187H  |                                         |       |      |                       |              |              |              |                           |

|    | F0188H  | Timer counter register 04               | TCR04 |      | R                     | -            | -            | $\checkmark$ | FFFFH                     |

|    | F0189H  |                                         |       |      |                       |              |              |              |                           |

|    | F018AH  | Timer counter register 05               | TCR05 |      | R                     | -            | -            | $\checkmark$ | FFFFH                     |

|    | F018BH  |                                         |       |      |                       |              |              |              |                           |

|    | F018CH  | Timer counter register 06               | TCR06 |      | R                     | -            |              | $\checkmark$ | FFFFH                     |

|    | F018DH  |                                         |       |      |                       |              |              |              |                           |

<R> <R> Notes 1. These registers for R5F10NMG, R5F10NLG, R5F10NME, and R5F10NLE can only be read.

<R>

2. R5F10NPJ, R5F10NMJ, R5F10NPG: 0020H R5F10NMG, R5F10NLG, R5F10NME, R5F10NLE: 0000H 3. R5F10NPJ, R5F10NMJ, R5F10NPG: 0087H

R5F10NMG, R5F10NLG, R5F10NME, R5F10NLE: 0000H

<R> 4. R5F10NPJ, R5F10NMJ, R5F10NPG: 0F0FH R5F10NMG, R5F10NLG, R5F10NME, R5F10NLE: 0303H

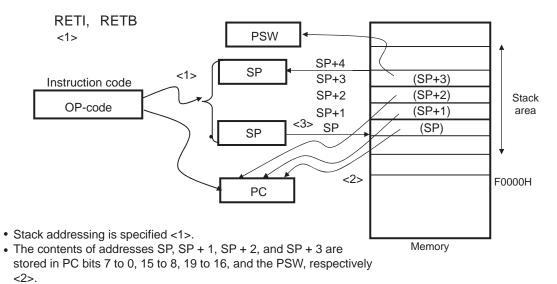

Figure 3-39. Example of RETI, RETB

• The value of SP <3> is increased by four.

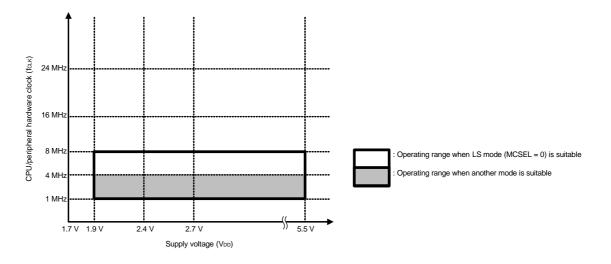

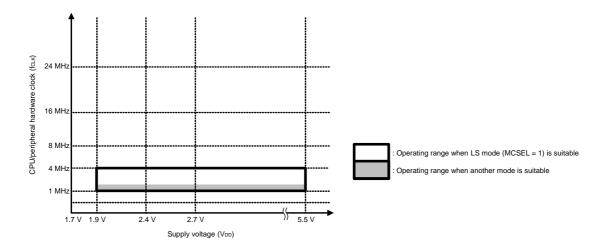

# 5.5.2 Details of LS (low-speed main) mode

LS (low-speed main) mode supports both CPU processing capacity and operating voltage performance, suitable for applications that require low-power consumption at 1 to 8 MHz.

LS mode can be operated immediately after a reset release. Also, this mode can be entered from HS (high-speed main) mode, LV (low-voltage main) mode, or LP (low-power main) mode. When entering from HS mode to LS mode, make sure that the operating frequency is 1 MHz  $\leq$  fcLK  $\leq$  8 MHz.

In LS mode, low-power consumption can be set by the MCSEL bit in the regulator mode control register (PMMC). When setting low-power consumption, set the MCSEL bit to 1 while the operating frequency is 1 MHz  $\leq$  fcLK  $\leq$  4 MHz.

The suitable operating range in LS mode is when the supply voltage is  $1.9 \text{ V} \le \text{VDD} \le 5.5 \text{ V}$  and the operating frequency is  $4 \text{ MHz} < \text{fcL} \text{K} \le 8 \text{ MHz}$  if MCSEL = 0, and when the supply voltage is  $1.9 \text{ V} \le \text{VDD} \le 5.5 \text{ V}$  and the operating frequency is  $1 \text{ MHz} < \text{fcL} \text{K} \le 4 \text{ MHz}$  if MCSEL = 1.

Figure 5 - 8 Operating Range in LS Mode (MCSEL = 0)

Figure 5 - 9 Operating Range in LS Mode (MCSEL = 1)

Caution When entering another flash operation mode, make sure that MCSEL = 0.

| Address:                                                      | F00FAH                                                                                                                                                                        | After reset: 00                               | H R/W                                                                                                                                                                          |                |                  |                  |        |         |  |  |  |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|--------|---------|--|--|--|--|--|

| Symbol                                                        | 7                                                                                                                                                                             | <6>                                           | 5                                                                                                                                                                              | 4              | <3>              | 2                | 1      | <0>     |  |  |  |  |  |

| PER1                                                          | 0                                                                                                                                                                             | FMCEN                                         | 0                                                                                                                                                                              | 0              | DTCEN            | 0                | 0      | DSADCEN |  |  |  |  |  |

| [                                                             | FMCEN                                                                                                                                                                         |                                               | Control                                                                                                                                                                        | of frequency n | neasurement cir  | cuit input clock | supply |         |  |  |  |  |  |

|                                                               | 0                                                                                                                                                                             | SFR used by                                   | ops input clock supply.<br>SFR used by the frequency measurement circuit cannot be written. The read value is 00H.<br>The frequency measurement circuit is in the reset state. |                |                  |                  |        |         |  |  |  |  |  |

|                                                               | 1       Enables input clock supply.         • SFR used by the frequency measurement circuit can be read and written.                                                          |                                               |                                                                                                                                                                                |                |                  |                  |        |         |  |  |  |  |  |

| Γ                                                             | DTCEN                                                                                                                                                                         |                                               |                                                                                                                                                                                | Control c      | f DTC input cloc | k supply         |        |         |  |  |  |  |  |

|                                                               | 0                                                                                                                                                                             | Stops input clo<br>• DTC cannot               |                                                                                                                                                                                |                |                  |                  |        |         |  |  |  |  |  |

|                                                               | 1                                                                                                                                                                             | Enables input <ul> <li>DTC can run</li> </ul> | ,                                                                                                                                                                              |                |                  |                  |        |         |  |  |  |  |  |

| DSADCEN Control of 24-bit ΔΣ A/D converter input clock supply |                                                                                                                                                                               |                                               |                                                                                                                                                                                |                |                  |                  |        |         |  |  |  |  |  |

|                                                               | O         Stops input clock supply.           0         • SFR used by the 24-bit ΔΣ A/D converter cannot be written. The read value is 00H. However, is not initialized. Note |                                               |                                                                                                                                                                                |                |                  |                  |        |         |  |  |  |  |  |

## Figure 6 - 11 Format of Peripheral enable register 1 (PER1)

Note To initialize the 24-bit  $\Delta\Sigma$  A/D converter and the SFR used by the 24-bit  $\Delta\Sigma$  A/D converter, use bit 0 (DSADRES) of PRR1.

• SFR used by the 24-bit  $\Delta\Sigma$  A/D converter can be read and written.

Caution 1. Be sure to clear the following bits to 0.

Enables input clock supply.

Bits 1, 2, 4, 5 and 7

1

Caution 2. Do not change the target bit in the PER1 register while operation of each peripheral function is enabled. Change the setting specified by PER1 while operation of each peripheral function assigned to PER1 is stopped.

#### 9.2 **Register Descriptions**

When writing to or reading from RTC registers, do so in accordance with section 9.6.5, Notes when writing to and reading from registers.

If the value in an RTC register after a reset is given as undefined in the list, it is not initialized by a reset. When RTC enters the reset state or a low power consumption state during counting operations (i.e. while the RCR2.START bit is 1), the year, month, day of the week, date, hours, minutes, seconds, and 64-Hz counters continue to operate. Note that a reset generated during writing to or updating of a register might destroy the register value. In addition, do not allow the chip to enter STOP mode immediately after setting any of these registers. For details, refer to section 9.6.4, Transitions to low power consumption modes after setting registers.

<R>

#### 9.2.1 Peripheral enable register 2 (PER2)

This register is used to enable or disable supplying the clock to the peripheral hardware. Clock supply to the hardware that is not used is also stopped so as to decrease the power consumption and noise.

To manipulate of the registers of the independent power supply real-time clock, set (1) the bit 0 (VRTCEN). Other than time when read/write accessing, clear (0) the bit 0 (VRTCEN).

The PER2 register can be set by a 1-bit or an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

| Address: F00 | FDH A  | After reset: 00H | R/W |   |   |       |   |        |

|--------------|--------|------------------|-----|---|---|-------|---|--------|

| Symbol       | <7>    | <6>              | 5   | 4 | 3 | <2>   | 1 | <0>    |

| PER2         | TMKAEN | OSDCEN           | 0   | 0 | 0 | MACEN | 0 | VRTCEN |

Figure 9 - 2 Format of Peripheral enable register 2 (PER2)

| Symbol | <7>                                                               | <6>    | 5 | 4 | 3 | <2>   | 1 | <0>    |  |

|--------|-------------------------------------------------------------------|--------|---|---|---|-------|---|--------|--|

| PER2   | TMKAEN                                                            | OSDCEN | 0 | 0 | 0 | MACEN | 0 | VRTCEN |  |

| [      | VRTCEN Control of independent power supply RTC input clock supply |        |   |   |   |       |   |        |  |

| VRTCE   | N Control of independent power supply RTC input clock supply                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0       | Stops input clock supply.         • SFR used by the independent power supply RTC cannot be written. The read value is 00H. The sub clock (fsx) clock can drive counting by the independent power supply RTC.         Enables input clock supply.         • SFR used by the independent power supply RTC can be read and written. |  |  |  |  |  |

| 1       |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Note 1. | If the battery back-up function isn't used, leak current may be generated via the VRTC pin when the Vod pin power supply voltage is less than 1.9 V. Therefore, set the VRTCEN bit to 0 except during reading or writing of the SFRs of the independent power supply RTC.                                                        |  |  |  |  |  |

| Note 2. | If the battery back-up function is used, leak current may be generated via the VRTC pin when the VBAT pin power supply voltage is less than 1.9 V. Therefore, set the VRTCEN bit to 0 except during reading or writing of the SFRs of the independent power supply RTC.                                                          |  |  |  |  |  |

| Note 3. | When the power of the VRTC pin is not supplied, set the VRTCEN bit to 0.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Caution | Be sure to clear the following bits to 0.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

Bits 1 and 3 to 5

# 9.2.31 RTC status register (RSR)

RSR is a flag register of the periodic interrupt, carry, and alarm. This register is a common function with the calendar count mode and the binary count mode.

Each flag is set to 1 when the prescaler or the clock counter matches each interrupt setting condition. The prescaler, clock counter, and the setting register of each interrupt are not reset, so each flag may be set before it is read. This register is set to 00h by an RTC software reset.

# Figure 9 - 49 Format of RTC Status Register (RSR)

| mbol                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                                                           | 5                 | 4                  | 3                | 2               | 1  | 0  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------------------|-----------------|----|----|--|--|--|--|

| RSR                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                           | 0                 | 0                  | 0                | PF              | CF | AF |  |  |  |  |

| Γ                     | PF                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |                   | Pe                 | riodic interrupt | flag            |    |    |  |  |  |  |

| ľ                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | No interrupt o                                                                                                              | occurs at a perio | od that is set wit | h RCR1.PES[      | 3:0] bits       |    |    |  |  |  |  |

|                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | Interrupt occu                                                                                                              | irs at a period t | hat is set with R  | CR1.PES[3:0]     | bits Note 2     |    |    |  |  |  |  |

| Du<br><0<br>• (<br><5 | During PF =<br><clear cond<br="">• 0 is writte<br/><set condit<="" td=""><td>n to the PF flag.<br/>ion&gt;</td><td>nterrupt occurs.</td><td></td><td></td><td>R1.PES[3:0] bit</td><td>5.</td><td></td></set></clear>                                                                                                                                                                                                    | n to the PF flag.<br>ion>                                                                                                   | nterrupt occurs.  |                    |                  | R1.PES[3:0] bit | 5. |    |  |  |  |  |

|                       | Interrupt occurs at a period that is set with RCR1.PES[3:0] bits.  CF Carry flag                                                                                                                                                                                                                                                                                                                                        |                                                                                                                             |                   |                    |                  |                 |    |    |  |  |  |  |

|                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | Carry flag No carry of second counter/binary counter 0, and no carry of the 64 Hz counter when the 64 Hz counter is reading |                   |                    |                  |                 |    |    |  |  |  |  |

|                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | Carry of second counter/binary counter 0, or carry of the 64 Hz counter when the 64 Hz counter is reading                   |                   |                    |                  |                 |    |    |  |  |  |  |

|                       | <ul> <li>During CF = 1, be sure to read again because the value which is read from the count register is not guaranteed.</li> <li><clear conditions=""> <ul> <li>0 is written to the CF flag.</li> <li><set condition=""></set></li> <li>Carry of second counter/binary counter 0, or carry of the 64 Hz counter when the 64 Hz counter is reading</li> <li>1 is written to the CF flag.</li> </ul> </clear></li> </ul> |                                                                                                                             |                   |                    |                  |                 |    |    |  |  |  |  |

| Γ                     | AF                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                             |                   |                    | Alarm flag       |                 |    |    |  |  |  |  |

| F                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                       | The counter of                                                                                                              | loes not match    | the alarm regis    | ters             |                 |    |    |  |  |  |  |

| F                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | The counter r                                                                                                               | natches the ala   | rm registers Not   | e 2              |                 |    |    |  |  |  |  |

|                       | <ul> <li>This bit is set to 1 when the counter matches the alarm time set with the alarm registers (calender count mode: RSECAR, RMINAR, RHRAR, RWKAR, RDAYAR, RMONAR, RYRAR; binary count mode: BCNT0AR, BCNT1AR, BCNT2AR, BCNT3AR) (only registers that the ENB bit is set to 1).</li> <li><clear conditions=""></clear></li> <li>0 is written to the AF flag.</li> <li><set condition=""></set></li> </ul>           |                                                                                                                             |                   |                    |                  |                 |    |    |  |  |  |  |

|                       | <ul> <li>The counter matches the alarm registers (only registers that the ENB bit is set to 1).</li> </ul>                                                                                                                                                                                                                                                                                                              |                                                                                                                             |                   |                    |                  |                 |    |    |  |  |  |  |

**Note 2.** Writing "1" to this bit is invalid.

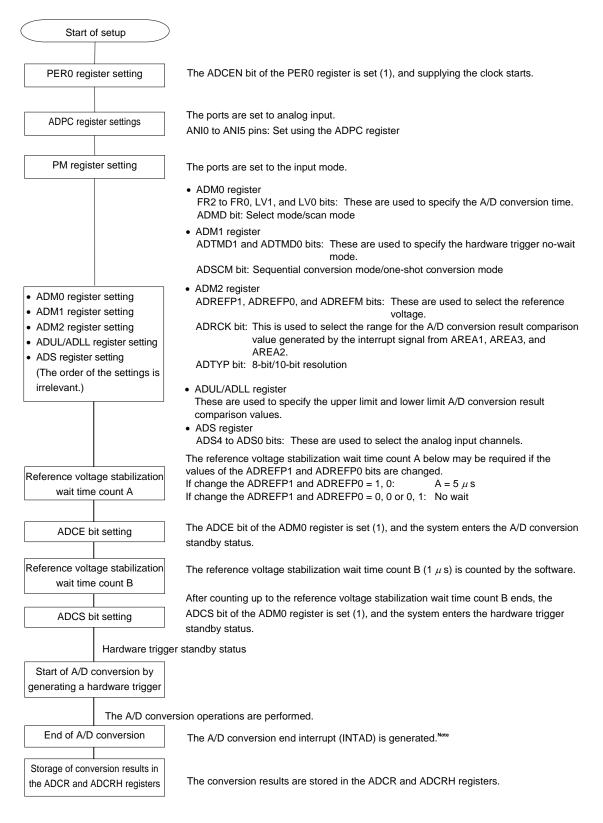

#### 15.7.2 Setting up hardware trigger no-wait mode

#### Figure 15-31. Setting up Hardware Trigger No-wait Mode

**Note** Depending on the settings of the ADRCK bit and ADUL/ADLL register, there is a possibility of no interrupt signal being generated. In this case, the results are not stored in the ADCR, ADCRH registers.

RENESAS

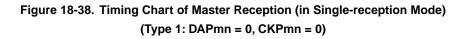

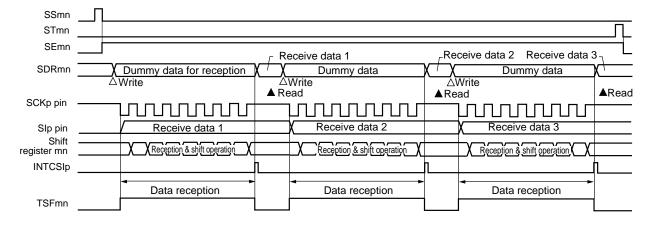

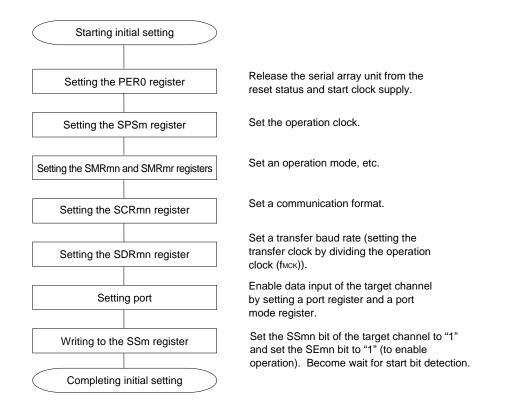

# (3) Processing flow (in single-reception mode)

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0, 2), p: CSI number (p = 00, 10, 30), mn = 00, 02, 12

# (2) Operation procedure

#### Figure 18-86. Initial Setting Procedure for UART Reception

# Caution Set the RXEmn bit of SCRmn register to 1, and then be sure to set SSmn to 1 after 4 or more fmck clocks have elapsed.

#### Figure 18-87. Procedure for Stopping UART Reception

#### 19.5.16 Communication operations

The following shows three operation procedures with the flowchart.

#### (1) Master operation in single master system

The flowchart when using the RL78/I1C as the master in a single master system is shown below.

This flowchart is broadly divided into the initial settings and communication processing. Execute the initial settings at startup. If communication with the slave is required, prepare the communication and then execute communication processing.

#### (2) Master operation in multimaster system

In the  $l^2C$  bus multimaster system, whether the bus is released or used cannot be judged by the  $l^2C$  bus specifications when the bus takes part in a communication. Here, when data and clock are at a high level for a certain period (1 frame), the RL78/I1C takes part in a communication with bus released state.

This flowchart is broadly divided into the initial settings, communication waiting, and communication processing. The processing when the RL78/I1C looses in arbitration and is specified as the slave is omitted here, and only the processing as the master is shown. Execute the initial settings at startup to take part in a communication. Then, wait for the communication request as the master or wait for the specification as the slave. The actual communication is performed in the communication processing, and it supports the transmission/reception with the slave and the arbitration with other masters.

#### (3) Slave operation

An example of when the RL78/I1C is used as the I<sup>2</sup>C bus slave is shown below.

When used as the slave, operation is started by an interrupt. Execute the initial settings at startup, then wait for the INTIICAn interrupt occurrence (communication waiting). When an INTIICAn interrupt occurs, the communication status is judged and its result is passed as a flag over to the main processing. By checking the flags, necessary communication processing is performed.

Remark n = 0

## 20.2.2 Peripheral reset control register 0 (PRR0)

The PRR0 register is used to control resetting of the on-chip peripheral modules.

Each bit in this register controls resetting and release of the reset state of the corresponding on-chip peripheral module. To reset the IrDA, be sure to set bit 6 (IRDARES) to 1.

The PRR0 register can be set by a 1-bit or an 8-bit memory manipulation instruction.

Reset signal generation clears the PRR0 register to 00H.

#### Figure 20-3. Format of Peripheral Reset Control Register 0 (PRR0)

| Address: F | 00F1H | After reset: 00H | H R/W  |                 |         |         |   |         |

|------------|-------|------------------|--------|-----------------|---------|---------|---|---------|

| Symbol     | 7     | <6>              | <5>    | <4>             | <3>     | <2>     | 1 | <0>     |

| PRR0       | 0     | IRDARES          | ADCRES | <b>IICA0RES</b> | SAU1RES | SAU0RES | 0 | TAU0RES |

|            |       |                  |        |                 |         |         |   |         |

| IRDARES | IRDARES Control resetting of the IrDA   |  |  |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|--|--|

| 0       | Releases the IrDA from the reset state. |  |  |  |  |  |  |

| 1       | The IrDA is in the reset state.         |  |  |  |  |  |  |

# 20.4 Usage Notes on IrDA

- (1) The IrDA function cannot be used to transition to SNOOZE via IrRxD reception.

- (2) The input of IrDA operating clock can be disabled/enabled with the peripheral enable register. Initially, register access is disabled because clock input is disabled. Enable IrDA operating clock input with the peripheral enable register before setting the register.

- (3) During HALT mode, the IrDA function continues to run.

- (4) The use of SAU initialization function (SS bit= 1) is prohibited during IrDA communication.

- (5) The IRCR register bits IRRXINV, IRTXINV, and IRCKS[2:0] can be set only when IRE bit is 0.

# 21.1 Functions of LCD Controller/Driver

The functions of the LCD controller/driver in the RL78/I1C microcontrollers are as follows.

- (1) Waveform A or B selectable

- (2) The LCD driver voltage generator can switch internal voltage boosting method, capacitor split method, and external resistance division method.

- (3) Automatic output of segment and common signals based on automatic display data register read

- (4) The reference voltage to be generated when operating the voltage boost circuit can be selected from 16 steps (contrast adjustment).

- (5) LCD blinking is available

Table 21-2 lists the maximum number of pixels that can be displayed in each display mode.

#### Table 21-2. Maximum Number of Pixels (1/3)

#### (a) 64-pin products

| Drive Waveform for | LCD Driver Voltage  | Bias Mode | Number of Time | Maximum Number of Pixels                   |

|--------------------|---------------------|-----------|----------------|--------------------------------------------|

| LCD Driver         | Generator           |           | Slices         |                                            |

| Waveform A         | External resistance |           | Static         | 19 (19 segment signals, 1 common signal)   |

|                    | division            | 1/2       | 2              | 38 (19 segment signals, 2 common signals)  |

|                    |                     |           | 3              | 57 (19 segment signals, 3 common signals)  |

|                    |                     | 1/3       | 3              |                                            |

|                    |                     |           | 4              | 76 (19 segment signals, 4 common signals)  |

|                    |                     |           | 6              | 102 (17 segment signals, 6 common signals) |

|                    |                     |           | 8              | 120 (15 segment signals, 8 common signals) |

|                    |                     | 1/4       | 8              |                                            |

|                    | Internal voltage    | 1/3       | 3              | 57 (19 segment signals, 3 common signals)  |

|                    | boosting            |           | 4              | 76 (19 segment signals, 4 common signals)  |

|                    |                     |           | 6              | 102 (17 segment signals, 6 common signals) |

|                    |                     |           | 8              | 120 (15 segment signals, 8 common signals) |

|                    |                     | 1/4       | 6              | 102 (17 segment signals, 6 common signals) |

|                    |                     |           | 8              | 120 (15 segment signals, 8 common signals) |

|                    | Capacitor split     | 1/3       | 3              | 57 (19 segment signals, 3 common signals)  |

|                    |                     |           | 4              | 76 (19 segment signals, 4 common signals)  |

|                    |                     |           | 6              | 102 (17 segment signals, 6 common signals) |

|                    |                     |           | 8              | 120 (15 segment signals, 8 common signals) |

| Waveform B         | External resistance | 1/3       | 3              | 57 (19 segment signals, 3 common signals)  |

|                    | division, internal  |           | 4              | 76 (19 segment signals, 4 common signals)  |

|                    | voltage boosting    |           | 6              | 102 (17 segment signals, 6 common signals) |

|                    |                     |           | 8              | 120 (15 segment signals, 8 common signals) |

|                    |                     | 1/4       | 8              |                                            |

|                    | Capacitor split     | 1/3       | 3              | 57 (19 segment signals, 3 common signals)  |

|                    |                     |           | 4              | 76 (19 segment signals, 4 common signals)  |

|                    |                     |           | 6              | 102 (17 segment signals, 6 common signals) |

|                    |                     |           | 8              | 120 (15 segment signals, 8 common signals) |

| Interrupt<br>Type | Defa                               |                         | Interrupt Source                                                           | Internal/<br>External | Vector<br>Table | Basic Co<br>Type <sup>nore ₂</sup>         | 100-pin      | 80-pin       | 64-pin       |

|-------------------|------------------------------------|-------------------------|----------------------------------------------------------------------------|-----------------------|-----------------|--------------------------------------------|--------------|--------------|--------------|

| 1990              | Default Priority <sup>Note 1</sup> | Name                    | Trigger                                                                    | External              | Address         | Basic Configuration<br>Type <sup>№®2</sup> | pin          | in           | 5            |

| Maskable          | 0                                  | INTWDTI                 | Watchdog timer interval <sup>Note 3</sup><br>(75% of overflow time+1/2fı∟) | Internal              | 0004H           | (A)                                        | V            | $\checkmark$ | $\checkmark$ |

|                   | 1                                  | INTLVI                  | Voltage detection <sup>Note 4</sup>                                        |                       | 0006H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 2                                  | INTP0 <sup>Note 5</sup> | Pin input edge detection                                                   | External              | 0008H           | (B)                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 3                                  | INTP1                   |                                                                            |                       | 000AH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 4                                  | INTP2                   |                                                                            |                       | 000CH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 5                                  | INTP3                   |                                                                            |                       | 000EH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 6                                  | INTP4                   |                                                                            |                       | 0010H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 7                                  | INTP5                   |                                                                            |                       | 0012H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 8                                  | INTST2                  | UART2 transmission transfer end or buffer empty interrupt                  | Internal              | 0014H           | (A)                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 9                                  | INTSR2                  | UART2 reception transfer end                                               |                       | 0016H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 10                                 | INTSRE2                 | UART2 reception communication error occurrence                             |                       | 0018H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 11                                 | INTCR                   | End of high-speed on-chip oscillator clock                                 |                       | 001AH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    |                         | frequency correction                                                       |                       |                 |                                            |              |              |              |

|                   | 12                                 | INTAES                  | AES encryption/decryption end                                              |                       | 001CH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    | INTAESF                 | AES encryption/decryption end of first block                               |                       |                 |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 13                                 | INTST0/                 | UART0 transmission transfer end or buffer                                  |                       | 001EH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    | INTCSI00/               | empty interrupt/CSI00 transfer end or buffer                               |                       |                 |                                            |              |              |              |

|                   |                                    | INTIIC00                | empty interrupt/IIC00 transfer end                                         |                       |                 |                                            |              |              |              |

|                   | 14                                 | INTIICA0                | End of IICA0 communication                                                 |                       | 0020H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 15                                 | INTSR0                  | UART0 reception transfer end                                               |                       | 0022H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 16                                 | INTSRE0                 | UART0 reception communication error                                        |                       | 0024H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    |                         | occurrence                                                                 |                       |                 |                                            |              |              |              |

|                   |                                    | INTTM01H                | End of timer channel 01 count or capture (at                               |                       |                 |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    |                         | higher 8-bit timer operation)                                              |                       |                 |                                            |              |              |              |

|                   | 17                                 | INTST1/                 | UART1 transmission transfer end or buffer                                  |                       | 0026H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    | INTCSI10/               | empty interrupt/CSI10 transfer end or buffer                               |                       |                 |                                            |              |              |              |

|                   |                                    | INTIIC10                | empty interrupt/IIC10 transfer end                                         |                       |                 |                                            |              |              |              |

|                   | 18                                 | INTSR1                  | UART1 reception transfer end                                               |                       | 0028H           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   | 19                                 | INTSRE1                 | UART1 reception communication error                                        |                       | 002AH           |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    |                         | occurrence                                                                 |                       |                 |                                            |              |              |              |

|                   |                                    | INTTM03H                | End of timer channel 03 count or capture (at                               |                       |                 |                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|                   |                                    |                         | higher 8-bit timer operation)                                              |                       |                 |                                            |              |              |              |

Table 24-1. Interrupt Source List (1/4)

**Notes 1.** The default priority determines the sequence of interrupts if two or more maskable interrupts occur simultaneously. Zero indicates the highest priority and 42 indicates the lowest priority.

- 2. Basic configuration types (A) to (C) correspond to (A) to (C) in Figure 24-1.

- 3. When bit 7 (WDTINT) of the option byte (000C0H) is set to 1.

- 4. When bit 7 (LVIMD) of the voltage detection level register (LVIS) is cleared to 0.

- 5. The input buffer power supply of P137 pins is connected to internal VDD. For PIOR04 = 0, interrupts can be accepted even when a battery backup function is used and power is supplied from the VBAT pin.

<R>

# 39.4 Operations of 32-bit Multiply-accumulator

#### 39.4.1 Basic operation

The register configuration shows as follow when multiplication or multiply-accumulation is executed.