Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VFDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (2x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1501-e-mc |

## 1.0 DEVICE OVERVIEW

The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pinout descriptions are shown in Table 1-2.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                             | PIC12(L)F1501 | PIC16(L)F1503 | PIC16(L)F1507 | PIC16(L)F1508 | PIC16(L)F1509 |   |

|------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---|

| Analog-to-Digital Converter (A                                         | ADC)          | •             | •             | •             | •             | • |

| Complementary Wave General                                             | ator (CWG)    | •             | •             | •             | •             | • |

| Digital-to-Analog Converter (I                                         | DAC)          | •             | •             |               | •             | • |

| Enhanced Universal<br>Synchronous/Asynchronous<br>Transmitter (EUSART) | Receiver/     |               |               |               | •             | • |

| Fixed Voltage Reference (FV                                            | R)            | •             | •             | •             | •             | • |

| Numerically Controlled Oscill                                          | ator (NCO)    | •             | •             | •             | •             | • |

| Temperature Indicator                                                  |               | •             | •             | •             | •             | • |

| Comparators                                                            | Comparators   |               |               |               |               |   |

|                                                                        | C1            | •             | •             |               | •             | • |

|                                                                        | C2            |               | •             |               | •             | • |

| Configurable Logic Cell (CLC                                           | ;)            |               |               |               |               |   |

|                                                                        | CLC1          | •             | •             | •             | •             | • |

|                                                                        | CLC2          | •             | •             | •             | •             | • |

|                                                                        | CLC3          |               |               |               | •             | • |

|                                                                        | CLC4          |               |               |               | •             | • |

| Master Synchronous Serial P                                            | orts          |               |               |               |               |   |

|                                                                        | MSSP1         |               | •             |               | •             | • |

| PWM Modules                                                            |               |               |               |               |               |   |

|                                                                        | PWM1          | •             | •             | •             | •             | • |

|                                                                        | PWM2          |               |               |               | •             | • |

|                                                                        | PWM3          |               |               |               |               | • |

|                                                                        | •             | •             | •             | •             | •             |   |

| Timers                                                                 | ,             |               | ı             | ı             |               |   |

|                                                                        | Timer0        | •             | •             | •             | •             | • |

|                                                                        | Timer1        | •             | •             | •             | •             | • |

|                                                                        | Timer2        | •             | •             | •             | •             | • |

TABLE 1-2: PIC12(L)F1501 PINOUT DESCRIPTION (CONTINUED)

| Name                                   | Function | Input<br>Type | Output<br>Type | Description                                           |

|----------------------------------------|----------|---------------|----------------|-------------------------------------------------------|

| RA5/CLKIN/T1CKI/CWG1A <sup>(1)</sup> / | RA5      | TTL           | CMOS           | General purpose I/O.                                  |

| NCO1 <sup>(1)</sup> /NCO1CLK/CLC1IN1/  | CLKIN    | CMOS          | _              | External clock input (EC mode).                       |

| CLC2/PWM4                              | T1CKI    | ST            | _              | Timer1 clock input.                                   |

|                                        | CWG1A    | _             | CMOS           | CWG complementary output.                             |

|                                        | NCO1     | ST            | _              | Numerically Controlled Oscillator output.             |

|                                        | NCO1CLK  | ST            | _              | Numerically Controlled Oscillator Clock source input. |

|                                        | CLC1IN1  | ST            | _              | Configurable Logic Cell source input.                 |

|                                        | CLC2     | _             | CMOS           | Configurable Logic Cell source output.                |

|                                        | PWM4     |               | CMOS           | Pulse Width Module source output.                     |

| VDD                                    | VDD      | Power         | _              | Positive supply.                                      |

| Vss                                    | Vss      | Power         | _              | Ground reference.                                     |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

$TTL = TTL \ compatible \ input \ ST = Schmitt \ Trigger \ input \ with \ CMOS \ levels \ I^2C^{\intercal M} = Schmitt \ Trigger \ input \ with \ I^2C$

HV = High Voltage XTAL = Crystal levels

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

TABLE 3-3: PIC12(L)F1501 MEMORY MAP (CONTINUED)

|      | Bank 30                      |                                    | Bank 31                      |  |

|------|------------------------------|------------------------------------|------------------------------|--|

| F0Ch | _                            | F8Ch                               |                              |  |

| F0Dh | _                            |                                    |                              |  |

| F0Eh | _                            |                                    | Unimplemented<br>Read as '0' |  |

| F0Fh | CLCDATA                      |                                    | Reau as 0                    |  |

| F10h | CLC1CON                      | FE3h                               |                              |  |

| F11h | CLC1POL                      |                                    | STATUS_SHAD                  |  |

| F12h | CLC1SEL0                     | FE4h                               | WREG SHAD                    |  |

| F13h | CLC1SEL1                     | FE5h                               | BSR_SHAD                     |  |

| F14h | CLC1GLS0                     | FE6h                               |                              |  |

| F15h | CLC1GLS1                     | FE7h                               | PCLATH_SHAD                  |  |

| F16h | CLC1GLS2                     | FE8h                               | FSR0L_SHAD                   |  |

| F17h | CLC1GLS3                     | FE9h                               | FSR0H_SHAD                   |  |

| F18h | CLC2CON                      | FEAh                               | FSR1L_SHAD                   |  |

| F19h | CLC2POL                      | FEBh                               | FSR1H_SHAD                   |  |

| F1Ah | CLC2SEL0                     | FECh                               | _                            |  |

| F1Bh | CLC2SEL1                     | FEDh                               | STKPTR                       |  |

| F1Ch | CLC2GLS0                     | FEEh                               | TOSL                         |  |

| F1Dh | CLC2GLS1                     | FEFh                               | TOSH                         |  |

| F1Eh | CLC2GLS2                     |                                    |                              |  |

| F1Fh | CLC2GLS3                     |                                    |                              |  |

| F20h | Unimplemented<br>Read as '0' |                                    |                              |  |

| F6Fh |                              |                                    |                              |  |

| ıd:  |                              | ata memory locations, read as '0'. |                              |  |

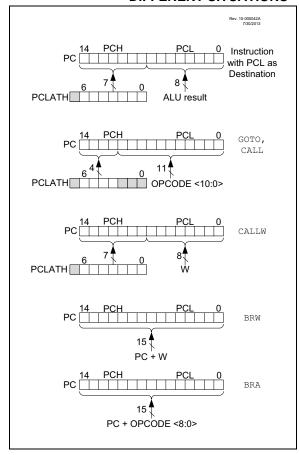

#### 3.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, "Implementing a Table Read" (DS00556).

#### 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection  $(\overline{CP} = 0)^{(1)}$ , disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the  $\overline{\mathsf{CP}}$  bit of Configuration Words.

### 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

#### 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

Note: If the user wants to modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, new data and retained data can be written into the write latches to reprogram the row of Flash program memory. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

TABLE 10-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC12(L)F1501 | 16                   | 16                          |

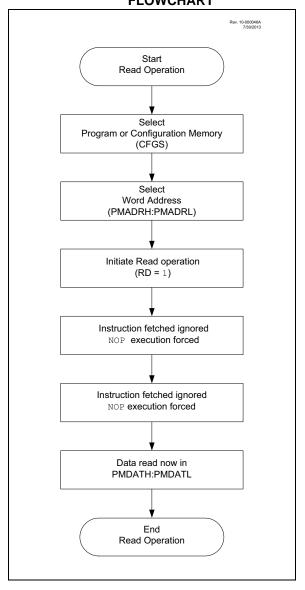

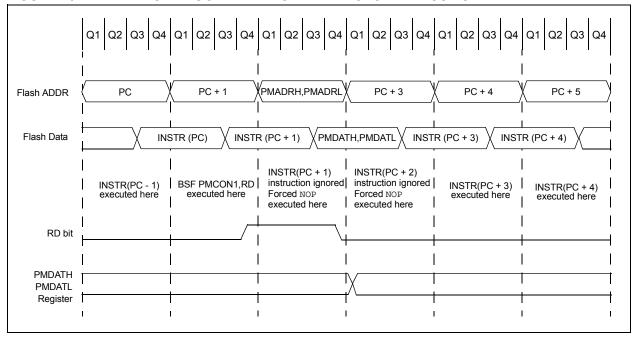

## 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

Note:

The two instructions following a program memory read are required to be NOPs. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

FIGURE 10-1: FLASH PROGRAM MEMORY READ FLOWCHART

### **EXAMPLE 10-1: FLASH PROGRAM MEMORY READ**

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

PROG_ADDR_LO

MOVLW

MOVWF

PMADRL

; Store LSB of address

PROG_ADDR_HI

MOVLW

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-2)

NOP

; Ignored (Figure 10-2)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

; Get MSB of word

PMDATH,W

MOVF

MOVWF

PROG_DATA_HI

; Store in user location

```

#### **EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY (16 WRITE LATCHES)**

```

; This write routine assumes the following:

; 1. 32 bytes of data are loaded, starting at the address in DATA_ADDR

; 2. Each word of data to be written is made up of two adjacent bytes in DATA_ADDR,

; stored in little endian format

; 3. A valid starting address (the least significant bits = 00000) is loaded in ADDRH:ADDRL

; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

PMADRH

; Bank 3

; Load initial address

MOVF

ADDRH, W

MOVWF

PMADRH

MOVF

ADDRL,W

MOVWF

PMADRL

MOVLW

LOW DATA_ADDR ; Load initial data address

MOVWF

FSR0L

HIGH DATA_ADDR ; Load initial data address

MOVLW

MOVWF

FSR0H

BCF

PMCON1,CFGS

; Not configuration space

BSF

PMCON1, WREN

; Enable writes

; Only Load Write Latches

BSF

PMCON1,LWLO

LOOP

MOVIW

FSR0++

; Load first data byte into lower

MOVWF

PMDATL

MOVIW

FSR0++

; Load second data byte into upper

MOVWF

HTAGMG

MOVF

PMADRL,W

; Check if lower bits of address are '00000'

XORLW

0x0F

; Check if we're on the last of 16 addresses

ANDI-W

0x0F

BTFSC

STATUS.Z

; Exit if last of 16 words,

GOTO

START_WRITE

MOVLW

55h

; Start of required write sequence:

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin write

; NOP instructions are forced as processor

NOP

; loads program memory write latches

NOP

; Still loading latches Increment address

INCF

PMADRL,F

GOTO

LOOP

; Write next latches

START_WRITE

PMCON1,LWLO

; No more loading latches - Actually start Flash program

; memory write

MOVLW

55h

; Start of required write sequence:

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

PMCON1,WR

; Set WR bit to begin write

BSF

NOP

; NOP instructions are forced as processor writes

; all the program memory write latches simultaneously

NOP

; to program memory.

; After NOPs, the processor

; stalls until the self-write process in complete

; after write processor continues with 3rd instruction

BCF

PMCON1, WREN

; Disable writes

BSF

INTCON, GIE

; Enable interrupts

```

## TABLE 13-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral | Conditions                                               | Description                                                        |

|------------|----------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 010 and<br>IRCF<3:0> = 000x                  | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                          | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                            | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                            | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC12F1501 devices, when VREGPM = 1 and not in Sleep | The device runs off of the Low-Power Regulator when in Sleep mode. |

### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR>1:0> |       | ADFVI | R<1:0> | 107              |

**Legend:** Shaded cells are unused by the temperature indicator module.

### REGISTER 15-3: ADCON2: ADC CONTROL REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0              | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|----------------------|---------|-----|-----|-----|-------|

|         | TRIGSEL | <3:0> <sup>(1)</sup> |         | _   | _   | _   | _     |

| bit 7   |         |                      |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 TRIGSEL<3:0>: Auto-Conversion Trigger Selection bits<sup>(1)</sup>

0000 = No auto-conversion trigger selected

0001 = Reserved

0010 = Reserved

$0011 = Timer0 - T0_overflow<sup>(2)</sup>$

$0100 = Timer1 - T1_overflow<sup>(2)</sup>$

0101 = Timer2 - T2\_match

0110 = Comparator C1 - C1OUT\_sync

0111 = Reserved

1000 = CLC1 - LC1\_out

1001 = CLC2 - LC2\_out

1010 = Reserved

1011 = Reserved

1100 = Reserved

1101 = Reserved

1110 = Reserved

1111 = Reserved

bit 3-0 **Unimplemented:** Read as '0'

**Note 1:** This is a rising edge sensitive input for all sources.

2: Signal also sets its corresponding interrupt flag.

#### 22.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 22-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

TABLE 22-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 22-5)

- Gate 2: CLCxGLS1 (Register 22-6)

- Gate 3: CLCxGLS2 (Register 22-7)

- Gate 4: CLCxGLS3 (Register 22-8)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 22-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 22.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- · S-R Latch

- · D Flip-Flop with Set and Reset

- · D Flip-Flop with Reset

- · J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in Figure 22-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 22.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

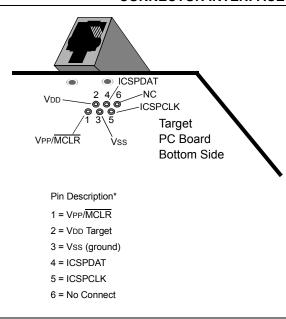

# 25.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>TM</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>TM</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification" (DS41573).

## 25.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

## 25.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC® Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

### 25.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP™ header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 25-1.

FIGURE 25-1: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 25-2.

#### 26.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 26-3 lists the instructions recognized by the MPASM $^{TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 26.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                  |

| W     | Working register (accumulator)                                                                                                                                        |

| b     | Bit address within an 8-bit file register                                                                                                                             |

| k     | Literal field, constant data or label                                                                                                                                 |

| х     | Don't care location (= 0 or 1).  The assembler will generate code with x = 0.  It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                         |

| n     | FSR or INDF number. (0-1)                                                                                                                                             |

| mm    | Pre-post increment-decrement mode selection                                                                                                                           |

TABLE 26-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |  |  |  |

|-------|-----------------|--|--|--|

| PC    | Program Counter |  |  |  |

| TO    | Time-Out bit    |  |  |  |

| С     | Carry bit       |  |  |  |

| DC    | Digit Carry bit |  |  |  |

| Z     | Zero bit        |  |  |  |

| PD    | Power-Down bit  |  |  |  |

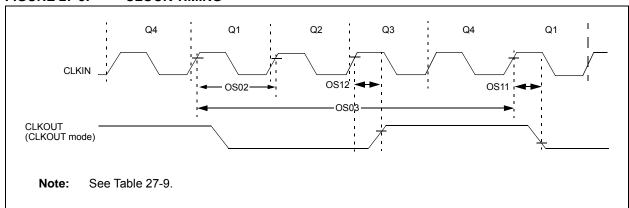

#### FIGURE 27-5: CLOCK TIMING

#### TABLE 27-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

| Param. | Sym. | Characteristic                          | Min. | Тур† | Max. | Units   | Conditions           |

|--------|------|-----------------------------------------|------|------|------|---------|----------------------|

|        | F000 | Estamal CLKIN Francisco (1)             | DC   |      | 0.5  | N 41.1— | Estamal Clask (ECL)  |

| OS01   | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | _    | 0.5  | MHz     | External Clock (ECL) |

|        |      |                                         | DC   | _    | 4    | MHz     | External Clock (ECM) |

|        |      |                                         | DC   | _    | 20   | MHz     | External Clock (ECH) |

| OS02   | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | _    | ∞    | ns      | External Clock (EC)  |

| OS03   | TCY  | Instruction Cycle Time <sup>(1)</sup>   | 200  | Tcy  | DC   | ns      | Tcy = 4/Fosc         |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

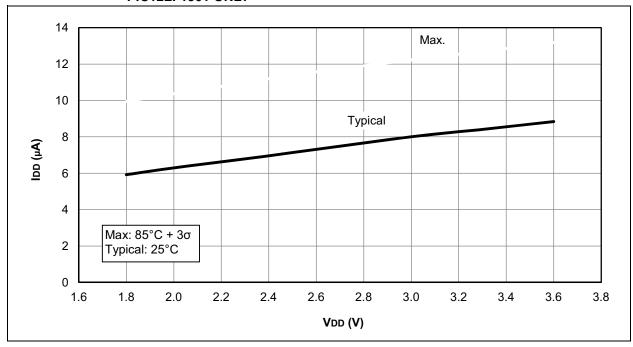

FIGURE 28-1: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 32 kHz, PIC12LF1501 ONLY

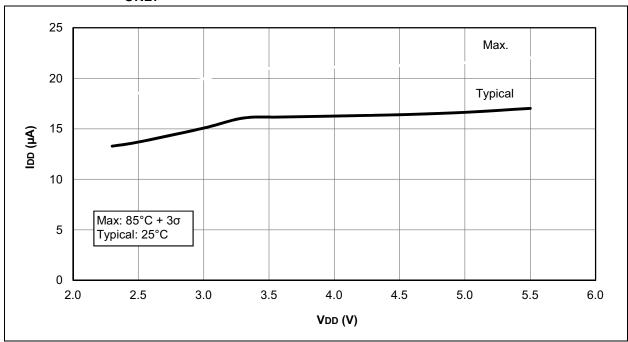

FIGURE 28-2: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 32 kHz, PIC12F1501 ONLY

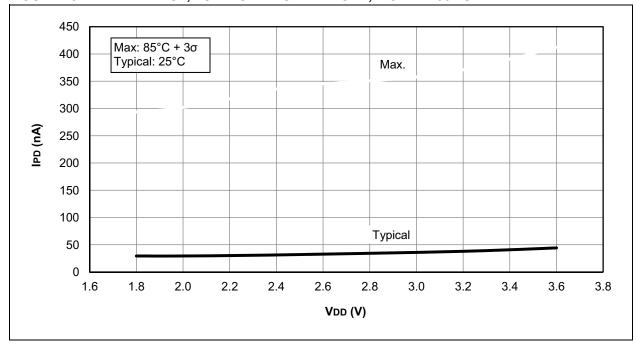

FIGURE 28-21: IPD BASE, LOW-POWER SLEEP MODE, PIC12LF1501 ONLY

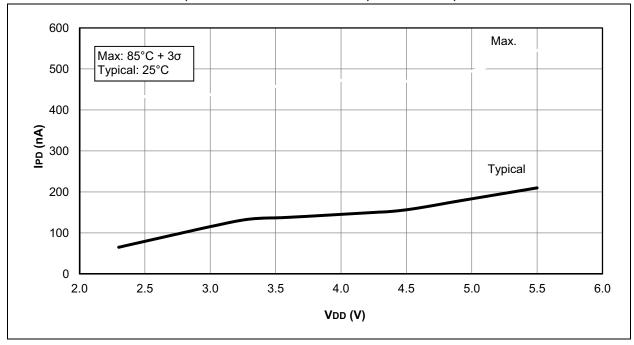

FIGURE 28-22: IPD BASE, LOW-POWER SLEEP MODE, VREGPM = 1, PIC12F1501 ONLY

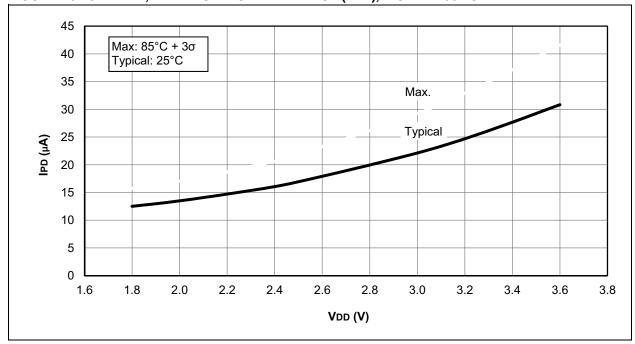

FIGURE 28-25: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC12LF1501 ONLY

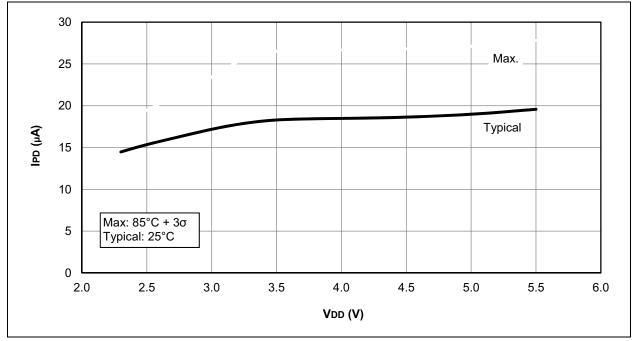

FIGURE 28-26: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC12F1501 ONLY

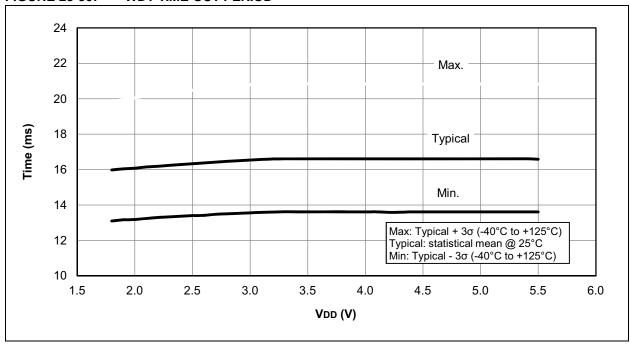

FIGURE 28-50: WDT TIME-OUT PERIOD