# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1501-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC12(L)F1501

| Address            | Name                   | Bit 7        | Bit 6         | Bit 5         | Bit 4         | Bit 3          | Bit 2          | Bit 1   | Bit 0    | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|------------------------|--------------|---------------|---------------|---------------|----------------|----------------|---------|----------|----------------------|---------------------------------|

| Bank 2             |                        |              |               |               |               |                |                |         |          |                      |                                 |

| 10Ch               | LATA                   | _            | _             | LATA5         | LATA4         | _              | LATA2          | LATA1   | LATA0    | xx -xxx              | uu -uuu                         |

| 10Dh<br>to<br>110h | _                      | Unimplemen   | Unimplemented |               |               |                |                |         |          |                      |                                 |

| 111h               | CM1CON0                | C10N         | C10UT         | C10E          | C1POL         | -              | C1SP           | C1HYS   | C1SYNC   | 0000 -100            | 0000 -100                       |

| 112h<br>to<br>114h | _                      | Unimplemen   | ted           |               |               |                |                | _       |          | _                    | _                               |

| 115h               | CMOUT                  | —            | _             | —             | —             | _              | _              | _       | MC10UT   | 00                   | 00                              |

| 116h               | BORCON                 | SBOREN       | BORFS         | —             | —             |                | —              | —       | BORRDY   | 10q                  | uuu                             |

| 117h               | FVRCON                 | FVREN        | FVRRDY        | TSEN          | TSRNG         | CDAFV          | ′R<1:0>        | ADFV    | ′R<1:0>  | 0q00 0000            | 0q00 0000                       |

| 118h               | DAC1CON0               | DACEN        |               | DACOE1        | DACOE2        |                | DACPSS         | —       |          | 0-00 -0              | 0-00 -0                         |

| 119h               | DAC1CON1               | _            | _             | _             |               |                | DACR<4:(       | )>      |          | 0 0000               | 0 0000                          |

| 11Ah<br>to<br>11Ch | _                      | Unimplemen   | ted           |               |               |                |                |         |          | -                    | —                               |

| 11Dh               | APFCON                 | CWG1BSEL     | CWGA1SEL      | _             | _             | T1GSEL         | _              | CLC1SEL | NCO1SEL  | 00 0-00              | 00 0-00                         |

| 11Eh               | —                      | Unimplemen   | ted           |               |               |                |                |         |          | _                    | _                               |

| 11Fh               | —                      | Unimplemen   | ted           |               |               |                |                |         |          | _                    | _                               |

| Bank 3             | 5                      |              |               |               |               |                |                |         |          |                      |                                 |

| 18Ch               | ANSELA                 | —            |               | —             | ANSA4         |                | ANSA2          | ANSA1   | ANSA0    | 1 -111               | 1 -111                          |

| 18Dh<br>to<br>190h | _                      | Unimplemen   | ted           |               |               |                |                |         |          | _                    | _                               |

| 191h               | PMADRL                 | Flash Progra | m Memory A    | ddress Regis  | ter Low Byte  |                |                |         |          | 0000 0000            | 0000 0000                       |

| 192h               | PMADRH                 | _(2)         | Flash Progra  | m Memory A    | ddress Regis  | ster High Byte | e              |         |          | 1000 0000            | 1000 0000                       |

| 193h               | PMDATL                 | Flash Progra | m Memory R    | ead Data Re   | gister Low By | te             |                |         |          | xxxx xxxx            | uuuu uuuu                       |

| 194h               | PMDATH                 | —            | _             | Flash Progr   | am Memory F   | Read Data Re   | egister High I | Byte    |          | xx xxxx              | uu uuuu                         |

| 195h               | PMCON1                 | _(2)         | CFGS          | LWLO          | FREE          | WRERR          | WREN           | WR      | RD       | 1000 x000            | 1000 q000                       |

| 196h               | PMCON2                 | Flash Progra | m Memory Co   | ontrol Regist | er 2          |                |                |         |          | 0000 0000            | 0000 0000                       |

| 197h               | VREGCON <sup>(1)</sup> | —            | -             | —             | —             | _              | —              | VREGPM  | Reserved | 01                   | 01                              |

| 198h<br>to<br>19Fh | _                      | Unimplemen   | ted           |               |               |                |                |         |          | _                    | _                               |

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-5:**

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC12F1501 only.

PIC12F1501 only.

Unimplemented, read as '1'.

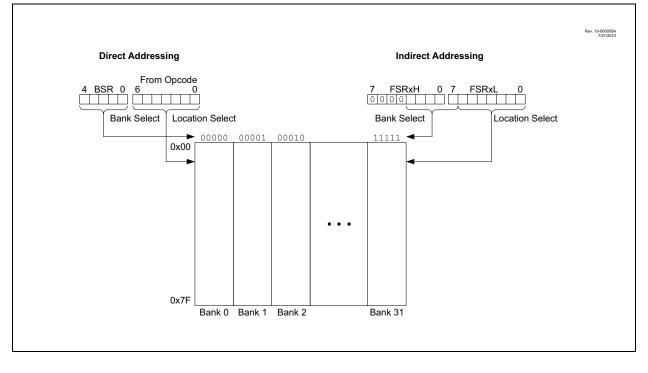

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

## 5.2.2.4 Peripheral Clock Sources

The clock sources described in this chapter and the Timer's are available to different peripherals. Table 5-1 lists the clocks and timers available for each peripheral.

| TABLE 5-1: | PERIPHERAL CLOCK |

|------------|------------------|

|            | SOURCES          |

|      | FOSC | FRC | HFINTOSC | LFINTOSC | TMR0 | TMR1 | TMR2 |

|------|------|-----|----------|----------|------|------|------|

| ADC  | •    | •   |          |          |      |      |      |

| CLC  | •    | •   | •        | •        | •    | •    | •    |

| COMP |      |     |          |          |      | ٠    |      |

| CWG  | ٠    |     | ٠        |          |      |      |      |

| NCO  | ٠    |     | ٠        |          |      |      |      |

| PWM  | ٠    |     |          |          |      |      | •    |

| PWRT |      |     |          | •        |      |      |      |

| TMR0 | ٠    |     |          |          |      |      |      |

| TMR1 | ٠    |     |          | •        |      |      |      |

| TMR2 | ٠    |     |          |          |      |      |      |

| WDT  |      |     |          | •        |      |      |      |

## 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC and 31 kHz LFINTOSC connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register (Register 5-1) select the frequency output of the internal oscillators.

| Note: | Following any Reset, the IRCF<3:0> bits<br>of the OSCCON register are set to '0111'<br>and the frequency selection is set to<br>500 kHz. The user can modify the IRCF |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | bits to select a different frequency.                                                                                                                                 |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

### 5.2.2.6 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-3). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-3 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-2.

Start-up delay specifications are located in Table 27-8, "Oscillator Parameters".

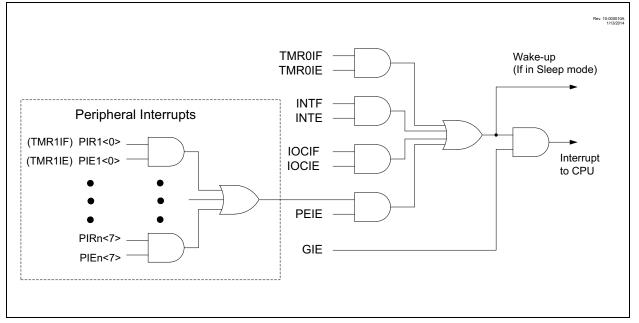

## 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

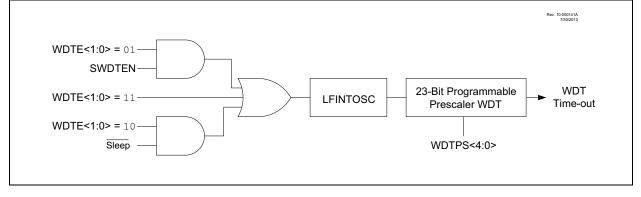

## 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

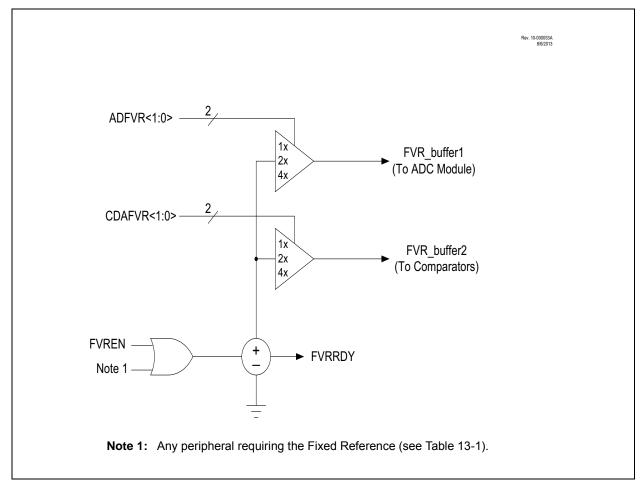

## 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with a nominal output level (VFVR) of 1.024V. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- Comparator positive input

- · Comparator negative input

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

## 13.1 Independent Gain Amplifier

The output of the FVR supplied to the peripherals, (listed above), is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0 "Analog-to-Digital Converter** (ADC) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the comparator modules. Reference **Section 17.0 "Comparator Module"** for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

## 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See the FVR Stabilization Period characterization graph, Figure 28-52.

## FIGURE 13-1: VOLTAGE REFERENCE BLOCK DIAGRAM

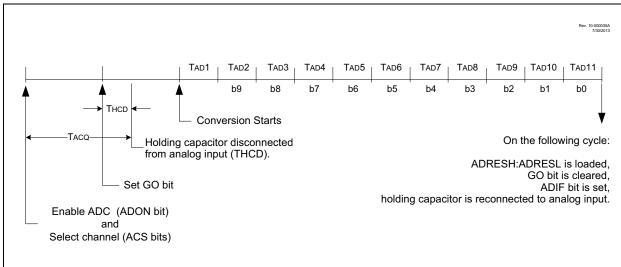

| ADC Clock              | Period (TAD) | Device Frequency (Fosc) |            |            |            |            |  |  |

|------------------------|--------------|-------------------------|------------|------------|------------|------------|--|--|

| ADC<br>Clock<br>Source | ADCS<2:0     | 20 MHz                  | 16 MHz     | 8 MHz      | 4 MHz      | 1 MHz      |  |  |

| Fosc/2                 | 000          | 100 ns                  | 125 ns     | 250 ns     | 500 ns     | 2.0 μs     |  |  |

| Fosc/4                 | 100          | 200 ns                  | 250 ns     | 500 ns     | 1.0 μs     | 4.0 μs     |  |  |

| Fosc/8                 | 001          | 400 ns                  | 500 ns     | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |  |

| Fosc/16                | 101          | 800 ns                  | 1.0 μs     | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |  |

| Fosc/32                | 010          | 1.6 μs                  | 2.0 μs     | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |  |

| Fosc/64                | 110          | 3.2 μs                  | 4.0 μs     | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |  |

| FRC                    | x11          | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |  |

## TABLE 15-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

Legend: Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

#### FIGURE 15-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

| Name   | Bit 7                    | Bit 6  | Bit 5     | Bit 4    | Bit 3 | Bit 2                  | Bit 1   | Bit 0  | Register<br>on Page |

|--------|--------------------------|--------|-----------|----------|-------|------------------------|---------|--------|---------------------|

| ADCON0 | _                        |        |           | CHS<4:0> |       |                        | GO/DONE | ADON   | 116                 |

| ADCON1 | ADFM                     |        | ADCS<2:0> |          | _     | _                      | ADPRE   | F<1:0> | 117                 |

| ADCON2 |                          | TRIGSE | EL<3:0>   |          | -     | —                      | —       | —      | 118                 |

| ADRESH | ADC Result Register High |        |           |          |       |                        |         |        |                     |

| ADRESL | ADC Result Register Low  |        |           |          |       |                        |         |        |                     |

| ANSELA | _                        | _      | -         | ANSA4    | -     | ANSA2                  | ANSA1   | ANSA0  | 99                  |

| INTCON | GIE                      | PEIE   | TMR0IE    | INTE     | IOCIE | TMR0IF                 | INTF    | IOCIF  | 64                  |

| PIE1   | TMR1GIE                  | ADIE   | _         | —        | _     | —                      | TMR2IE  | TMR1IE | 65                  |

| PIR1   | TMR1GIF                  | ADIF   | _         | _        | _     | —                      | TMR2IF  | TMR1IF | 68                  |

| TRISA  | _                        | _      | TRISA5    | TRISA4   | —(1)  | TRISA2                 | TRISA1  | TRISA0 | 98                  |

| FVRCON | FVREN                    | FVRRDY | TSEN      | TSRNG    | CDAFV | CDAFVR<1:0> ADFVR<1:0> |         |        |                     |

TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

Note 1: Unimplemented, read as '1'.

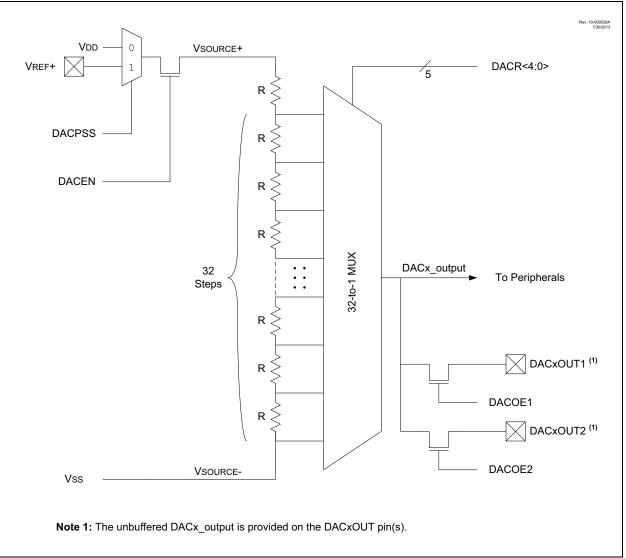

## 16.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The positive input source (VSOURCE+) of the DAC can be connected to:

- External VREF+ pin

- VDD supply voltage

The negative input source (VSOURCE-) of the DAC can be connected to:

Vss

The output of the DAC (DACx\_output) can be selected as a reference voltage to the following:

- Comparator positive input

- · ADC input channel

- DACxOUT1 pin

- DACxOUT2 pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACxCON0 register.

## FIGURE 16-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

| Name     | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2     | Bit 1      | Bit 0    | Register<br>on Page |

|----------|-------|--------|--------|--------|-------|-----------|------------|----------|---------------------|

| ANSELA   | _     | _      | _      | ANSA4  | -     | ANSA2     | ANSA1      | ANSA0    | 99                  |

| CM1CON0  | C10N  | C10UT  | C10E   | C1POL  | _     | C1SP      | C1HYS      | C1SYNC   | 131                 |

| CM1CON1  | C1NTP | C1INTN | C1PCI  | H<1:0> | _     |           | C1NCH<2:0> | <b>,</b> | 132                 |

| CMOUT    | _     |        |        | _      |       |           | _          | MC1OUT   | 132                 |

| DAC1CON0 | DACEN | _      | DACOE1 | DACOE2 | _     | DACPSS    | —          | —        | 126                 |

| DAC1CON1 | _     | _      | _      |        |       | DACR<4:0> |            |          | 126                 |

| FVRCON   | FVREN | FVRRDY | TSEN   | TSRNG  | CDAFV | R<1:0>    | ADFV       | R<1:0>   | 107                 |

| INTCON   | GIE   | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF    | INTF       | IOCIF    | 64                  |

| PIE2     | _     | _      | C1IE   | —      | _     | NCO1IE    | —          | —        | 66                  |

| PIR2     | _     | _      | C1IF   | —      | _     | NCO1IF    | —          | —        | 69                  |

| PORTA    | _     | _      | RA5    | RA4    | RA3   | RA2       | RA1        | RA0      | 98                  |

| LATA     | _     | _      | LATA5  | LATA4  | _     | LATA2     | LATA1      | LATA0    | 99                  |

| TRISA    | _     | _      | TRISA5 | TRISA4 | (1)   | TRISA2    | TRISA1     | TRISA0   | 98                  |

## TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

Note 1: Unimplemented, read as '1'.

## 19.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 19-1 is a block diagram of the Timer1 module.

T1GSS<1:0> Rev. 10-000018E T1GSPM T1G 00 T0 overflow 01 1 T1GVAL C1OUT\_sync 10 D 0 Q Single Pulse 0 Acq. Control Reserved 11 1 Q1 ō D T1GGO/DONE T1GPOL •CK Q Interrupt TMR10N set bit R det TMR1GIF T1GTM TMR1GE set flag bit TMR1IF TMR10N ΕN TMR1<sup>(2)</sup> T1\_overflow Synchronized Clock Input TMR1H TMR1L 0 D O 1 T1CLK **T1SYNC** TMR1CS<1:0> LFINTOSC 11 (1) T1CKI 10 Prescaler Synchronize<sup>(3)</sup> Fosc 1,2,4,8 01 Internal Clock det 00 2 Fosc/4 Fosc/2 T1CKPS<1:0> Internal Clock Internal Sleep Clock Input Note 1: ST Buffer is high speed type when using T1CKI. 2: Timer1 register increments on rising edge. 3: Synchronize does not operate while in Sleep.

## FIGURE 19-1: TIMER1 BLOCK DIAGRAM

## PIC12(L)F1501

| FIGURE 19-6:                     | TIMER1 GATE SINGLE                                             | -PULSE AND TOGGLE COMBINED MODE                                             |

|----------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|

| TMR1GE                           |                                                                |                                                                             |

| T1GP <u>OL</u><br>T1GSP <u>M</u> |                                                                |                                                                             |

| T1GT <u>M</u>                    |                                                                |                                                                             |

| T1GG <u>O/</u><br>DONE           | ← Set by software<br>Counting enabled of<br>rising edge of T10 | Cleared by hardware on<br>falling edge of T1GVAL                            |

| t1g_in                           |                                                                |                                                                             |

| тіскі                            |                                                                |                                                                             |

| T1GV <u>AL</u>                   |                                                                |                                                                             |

| Timer1                           | Ν                                                              | N + 1     N + 2     N + 3     N + 4       Set by hardware on     Cleared by |

| TMR1GIF                          | <ul> <li>Cleared by software</li> </ul>                        | falling edge of T1GVAL                                                      |

## 24.8 Dead-Band Uncertainty

When the rising and falling edges of the input source triggers the dead-band counters, the input may be asynchronous. This will create some uncertainty in the deadband time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 24-1 for more detail.

#### EQUATION 24-1: DEAD-BAND UNCERTAINTY

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

Example:

$$Fcwg\_clock = 16 MHz$$

Therefore:

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

$$= \frac{1}{16 MHz}$$

$$= 62.5 ns$$

## 24.9 Auto-Shutdown Control

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software.

## 24.9.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

#### 24.9.1.1 Software Generated Shutdown

Setting the GxASE bit of the CWGxCON2 register will force the CWG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist as long as the GxASE bit is set.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the next rising edge event. See Figure 24-6.

## 24.9.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Any combination of two input sources can be selected to cause a shutdown condition. The sources are:

- Comparator C1 C1OUT\_async

- CLC2 LC2\_out

- CWG1FLT

Shutdown inputs are selected in the CWGxCON2 register. (Register 24-3).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

## TABLE 27-4: I/O PORTS

| Standard O | perating Condit | ions (unless oth | erwise stated) |

|------------|-----------------|------------------|----------------|

| Param.<br>No. | Sym. | Characteristic                       | Min.            | Тур†     | Max.     | Units | Conditions                                                                 |  |  |  |

|---------------|------|--------------------------------------|-----------------|----------|----------|-------|----------------------------------------------------------------------------|--|--|--|

|               | VIL  | Input Low Voltage                    |                 |          | •        |       | •                                                                          |  |  |  |

|               |      | I/O PORT:                            |                 |          |          |       |                                                                            |  |  |  |

| D030          |      | with TTL buffer                      | —               |          | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D030A         |      |                                      | —               |          | 0.15 VDD | V     | $1.8V \le V\text{DD} \le 4.5V$                                             |  |  |  |

| D032          |      | MCLR                                 | —               |          | 0.2 Vdd  | V     |                                                                            |  |  |  |

|               | VIH  | Input High Voltage                   |                 |          | •        | •     | ·                                                                          |  |  |  |

|               |      | I/O PORT:                            |                 |          |          |       |                                                                            |  |  |  |

| D040          |      | with TTL buffer                      | 2.0             |          | _        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                           |  |  |  |

| D040A         |      |                                      | 0.25 VDD +      |          | —        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |  |  |  |

|               |      |                                      | 0.8             |          |          |       |                                                                            |  |  |  |

| D042          |      | MCLR                                 | 0.8 VDD         | —        | —        | V     |                                                                            |  |  |  |

|               | lı∟  | Input Leakage Current <sup>(1)</sup> |                 |          |          |       |                                                                            |  |  |  |

| D060          |      | I/O Ports                            | —               | ± 5      | ± 125    | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 85°C                    |  |  |  |

|               |      |                                      | —               | ± 5      | ± 1000   | nA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance, 125°C                   |  |  |  |

| D061          |      | MCLR <sup>(2)</sup>                  | —               | ± 50     | ± 200    | nA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 85°C                     |  |  |  |

|               | IPUR | Weak Pull-up Current                 | 1               |          |          |       |                                                                            |  |  |  |

| D070*         |      |                                      | 25              | 100      | 200      | μA    | VDD = 3.3V, VPIN = VSS                                                     |  |  |  |

|               |      |                                      | 25              | 140      | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |  |  |  |

|               | Vol  | Output Low Voltage                   |                 |          | •        | •     | ·                                                                          |  |  |  |

| D080          |      | I/O Ports                            | -               | _        | 0.6      | v     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |  |

|               | Voн  | Output High Voltage                  | 1               |          |          |       |                                                                            |  |  |  |

| D090          |      | I/O Ports                            | VDD - 0.7       | _        | _        | v     | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |  |  |  |

|               |      | Capacitive Loading Specifi           | ications on Out | put Pins |          |       | 1                                                                          |  |  |  |

| D101A*        | CIO  | All I/O pins                         |                 | _        | 50       | pF    |                                                                            |  |  |  |

|               |      |                                      |                 |          | 1        | · · · |                                                                            |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

## PIC12(L)F1501

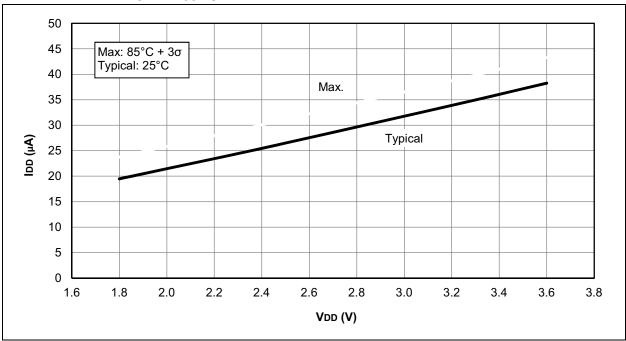

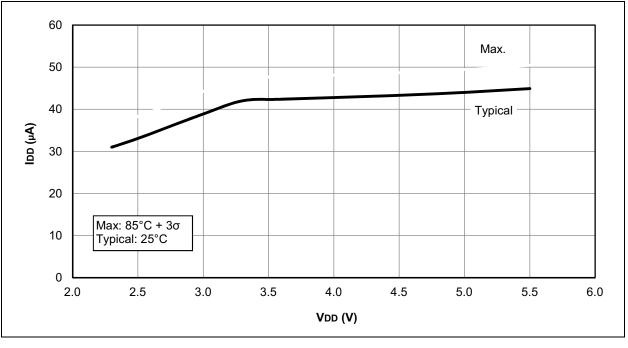

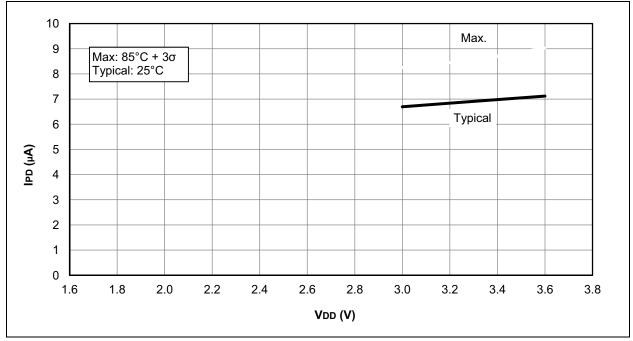

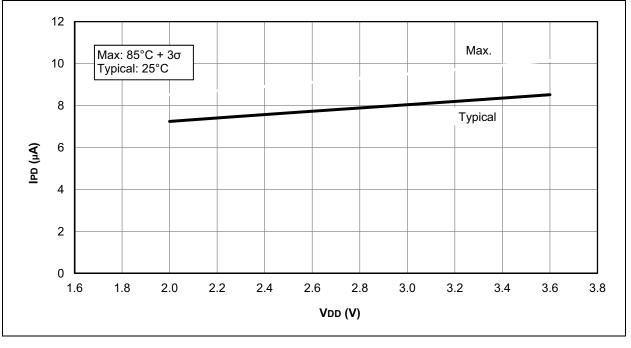

FIGURE 28-3: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 500 kHz, PIC12LF1501 ONLY

FIGURE 28-4: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 500 kHz, PIC12F1501 ONLY

## PIC12(L)F1501

## 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

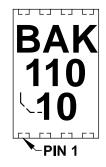

## Package Marking Information (Continued)

8-Lead MSOP (3x3 mm)

8-Lead DFN (2x3x0.9 mm) 8-Lead UDFN (2x3x0.5 mm)

Example

Example

8-Lead DFN (3x3x0.9 mm)

Example

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

Microchip Technology Drawing No. C04-057C Sheet 1 of 2

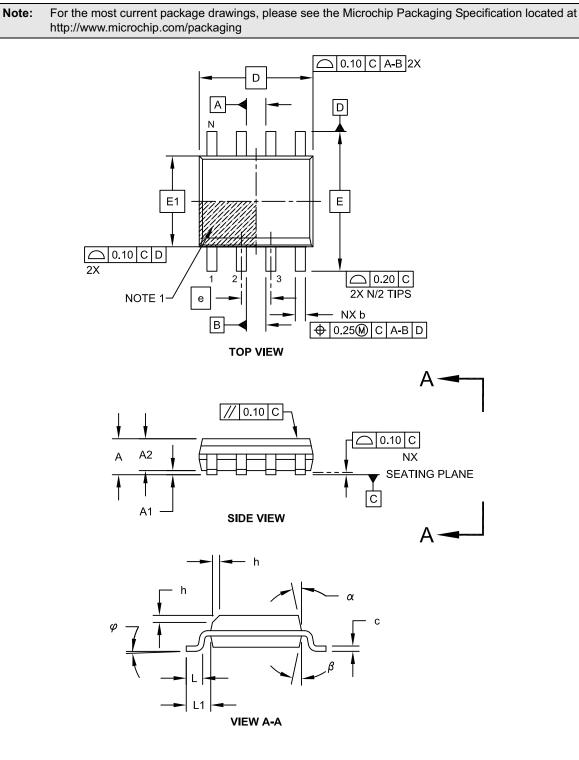

## 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  |            |          |      |  |

|------------------------|--------|------------|----------|------|--|

| Dimension              | Limits | MIN        | NOM      | MAX  |  |

| Number of Pins         | N      |            | 8        |      |  |

| Pitch                  | е      |            | 0.65 BSC |      |  |

| Overall Height         | A      | 0.80       | 0.90     | 1.00 |  |

| Standoff               | A1     | 0.00       | 0.02     | 0.05 |  |

| Contact Thickness      | A3     | 0.20 REF   |          |      |  |

| Overall Length         | D      | D 3.00 BSC |          |      |  |

| Exposed Pad Width      | E2     | 1.34       | -        | 1.60 |  |

| Overall Width          | E      |            | 3.00 BSC |      |  |

| Exposed Pad Length     | D2     | 1.60       | -        | 2.40 |  |

| Contact Width          | b      | 0.25       | 0.30     | 0.35 |  |

| Contact Length         | L      | 0.20       | 0.30     | 0.55 |  |

| Contact-to-Exposed Pad | K      | 0.20       | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

3. Package is saw singulated

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-062C Sheet 2 of 2