Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

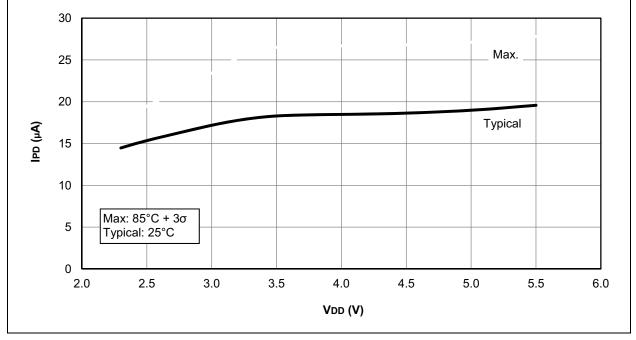

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 8-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1501-i-sn |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<1:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0>

#### TABLE 5-2: OSCILLATOR SWITCHING DELAYS

bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-2.

# 5.3.2 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PPLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

| Switch From      | Oscillator Delay |                              |  |

|------------------|------------------|------------------------------|--|

|                  | LFINTOSC         | 1 cycle of each clock source |  |

| Any clock source | HFINTOSC         | 2 μs (approx.)               |  |

|                  | ECH, ECM, ECL    | 2 cycles                     |  |

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a **SLEEP** instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

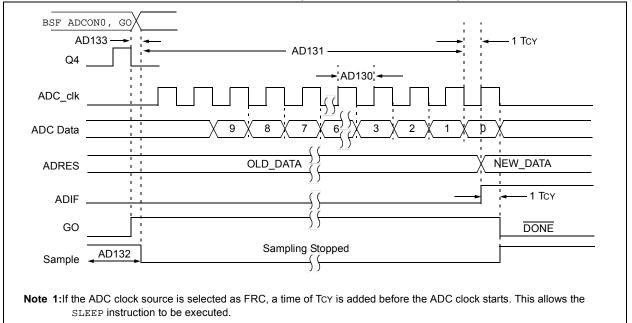

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- 8. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- CWG, NCO and CLC modules using HFINTOSC

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

## 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

#### 17.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 17-2 shows the output state versus input conditions, including polarity control.

TABLE 17-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 17.2.6 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal-Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

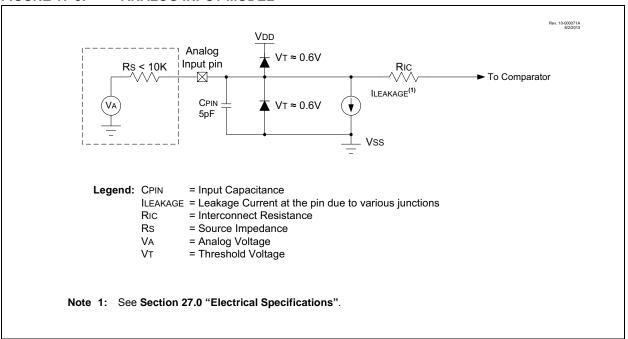

### 17.3 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 17-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| FIGURE 19-3.           | TIMERI GATE SINGLE-PULSE                 |                                                                         |

|------------------------|------------------------------------------|-------------------------------------------------------------------------|

| TMR1GE                 |                                          |                                                                         |

| T1GPOL                 |                                          |                                                                         |

| T1GSPM                 |                                          |                                                                         |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled on | Cleared by hardware on falling edge of T1GVAL                           |

| t1g_in                 | rising edge of T1G                       |                                                                         |

| T1CKI                  |                                          |                                                                         |

| T1GVAL                 |                                          |                                                                         |

| Timer1                 | N N + 1                                  | N + 2                                                                   |

| TMR1GIF                | Cleared by software                      | ← Set by hardware on<br>falling edge of T1GVAL ← Cleared by<br>software |

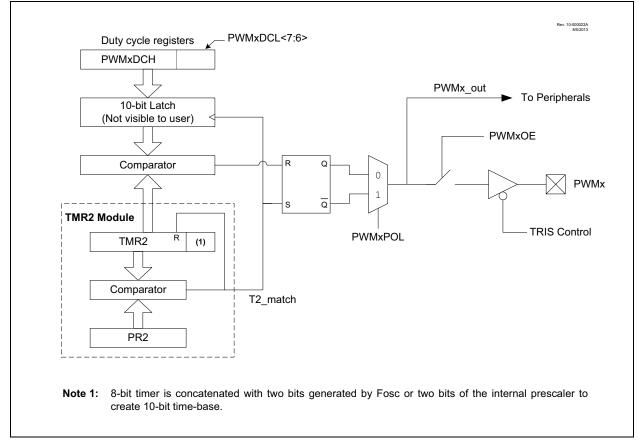

Figure 21-1 shows a simplified block diagram of PWM

For a step-by-step procedure on how to set up this

module for PWM operation, refer to Section

21.1.9 "Setup for PWM Operation using PWMx

operation.

Pins".

# 21.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

## FIGURE 21-1: SIMPLIFIED PWM BLOCK DIAGRAM

# 22.6 Register Definitions: CLC Control

| R/W-0/0          | R/W-0/0                                                                                                                                                                 | R-0/0                                                                                                                                                                             | R/W-0/0                                | R/W-0/0                                                                       | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------|------------------|------------------|-------------|--|--|

| LCxEN            | LCxOE LCxOUT LCxINTP LCxINTN LCxMODE<2:0>                                                                                                                               |                                                                                                                                                                                   |                                        |                                                                               |                  |                  |             |  |  |

| bit 7            |                                                                                                                                                                         |                                                                                                                                                                                   |                                        |                                                                               |                  |                  | bit         |  |  |

|                  |                                                                                                                                                                         |                                                                                                                                                                                   |                                        |                                                                               |                  |                  |             |  |  |

| Legend:          |                                                                                                                                                                         |                                                                                                                                                                                   |                                        |                                                                               |                  |                  |             |  |  |

| R = Readable     | e bit                                                                                                                                                                   | W = Writable                                                                                                                                                                      | bit                                    | •                                                                             | nented bit, read |                  |             |  |  |

| u = Bit is unc   | hanged                                                                                                                                                                  | x = Bit is unkr                                                                                                                                                                   | nown                                   | -n/n = Value a                                                                | t POR and BO     | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set |                                                                                                                                                                         | '0' = Bit is cle                                                                                                                                                                  | ared                                   |                                                                               |                  |                  |             |  |  |

| bit 7            | LCxEN: Con                                                                                                                                                              | figurable Logic                                                                                                                                                                   | Cell Enable bi                         | it                                                                            |                  |                  |             |  |  |

|                  | 1 = Configur                                                                                                                                                            | LCxEN: Configurable Logic Cell Enable bit<br>1 = Configurable logic cell is enabled and mixing input signals<br>0 = Configurable logic cell is disabled and has logic zero output |                                        |                                                                               |                  |                  |             |  |  |

| bit 6            | LCxOE: Con                                                                                                                                                              | LCxOE: Configurable Logic Cell Output Enable bit                                                                                                                                  |                                        |                                                                               |                  |                  |             |  |  |

|                  |                                                                                                                                                                         | rable logic cell p<br>rable logic cell p                                                                                                                                          |                                        |                                                                               |                  |                  |             |  |  |

| bit 5            | LCxOUT: Co                                                                                                                                                              | onfigurable Logi                                                                                                                                                                  | c Cell Data Ou                         | utput bit                                                                     |                  |                  |             |  |  |

|                  | Read-only: lo                                                                                                                                                           | ogic cell output                                                                                                                                                                  | data, after LC>                        | <pol; sampled<="" td=""><td>from lcx_out w</td><td>/ire.</td><td></td></pol;> | from lcx_out w   | /ire.            |             |  |  |

| bit 4            | LCxINTP: Co                                                                                                                                                             | onfigurable Log                                                                                                                                                                   | ic Cell Positive                       | e Edge Going I                                                                | nterrupt Enable  | e bit            |             |  |  |

|                  |                                                                                                                                                                         | will be set wher<br>will not be set                                                                                                                                               | n a rising edge                        | e occurs on lcx                                                               | _out             |                  |             |  |  |

| bit 3            |                                                                                                                                                                         |                                                                                                                                                                                   | ic Cell Negativ                        | ve Edge Going                                                                 | Interrupt Enabl  | e bit            |             |  |  |

|                  | LCxINTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit<br>1 = CLCxIF will be set when a falling edge occurs on lcx_out<br>0 = CLCxIF will not be set |                                                                                                                                                                                   |                                        |                                                                               |                  |                  |             |  |  |

| bit 2-0          |                                                                                                                                                                         |                                                                                                                                                                                   | ble I ogic Cell                        | Functional Mo                                                                 | de hits          |                  |             |  |  |

| dit 2-0          | 111 = Cell is<br>110 = Cell is<br>101 = Cell is<br>100 = Cell is<br>011 = Cell is                                                                                       | s 4-input AND<br>s OR-XOR                                                                                                                                                         | arent latch with<br>th R<br>lop with R | h S and R                                                                     | de dits          |                  |             |  |  |

#### REGISTER 22-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

|                  | R/W-x/u                                         | R/W-x/u                            | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|-------------------------------------------------|------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| LCxG4D4T         | LCxG4D4N                                        | LCxG4D3T                           | LCxG4D3N        | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N     |

| bit 7            |                                                 |                                    |                 |                |                  |                  | bit (        |

| Legend:          |                                                 |                                    |                 |                |                  |                  |              |

| R = Readable b   | oit                                             | W = Writable                       | bit             | U = Unimpler   | nented bit, read | as '0'           |              |

| u = Bit is uncha | anged                                           | x = Bit is unkr                    | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| 1' = Bit is set  | 0                                               | '0' = Bit is clea                  | ared            |                |                  |                  |              |

| bit 7            |                                                 | Note 4 Date 4 T                    |                 | tod) bit       |                  |                  |              |

|                  |                                                 | Bate 4 Data 4 7<br>gated into Icxo | ,               | led) bit       |                  |                  |              |

|                  |                                                 | not gated into                     |                 |                |                  |                  |              |

| bit 6            |                                                 | Gate 4 Data 4                      | •               | ted) bit       |                  |                  |              |

|                  | 1 = Icxd4N is gated into Icxg4                  |                                    |                 |                |                  |                  |              |

|                  | 0 = lcxd4N is not gated into lcxg4              |                                    |                 |                |                  |                  |              |

| bit 5            | LCxG4D3T: O                                     | Gate 4 Data 3 1                    | True (non-inver | rted) bit      |                  |                  |              |

|                  |                                                 | gated into lcxg                    | ,               |                |                  |                  |              |

|                  |                                                 | not gated into                     | •               |                |                  |                  |              |

| bit 4            |                                                 | Gate 4 Data 3 I                    | •               | ted) bit       |                  |                  |              |

|                  |                                                 | gated into lcxg<br>not gated into  |                 |                |                  |                  |              |

| bit 3            |                                                 | Gate 4 Data 2 1                    | •               | ted) hit       |                  |                  |              |

| 511 5            |                                                 | gated into Icxo                    |                 |                |                  |                  |              |

|                  |                                                 | not gated into                     | ,               |                |                  |                  |              |

| bit 2            | LCxG4D2N: Gate 4 Data 2 Negated (inverted) bit  |                                    |                 |                |                  |                  |              |

|                  |                                                 | gated into Icx                     |                 |                |                  |                  |              |

|                  | 0 = Icxd2N is                                   | not gated into                     | lcxg4           |                |                  |                  |              |

| bit 1            | LCxG4D1T: Gate 4 Data 1 True (non-inverted) bit |                                    |                 |                |                  |                  |              |

|                  |                                                 | gated into lcxg                    | •               |                |                  |                  |              |

|                  |                                                 | not gated into                     | •               |                |                  |                  |              |

| bit 0            |                                                 | Gate 4 Data 1                      | •               | ted) bit       |                  |                  |              |

|                  |                                                 | gated into lcxg<br>not gated into  |                 |                |                  |                  |              |

## REGISTER 22-8: CLCxGLS3: GATE 4 LOGIC SELECT REGISTER

DS40001615C-page 176

## 23.9 Register Definitions: NCOx Control Registers

## REGISTER 23-1: NCOxCON: NCOx CONTROL REGISTER

| R/W-0/0                                                                  | R/W-0/0                                                                                                                                   | R-0/0              | R/W-0/0 | U-0 | U-0          | U-0 | R/W-0/0 |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-----|--------------|-----|---------|

| NxEN                                                                     | NxOE                                                                                                                                      | NxOUT              | NxPOL   | _   | —            | —   | NxPFM   |

| bit 7                                                                    |                                                                                                                                           | 2                  |         |     |              | •   | bit 0   |

| Legend:                                                                  |                                                                                                                                           |                    |         |     |              |     |         |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' |                                                                                                                                           |                    |         |     |              |     |         |

| u = Bit is uncha                                                         | anged                                                                                                                                     | x = Bit is unkno   | wn      | •   | POR and BOR/ |     | Resets  |

| '1' = Bit is set                                                         | 3                                                                                                                                         | '0' = Bit is clear | ed      |     |              |     |         |

|                                                                          |                                                                                                                                           |                    |         |     |              |     |         |

| bit 7                                                                    | NxEN: NCOx Enable bit<br>1 = NCOx module is enabled<br>0 = NCOx module is disabled                                                        |                    |         |     |              |     |         |

| bit 6                                                                    | NxOE: NCOx Output Enable bit<br>1 = NCOx output pin is enabled<br>0 = NCOx output pin is disabled                                         |                    |         |     |              |     |         |

| bit 5                                                                    | NxOUT: NCOx Output bit<br>1 = NCOx output is high<br>0 = NCOx output is low                                                               |                    |         |     |              |     |         |

| bit 4                                                                    | NxPOL: NCOx Polarity bit<br>1 = NCOx output signal is active low (inverted)<br>0 = NCOx output signal is active high (non-inverted)       |                    |         |     |              |     |         |

| bit 3-1                                                                  | Unimplemented: Read as '0'                                                                                                                |                    |         |     |              |     |         |

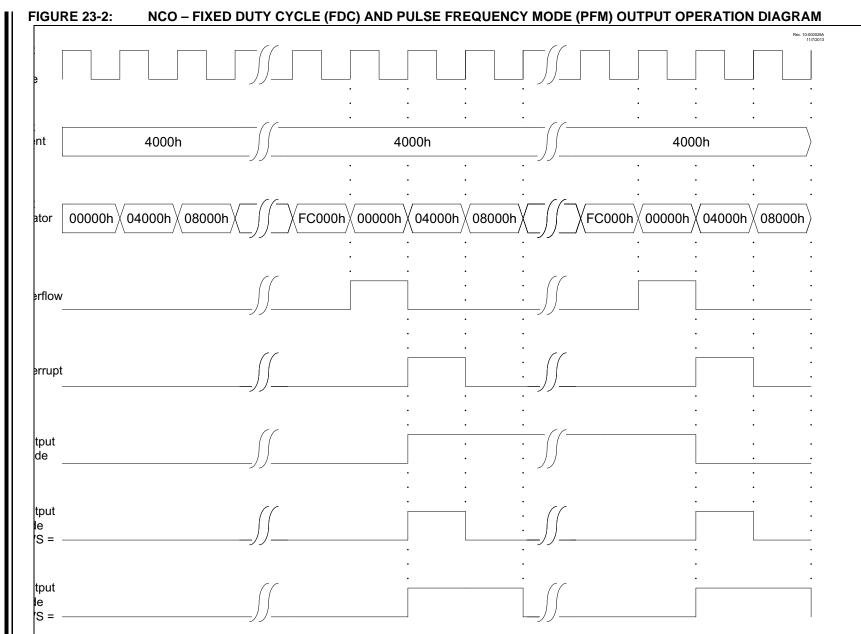

| bit 0                                                                    | NxPFM: NCOx Pulse Frequency Mode bit         1 = NCOx operates in Pulse Frequency mode         0 = NCOx operates in Fixed Duty Cycle mode |                    |         |     |              |     |         |

#### REGISTER 23-2: NCOxCLK: NCOx INPUT CLOCK CONTROL REGISTER

| NxPWS<2:0>(1, 2)         —         —         —         NxCKS<1:0>           bit 7         bit 7 | R/W-0/0 | R/W-0/0          | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------------------------------------------------------------------------------------------------|---------|------------------|---------|-----|-----|-----|---------|---------|

| bit 7 bit                                                                                       |         | NxPWS<2:0>(1, 2) |         | —   | —   | —   | NxCKS   | S<1:0>  |

|                                                                                                 | bit 7   |                  |         |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 NxPWS<2:0>: NCOx Output Pulse Width Select bits<sup>(1, 2)</sup>

- 111 = 128 NCOx clock periods

- 110 = 64 NCOx clock periods

- 101 = 32 NCOx clock periods

- 100 = 16 NCOx clock periods

- 011 = 8 NCOx clock periods

- 010 = 4 NCOx clock periods

- 001 = 2 NCOx clock periods

- 000 = 1 NCOx clock periods

- bit 4-2 Unimplemented: Read as '0'

- bit 1-0 NxCKS<1:0>: NCOx Clock Source Select bits

- 11 = NCO1CLK pin

- 10 = LC1\_out

- 01 = Fosc

- 00 = HFINTOSC (16 MHz)

Note 1: NxPWS applies only when operating in Pulse Frequency mode.

2: If NCOx pulse width is greater than NCO\_overflow period, operation is indeterminate.

PIC12(L)F1501

DS40001615C-page 186

Status

© 2011-2015 Microchip Technology Inc

| Name     | Bit 7 | Bit 6   | Bit 5        | Bit 4                  | Bit 3  | Bit 2    | Bit 1     | Bit 0      | Register<br>on Page |

|----------|-------|---------|--------------|------------------------|--------|----------|-----------|------------|---------------------|

| ANSELA   | _     | —       | -            | ANSA4                  | _      | ANSA2    | ANSA1     | ANSA0      | 99                  |

| CWG1CON0 | G1EN  | G10EB   | G10EA        | G1POLB                 | G1POLA | _        | —         | G1CS0      | 187                 |

| CWG1CON1 | G1ASD | LB<1:0> | G1ASD        | G1ASDLA<1:0> G1IS<1:0> |        |          |           |            | 188                 |

| CWG1CON2 | G1ASE | G1ARSEN | _            | _                      | _      | G1ASDSC1 | G1ASDSFLT | G1ASDSCLC2 | 189                 |

| CWG1DBF  | _     | _       | CWG1DBF<5:0> |                        |        |          | 190       |            |                     |

| CWG1DBR  | _     | _       | CWG1DBR<5:0> |                        |        |          |           | 190        |                     |

| TRISA    |       | —       | TRISA5       | TRISA4                 | _(1)   | TRISA2   | TRISA1    | TRISA0     | 98                  |

Legend:

x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by CWG.

Note

1:

Unimplemented, read as '1'.

# 26.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 26-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 26.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number. (0-1)                                                                                                                                                         |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                       |

# TABLE 26-2:ABBREVIATIONDESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

# PIC12(L)F1501

# 26.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | ESRn is limited to the range 0000h -                                                          |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ADDLW            | Add literal and W                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDLW k                                                                                             |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) + k \to (W)$                                                                                             |

| Status Affected: | C, DC, Z                                                                                                      |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                     |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

## ADDWFC ADD W and CARRY bit to f

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                   |

| Operation:       | $(f<7>) \rightarrow dest<7>$<br>$(f<7:1>) \rightarrow dest<6:0>,$<br>$(f<0>) \rightarrow C,$                                                                                                                                        |

| Status Affected: | C, Z                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

# PIC12(L)F1501

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<6:3>) → PC<14:11>                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT       | Clear Watchdog Timer                                                                                                              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:      | [label] CLRWDT                                                                                                                    |

| Operands:    | None                                                                                                                              |

| Operation:   | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO, PD}$ |

| Description: | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT.<br>Status bits TO and PD are set.  |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | $\begin{array}{l} (\text{PC}) +1 \rightarrow \text{TOS}, \\ (\text{W}) \rightarrow \text{PC} < 7:0 >, \\ (\text{PCLATH} < 6:0 >) \rightarrow \text{PC} < 14:8 > \end{array}$                                          |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                             |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |

| Status Affected: | Z                                                                                                                                                             |

| Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                       |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                          |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01,10,11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                        |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•}  FSR + 1 (preincrement) \\ &\text{•}  FSR + 1 (predecrement) \\ &\text{•}  FSR + k (relative offset) \\ &\text{After the Move, the FSR value will be either:} \\ &\text{•}  FSR + 1 (all increments) \\ &\text{•}  FSR + 1 (all decrements) \\ &\text{•}  Unchanged \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                                      |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

> **Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

### MOVLB Move literal to BSR

Description:

| Syntax:          | [ <i>label</i> ]MOVLB k                                              |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \leq k \leq 31$                                                   |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVLP k                                                                                         |

| Operands:        | $0 \le k \le 127$                                                                                         |

| Operation:       | $k \rightarrow PCLATH$                                                                                    |

| Status Affected: | None                                                                                                      |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                                 |

| MOVLW            | Move literal to W                                                                                         |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                                       |

| Status Affected: | None                                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's.            |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVLW 0x5A                                                                                                |

|                  | After Instruction                                                                                         |

|                  | W = 0x5A                                                                                                  |

| MOVWF            | Move W to f                                                                                               |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                  |

| Operands:        | $0 \leq f \leq 127$                                                                                       |

| Operation:       | $(W) \to (f)$                                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to register 'f'.                                                                |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVWF OPTION_REG                                                                                          |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit<br>literal 'k'. The result is placed in the<br>W register. |

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] TRIS f                                                                                                                                     |

| Operands:        | $5 \le f \le 7$                                                                                                                                      |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

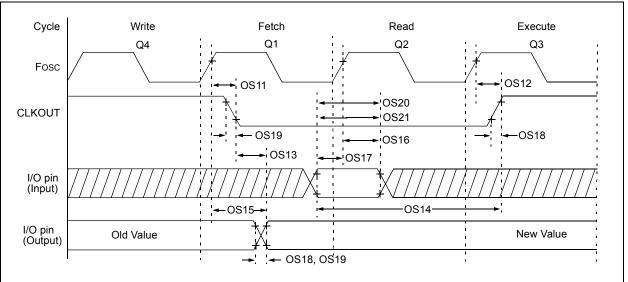

| TABLE 27-9: | CLKOUT AND I/O TIMING PARAMETERS |

|-------------|----------------------------------|

|-------------|----------------------------------|

| Standard Operating Conditions (unless otherwise stated) |          |                                                               |               |          |          |       |                                                                           |  |  |

|---------------------------------------------------------|----------|---------------------------------------------------------------|---------------|----------|----------|-------|---------------------------------------------------------------------------|--|--|

| Param.<br>No.                                           | Sym.     | Characteristic                                                | Min.          | Тур†     | Max.     | Units | Conditions                                                                |  |  |

| OS11                                                    | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                               | _             | _        | 70       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS12                                                    | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                               | —             |          | 72       | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS13                                                    | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                      | —             | -        | 20       | ns    |                                                                           |  |  |

| OS14                                                    | TioV2ckH | Port input valid before CLKOUT↑ <sup>(1)</sup>                | Tosc + 200 ns |          | _        | ns    |                                                                           |  |  |

| OS15                                                    | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                            | —             | 50       | 70*      | ns    | $3.3V \le V\text{DD} \le 5.0V$                                            |  |  |

| OS16                                                    | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in setup time) | 50            | _        | —        | ns    | $3.3V \leq V\text{DD} \leq 5.0V$                                          |  |  |

| OS17                                                    | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)   | 20            | —        | —        | ns    |                                                                           |  |  |

| OS18*                                                   | TioR     | Port output rise time                                         | _             | 40<br>15 | 72<br>32 | ns    | $VDD = 1.8V$ $3.3V \le VDD \le 5.0V$                                      |  |  |

| OS19*                                                   | TioF     | Port output fall time                                         | —             | 28<br>15 | 55<br>30 | ns    | $\begin{array}{l} VDD \mbox{=} 1.8V \\ 3.3V \le VDD \le 5.0V \end{array}$ |  |  |

| OS20*                                                   | Tinp     | INT pin input high or low time                                | 25            | —        | —        | ns    |                                                                           |  |  |

| OS21*                                                   | Tioc     | Interrupt-on-change new input level time                      | 25            |          |          | ns    |                                                                           |  |  |

\* These parameters are characterized but not tested.

$\dagger$  Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

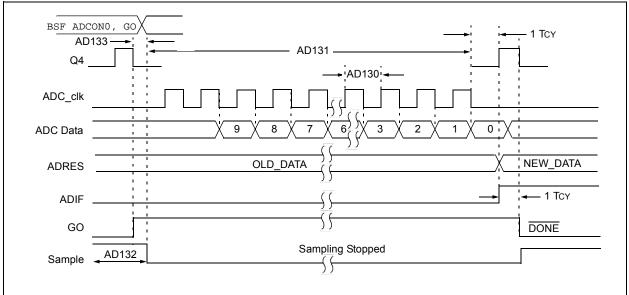

# TABLE 27-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3)</sup>

## Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                                |  |

|---------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------------|--|

| AD01          | NR   | Resolution                                        | _    | _    | 10   | bit   |                                                                           |  |

| AD02          | EIL  | Integral Error                                    | _    | ±1   | ±1.7 | LSb   | VREF = 3.0V                                                               |  |

| AD03          | Edl  | Differential Error                                | —    | ±1   | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                           |  |