#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64 x 8                                                                     |

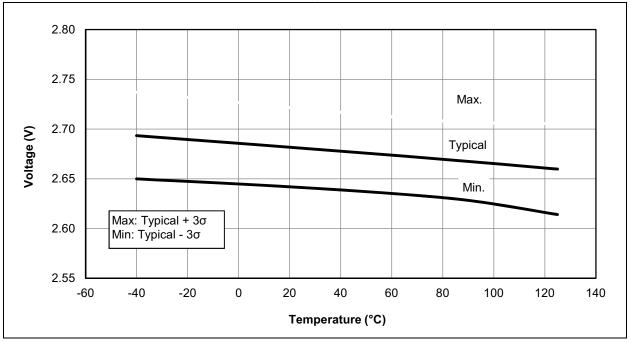

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VFDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (2x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1501t-i-mc |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### REGISTER 3-1: STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 26.0 "Instruction Set Summary"**).

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

| U-0              | U-0   | U-0             | R-1/q | R-1/q                                            | R/W-0/u          | R/W-0/u           | R/W-0/u          |  |

|------------------|-------|-----------------|-------|--------------------------------------------------|------------------|-------------------|------------------|--|

| _                | _     |                 | TO    | PD                                               | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |

| bit 7            |       |                 |       |                                                  |                  | •                 | bit 0            |  |

|                  |       |                 |       |                                                  |                  |                   |                  |  |

| Legend:          |       |                 |       |                                                  |                  |                   |                  |  |

| R = Readable b   | oit   | W = Writable    | bit   | U = Unimpler                                     | nented bit, read | as '0'            |                  |  |

| u = Bit is uncha | anged | x = Bit is unkn | iown  | -n/n = Value at POR and BOR/Value at all other F |                  |                   | ther Resets      |  |

| '1' = Bit is set | 6     |                 | ared  | q = Value depends on condition                   |                  |                   |                  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

# PIC12(L)F1501

|          |                 |               |                                                   |               |               |             |        | ,       |        |                      |                                 |

|----------|-----------------|---------------|---------------------------------------------------|---------------|---------------|-------------|--------|---------|--------|----------------------|---------------------------------|

| Address  | Name            | Bit 7         | Bit 6                                             | Bit 5         | Bit 4         | Bit 3       | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3   | 1               |               |                                                   |               |               |             |        |         |        |                      |                                 |

| F8Ch     | —               | Unimplemen    | ted                                               |               |               |             |        |         |        | _                    | _                               |

| <br>FE3h |                 |               |                                                   |               |               |             |        |         |        |                      |                                 |

| FE4h     | STATUS_<br>SHAD | —             | —                                                 | —             | -             | —           | Z_SHAD | DC_SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h     | WREG_<br>SHAD   | Working Reg   | jister Shadow                                     |               |               |             |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE6h     | BSR_<br>SHAD    | —             | —                                                 | —             | Bank Select   | Register Sh | adow   |         |        | x xxxx               | u uuuu                          |

| FE7h     | PCLATH_<br>SHAD | —             | Program Co                                        | unter Latch H | ligh Register | Shadow      |        |         |        | -xxx xxxx            | uuuu uuuu                       |

| FE8h     | FSR0L_<br>SHAD  | Indirect Data | Memory Add                                        | ress 0 Low F  | Pointer Shado | W           |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE9h     | FSR0H_<br>SHAD  | Indirect Data | Memory Add                                        | ress 0 High I | Pointer Shad  | WO          |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEAh     | FSR1L_<br>SHAD  | Indirect Data | Memory Add                                        | ress 1 Low F  | Pointer Shado | w           |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEBh     | FSR1H_<br>SHAD  | Indirect Data | ndirect Data Memory Address 1 High Pointer Shadow |               |               |             |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FECh     | —               | Unimplemen    | implemented                                       |               |               |             |        |         | —      | —                    |                                 |

| FEDh     | STKPTR          | —             | _                                                 | _             | Current Sta   | ck Pointer  |        |         |        | 1 1111               | 1 1111                          |

| FEEh     | TOSL            | Top-of-Stack  | Low byte                                          |               |               |             |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| FEFh     | TOSH            | —             | Top-of-Stack                                      | High byte     |               |             |        |         |        | -xxx xxxx            | -uuu uuuu                       |

**TABLE 3-5:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

PIC12F1501 only.

Unimplemented, read as '1'. Legend: : Note 1:

2:

# 5.0 OSCILLATOR MODULE

#### 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from an external clock or from one of two internal oscillators, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fast start-up oscillator allows internal circuits to power-up and stabilize before switching to the 16 MHz HFINTOSC

The oscillator module can be configured in one of the following clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 20 MHz)

- 4. INTOSC Internal oscillator (31 kHz to 16 MHz)

Clock Source modes are selected by the FOSC<1:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The ECH, ECM, and ECL clock modes rely on an external logic level signal as the device clock source.

The INTOSC internal oscillator block produces a low and high-frequency clock source, designated LFINTOSC and HFINTOSC. (See Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these two clock sources.

#### 5.2.2.4 Peripheral Clock Sources

The clock sources described in this chapter and the Timer's are available to different peripherals. Table 5-1 lists the clocks and timers available for each peripheral.

| TABLE 5-1: | PERIPHERAL CLOCK |

|------------|------------------|

|            | SOURCES          |

|      | FOSC | FRC | HFINTOSC | LFINTOSC | TMR0 | TMR1 | TMR2 |

|------|------|-----|----------|----------|------|------|------|

| ADC  | ٠    | •   |          |          |      |      |      |

| CLC  | •    | •   | •        | •        | •    | •    | •    |

| COMP |      |     |          |          |      | ٠    |      |

| CWG  | ٠    |     | ٠        |          |      |      |      |

| NCO  | ٠    |     | ٠        |          |      |      |      |

| PWM  | ٠    |     |          |          |      |      | •    |

| PWRT |      |     |          | •        |      |      |      |

| TMR0 | ٠    |     |          |          |      |      |      |

| TMR1 | ٠    |     |          | •        |      |      |      |

| TMR2 | ٠    |     |          |          |      |      |      |

| WDT  |      |     |          | •        |      |      |      |

#### 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC and 31 kHz LFINTOSC connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register (Register 5-1) select the frequency output of the internal oscillators.

| Note: | Following any Reset, the IRCF<3:0> bits<br>of the OSCCON register are set to '0111'<br>and the frequency selection is set to<br>500 kHz. The user can modify the IRCF |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | bits to select a different frequency.                                                                                                                                 |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

#### 5.2.2.6 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-3). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-3 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-2.

Start-up delay specifications are located in Table 27-8, "Oscillator Parameters".

# PIC12(L)F1501

| U-0                       | U-0                                                                                                       | U-0                                                                 | U-0                                            | U-0            | U-0              | R/W-0/0          | R/W-0/0     |

|---------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------|----------------|------------------|------------------|-------------|

| _                         | _                                                                                                         |                                                                     |                                                |                |                  | CLC2IF           | CLC1IF      |

| bit 7                     |                                                                                                           |                                                                     |                                                | ·              |                  |                  | bit 0       |

|                           |                                                                                                           |                                                                     |                                                |                |                  |                  |             |

| Legend:                   |                                                                                                           |                                                                     |                                                |                |                  |                  |             |

| R = Read                  | dable bit                                                                                                 | W = Writable                                                        | bit                                            | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is                | unchanged                                                                                                 | x = Bit is unkr                                                     | nown                                           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is              | s set                                                                                                     | '0' = Bit is clea                                                   | ared                                           |                |                  |                  |             |

| bit 7-2<br>bit 1<br>bit 0 | CLC2IF: Con<br>1 = Interrupt i<br>0 = Interrupt i<br>CLC1IF: Con<br>1 = Interrupt i                       | is not pending<br>figurable Logic<br>is pending                     | Block 2 Interr                                 |                |                  |                  |             |

| Note:                     | Interrupt flag bits a<br>condition occurs, r<br>its corresponding o<br>Enable bit, GIE o<br>User software | egardless of the<br>enable bit or th<br>f the INTCON<br>should ensu | e state of<br>e Global<br>register.<br>ire the |                |                  |                  |             |

## REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### 10.6 Register Definitions: Flash Program Memory Control

#### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u             | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u             | R/W-x/u |

|---------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                     |         |                      | PMDA    | AT<7:0>           |                      |                     |         |

| bit 7               |         |                      |         |                   |                      |                     | bit C   |

|                     |         |                      |         |                   |                      |                     |         |

| Legend:             |         |                      |         |                   |                      |                     |         |

| R = Readable bit    |         | W = Writable bit     |         | U = Unimpleme     | nted bit, read as '0 | ,                   |         |

| u = Bit is unchange | ed      | x = Bit is unknowr   | ı       | -n/n = Value at F | OR and BOR/Valu      | ue at all other Res | ets     |

| '1' = Bit is set    |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0

PMDAT<7:0>: Read/write value for Least Significant bits of program memory

#### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|

| —     | —   |         | PMDAT<13:8> |         |         |         |         |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PMAD    | R<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

PMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | PMADR<14:8> | >       |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 PMADR<14:8>: Specifies the Most Significant bits for program memory address

Note 1: Unimplemented, read as '1'.

### **REGISTER 15-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                                          | R/W-x/u | R/W-x/u | R/W-x/u      |  |

|------------------|---------|--------------------|---------|--------------------------------------------------|---------|---------|--------------|--|

|                  |         |                    | ADRE    | S<9:2>                                           |         |         |              |  |

| bit 7            |         |                    |         |                                                  |         |         | bit 0        |  |

|                  |         |                    |         |                                                  |         |         |              |  |

| Legend:          |         |                    |         |                                                  |         |         |              |  |

| R = Readable     | bit     | W = Writable b     | it      | U = Unimplemented bit, read as '0'               |         |         |              |  |

| u = Bit is unch  | anged   | x = Bit is unkno   | own     | -n/n = Value at POR and BOR/Value at all other F |         |         | other Resets |  |

| '1' = Bit is set |         | '0' = Bit is clear | red     |                                                  |         |         |              |  |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

#### **REGISTER 15-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | <1:0>   | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result bit 5-0 Reserved: Do not use.

| R/W-x/u                                                                          | R/W-x/u | R/W-x/u           | R/W-x/u          | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|----------------------------------------------------------------------------------|---------|-------------------|------------------|------------------------------------|---------|---------|---------|--|

| —                                                                                | —       | —                 | —                | _                                  | -       | ADRE    | S<9:8>  |  |

| bit 7                                                                            |         |                   |                  | -                                  |         |         | bit C   |  |

|                                                                                  |         |                   |                  |                                    |         |         |         |  |

| Legend:                                                                          |         |                   |                  |                                    |         |         |         |  |

| R = Readable                                                                     | bit     | W = Writable      | bit              | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all |         |                   | R/Value at all o | other Resets                       |         |         |         |  |

| '1' = Bit is set                                                                 |         | '0' = Bit is clea | ared             |                                    |         |         |         |  |

bit 7-2 **Reserved**: Do not use.

| bit 1-0 | ADRES<9:8>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Upper two bits of 10-bit conversion result |

## REGISTER 15-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u    | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------|-------------|---------|---------|---------|---------|---------|---------|--|

| ADRES<7:0> |             |         |         |         |         |         |         |  |

| bit 7      | bit 7 bit 0 |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

#### 16.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACxCON1 register.

The DAC output voltage can be determined by using Equation 16-1.

#### 16.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 27-14.

### 16.3 DAC Voltage Reference Output

The unbuffered DAC voltage can be output to the DACxOUTn pin(s) by setting the respective DACOEn bit(s) of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTn pin automatically overrides the digital output buffer, the weak pull-up and digital input threshold detector functions of that pin.

Reading the DACxOUTn pin when it has been configured for DAC reference voltage output will always return a '0'.

**Note:** The unbuffered DAC output (DACxOUTn) is not intended to drive an external load.

## 16.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 16.5 Effects of a Reset

A device Reset affects the following:

- · DACx is disabled.

- DACx output voltage is removed from the DACxOUTn pin(s).

- The DACR<4:0> range select bits are cleared.

#### EQUATION 16-1: DAC OUTPUT VOLTAGE

#### <u>IF DACEN = 1</u>

$$DACx\_output = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE-$$

**Note:** See the DACxCON0 register for the available VSOURCE+ and VSOURCE- selections.

## 17.8 Register Definitions: Comparator Control

| R/W-0/0                 | R-0/0                    | R/W-0/0                                 | R/W-0/0         | U-0              | R/W-1/1         | R/W-0/0         | R/W-0/0         |  |

|-------------------------|--------------------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------|-----------------|--|

| CxON                    | CxOUT                    | CxOE                                    | CxPOL           | _                | CxSP            | CxHYS           | CxSYNC          |  |

| bit 7                   |                          |                                         |                 |                  |                 |                 | bit 0           |  |

| Logondi                 |                          |                                         |                 |                  |                 |                 |                 |  |

| Legend:<br>R = Readable | ∍ hit                    | W = Writable                            | hit             | II = I Inimpler  | mented hit rea  | 1 as '0'        |                 |  |

| u = Bit is unc          |                          | x = Bit is unki                         |                 |                  |                 |                 |                 |  |

| '1' = Bit is set        |                          | '0' = Bit is cle                        |                 |                  |                 |                 |                 |  |

|                         |                          |                                         |                 |                  |                 |                 |                 |  |

| bit 7                   | CxON: Com                | parator Enable                          | bit             |                  |                 |                 |                 |  |

|                         |                          | ator is enabled                         |                 |                  |                 |                 |                 |  |

|                         | -                        | ator is disabled                        |                 | s no active pow  | ver             |                 |                 |  |

| bit 6                   |                          | nparator Output                         |                 |                  |                 |                 |                 |  |

|                         |                          | (inverted polar                         | <u>ity):</u>    |                  |                 |                 |                 |  |

|                         | 1 = CxVP <<br>0 = CxVP > | -                                       |                 |                  |                 |                 |                 |  |

|                         |                          | ) (non-inverted)                        | oolaritv):      |                  |                 |                 |                 |  |

|                         | 1 = CxVP >               |                                         | <b>, ,</b>      |                  |                 |                 |                 |  |

|                         | 0 = CxVP <               | CxVN                                    |                 |                  |                 |                 |                 |  |

| bit 5                   | CxOE: Com                | parator Output                          | Enable bit      |                  |                 |                 |                 |  |

|                         |                          | is present on th                        |                 | Requires that th | ne associated T | RIS bit be clea | red to actually |  |

|                         |                          | e pin. Not affect                       | ed by CxON.     |                  |                 |                 |                 |  |

|                         |                          | is internal only                        |                 |                  |                 |                 |                 |  |

| bit 4                   |                          | nparator Outpu                          |                 | ct bit           |                 |                 |                 |  |

|                         |                          | ator output is inv<br>ator output is no |                 |                  |                 |                 |                 |  |

| bit 3                   | -                        | -                                       |                 |                  |                 |                 |                 |  |

|                         | •                        | nted: Read as '                         |                 | :1               |                 |                 |                 |  |

| bit 2                   |                          | parator Speed/F                         |                 |                  |                 |                 |                 |  |

|                         |                          | ator mode in no<br>ator mode in lov     |                 |                  |                 |                 |                 |  |

| bit 1                   | -                        | nparator Hyster                         | -               |                  |                 |                 |                 |  |

|                         |                          | ator hysteresis                         |                 |                  |                 |                 |                 |  |

|                         |                          | ator hysteresis                         |                 |                  |                 |                 |                 |  |

| bit 0                   | -                        | omparator Outp                          |                 | is Mode bit      |                 |                 |                 |  |

|                         |                          | ator output to                          | •               |                  | onous to chand  | ges on Timer1   | clock source    |  |

|                         |                          |                                         |                 |                  |                 |                 |                 |  |

|                         | 0 0.00 0.0               | updated on the                          | falling edge of | Limer1 clock s   | ource.          |                 |                 |  |

#### REGISTER 17-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

#### 19.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 19-1 displays the Timer1 enable selections.

| TABLE 19-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### 19.2 Clock Source Selection

The TMR1CS<1:0> bits of the T1CON register are used to select the clock source for Timer1. Table 19-2 displays the clock source selections.

#### 19.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 19.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 19-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | Clock Source                   |  |  |

|-------------|--------------------------------|--|--|

| 11          | LFINTOSC                       |  |  |

| 10          | External Clocking on T1CKI Pin |  |  |

| 01          | System Clock (Fosc)            |  |  |

| 00          | Instruction Clock (Fosc/4)     |  |  |

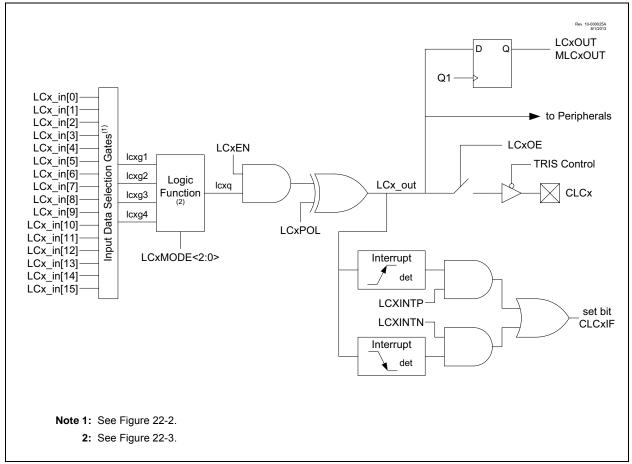

## 22.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 16 input signals, and through the use of configurable gates, reduces the 16 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 22-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- · Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### FIGURE 22-1: CONFIGURABLE LOGIC CELL BLOCK DIAGRAM

| R/W-x/u                 | R/W-x/u                                                                           | R/W-x/u            | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |

|-------------------------|-----------------------------------------------------------------------------------|--------------------|-----------------|----------------|------------------|------------------|-------------|--|--|

| LCxG2D4T                | LCxG2D4N                                                                          | LCxG2D3T           | LCxG2D3N        | LCxG2D2T       | LCxG2D2N         | LCxG2D1T         | LCxG2D1N    |  |  |

| bit 7                   | •                                                                                 |                    |                 |                |                  |                  | bit (       |  |  |

|                         |                                                                                   |                    |                 |                |                  |                  |             |  |  |

| Legend:<br>R = Readable | hit                                                                               |                    | hit             | II – Unimplor  | nented bit, read |                  |             |  |  |

|                         |                                                                                   | W = Writable bit   |                 |                | ,                |                  | ther Decete |  |  |

| u = Bit is uncha        | angeo                                                                             | x = Bit is unknown |                 | -n/n = value a | at POR and BO    | R/value at all c | iner Resets |  |  |

| '1' = Bit is set        |                                                                                   | '0' = Bit is cle   | ared            |                |                  |                  |             |  |  |

| bit 7                   | LCxG2D4T:                                                                         | Gate 2 Data 4 1    | Frue (non-invei | rted) bit      |                  |                  |             |  |  |

|                         |                                                                                   | gated into lcxo    |                 | ,              |                  |                  |             |  |  |

|                         | 0 = Icxd4T is                                                                     | not gated into     | lcxg2           |                |                  |                  |             |  |  |

| bit 6                   | LCxG2D4N:                                                                         | Gate 2 Data 4      | Negated (inver  | ted) bit       |                  |                  |             |  |  |

|                         | 1 = lcxd4N is gated into lcxg2                                                    |                    |                 |                |                  |                  |             |  |  |

|                         | 0 = lcxd4N is not gated into lcxg2                                                |                    |                 |                |                  |                  |             |  |  |

| bit 5                   | LCxG2D3T: 0                                                                       | Gate 2 Data 3 1    | Frue (non-invei | rted) bit      |                  |                  |             |  |  |

|                         | 1 = Icxd3T is gated into Icxg2                                                    |                    |                 |                |                  |                  |             |  |  |

|                         | 0 = Icxd3T is                                                                     | not gated into     | lcxg2           |                |                  |                  |             |  |  |

| bit 4                   | LCxG2D3N:                                                                         | Gate 2 Data 3      | Negated (inver  | ted) bit       |                  |                  |             |  |  |

|                         | 1 = lcxd3N is gated into lcxg2                                                    |                    |                 |                |                  |                  |             |  |  |

|                         |                                                                                   | not gated into     | •               |                |                  |                  |             |  |  |

| bit 3                   |                                                                                   | Gate 2 Data 2 1    |                 | rted) bit      |                  |                  |             |  |  |

|                         | 1 = lcxd2T is gated into lcxg2<br>0 = lcxd2T is not gated into lcxg2              |                    |                 |                |                  |                  |             |  |  |

| hit 0                   |                                                                                   | 0                  | 0               | tod) bit       |                  |                  |             |  |  |

| bit 2                   |                                                                                   | Gate 2 Data 2      | 0 (             | ted) bit       |                  |                  |             |  |  |

|                         | 1 = Icxd2N is gated into Icxg2<br>0 = Icxd2N is not gated into Icxg2              |                    |                 |                |                  |                  |             |  |  |

| bit 1                   |                                                                                   | •                  | •               | ted) hit       |                  |                  |             |  |  |

| bit i                   | LCxG2D1T: Gate 2 Data 1 True (non-inverted) bit<br>1 = lcxd1T is gated into lcxg2 |                    |                 |                |                  |                  |             |  |  |

|                         |                                                                                   | not gated into     |                 |                |                  |                  |             |  |  |

| bit 0                   |                                                                                   | Gate 2 Data 1      |                 | ted) bit       |                  |                  |             |  |  |

|                         | 1 = lcxd1N is gated into lcxg2                                                    |                    |                 |                |                  |                  |             |  |  |

|                         | 0 = lcxd1N is not gated into lcxg2                                                |                    |                 |                |                  |                  |             |  |  |

#### REGISTER 22-6: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

| R/W-x/u          | R/W-x/u       | R/W-x/u                             | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------------|-------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T         | LCxG3D4N      | LCxG3D3T                            | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7            |               |                                     |                 |                |                  |                  | bit C       |

|                  |               |                                     |                 |                |                  |                  |             |

| Legend:          |               |                                     |                 |                |                  | ( <b>a</b> )     |             |

| R = Readable     |               | W = Writable                        |                 | •              | nented bit, read |                  |             |

| u = Bit is unch  | anged         | x = Bit is unkr                     |                 | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |               | '0' = Bit is clea                   | ared            |                |                  |                  |             |

| bit 7            |               | Gate 3 Data 4 1                     | True (non-inver | ted) bit       |                  |                  |             |

|                  |               | gated into lcxc                     | -               | (eu) bit       |                  |                  |             |

|                  |               | not gated into                      |                 |                |                  |                  |             |

| bit 6            | LCxG3D4N:     | Gate 3 Data 4                       | Negated (inver  | ted) bit       |                  |                  |             |

|                  |               | gated into Icx                      |                 |                |                  |                  |             |

|                  |               | not gated into                      | •               |                |                  |                  |             |

| bit 5            |               | Gate 3 Data 3 1                     | •               | ted) bit       |                  |                  |             |

|                  |               | gated into lcxg<br>not gated into   |                 |                |                  |                  |             |

| bit 4            |               | Gate 3 Data 3                       | •               | ted) hit       |                  |                  |             |

| bit 4            |               | gated into lcx                      | •               | (eu) bit       |                  |                  |             |

|                  |               | not gated into                      |                 |                |                  |                  |             |

| bit 3            | LCxG3D2T: (   | Gate 3 Data 2 1                     | rue (non-inver  | ted) bit       |                  |                  |             |

|                  |               | gated into lcxg                     |                 |                |                  |                  |             |

|                  |               | not gated into                      | •               |                |                  |                  |             |

| bit 2            |               | Gate 3 Data 2 I                     | •               | ted) bit       |                  |                  |             |

|                  |               | s gated into lcxg<br>not gated into |                 |                |                  |                  |             |

| bit 1            |               | Gate 3 Data 1 1                     | -               | ted) hit       |                  |                  |             |

| bit i            |               | gated into Icxo                     | ·               |                |                  |                  |             |

|                  |               | not gated into                      |                 |                |                  |                  |             |

| bit 0            | LCxG3D1N:     | Gate 3 Data 1 I                     | Negated (inver  | ted) bit       |                  |                  |             |

|                  |               | gated into lcx                      |                 |                |                  |                  |             |

|                  | 0 = lcxd1N is |                                     |                 |                |                  |                  |             |

### REGISTER 22-7: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

PIC12(L)F1501

DS40001615C-page 186

Status

© 2011-2015 Microchip Technology Inc

# PIC12(L)F1501

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for highperformance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

## 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

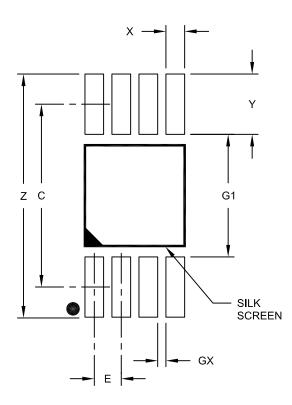

## RECOMMENDED LAND PATTERN

|                         | Units    |      | MILLIMETERS |      |  |

|-------------------------|----------|------|-------------|------|--|

| Dimensio                | n Limits | MIN  | NOM         | MAX  |  |

| Contact Pitch           | E        |      | 0.65 BSC    |      |  |

| Contact Pad Spacing     | С        |      | 4.40        |      |  |

| Overall Width           | Z        |      |             | 5.85 |  |

| Contact Pad Width (X8)  | X1       |      |             | 0.45 |  |

| Contact Pad Length (X8) | Y1       |      |             | 1.45 |  |

| Distance Between Pads   | G1       | 2.95 |             |      |  |

| Distance Between Pads   | GX       | 0.20 |             |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2111A

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-915-1

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.