Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

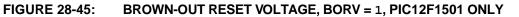

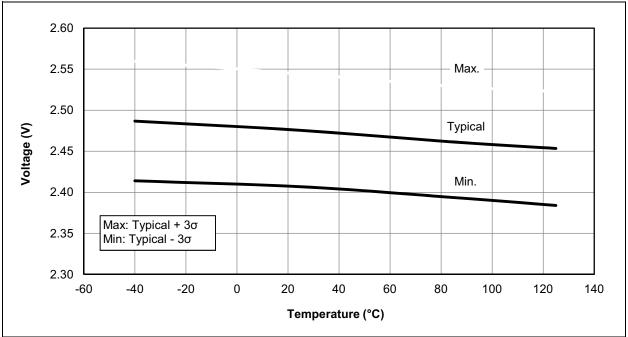

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                     |

| Supplier Device Package    | 8-MSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f1501t-i-ms |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC12(L)F1501

# TABLE 3-3: PIC12(L)F1501 MEMORY MAP (CONTINUED)

|              | Bank 30                      |      | Bank 31       |

|--------------|------------------------------|------|---------------|

| F0Ch         | _                            | F8Ch |               |

| F0Dh         | _                            |      |               |

| F0Eh         | _                            |      | Unimplemented |

| F0Fh         | CLCDATA                      |      | Read as '0'   |

| F10h         | CLC1CON                      | FF2h |               |

| F11h         | CLC1POL                      | FE3h | STATUS SHAD   |

| F12h         | CLC1SEL0                     | FE4h | WREG_SHAD     |

| F13h         | CLC1SEL1                     | FE5h | BSR_SHAD      |

| F14h         | CLC1GLS0                     | FE6h | PCLATH_SHAD   |

| F15h         | CLC1GLS1                     | FE7h | FSR0L_SHAD    |

| F16h         | CLC1GLS2                     | FE8h | FSR0L_SHAD    |

| F17h         | CLC1GLS3                     | FE9h | FSR1L_SHAD    |

| F18h         | CLC2CON                      | FEAh | FSR1L_SHAD    |

| F19h         | CLC2POL                      | FEBh | FSRIN_SHAD    |

| F1Ah         | CLC2SEL0                     | FECh |               |

| F1Bh         | CLC2SEL1                     | FEDh | STKPTR        |

| F1Ch         | CLC2GLS0                     | FEEh | TOSL          |

| F1Dh         | CLC2GLS1                     | FEFh | TOSH          |

| F1Eh         | CLC2GLS2                     |      |               |

| F1Fh         | CLC2GLS3                     |      |               |

| F20h<br>F6Fh | Unimplemented<br>Read as '0' |      |               |

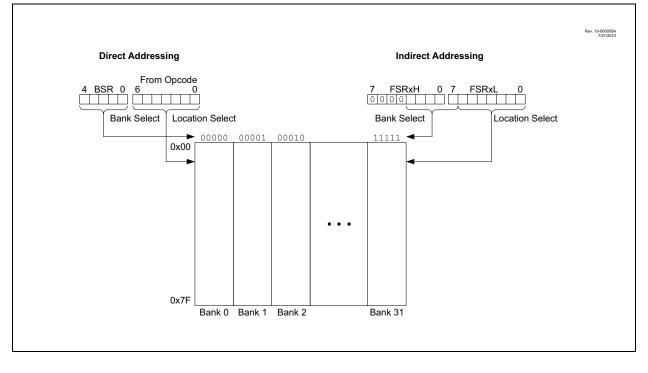

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

# 5.4 Register Definitions: Oscillator Control

| U-0                               | R/W-0/0                  | R/W-1/1            | R/W-1/1       | R/W-1/1         | U-0              | R/W-0/0          | R/W-0/0      |  |

|-----------------------------------|--------------------------|--------------------|---------------|-----------------|------------------|------------------|--------------|--|

| _                                 | IRCF<3:0>                |                    |               |                 | _                | SCS              | <1:0>        |  |

| oit 7                             |                          |                    |               |                 |                  |                  | bit (        |  |

|                                   |                          |                    |               |                 |                  |                  |              |  |

| egend:                            |                          |                    |               |                 |                  |                  |              |  |

| R = Readable bit W = Writable bit |                          |                    | bit           | U = Unimpler    | nented bit, read | d as '0'         |              |  |

| ı = Bit is unch                   | anged                    | x = Bit is unkn    | iown          | -n/n = Value a  | at POR and BC    | R/Value at all o | other Resets |  |

| 1' = Bit is set                   |                          | '0' = Bit is clea  | ared          |                 |                  |                  |              |  |

|                                   |                          |                    |               |                 |                  |                  |              |  |

| oit 7                             | Unimplemer               | nted: Read as '    | כ'            |                 |                  |                  |              |  |

| oit 6-3                           | IRCF<3:0>:               | Internal Oscillate | or Frequency  | Select bits     |                  |                  |              |  |

|                                   | 1111 = 16 N              |                    |               |                 |                  |                  |              |  |

|                                   | 1110 = 8 M               |                    |               |                 |                  |                  |              |  |

|                                   | 1101 = 4 MHz             |                    |               |                 |                  |                  |              |  |

|                                   | 1100 = 2 M               |                    |               |                 |                  |                  |              |  |

|                                   | 1011 = 1 M               |                    |               |                 |                  |                  |              |  |

|                                   | 1010 = 500               |                    |               |                 |                  |                  |              |  |

|                                   | 1001 = 250<br>1000 = 125 |                    |               |                 |                  |                  |              |  |

|                                   |                          |                    | on Depat)     |                 |                  |                  |              |  |

|                                   | 0111 = 500<br>0110 = 250 | kHz (default up    | on Resel)     |                 |                  |                  |              |  |

|                                   | 0110 = 230<br>0101 = 125 |                    |               |                 |                  |                  |              |  |

|                                   | 0100 = 62.5              |                    |               |                 |                  |                  |              |  |

|                                   | $0.01 \times = 31.2$     |                    |               |                 |                  |                  |              |  |

|                                   | 000x = 31 k              |                    |               |                 |                  |                  |              |  |

| oit 2                             | Unimplemer               | nted: Read as '    | o'            |                 |                  |                  |              |  |

| oit 1-0                           | SCS<1:0>: 8              | System Clock Se    | elect bits    |                 |                  |                  |              |  |

|                                   |                          | oscillator block   |               |                 |                  |                  |              |  |

|                                   | 01 = Reserve             | ed                 |               |                 |                  |                  |              |  |

|                                   | 00 = Clock d             | etermined by F     | OSC<1:0> in ( | Configuration V | Vords.           |                  |              |  |

|                                   | olicate frequen          |                    |               |                 |                  |                  |              |  |

# REGISTER 5-1: OSCCON: OSCILLATOR CONTROL REGISTER

# 6.3 Register Definitions: BOR Control

### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-Out Reset Enable bit                                                 |

|---------|---------------------------------------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words = 01:                                                 |

|         | 1 = BOR Enabled                                                                             |

|         | 0 = BOR Disabled                                                                            |

|         | <u>If BOREN &lt;1:0&gt; in Configuration Words ≠ 01</u> :                                   |

|         | SBOREN is read/write, but has no effect on the BOR                                          |

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup>                                        |

|         | If BOREN <1:0> = 10 (Disabled in Sleep) or BOREN<1:0> = 01 (Under software control):        |

|         | <ul> <li>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)</li> </ul> |

|         | 0 = Band gap operates normally, and may turn off                                            |

|         | <u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u>           |

|         | BORFS is Read/Write, but has no effect.                                                     |

| bit 5-1 | Unimplemented: Read as '0'                                                                  |

| bit 0   | BORRDY: Brown-Out Reset Circuit Ready Status bit                                            |

|         | 1 = The Brown-out Reset circuit is active                                                   |

|         | 0 = The Brown-out Reset circuit is inactive                                                 |

| Noto 1. | POPEN<1:0> hits are located in Configuration Words                                          |

### **Note 1:** BOREN<1:0> bits are located in Configuration Words.

# 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the CP bit of Configuration Words.

# 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

# 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

| Note: | If the user wants to modify only a portion<br>of a previously programmed row, then the<br>contents of the entire row must be read<br>and saved in RAM prior to the erase.<br>Then, new data and retained data can be<br>written into the write latches to reprogram<br>the row of Flash program memory. How-<br>ever, any unprogrammed locations can be<br>written without first erasing the row. In this<br>case, it is not necessary to save and |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | rewrite the other previously programmed locations.                                                                                                                                                                                                                                                                                                                                                                                                 |

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

#### TABLE 10-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |  |

|---------------|----------------------|-----------------------------|--|

| PIC12(L)F1501 | 16                   | 16                          |  |

# 11.3 PORTA Registers

### 11.3.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRIS bit will always read as '1'. Example 11-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 11-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

### 11.3.2 DIRECTION CONTROL

The TRISA register (Register 11-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 11.3.3 ANALOG CONTROL

The ANSELA register (Register 11-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

### EXAMPLE 11-1: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

| 1       |             |                        |

### 11.3.4 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below in Table 11-2.

### TABLE 11-2: PORTA OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup>                                               |

|----------|--------------------------------------------------------------------------------|

| RA0      | ICSPDAT<br>DACOUT1<br>CWG1B <sup>(2)</sup><br>PWM2<br>RA0                      |

| RA1      | NCO1 <sup>(2)</sup><br>RA1                                                     |

| RA2      | DACOUT2<br>CWG1A <sup>(2)</sup><br>CLC1 <sup>(2)</sup><br>C1OUT<br>PWM1<br>RA2 |

| RA3      | None                                                                           |

| RA4      | CLKOUT<br>CWG1B <sup>(3)</sup><br>CLC1 <sup>(3)</sup><br>PWM3<br>RA4           |

| RA5      | CWG1A <sup>(3)</sup><br>CLC2<br>NCO1 <sup>(3)</sup><br>PWM4<br>RA5             |

Note 1: Priority listed from highest to lowest.

2: Default pin (see APFCON register).

3: Alternate pin (see APFCON register).

# 12.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-on-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 12-1 is a block diagram of the IOC module.

# 12.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

# 12.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

# 12.3 Interrupt Flags

The IOCAFx bits located in the IOCAF register are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx bits.

# 12.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 12-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 12.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

# 17.8 Register Definitions: Comparator Control

| R/W-0/0                 | R-0/0                                                                                                              | R/W-0/0            | R/W-0/0         | U-0              | R/W-1/1          | R/W-0/0         | R/W-0/0         |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|------------------|------------------|-----------------|-----------------|--|--|

| CxON                    | CxOUT                                                                                                              | CxOE               | CxPOL           | _                | CxSP             | CxHYS           | CxSYNC          |  |  |

| bit 7                   |                                                                                                                    |                    |                 |                  |                  |                 | bit 0           |  |  |

| Logondi                 |                                                                                                                    |                    |                 |                  |                  |                 |                 |  |  |

| Legend:<br>R = Readable | ∍ hit                                                                                                              | W = Writable       | hit             | II = I Inimpler  | mented bit, read | 1 as '0'        |                 |  |  |

| u = Bit is unchanged    |                                                                                                                    | x = Bit is unknown |                 | -                | at POR and BC    |                 | other Resets    |  |  |

| '1' = Bit is set        |                                                                                                                    | '0' = Bit is cle   |                 |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    |                    |                 |                  |                  |                 |                 |  |  |

| bit 7                   | CxON: Com                                                                                                          | parator Enable     | bit             |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    | ator is enabled    |                 |                  |                  |                 |                 |  |  |

|                         | -                                                                                                                  | ator is disabled   |                 | s no active pow  | ver              |                 |                 |  |  |

| bit 6                   |                                                                                                                    | nparator Output    |                 |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    | (inverted polar    | <u>ity):</u>    |                  |                  |                 |                 |  |  |

|                         | 1 = CxVP <<br>0 = CxVP >                                                                                           | -                  |                 |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    | ) (non-inverted)   | oolaritv):      |                  |                  |                 |                 |  |  |

|                         | 1 = CxVP >                                                                                                         |                    | <b>, ,</b>      |                  |                  |                 |                 |  |  |

|                         | 0 = CxVP <                                                                                                         | CxVN               |                 |                  |                  |                 |                 |  |  |

| bit 5                   | CxOE: Comparator Output Enable bit                                                                                 |                    |                 |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    | is present on th   |                 | Requires that th | ne associated T  | RIS bit be clea | red to actually |  |  |

|                         | drive the pin. Not affected by CxON.<br>0 = CxOUT is internal only                                                 |                    |                 |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    | •                  |                 |                  |                  |                 |                 |  |  |

| bit 4                   | CxPOL: Comparator Output Polarity Select bit                                                                       |                    |                 |                  |                  |                 |                 |  |  |

|                         | <ol> <li>Comparator output is inverted</li> <li>Comparator output is not inverted</li> </ol>                       |                    |                 |                  |                  |                 |                 |  |  |

| bit 3                   | -                                                                                                                  | -                  |                 |                  |                  |                 |                 |  |  |

|                         | •                                                                                                                  | nted: Read as '    |                 | :1               |                  |                 |                 |  |  |

| bit 2                   | CxSP: Comparator Speed/Power Select bit                                                                            |                    |                 |                  |                  |                 |                 |  |  |

|                         | <ol> <li>Comparator mode in normal power, higher speed</li> <li>Comparator mode in low-power, low-speed</li> </ol> |                    |                 |                  |                  |                 |                 |  |  |

| bit 1                   | CxHYS: Comparator Hysteresis Enable bit                                                                            |                    |                 |                  |                  |                 |                 |  |  |

|                         |                                                                                                                    |                    |                 |                  |                  |                 |                 |  |  |

|                         | <ul> <li>1 = Comparator hysteresis enabled</li> <li>0 = Comparator hysteresis disabled</li> </ul>                  |                    |                 |                  |                  |                 |                 |  |  |

| bit 0                   | -                                                                                                                  | omparator Outp     |                 | is Mode bit      |                  |                 |                 |  |  |

|                         |                                                                                                                    | ator output to     | •               |                  | onous to chand   | ges on Timer1   | clock source    |  |  |

|                         |                                                                                                                    |                    |                 |                  |                  |                 |                 |  |  |

|                         | 0 0.00 0.0                                                                                                         | updated on the     | falling edge of | Limer1 clock s   | ource.           |                 |                 |  |  |

### REGISTER 17-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

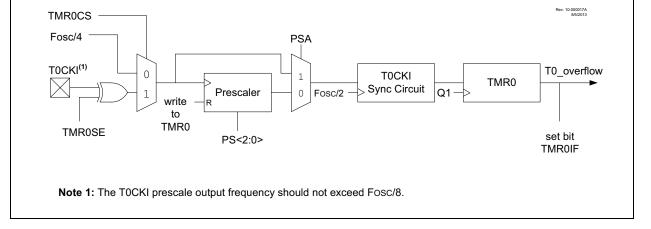

# 18.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 3-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- · TMR0 can be used to gate Timer1

Figure 18-1 is a block diagram of the Timer0 module.

### 18.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

### 18.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

### FIGURE 18-1: TIMER0 BLOCK DIAGRAM

#### 18.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

# **19.6** Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR10N bit of the T1CON register

- TMR1IE bit of the PIE1 register

- · PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

**Note:** The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 19.7 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the T1SYNC bit setting.

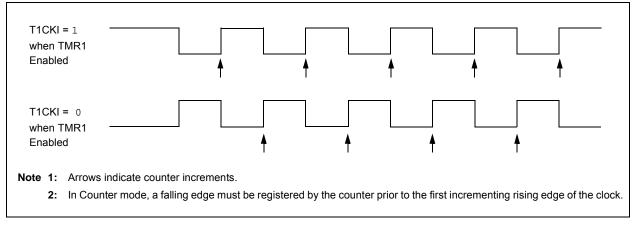

### FIGURE 19-2: TIMER1 INCREMENTING EDGE

### 19.7.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 11.1 "Alternate Pin Function"** for more information.

### 20.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4).

TMR2 increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/ postscaler (see **Section 20.2 "Timer2 Interrupt"**).

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- · a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMR2 is not cleared when T2CON is written.

# 20.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (T2\_match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

### 20.3 Timer2 Output

The output of TMR2 is T2\_match. T2\_match is available to the following peripherals:

- Configurable Logic Cell (CLC)

- Numerically Controlled Oscillator (NCO)

- Pulse Width Modulator (PWM)

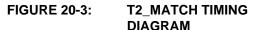

The T2\_match signal is synchronous with the system clock. Figure 20-3 shows two examples of the timing of the T2\_match signal relative to Fosc and prescale value, T2CKPS<1:0>. The upper diagram illustrates 1:1 prescale timing and the lower diagram, 1:X prescale timing.

# 20.4 Timer2 Operation During Sleep

Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

# 22.0 CONFIGURABLE LOGIC CELL (CLC)

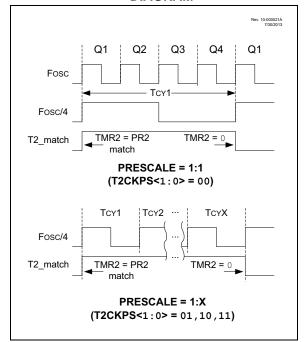

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 16 input signals, and through the use of configurable gates, reduces the 16 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 22-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- · Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

### FIGURE 22-1: CONFIGURABLE LOGIC CELL BLOCK DIAGRAM

| Name     | Bit7     | Bit6        | Bit5        | Bit4     | Blt3        | Bit2              | Bit1          | Bit0     | Register<br>on Page |

|----------|----------|-------------|-------------|----------|-------------|-------------------|---------------|----------|---------------------|

| ANSELA   | _        | _           | _           | ANSA4    | —           | ANSA2             | ANSA1         | ANSA0    | 99                  |

| CLC1CON  | LC1EN    | LC10E       | LC10UT      | LC1INTP  | LC1INTN     | LC1MODE<2:0>      |               |          | 163                 |

| CLCDATA  | _        | _           | —           | —        | —           | MLC3OUT           | MLC2OUT       | MLC1OUT  | 171                 |

| CLC1GLS0 | LC1G1D4T | LC1G1D4N    | LC1G1D3T    | LC1G1D3N | LC1G1D2T    | LC1G1D2N          | LC1G1D1T      | LC1G1D1N | 167                 |

| CLC1GLS1 | LC1G2D4T | LC1G2D4N    | LC1G2D3T    | LC1G2D3N | LC1G2D2T    | LC1G2D2N          | LC1G2D1T      | LC1G2D1N | 168                 |

| CLC1GLS2 | LC1G3D4T | LC1G3D4N    | LC1G3D3T    | LC1G3D3N | LC1G3D2T    | LC1G3D2N          | LC1G3D1T      | LC1G3D1N | 169                 |

| CLC1GLS3 | LC1G4D4T | LC1G4D4N    | LC1G4D3T    | LC1G4D3N | LC1G4D2T    | LC1G4D2N          | LC1G4D1T      | LC1G4D1N | 170                 |

| CLC1POL  | LC1POL   | _           | _           | _        | LC1G4POL    | LC1G3POL LC1G2POL |               | LC1G1POL | 164                 |

| CLC1SEL0 | —        |             | LC1D2S<2:0> |          | —           | – LC1D1S<2:0>     |               |          | 165                 |

| CLC1SEL1 | -        |             | LC1D4S<2:0> |          | —           | LC1D3S<2:0>       |               |          | 166                 |

| CLC2CON  | LC2EN    | LC2OE       | LC2OUT      | LC2INTP  | LC2INTN     | LC2MODE<2:0>      |               |          | 163                 |

| CLC2GLS0 | LC2G1D4T | LC2G1D4N    | LC2G1D3T    | LC2G1D3N | LC2G1D2T    | LC2G1D2N          | LC2G1D1T      | LC2G1D1N | 167                 |

| CLC2GLS1 | LC2G2D4T | LC2G2D4N    | LC2G2D3T    | LC2G2D3N | LC2G2D2T    | LC2G2D2N          | LC2G2D1T      | LC2G2D1N | 168                 |

| CLC2GLS2 | LC2G3D4T | LC2G3D4N    | LC2G3D3T    | LC2G3D3N | LC2G3D2T    | LC2G3D2N          | LC2G3D1T      | LC2G3D1N | 169                 |

| CLC2GLS3 | LC2G4D4T | LC2G4D4N    | LC2G4D3T    | LC2G4D3N | LC2G4D2T    | LC2G4D2N          | LC2G4D1T      | LC2G4D1N | 170                 |

| CLC2POL  | LC2POL   | _           | -           | -        | LC2G4POL    | LC2G3POL LC2G2POI |               | LC2G1POL | 164                 |

| CLC2SEL0 | —        | LC2D2S<2:0> |             |          | —           |                   | 165           |          |                     |

| CLC2SEL1 | —        | LC2D4S<2:0> |             | —        | LC2D3S<2:0> |                   |               | 166      |                     |

| INTCON   | GIE      | PEIE        | TMR0IE      | INTE     | IOCIE       | TMR0IF            | INTF          | IOCIF    | 64                  |

| PIE3     | —        | —           | _           | _        | —           | —                 | - CLC2IE      |          | 67                  |

| PIR3     | _        | _           | _           | _        | —           | —                 | CLC2IF CLC1IF |          | 70                  |

| TRISA    | _        | _           | TRISA5      | TRISA4   | (1)         | TRISA2            | TRISA1        | TRISA0   | 98                  |

# TABLE 22-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

— = unimplemented read as '0',. Shaded cells are not used for CLC module. Unimplemented, read as '1'. Legend: Note 1:

### 24.8 Dead-Band Uncertainty

When the rising and falling edges of the input source triggers the dead-band counters, the input may be asynchronous. This will create some uncertainty in the deadband time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 24-1 for more detail.

### EQUATION 24-1: DEAD-BAND UNCERTAINTY

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

Example:

$$Fcwg\_clock = 16 MHz$$

Therefore:

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

$$= \frac{1}{16 MHz}$$

$$= 62.5 ns$$

## 24.9 Auto-Shutdown Control

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software.

### 24.9.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

### 24.9.1.1 Software Generated Shutdown

Setting the GxASE bit of the CWGxCON2 register will force the CWG into the shutdown state.

When auto-restart is disabled, the shutdown state will persist as long as the GxASE bit is set.

When auto-restart is enabled, the GxASE bit will clear automatically and resume operation on the next rising edge event. See Figure 24-6.

### 24.9.1.2 External Input Source

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Any combination of two input sources can be selected to cause a shutdown condition. The sources are:

- Comparator C1 C1OUT\_async

- CLC2 LC2\_out

- CWG1FLT

Shutdown inputs are selected in the CWGxCON2 register. (Register 24-3).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                   |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |  |  |  |  |  |

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit<br>literal 'k'. The result is placed in the<br>W register. |  |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] TRIS f                                                                                                                                     |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                      |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |  |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

# 27.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:

| Operating Voltage: VDDMIN ≤ VDD ≤ VDDMAX          |     |

|---------------------------------------------------|-----|

| Operating Temperature: $TA_MIN \le TA \le TA_MAX$ |     |

| VDD — Operating Supply Voltage <sup>(1)</sup>     |     |

| PIC12LF1501                                       |     |

| VDDMIN (Fosc $\leq$ 16 MHz) +1.8V                 | /   |

| VDDMIN (16 MHz < Fosc $\leq$ 20 MHz)              | ,   |

| VDDMAX                                            | ,   |

| PIC12F1501                                        |     |

| VDDMIN (Fosc $\leq$ 16 MHz)                       | r - |

| VDDMIN (16 MHz < Fosc $\leq$ 20 MHz) +2.5V        |     |

| VDDMAX                                            | ,   |

| TA — Operating Ambient Temperature Range          |     |

| Industrial Temperature                            |     |

| Ta_min40°C                                        |     |

| Ta_max                                            |     |

| Extended Temperature                              |     |

| Ta_min40°C                                        |     |

| TA_MAX +125°C                                     | ;   |

|                                                   |     |

Note 1: See Parameter D001, DC Characteristics: Supply Voltage.

### TABLE 27-8: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated) |           |                                                          |                    |      |      |      |       |                                        |

|---------------------------------------------------------|-----------|----------------------------------------------------------|--------------------|------|------|------|-------|----------------------------------------|

| Param.<br>No.                                           | Sym.      | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                             |

| OS08                                                    | HFosc     | Internal Calibrated HFINTOSC<br>Frequency <sup>(1)</sup> | ±2%                | —    | 16.0 | _    | MHz   | VDD = 3.0V, TA = 25°C,<br>(Note 2)     |

| OS09                                                    | LFosc     | Internal LFINTOSC Frequency                              | —                  | _    | 31   | _    | kHz   | (Note 3)                               |

| OS10*                                                   | TIOSC ST  | HFINTOSC<br>Wake-up from Sleep Start-up Time             | -                  | _    | 5    | 15   | μS    |                                        |

| OS10A*                                                  | TLFOSC ST | LFINTOSC<br>Wake-up from Sleep Start-up Time             | —                  |      | 0.5  |      | ms    | $-40^\circ C \le T A \le +125^\circ C$ |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

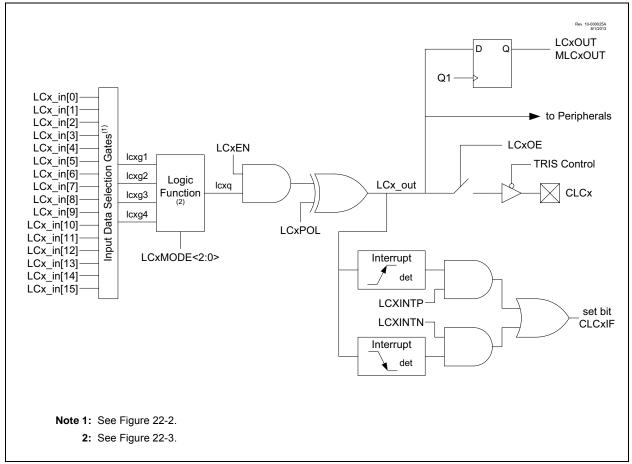

2: See Figure 27-6: "HFINTOSC Frequency Accuracy over Device VDD and Temperature", Figure 28-60: "HFINTOSC Accuracy Over Temperature, VDD = 1.8V, PIC12LF1501 Only", and Figure 28-61: "HFINTOSC Accuracy Over Temperature, 2.3V ≤ VDD ≤ 5.5V".

3: See Figure 28-58: "LFINTOSC Frequency over VDD and Temperature, PIC12LF1501 Only", and Figure 28-59: "LFINTOSC Frequency over VDD and Temperature, PIC12F1501".

### FIGURE 27-6: HFINTOSC FREQUENCY ACCURACY OVER VDD AND TEMPERATURE

# 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility