Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

|                            |                                                                             |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 64 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 4x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-VDFN Exposed Pad                                                          |

| Supplier Device Package    | 8-DFN (3x3)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1501t-i-mf |

#### **TABLE OF CONTENTS**

| 1.0   | Device Overview                                | 7   |

|-------|------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                         | 11  |

| 3.0   | Memory Organization                            | 13  |

| 4.0   | Device Configuration                           | 37  |

| 5.0   | Oscillator Module                              | 42  |

| 6.0   | Resets                                         | 51  |

| 7.0   | Interrupts                                     | 59  |

| 8.0   | Power-Down Mode (Sleep)                        | 72  |

| 9.0   | Watchdog Timer (WDT)                           | 75  |

| 10.0  | Flash Program Memory Control                   | 79  |

|       | I/O Ports                                      |     |

| 12.0  | Interrupt-On-Change                            | 101 |

| 13.0  | Fixed Voltage Reference (FVR)                  | 105 |

| 14.0  | Temperature Indicator Module                   | 108 |

| 15.0  | Analog-to-Digital Converter (ADC) Module       | 110 |

| 16.0  | 5-Bit Digital-to-Analog Converter (DAC) Module | 124 |

| 17.0  | Comparator Module                              | 127 |

| 18.0  | Timer0 Module                                  | 134 |

| 19.0  | Timer1 Module with Gate Control                | 137 |

| 20.0  | Timer2 Module                                  | 148 |

| 21.0  | Pulse-Width Modulation (PWM) Module            | 151 |

|       | Configurable Logic Cell (CLC)                  |     |

| 23.0  | Numerically Controlled Oscillator (NCO) Module | 173 |

|       | Complementary Waveform Generator (CWG) Module  |     |

| 25.0  | In-Circuit Serial Programming™ (ICSP™)         | 192 |

|       | Instruction Set Summary                        |     |

| 27.0  | Electrical Specifications                      | 209 |

| 28.0  | DC and AC Characteristics Graphs and Charts    | 232 |

|       | Development Support                            |     |

| 30.0  | Packaging Information                          | 271 |

| Appe  | ndix A: Data Sheet Revision History            | 288 |

|       | ficrochip Website                              |     |

| Custo | mer Change Notification Service                | 289 |

| Custo | mer Support                                    | 289 |

| Produ | ıct Identification System                      | 290 |

DS40001615C-page 19

#### 3.3.5 DEVICE MEMORY MAPS

The memory maps for Bank 0 through Bank 31 are shown in the tables in this section.

| <b>TABLE 3-3:</b> | PIC12(L)F1501 | MEMORY MAP |

|-------------------|---------------|------------|

|-------------------|---------------|------------|

|               | BANK 0                      |              | BANK 1                       |              | BANK 2                       |               | BANK 3                       |              | BANK 4                       |              | BANK 5                       |              | BANK 6                       |              | BANK 7                       |

|---------------|-----------------------------|--------------|------------------------------|--------------|------------------------------|---------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|

| 000h          |                             | 080h         |                              | 100h         |                              | 180h          |                              | 200h         |                              | 280h         |                              | 300h         |                              | 380h         |                              |

|               | Core Registers              |              | Core Registers               |              | Core Registers               |               | Core Registers               |              | Core Registers               |              | Core Registers               |              | Core Registers               |              | Core Registers               |

|               | (Table 3-2)                 |              | (Table 3-2)                  |              | (Table 3-2)                  |               | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |              | (Table 3-2)                  |

| 00Bh          |                             | 08Bh         |                              | 10Bh         |                              | 18Bh          |                              | 20Bh         |                              | 28Bh         |                              | 30Bh         |                              | 38Bh         |                              |

| 00Ch          | PORTA                       | 08Ch         | TRISA                        | 10Ch         | LATA                         | 18Ch          | ANSELA                       | 20Ch         | WPUA                         | 28Ch         | _                            | 30Ch         | _                            | 38Ch         | _                            |

| 00Dh          | _                           | 08Dh         | _                            | 10Dh         | _                            | 18Dh          | _                            | 20Dh         | _                            | 28Dh         | _                            | 30Dh         | _                            | 38Dh         | _                            |

| 00Eh          | _                           | 08Eh         | _                            | 10Eh         | _                            | 18Eh          | _                            | 20Eh         | _                            | 28Eh         | _                            | 30Eh         | _                            | 38Eh         | _                            |

| 00Fh          | _                           | 08Fh         | _                            | 10Fh         | _                            | 18Fh          | _                            | 20Fh         | _                            | 28Fh         | _                            | 30Fh         | _                            | 38Fh         | _                            |

| 010h          | _                           | 090h         | _                            | 110h         | _                            | 190h          | _                            | 210h         | _                            | 290h         | _                            | 310h         | _                            | 390h         | _                            |

| 011h          | PIR1                        | 091h         | PIE1                         | 111h         | CM1CON0                      | 191h          | PMADRL                       | 211h         | _                            | 291h         | _                            | 311h         | _                            | 391h         | IOCAP                        |

| 012h          | PIR2                        | 092h         | PIE2                         | 112h         | CM1CON1                      | 192h          | PMADRH                       | 212h         | _                            | 292h         | _                            | 312h         | _                            | 392h         | IOCAN                        |

| 013h          | PIR3                        | 093h         | PIE3                         | 113h         |                              | 193h          | PMDATL                       | 213h         |                              | 293h         | _                            | 313h         | _                            | 393h         | IOCAF                        |

| 014h          | TMR0                        | 094h         | OPTION REG                   | 114h         | <br>CMOUT                    | 194h          | PMDATH                       | 214h         |                              | 294h         | _                            | 314h         |                              | 394h         | _                            |

| 015h<br>016h  | TMR0<br>TMR1L               | 095h<br>096h | PCON PCON                    | 115h<br>116h | BORCON                       | 195h<br>196h  | PMCON1<br>PMCON2             | 215h<br>216h | _                            | 295h<br>296h |                              | 315h<br>316h |                              | 395h<br>396h | _                            |

| 016H<br>017h  | TMR1H                       | 090h         | WDTCON                       | 117h         | FVRCON                       | 19011<br>197h | VREGCON                      | 217h         |                              | 297h         |                              | 317h         |                              | 397h         | _                            |

| 01711<br>018h | T1CON                       | 098h         | WB10011                      | 118h         | DACCON0                      | 198h          | —                            | 218h         |                              | 298h         | _                            | 318h         | _                            | 398h         | _                            |

| 019h          | TIGCON                      | 099h         | OSCCON                       | 119h         | DACCON0<br>DACCON1           | 199h          |                              | 219h         |                              | 299h         | _                            | 319h         | _                            | 399h         | _                            |

| 019II<br>01Ah | TMR2                        | 09Ah         | OSCSTAT                      | 11Ah         | —                            | 19Ah          |                              | 21Ah         |                              | 29Ah         | _                            | 31Ah         | _                            | 39Ah         | _                            |

| -             | PR2                         | 09Bh         | ADRESL                       | 11Bh         |                              | 19Bh          |                              | 21Bh         | _                            | 29Bh         | _                            | 31Bh         | _                            | 39Bh         | _                            |

| 01Bh          | T2CON                       | 09Ch         | ADRESH                       | 11Ch         |                              | 19Ch          |                              | 21Ch         |                              | 29Ch         |                              | 31Ch         |                              | 39Ch         | _                            |

| 01Ch          | TZCON                       |              | _                            |              |                              |               | _                            | -            |                              |              | _                            |              | _                            |              |                              |

| 01Dh          | _                           | 09Dh         | ADCON0                       | 11Dh         | APFCON                       | 19Dh          | _                            | 21Dh         | _                            | 29Dh         | _                            | 31Dh         | _                            | 39Dh         |                              |

| 01Eh          |                             | 09Eh         | ADCON1                       | 11Eh         |                              | 19Eh          |                              | 21Eh         | _                            | 29Eh         | _                            | 31Eh         | _                            | 39Eh         | _                            |

| 01Fh          | _                           | 09Fh<br>0A0h | ADCON2                       | 11Fh         |                              | 19Fh          |                              | 21Fh         | _                            | 29Fh         | _                            | 31Fh         |                              | 39Fh         | _                            |

| 020h          | OI D                        | UAUII        |                              | 120h         |                              | 1A0h          |                              | 220h         |                              | 2A0h         |                              | 320h         |                              | 3A0h         |                              |

|               | General Purpose<br>Register |              |                              |              |                              |               |                              |              |                              |              |                              |              |                              |              |                              |

|               | 48 Bytes                    |              | 11.2                         |              | 11.2                         |               | l lainealaneanta d           |              | l ladan la anamta d          |              | l la incula un cuta d        |              |                              |              | l la incole no cata d        |

| 04Fh          | .0 2 ) 100                  |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |               | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |

| 050h          |                             |              | Neau as 0                    |              | ineau as 0                   |               | Neau as 0                    |              | Neau as 0                    |              | Neau as 0                    |              | ixeau as 0                   |              | ineau as 0                   |

| 00011         | Unimplemented               |              |                              |              |                              |               |                              |              |                              |              |                              |              |                              |              |                              |

|               | Read as '0'                 | 0EFh         |                              | 4051         |                              |               |                              | 0051         |                              | 0==1         |                              | 36Fh         |                              | 3EFh         |                              |

| 06Fh<br>070h  |                             | 0EFn<br>0F0h |                              | 16Fh<br>170h |                              | 1EFh<br>1F0h  |                              | 26Fh<br>270h |                              | 2EFh<br>2F0h |                              | 370h         |                              | 3F0h         |                              |

| 07011         |                             | 01 011       | Common RAM                   | 17011        | Common RAM                   | 11 011        | Common RAM                   | 27011        | Common RAM                   | 21 011       | Common RAM                   | 37011        | Common RAM                   | 31 011       | Common RAM                   |

|               | Common RAM                  |              | (Accesses                    |              | (Accesses                    |               | (Accesses                    |              | (Accesses                    |              | (Accesses                    |              | (Accesses                    |              | (Accesses                    |

| 07Fh          |                             | 0FFh         | 70h – 7Fh)                   | 17Fh         | 70h – 7Fh)                   | 1FFh          | 70h – 7Fh)                   | 27Fh         | 70h – 7Fh)                   | 2FFh         | 70h – 7Fh)                   | 37Fh         | 70h – 7Fh)                   | 3FFh         | 70h – 7Fh)                   |

| UIFII         |                             | OFFII        |                              | 17 [1]       |                              | ILLII         |                              | 21 [1]       |                              | 25511        |                              | SIFII        |                              | SEE          |                              |

Legend

= Unimplemented data memory locations, read as '0'

DS40001615C-page 20

Legend:

= Unimplemented data memory locations, read as '0'

| TABL   | _E 3-3: P                     | IC12(   | L)F1501 MEI                   | MOR    | Y MAP (CON                    | TINU  | ED)                           |       |                               |       |                               |       |                               |         |                               |

|--------|-------------------------------|---------|-------------------------------|--------|-------------------------------|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|---------|-------------------------------|

|        | BANK 8                        | _       | BANK 9                        | _      | BANK 10                       | _     | BANK 11                       | _     | BANK 12                       | _     | BANK 13                       |       | BANK 14                       |         | BANK 15                       |

| 400h   | Core Registers<br>(Table 3-2) | 480h    | Core Registers<br>(Table 3-2) | 500h   | Core Registers<br>(Table 3-2) | 580h  | Core Registers<br>(Table 3-2) | 600h  | Core Registers<br>(Table 3-2) | 680h  | Core Registers<br>(Table 3-2) | 700h  | Core Registers<br>(Table 3-2) | 780h    | Core Registers<br>(Table 3-2) |

| 40Bh   | ,                             | 48Bh    | , ,                           | 50Bh   | , i                           | 58Bh  | , , , ,                       | 60Bh  | , ,                           | 68Bh  | , ,                           | 70Bh  | , ,                           | 78Bh    | , , , ,                       |

| 40Ch   | _                             | 48Ch    | _                             | 50Ch   | _                             | 58Ch  | _                             | 60Ch  | _                             | 68Ch  | _                             | 70Ch  | _                             | 78Ch    | _                             |

| 40Dh   | _                             | 48Dh    | _                             | 50Dh   | _                             | 58Dh  | _                             | 60Dh  | _                             | 68Dh  | _                             | 70Dh  | _                             | 78Dh    | _                             |

| 40Eh   | _                             | 48Eh    | _                             | 50Eh   | _                             | 58Eh  | _                             | 60Eh  | _                             | 68Eh  | _                             | 70Eh  | _                             | 78Eh    | _                             |

| 40Fh   | _                             | 48Fh    | _                             | 50Fh   | _                             | 58Fh  | _                             | 60Fh  | _                             | 68Fh  | _                             | 70Fh  | _                             | 78Fh    | _                             |

| 410h   | _                             | 490h    | _                             | 510h   | _                             | 590h  | _                             | 610h  | _                             | 690h  | _                             | 710h  | _                             | 790h    | _                             |

| 411h   | _                             | 491h    | _                             | 511h   | _                             | 591h  | _                             | 611h  | PWM1DCL                       | 691h  | CWG1DBR                       | 711h  | _                             | 791h    | _                             |

| 412h   | ı                             | 492h    |                               | 512h   |                               | 592h  | _                             | 612h  | PWM1DCH                       | 692h  | CWG1DBF                       | 712h  |                               | 792h    | _                             |

| 413h   | _                             | 493h    | _                             | 513h   | _                             | 593h  | _                             | 613h  | PWM1CON                       | 693h  | CWG1CON0                      | 713h  | _                             | 793h    | _                             |

| 414h   | ı                             | 494h    |                               | 514h   |                               | 594h  | _                             | 614h  | PWM2DCL                       | 694h  | CWG1CON1                      | 714h  |                               | 794h    | _                             |

| 415h   |                               | 495h    |                               | 515h   |                               | 595h  | _                             | 615h  | PWM2DCH                       | 695h  | CWG1CON2                      | 715h  |                               | 795h    | _                             |

| 416h   | I                             | 496h    | I                             | 516h   | I                             | 596h  | _                             | 616h  | PWM2CON                       | 696h  |                               | 716h  | I                             | 796h    | _                             |

| 417h   | _                             | 497h    | _                             | 517h   | _                             | 597h  | _                             | 617h  | PWM3DCL                       | 697h  | _                             | 717h  | _                             | 797h    | _                             |

| 418h   |                               | 498h    | NCO1ACCL                      | 518h   |                               | 598h  | _                             | 618h  | PWM3DCH                       | 698h  |                               | 718h  |                               | 798h    | _                             |

| 419h   |                               | 499h    | NCO1ACCH                      | 519h   | _                             | 599h  | _                             | 619h  | PWM3CON                       | 699h  | _                             | 719h  | _                             | 799h    | _                             |

| 41Ah   | _                             | 49Ah    | NCO1ACCU                      | 51Ah   | _                             | 59Ah  | _                             | 61Ah  | PWM4DCL                       | 69Ah  | _                             | 71Ah  | _                             | 79Ah    | _                             |

| 41Bh   |                               | 49Bh    | NCO1INCL                      | 51Bh   | _                             | 59Bh  | _                             | 61Bh  | PWM4DCH                       | 69Bh  | _                             | 71Bh  | _                             | 79Bh    | _                             |

| 41Ch   | _                             | 49Ch    | NCO1INCH                      | 51Ch   | _                             | 59Ch  | _                             | 61Ch  | PWM4CON                       | 69Ch  | _                             | 71Ch  | _                             | 79Ch    | _                             |

| 41Dh   | _                             | 49Dh    | _                             | 51Dh   | _                             | 59Dh  | _                             | 61Dh  | _                             | 69Dh  | _                             | 71Dh  |                               | 79Dh    | _                             |

| 41Eh   | _                             | 49Eh    | NCO1CON                       | 51Eh   | _                             | 59Eh  | _                             | 61Eh  |                               | 69Eh  | _                             | 71Eh  | _                             | 79Eh    |                               |

| 41Fh   | _                             | 49Fh    | NCO1CLK                       | 51Fh   | _                             | 59Fh  | _                             | 61Fh  | _                             | 69Fh  | _                             | 71Fh  | _                             | 79Fh    | _                             |

| 420h   |                               | 4A0h    |                               | 520h   |                               | 5A0h  |                               | 620h  |                               | 6A0h  |                               | 720h  |                               | 7A0h    |                               |

|        | Unimplemented<br>Read as '0'  |         | Unimplemented<br>Read as '0'  |        | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |       | Unimplemented<br>Read as '0'  |         | Unimplemented<br>Read as '0'  |

| 46Fh   |                               | 4EFh    |                               | 56Fh   |                               | 5EFh  |                               | 66Fh  |                               | 6EFh  |                               | 76Fh  |                               | 7EFh    |                               |

| 470h   |                               | 4F0h    |                               | 570h   |                               | 5F0h  |                               | 670h  |                               | 6F0h  |                               | 770h  |                               | 7F0h    |                               |

|        | Common RAM                    |         | Common RAM                    |        | Common RAM                    |       | Common RAM                    |       | Common RAM                    |       | Common RAM                    |       | Common RAM                    |         | Common RAM                    |

|        | (Accesses                     |         | (Accesses                     |        | (Accesses                     |       | (Accesses                     |       | (Accesses                     |       | (Accesses                     |       | (Accesses                     |         | (Accesses                     |

| 47Fh   | 70h – 7Fh)                    | 4FFh    | 70h – 7Fh)                    | 57Fh   | 70h – 7Fh)                    | 5FFh  | 70h – 7Fh)                    | 67Fh  | 70h – 7Fh)                    | 6FFh  | 70h – 7Fh)                    | 77Fh  | 70h – 7Fh)                    | 7FFh    | 70h – 7Fh)                    |

| 4/1711 |                               | J 4FFII |                               | 37 FII |                               | SEEII |                               | 0/11  |                               | OFFII |                               | // [  |                               | ] /FFII |                               |

|        | BANK 16                       |         | BANK 17                       |        | BANK 18                       |       | BANK 19                       |       | BANK 20                       |       | BANK 21                       |       | BANK 22                       |         | BANK 23                       |

| 800h   |                               | 880h    |                               | 900h   |                               | 980h  |                               | A00h  |                               | A80h  |                               | B00h  |                               | B80h    |                               |

|        | Core Registers<br>(Table 3-2) |         | Core Registers<br>(Table 3-2) |        | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |         | Core Registers<br>(Table 3-2) |

| 80Bh   | ,                             | 88Bh    | ( ,                           | 90Bh   | ( /                           | 98Bh  | ( ,                           | A0Bh  | ( ,                           | A8Bh  | ( ,                           | B0Bh  | ( ,                           | B8Bh    | , , , , ,                     |

| 80Ch   |                               | 88Ch    |                               | 90Ch   |                               | 98Ch  |                               | A0Ch  |                               | A8Ch  |                               | B0Ch  |                               | B8Ch    |                               |

| 80CII  | Unimplemented<br>Read as '0'  | OOCII   | Unimplemented<br>Read as '0'  | 90011  | Unimplemented<br>Read as '0'  | 90011 | Unimplemented<br>Read as '0'  | AUCII | Unimplemented<br>Read as '0'  | Aocii | Unimplemented<br>Read as '0'  | BUCII | Unimplemented<br>Read as '0'  | Boon    | Unimplemented<br>Read as '0'  |

|        | incau as 0                    |         | incau as 0                    |        | incau as 0                    |       | incau as 0                    | l     | incau as 0                    |       | ixeau as 0                    |       | ixeau as 0                    |         |                               |

| 86Fh   |                               | 8EFh    |                               | 96Fh   |                               | 9EFh  |                               | A6Fh  |                               | AEFh  |                               | B6Fh  |                               | BEFh    |                               |

| 870h   | Common RAM<br>(Accesses       | 8F0h    | Common RAM<br>(Accesses       | 970h   | Common RAM<br>(Accesses       | 9F0h  | Common RAM<br>(Accesses       | A70h  | Common RAM<br>(Accesses       | AF0h  | Common RAM<br>(Accesses       | B70h  | Common RAM<br>(Accesses       | BF0h    | Common RAM<br>(Accesses       |

| 87Fh   | 70h – 7Fh)                    | 8FFh    | 70h – 7Fh)                    | 97Fh   | 70h – 7Fh)                    | 9FFh  | 70h – 7Fh)                    | A7Fh  | 70h – 7Fh)                    | AFFh  | 70h – 7Fh)                    | B7Fh  | 70h – 7Fh)                    | BFFh    | 70h – 7Fh)                    |

#### 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP}=0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See Section 4.4 "Write Protection" for more information.

#### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

#### 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 10.4 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification" (DS41573).

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| U-0   | U-0 | U-0 | R-0/q  | U-0 | U-0 | R-0/q  | R-0/q  |

|-------|-----|-----|--------|-----|-----|--------|--------|

| _     | _   | _   | HFIOFR | _   | -   | LFIOFR | HFIOFS |

| bit 7 |     |     |        |     |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Conditional

bit 7-5 **Unimplemented:** Read as '0'

bit 4 HFIOFR: High-Frequency Internal Oscillator Ready bit

1 = HFINTOSC is ready

0 = HFINTOSC is not ready

bit 3-2 **Unimplemented:** Read as '0'

bit 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit

1 = LFINTOSC is ready

0 = LFINTOSC is not ready

bit 0 HFIOFS: High-Frequency Internal Oscillator Stable bit

1 = HFINTOSC 16 MHz Oscillator is stable and is driving the INTOSC

0 = HFINTOSC 16 MHz is not stable, the Start-up Oscillator is driving INTOSC

#### TABLE 5-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Register on Page |

|---------|-------|-------|-------|--------|-------|-------|--------|--------|------------------|

| OSCCON  | _     |       | IRCF  | <3:0>  |       | _     | SCS    | 49     |                  |

| OSCSTAT | _     | _     | _     | HFIOFR | _     | _     | LFIOFR | HFIOFS | 50               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 5-4: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|------------------|

| CONFICA | 13:8 | 1       | _       |          | _        | CLKOUTEN | BOREI    | N<1:0>  | -       | 20               |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | _        | FOSC    | <1:0>   | 38               |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|-----|-----|-----|---------|---------|

| TMR1GIF | ADIF    | _   | _   | _   | _   | TMR2IF  | TMR1IF  |

| bit 7   |         |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 TMR1GIF: Timer1 Gate Interrupt Flag bit

1 = Interrupt is pending

0 = Interrupt is not pending

bit 6 ADIF: ADC Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 5-2 **Unimplemented:** Read as '0'

bit 1 TMR2IF: Timer2 to PR2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 0 TMR1IF: Timer1 Overflow Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of

its corresponding enable bit or the Global Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

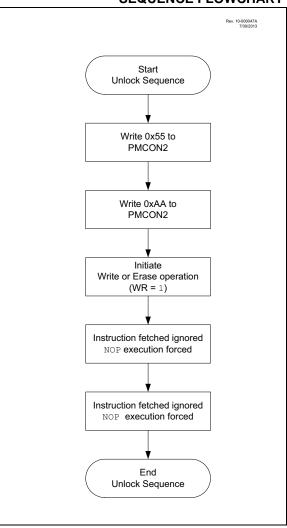

## 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- · Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two  $\mathtt{NOP}$  instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two  $\mathtt{NOP}$  instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

# FIGURE 10-3: FLASH PROGRAM MEMORY UNLOCK SEQUENCE FLOWCHART

#### **EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY**

```

; This row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

BCF

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

PMADRL

MOVF

ADDRL,W

; Load lower 8 bits of erase address boundary

MOVWF

PMADRL

MOVF

ADDRH,W

; Load upper 6 bits of erase address boundary

MOVWF

PMADRH

BCF

PMCON1,CFGS

; Not configuration space

PMCON1, FREE

; Specify an erase operation

BSF

BSF

PMCON1,WREN

; Enable writes

MOVLW

55h

; Start of required sequence to initiate erase

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin erase

NOP

; NOP instructions are forced as processor starts

NOP

; row erase of program memory.

; The processor stalls until the erase process is complete

; after erase processor continues with 3rd instruction

BCF

PMCON1, WREN

; Disable writes

INTCON, GIE

; Enable interrupts

BSF

```

#### 15.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register).

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time(2).

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- Read ADC Result.

- Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 15.4 "ADC Acquisition Requirements".

#### **EXAMPLE 15-1: ADC CONVERSION**

```

; This code block configures the ADC

;for polling, Vdd and Vss references, FRC

; oscillator and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL

ADCON1

B'11110000' ; Right justify, FRC

MOVLW

;oscillator

MOVWF

ADCON1

; Vdd and Vss Vref+

BANKSEL

TRISA

TRISA,0

;Set RAO to input

BSF

BANKSEL

ANSEL

BSF

ANSEL, 0

;Set RAO to analog

BANKSEL

WPUA

BCF

WPUA,0

;Disable weak

pull-up on RA0

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWF

ADCON0

;Turn ADC On

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

;No, test again

$-1

BANKSEL

ADRESH

MOVF

ADRESH,W ;Read upper 2 bits

MOVWF

RESULTHI ;store in GPR space

BANKSEL

ADRESL

ADRESL, W

;Read lower 8 bits

MOVF

MOVWF

RESULTLO

;Store in GPR space

```

#### 23.2 Fixed Duty Cycle (FDC) Mode

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 23-2.

The FDC mode is selected by clearing the NxPFM bit in the NCOxCON register.

#### 23.3 Pulse Frequency (PF) Mode

In Pulse Frequency (PF) mode, every time the accumulator overflows (NCO\_overflow), the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output.

The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 23-2.

The value of the active and inactive states depends on the polarity bit, NxPOL in the NCOxCON register.

The PF mode is selected by setting the NxPFM bit in the NCOxCON register.

#### 23.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the NxPWS<2:0> bits in the NCOxCLK register.

When the selected pulse width is greater than the accumulator overflow time frame, the output of the NCOx operation is indeterminate.

#### 23.4 Output Polarity Control

The last stage in the NCOx module is the output polarity. The NxPOL bit in the NCOxCON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCOx output can be used internally by source code or other peripherals. Accomplish this by reading the NxOUT (read-only) bit of the NCOxCON register.

The NCOx output signal is available to the following peripherals:

- CLC

- CWG

#### 23.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCOx Interrupt Flag bit, NCOxIF, of the PIRx register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- · NxEN bit of the NCOxCON register

- · NCOxIE bit of the PIEx register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCOxIF bit in the Interrupt Service Routine.

#### 23.6 Effects of a Reset

All of the NCOx registers are cleared to zero as the result of a Reset.

#### 23.7 Operation In Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 23.8 Alternate Pin Locations

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 11.1 "Alternate Pin Function"** for more information.

DS40001615C-page 183

#### 27.0 ELECTRICAL SPECIFICATIONS

### 27.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias40°C to +125°C                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage temperature65°C to +150°C                                                                                                                                                                                                                                                           |

| Voltage on pins with respect to Vss                                                                                                                                                                                                                                                         |

| on VDD pin                                                                                                                                                                                                                                                                                  |

| PIC12F15010.3V to +6.5V                                                                                                                                                                                                                                                                     |

| PIC12LF15010.3V to +4.0V                                                                                                                                                                                                                                                                    |

| on MCLR pin0.3V to +9.0V                                                                                                                                                                                                                                                                    |

| on all other pins0.3V to (VDD + 0.3V)                                                                                                                                                                                                                                                       |

| Maximum current                                                                                                                                                                                                                                                                             |

| on Vss pin <sup>(1)</sup>                                                                                                                                                                                                                                                                   |

| -40°C ≤ TA ≤ +85°C                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                             |

| +85°C ≤ TA ≤ +125°C                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                             |

| +85°C ≤ TA ≤ +125°C                                                                                                                                                                                                                                                                         |

| $+85^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ 85 mA on VDD pin <sup>(1)</sup>                                                                                                                                                                                              |

| $+85^{\circ}C \leq TA \leq +125^{\circ}C \qquad \qquad 85 \text{ mA}$ on VDD pin <sup>(1)</sup> $-40^{\circ}C \leq TA \leq +85^{\circ}C \qquad \qquad 250 \text{ mA}$                                                                                                                       |

| $+85^{\circ}C \leq TA \leq +125^{\circ}C \\ \text{on VDD pin}^{(1)} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \\ +85^{\circ}C \leq TA \leq +125^{\circ}C \\ 85 \text{ mA}$                                                                                                                  |

| $+85^{\circ}C \leq TA \leq +125^{\circ}C \\ \text{on V}_{DD} \text{ pin}^{\text{(1)}} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \\ +85^{\circ}C \leq TA \leq +125^{\circ}C \\ \text{Sunk by any standard I/O pin} \\ 85 \text{ mA} \\ \text{Sunk by any standard I/O pin} \\ 85 \text{ mA}$ |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 27-6 to calculate device specifications.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

<sup>2:</sup> Power dissipation is calculated as follows: PDIS = VDD x {IDD  $- \Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$ (VOI x IOL).

TABLE 27-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

| PIC12LF | 1501            | Stand | ard Opera | ating Con | ditions (u | ınless otl  | herwise stated)                            |

|---------|-----------------|-------|-----------|-----------|------------|-------------|--------------------------------------------|

| PIC12F1 | 501             |       |           |           |            |             |                                            |

| Param.  | Device          |       |           |           |            |             | Conditions                                 |

| No.     | Characteristics | Min.  | Тур†      | Max.      | Units      | <b>V</b> DD | Note                                       |

| D013    |                 | _     | 30        | 65        | μА         | 1.8         | Fosc = 1 MHz,                              |

|         |                 | _     | 55        | 100       | μΑ         | 3.0         | External Clock (ECM),<br>Medium Power mode |

| D013    |                 | _     | 65        | 110       | μΑ         | 2.3         | Fosc = 1 MHz,                              |

|         |                 | _     | 85        | 140       | μА         | 3.0         | External Clock (ECM),  Medium Power mode   |

|         |                 | —     | 115       | 190       | μΑ         | 5.0         | Medium Power mode                          |

| D014    |                 |       | 115       | 190       | μΑ         | 1.8         | Fosc = 4 MHz,                              |

|         |                 | _     | 210       | 310       | μΑ         | 3.0         | External Clock (ECM),<br>Medium Power mode |

| D014    |                 | _     | 180       | 270       | μΑ         | 2.3         | Fosc = 4 MHz,                              |

|         |                 | _     | 240       | 365       | μΑ         | 3.0         | External Clock (ECM),                      |

|         |                 | _     | 295       | 460       | μΑ         | 5.0         | Medium Power mode                          |

| D015    |                 | _     | 3.2       | 12        | μΑ         | 1.8         | Fosc = 31 kHz,                             |

|         |                 | _     | 5.4       | 20        | μΑ         | 3.0         | LFINTOSC,<br>-40°C ≤ TA ≤ +85°C            |

| D015    |                 | _     | 13        | 28        | μΑ         | 2.3         | Fosc = 31 kHz,                             |

|         |                 | _     | 15        | 30        | μΑ         | 3.0         | LFINTOSC,                                  |

|         |                 | _     | 17        | 36        | μΑ         | 5.0         | -40°C ≤ TA ≤ +85°C                         |

| D016    |                 | _     | 215       | 360       | μΑ         | 1.8         | Fosc = 500 kHz,                            |

|         |                 | _     | 275       | 480       | μΑ         | 3.0         | HFINTOSC                                   |

| D016    |                 | _     | 270       | 450       | μΑ         | 2.3         | Fosc = 500 kHz,                            |

|         |                 | _     | 300       | 500       | μΑ         | 3.0         | HFINTOSC                                   |

|         |                 | _     | 350       | 620       | μΑ         | 5.0         |                                            |

| D017*   |                 |       | 410       | 660       | μΑ         | 1.8         | Fosc = 8 MHz,                              |

|         |                 | _     | 630       | 970       | μΑ         | 3.0         | HFINTOSC                                   |

| D017*   |                 | _     | 530       | 750       | μΑ         | 2.3         | Fosc = 8 MHz,                              |

|         |                 | _     | 660       | 1100      | μΑ         | 3.0         | HFINTOSC                                   |

|         |                 |       | 730       | 1200      | μΑ         | 5.0         |                                            |

| D018    |                 | _     | 600       | 940       | μΑ         | 1.8         | Fosc = 16 MHz,                             |

|         |                 |       | 970       | 1400      | μΑ         | 3.0         | HFINTOSC                                   |

| D018    |                 |       | 780       | 1200      | μΑ         | 2.3         | Fosc = 16 MHz,                             |

|         |                 | _     | 1000      | 1550      | μΑ         | 3.0         | HFINTOSC                                   |

|         |                 |       | 1090      | 1700      | μΑ         | 5.0         |                                            |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

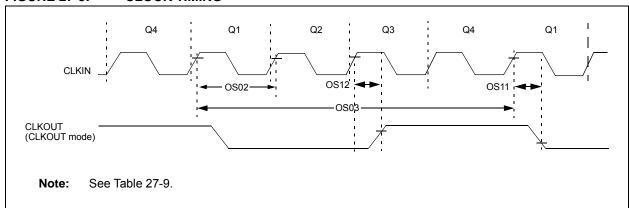

#### FIGURE 27-5: CLOCK TIMING

#### TABLE 27-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

| Param. | Sym. | Characteristic                          | Min. | Тур† | Max. | Units   | Conditions           |

|--------|------|-----------------------------------------|------|------|------|---------|----------------------|

|        | F000 | Estamal CLKIN Francisco (1)             | DC   |      | 0.5  | N 41.1— | Estamal Clask (ECL)  |

| OS01   | Fosc | External CLKIN Frequency <sup>(1)</sup> | DC   | _    | 0.5  | MHz     | External Clock (ECL) |

|        |      |                                         | DC   | _    | 4    | MHz     | External Clock (ECM) |

|        |      |                                         | DC   | _    | 20   | MHz     | External Clock (ECH) |

| OS02   | Tosc | External CLKIN Period <sup>(1)</sup>    | 50   | _    | ∞    | ns      | External Clock (EC)  |

| OS03   | TCY  | Instruction Cycle Time <sup>(1)</sup>   | 200  | Tcy  | DC   | ns      | Tcy = 4/Fosc         |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

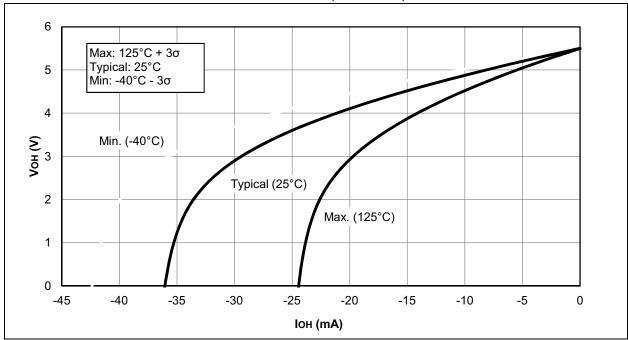

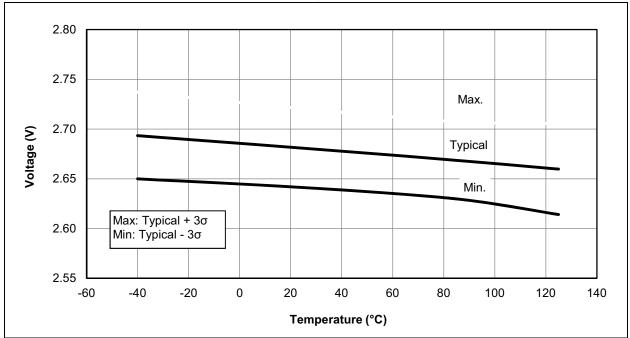

FIGURE 28-35: Voh vs. Ioh OVER TEMPERATURE, VDD = 5.5V, PIC12F1501 ONLY

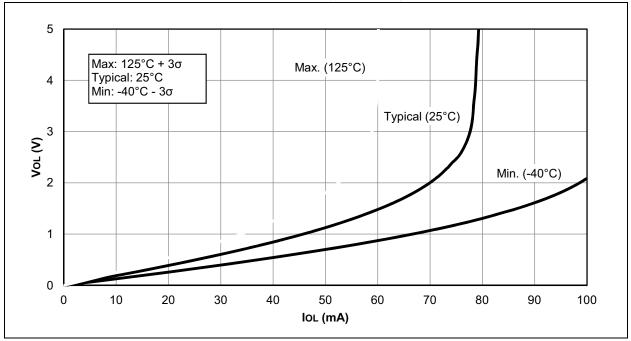

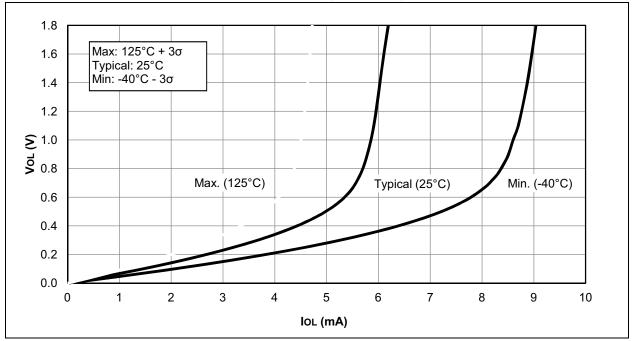

FIGURE 28-36: Vol vs. Iol OVER TEMPERATURE, VDD = 5.5V, PIC12F1501 ONLY

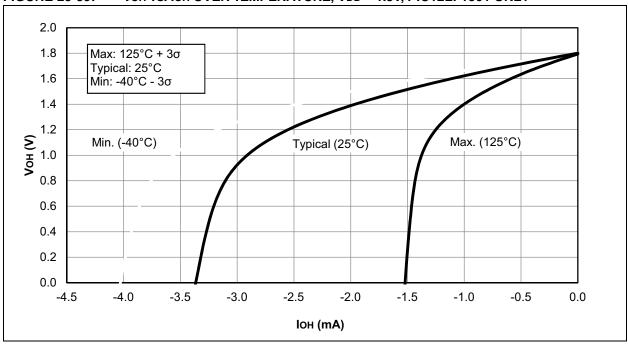

FIGURE 28-39: VOH VS. IOH OVER TEMPERATURE, VDD = 1.8V, PIC12LF1501 ONLY

FIGURE 28-40: Vol vs. Iol OVER TEMPERATURE, VDD = 1.8V, PIC12LF1501 ONLY

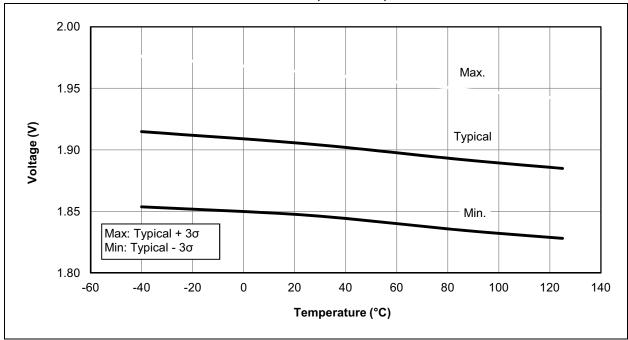

FIGURE 28-43: BROWN-OUT RESET VOLTAGE, BORV = 1, PIC12LF1501 ONLY

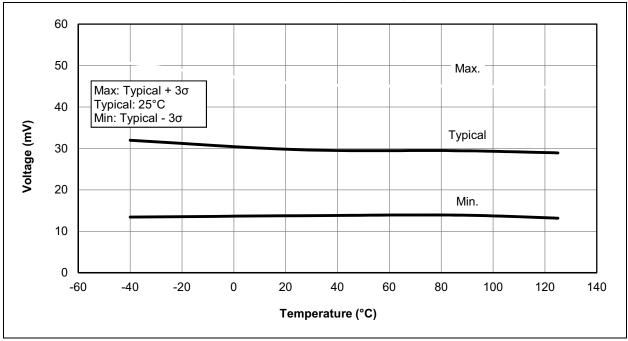

FIGURE 28-44: BROWN-OUT RESET HYSTERESIS, BORV = 1, PIC12LF1501 ONLY

# 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoQ® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

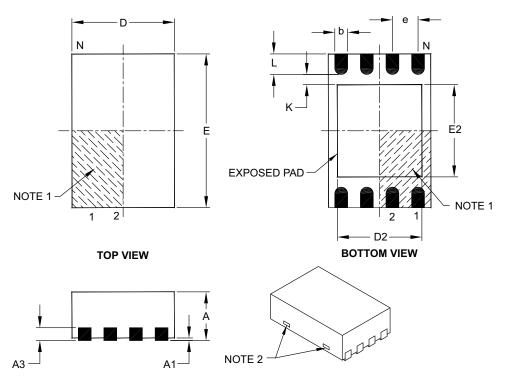

#### 8-Lead Plastic Dual Flat, No Lead Package (MC) - 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          | MILLIMETERS |      |  |

|------------------------|-------|----------|-------------|------|--|

| Dimension Limits       |       | MIN      | NOM         | MAX  |  |

| Number of Pins         | N     | 8        |             |      |  |

| Pitch                  | е     | 0.50 BSC |             |      |  |

| Overall Height         | Α     | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1    | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | А3    | 0.20 REF |             |      |  |

| Overall Length         | D     | 2.00 BSC |             |      |  |

| Overall Width          | Е     | 3.00 BSC |             |      |  |

| Exposed Pad Length     | D2    | 1.30     | _           | 1.55 |  |

| Exposed Pad Width      | E2    | 1.50     | _           | 1.75 |  |

| Contact Width          | b     | 0.20     | 0.25        | 0.30 |  |

| Contact Length         | L     | 0.30     | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | K     | 0.20     | _           | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C