Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 64 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

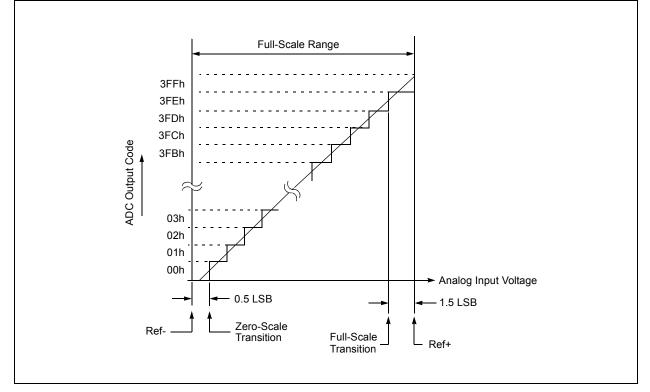

| Data Converters            | A/D 4x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-UFDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-UDFN (2x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1501t-i-mu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-3: PIC12(L)F1501 MEMORY MAP (CONTINUED)

|              | BANK 24                               | •            | BANK 25                               |              | BANK 26                               |              | BANK 27                               |              | BANK 28                               |              | BANK 29                               |              | BANK 30                               |              | BANK 31                               |

|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| C00h         | Core Registers<br>(Table 3-2)         | C80h         | Core Registers<br>(Table 3-2)         | D00h         | Core Registers<br>(Table 3-2)         | D80h         | Core Registers<br>(Table 3-2)         | E00h         | Core Registers<br>(Table 3-2)         | E80h         | Core Registers<br>(Table 3-2)         | F00h         | Core Registers<br>(Table 3-2)         | F80h         | Core Registers<br>(Table 3-2)         |

| C0Bh         |                                       | C8Bh         |                                       | D0Bh         |                                       | D8Bh         |                                       | E0Bh         |                                       | E8Bh         |                                       | F0Bh         |                                       | F8Bh         |                                       |

| C0Ch         | _                                     | C8Ch         | _                                     | D0Ch         | —                                     | D8Ch         | _                                     | E0Ch         | —                                     | E8Ch         | —                                     | F0Ch         |                                       | F8Ch         |                                       |

| C0Dh         | —                                     | C8Dh         | —                                     | D0Dh         | _                                     | D8Dh         | —                                     | E0Dh         | —                                     | E8Dh         | _                                     | F0Dh         |                                       | F8Dh         |                                       |

| C0Eh         | —                                     | C8Eh         | _                                     | D0Eh         |                                       | D8Eh         | —                                     | E0Eh         | —                                     | E8Eh         |                                       | F0Eh         |                                       | F8Eh         |                                       |

| C0Fh         | —                                     | C8Fh         |                                       | D0Fh         | _                                     | D8Fh         | —                                     | E0Fh         | —                                     | E8Fh         | _                                     | F0Fh         |                                       | F8Fh         |                                       |

| C10h         | —                                     | C90h         | _                                     | D10h         | _                                     | D90h         | —                                     | E10h         | —                                     | E90h         | _                                     | F10h         |                                       | F90h         |                                       |

| C11h         | —                                     | C91h         | —                                     | D11h         | _                                     | D91h         | —                                     | E11h         | —                                     | E91h         | _                                     | F11h         |                                       | F91h         |                                       |

| C12h         | —                                     | C92h         | _                                     | D12h         |                                       | D92h         | —                                     | E12h         | _                                     | E92h         |                                       | F12h         |                                       | F92h         |                                       |

| C13h         | —                                     | C93h         | _                                     | D13h         |                                       | D93h         | —                                     | E13h         | _                                     | E93h         |                                       | F13h         |                                       | F93h         |                                       |

| C14h         | —                                     | C94h         | —                                     | D14h         | —                                     | D94h         | —                                     | E14h         | —                                     | E94h         | _                                     | F14h         |                                       | F94h         |                                       |

| C15h         | —                                     | C95h         | _                                     | D15h         | _                                     | D95h         | _                                     | E15h         | _                                     | E95h         | _                                     | F15h         |                                       | F95h         |                                       |

| C16h         | —                                     | C96h         | —                                     | D16h         | _                                     | D96h         | _                                     | E16h         | _                                     | E96h         | _                                     | F16h         |                                       | F96h         |                                       |

| C17h         | —                                     | C97h         | —                                     | D17h         | _                                     | D97h         | _                                     | E17h         | _                                     | E97h         | _                                     | F17h         | See Table 3-3 for                     | F97h         | See Table 3-3 for                     |

| C18h         | _                                     | C98h         | —                                     | D18h         | —                                     | D98h         | _                                     | E18h         | _                                     | E98h         | _                                     | F18h         | register mapping                      | F98h         | register mapping                      |

| C19h         | _                                     | C99h         | —                                     | D19h         | —                                     | D99h         | _                                     | E19h         | _                                     | E99h         | _                                     | F19h         | details                               | F99h         | details                               |

| C1Ah         | —                                     | C9Ah         | _                                     | D1Ah         | —                                     | D9Ah         | _                                     | E1Ah         | _                                     | E9Ah         | —                                     | F1Ah         |                                       | F9Ah         |                                       |

| C1Bh         | _                                     | C9Bh         | —                                     | D1Bh         |                                       | D9Bh         | _                                     | E1Bh         |                                       | E9Bh         |                                       | F1Bh         |                                       | F9Bh         |                                       |

| C1Ch         | _                                     | C9Ch         | —                                     | D1Ch         |                                       | D9Ch         | _                                     | E1Ch         |                                       | E9Ch         |                                       | F1Ch         |                                       | F9Ch         |                                       |

| C1Dh         | —                                     | C9Dh         | —                                     | D1Dh         |                                       | D9Dh         | _                                     | E1Dh         |                                       | E9Dh         |                                       | F1Dh         |                                       | F9Dh         |                                       |

| C1Eh         | —                                     | C9Eh         | —                                     | D1Eh         |                                       | D9Eh         | _                                     | E1Eh         |                                       | E9Eh         |                                       | F1Eh         |                                       | F9Eh         |                                       |

| C1Fh         | —                                     | C9Fh         | —                                     | D1Fh         |                                       | D9Fh         | _                                     | E1Fh         |                                       | E9Fh         |                                       | F1Fh         |                                       | F9Fh         |                                       |

| C20h         |                                       | CA0h         |                                       | D20h         |                                       | DA0h         |                                       | E20h         |                                       | EA0h         |                                       | F20h         |                                       | FA0h         |                                       |

|              | Unimplemented<br>Read as '0'          |              |                                       |              |                                       |

| C6Fh         |                                       | CEFh         |                                       | D6Fh         |                                       | DEFh         |                                       | E6Fh         |                                       | EEFh         |                                       | F6Fh         |                                       | FEFh         |                                       |

| C70h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | CF0h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | D70h<br>D7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | DF0h<br>DFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | E70h<br>E7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | EF0h<br>EFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | F70h<br>F7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | FF0h<br>FFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

Legend: = Unimplemented data memory locations, read as '0'.

## 5.2 Clock Source Types

Clock sources can be classified as external, internal or peripheral.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The peripheral clock source is a nominal 600 kHz internal RC oscillator, FRC. The FRC is traditionally used with the ADC module, but is sometimes available to other peripherals. See **Section 5.2.2.4 "Peripheral Clock Sources"**.

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

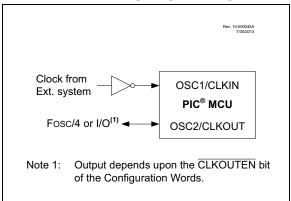

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High power, 4-20 MHz

- · ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

### FIGURE 5-2: EXTERNAL CLOCK (EC) MODE OPERATION

| U-0                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                       | U-0                                                                 | U-0                                            | U-0            | U-0              | R/W-0/0          | R/W-0/0     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------|----------------|------------------|------------------|-------------|

| _                                                                                                                                                                                                                                                                                                                                | _                                                                                                         |                                                                     |                                                |                |                  | CLC2IF           | CLC1IF      |

| bit 7                                                                                                                                                                                                                                                                                                                            |                                                                                                           |                                                                     |                                                | ·              |                  |                  | bit 0       |

|                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |                                                                     |                                                |                |                  |                  |             |

| Legend:                                                                                                                                                                                                                                                                                                                          |                                                                                                           |                                                                     |                                                |                |                  |                  |             |

| R = Read                                                                                                                                                                                                                                                                                                                         | dable bit                                                                                                 | W = Writable                                                        | bit                                            | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is                                                                                                                                                                                                                                                                                                                       | unchanged                                                                                                 | x = Bit is unkr                                                     | nown                                           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is                                                                                                                                                                                                                                                                                                                     | s set                                                                                                     | '0' = Bit is clea                                                   | ared                                           |                |                  |                  |             |

| bit 7-2       Unimplemented: Read as '0'         bit 1       CLC2IF: Configurable Logic Block 2 Interrupt Flag bit         1 = Interrupt is pending       0 = Interrupt is not pending         bit 0       CLC1IF: Configurable Logic Block 1 Interrupt Flag bit         1 = Interrupt is pending       1 = Interrupt is pending |                                                                                                           |                                                                     |                                                |                |                  |                  |             |

| Note:                                                                                                                                                                                                                                                                                                                            | Interrupt flag bits a<br>condition occurs, r<br>its corresponding o<br>Enable bit, GIE o<br>User software | egardless of the<br>enable bit or th<br>f the INTCON<br>should ensu | e state of<br>e Global<br>register.<br>ire the |                |                  |                  |             |

## REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

appropriate interrupt flag bits are clear prior to enabling an interrupt.

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a **SLEEP** instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- 8. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- CWG, NCO and CLC modules using HFINTOSC

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12 "Determining the Cause of a Reset**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

## 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| TABLE 9-3: | SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER |

|------------|-----------------------------------------------------|

|            |                                                     |

| Name   | Bit 7  | Bit 6  | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------------|-------|-------|-------|----------|--------|---------------------|

| OSCCON | —      |        | IRCF        | <3:0> |       | —     | SCS<1:0> |        | 49                  |

| PCON   | STKOVF | STKUNF | —           | RWDT  | RMCLR | RI    | POR      | BOR    | 57                  |

| STATUS | —      | —      | _           | TO    | PD    | Z     | DC       | С      | 17                  |

| WDTCON | —      | _      | - WDTPS<4:0 |       |       |       |          | SWDTEN | 77                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5  | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|-----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | _       | —       |           | —        | CLKOUTEN | BORE     | N<1:0>  | —       | 20                  |

| CONFIG1 |      |         | MCLRE   | PWRTE WDT |          | E<1:0>   |          | FOSC    | <1:0>   | 38                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

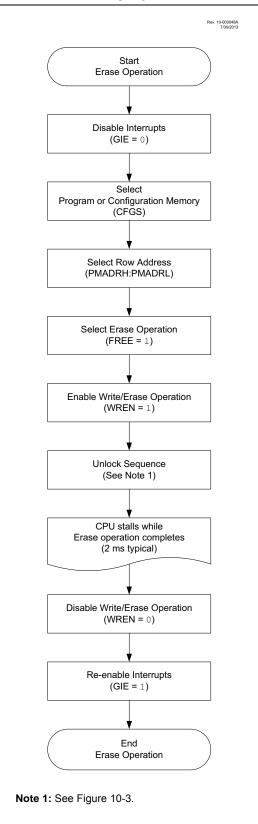

#### 10.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

See Example 10-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions immediately following the WR bit set instruction. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

## FIGURE 10-4:

#### FLASH PROGRAM MEMORY ERASE FLOWCHART

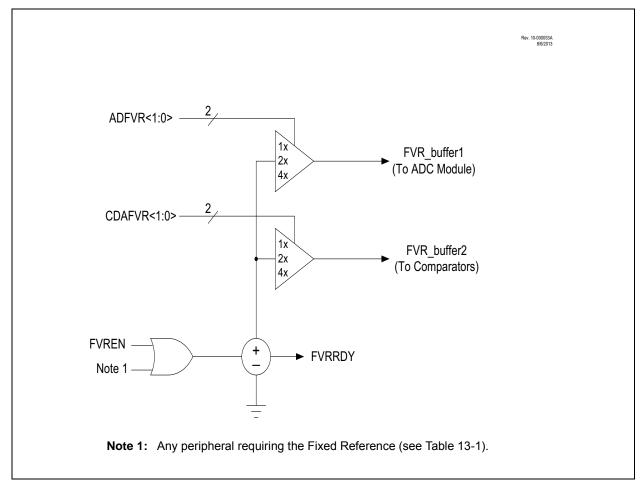

## 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with a nominal output level (VFVR) of 1.024V. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- Comparator positive input

- · Comparator negative input

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

## 13.1 Independent Gain Amplifier

The output of the FVR supplied to the peripherals, (listed above), is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0 "Analog-to-Digital Converter** (ADC) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the comparator modules. Reference **Section 17.0 "Comparator Module"** for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

## 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See the FVR Stabilization Period characterization graph, Figure 28-52.

## FIGURE 13-1: VOLTAGE REFERENCE BLOCK DIAGRAM

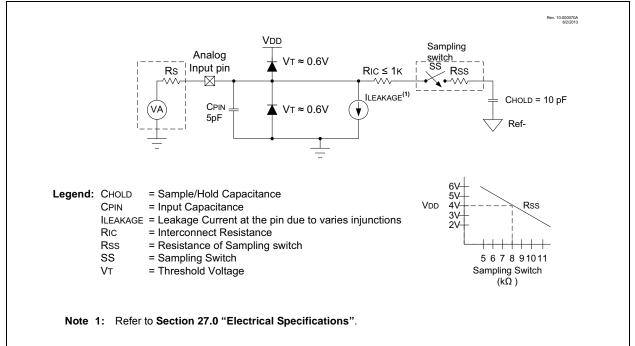

## FIGURE 15-4: ANALOG INPUT MODEL

## 16.6 Register Definitions: DAC Control

#### REGISTER 16-1: DACxCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0           | U-0                                                  | R/W-0/0                                              | R/W-0/0         | U-0             | R/W-0/0            | U-0                 | U-0   |  |  |  |  |  |

|-------------------|------------------------------------------------------|------------------------------------------------------|-----------------|-----------------|--------------------|---------------------|-------|--|--|--|--|--|

| DACEN             | —                                                    | DACOE1                                               | DACOE2          | —               | DACPSS             | —                   | _     |  |  |  |  |  |

| bit 7             |                                                      |                                                      |                 |                 |                    |                     | bit C |  |  |  |  |  |

|                   |                                                      |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

| Legend:           |                                                      |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

| R = Readable bi   | it                                                   | W = Writable bi                                      | it              | U = Unimplem    | ented bit, read as | '0'                 |       |  |  |  |  |  |

| u = Bit is unchar | nged                                                 | x = Bit is unkno                                     | wn              | -n/n = Value at | POR and BOR/Va     | alue at all other R | esets |  |  |  |  |  |

| '1' = Bit is set  |                                                      | '0' = Bit is clear                                   | ed              |                 |                    |                     |       |  |  |  |  |  |

|                   |                                                      |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

| bit 7             | DACEN: DAC E                                         | Enable bit                                           |                 |                 |                    |                     |       |  |  |  |  |  |

|                   | 1 = DACx is e                                        |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

|                   | 0 = DACx is di                                       | isabled                                              |                 |                 |                    |                     |       |  |  |  |  |  |

| bit 6             | Unimplemente                                         | ed: Read as '0'                                      |                 |                 |                    |                     |       |  |  |  |  |  |

| bit 5             | DACOE1: DAC                                          | Voltage Output                                       | Enable bit      |                 |                    |                     |       |  |  |  |  |  |

|                   |                                                      | 1 = DACx voltage level is output on the DACxOUT1 pin |                 |                 |                    |                     |       |  |  |  |  |  |

|                   | 0 = DACx volta                                       | age level is disco                                   | onnected from t | he DACxOUT1 p   | pin                |                     |       |  |  |  |  |  |

| bit 4             | DACOE2: DAC                                          | Voltage Output                                       | Enable bit      |                 |                    |                     |       |  |  |  |  |  |

|                   | 1 = DACx voltage level is output on the DACxOUT2 pin |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

|                   | 0 = DACx volta                                       | age level is disco                                   | onnected from t | he DACxOUT2 p   | bin                |                     |       |  |  |  |  |  |

| bit 3             | Unimplemente                                         | ed: Read as '0'                                      |                 |                 |                    |                     |       |  |  |  |  |  |

| bit 2             | DACPSS: DAC                                          | Positive Source                                      | e Select bit    |                 |                    |                     |       |  |  |  |  |  |

|                   | 1 = VREF+ pi                                         | in                                                   |                 |                 |                    |                     |       |  |  |  |  |  |

|                   | 0 = VDD                                              |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

| bit 1-0           | Unimplemente                                         | ed: Read as '0'                                      |                 |                 |                    |                     |       |  |  |  |  |  |

|                   |                                                      |                                                      |                 |                 |                    |                     |       |  |  |  |  |  |

#### REGISTER 16-2: DACxCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| _     | _   | _   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4     | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Register<br>on page |

|----------|-------|-------|--------|-----------|-------|--------|-------|-------|---------------------|

| DAC1CON0 | DACEN | _     | DACOE1 | DACOE2    | _     | DACPSS | _     | _     | 126                 |

| DAC1CON1 |       | -     | _      | DACR<4:0> |       |        |       | 126   |                     |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

| FIGURE 19-3.           | TIMERI GATE SINGLE-PULSE                 |                                                                         |

|------------------------|------------------------------------------|-------------------------------------------------------------------------|

| TMR1GE                 |                                          |                                                                         |

| T1GPOL                 |                                          |                                                                         |

| T1GSPM                 |                                          |                                                                         |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled on | Cleared by hardware on falling edge of T1GVAL                           |

| t1g_in                 | rising edge of T1G                       |                                                                         |

| T1CKI                  |                                          |                                                                         |

| T1GVAL                 |                                          |                                                                         |

| Timer1                 | N N + 1                                  | N + 2                                                                   |

| TMR1GIF                | Cleared by software                      | ← Set by hardware on<br>falling edge of T1GVAL ← Cleared by<br>software |

| FIGURE 19-6:                     | TIMER1 GATE SINGLE                                             | -PULSE AND TOGGLE COMBINED MODE                                             |

|----------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|

| TMR1GE                           |                                                                |                                                                             |

| T1GP <u>OL</u><br>T1GSP <u>M</u> |                                                                |                                                                             |

| T1GT <u>M</u>                    |                                                                |                                                                             |

| T1GG <u>O/</u><br>DONE           | ← Set by software<br>Counting enabled or<br>rising edge of T10 | Cleared by hardware on<br>falling edge of T1GVAL                            |

| t1g_in                           |                                                                |                                                                             |

| тіскі                            |                                                                |                                                                             |

| T1GV <u>AL</u>                   |                                                                |                                                                             |

| Timer1                           | Ν                                                              | N + 1     N + 2     N + 3     N + 4       Set by hardware on     Cleared by |

| TMR1GIF                          | <ul> <li>Cleared by software</li> </ul>                        | falling edge of T1GVAL                                                      |

| Name   | Bit 7                                                                      | Bit 6          | Bit 5          | Bit 4         | Bit 3          | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------------------------------------------------------------------------|----------------|----------------|---------------|----------------|--------|---------|---------|---------------------|

| ANSELA | —                                                                          | _              | _              | ANSA4         | —              | ANSA2  | ANSA1   | ANSA0   | 99                  |

| APFCON | CWG1BSEL                                                                   | CWGA1SEL       | _              | _             | T1GSEL         | —      | CLC1SEL | NCO1SEL | 96                  |

| INTCON | GIE                                                                        | PEIE           | TMR0IE         | INTE          | IOCIE          | TMR0IF | INTF    | IOCIF   | 64                  |

| PIE1   | TMR1GIE                                                                    | ADIE           | _              | _             | —              | —      | TMR2IE  | TMR1IE  | 65                  |

| PIR1   | TMR1GIF                                                                    | ADIF           | _              | _             | _              | —      | TMR2IF  | TMR1IF  | 68                  |

| TMR1H  | Holding Regi                                                               | ster for the M | ost Significan | t Byte of the | 16-bit TMR1 (  | Count  |         |         | 141*                |

| TMR1L  | L Holding Register for the Least Significant Byte of the 16-bit TMR1 Count |                |                |               |                |        | 141*    |         |                     |

| TRISA  | —                                                                          | _              | TRISA5         | TRISA4        | (1)            | TRISA2 | TRISA1  | TRISA0  | 98                  |

| T1CON  | TMR1C                                                                      | S<1:0>         | T1CKP          | S<1:0>        | —              | T1SYNC | _       | TMR10N  | 145                 |

| T1GCON | TMR1GE                                                                     | T1GPOL         | T1GTM          | T1GSPM        | T1GGO/<br>DONE | T1GVAL | T1GS    | S<1:0>  | 146                 |

TABLE 19-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module. \* Page provides register information.

Note 1: Unimplemented, read as '1'.

## 21.2 Register Definitions: PWM Control

| R/W-0/0              | R/W-0/0     | R-0/0             | R/W-0/0         | U-0                                                   | U-0 | U-0 | U-0   |  |  |

|----------------------|-------------|-------------------|-----------------|-------------------------------------------------------|-----|-----|-------|--|--|

| PWMxEN               | PWMxOE      | PWMxOUT           | PWMxPOL         | —                                                     | —   | —   | —     |  |  |

| bit 7                |             |                   |                 |                                                       |     |     | bit 0 |  |  |

|                      |             |                   |                 |                                                       |     |     |       |  |  |

| Legend:              |             |                   |                 |                                                       |     |     |       |  |  |

| R = Readable         | bit         | W = Writable      | bit             | U = Unimplemented bit, read as '0'                    |     |     |       |  |  |

| u = Bit is unchanged |             | x = Bit is unkr   | nown            | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |  |

| '1' = Bit is set     |             | '0' = Bit is clea | ared            |                                                       |     |     |       |  |  |

|                      |             |                   |                 |                                                       |     |     |       |  |  |

| bit 7                | PWMxEN: P\  | NM Module En      | able bit        |                                                       |     |     |       |  |  |

|                      | 1 = PWM mc  | dule is enable    | d               |                                                       |     |     |       |  |  |

|                      | 0 = PWM mc  | odule is disable  | d               |                                                       |     |     |       |  |  |

| bit 6                | PWMxOE: P   | WM Module Ou      | itput Enable bi | t                                                     |     |     |       |  |  |

|                      |             | PWMx pin is e     |                 |                                                       |     |     |       |  |  |

|                      | •           | PWMx pin is a     |                 |                                                       |     |     |       |  |  |

| bit 5                | PWMxOUT: F  | PWM Module C      | output Value bi | t                                                     |     |     |       |  |  |

| bit 4                | PWMxPOL:    | PWMx Output F     | Polarity Select | bit                                                   |     |     |       |  |  |

|                      | 1 = PWM out | tput is active-lo | W               |                                                       |     |     |       |  |  |

|                      | 0 = PWM out | tput is active-hi | gh              |                                                       |     |     |       |  |  |

| bit 3-0              | Unimplemen  | ted: Read as '    | 0'              |                                                       |     |     |       |  |  |

|                      |             |                   |                 |                                                       |     |     |       |  |  |

## REGISTER 21-1: PWMxCON: PWM CONTROL REGISTER

### REGISTER 22-9: CLCDATA: CLC DATA OUTPUT

| U-0                                | U-0 | U-0                | U-0                                | U-0                                                   | U-0 | R-0     | R-0     |  |

|------------------------------------|-----|--------------------|------------------------------------|-------------------------------------------------------|-----|---------|---------|--|

| _                                  | -   | —                  | _                                  | —                                                     | —   | MLC2OUT | MLC1OUT |  |

| bit 7                              |     |                    |                                    |                                                       |     |         | bit 0   |  |

|                                    |     |                    |                                    |                                                       |     |         |         |  |

| Legend:                            |     |                    |                                    |                                                       |     |         |         |  |

| R = Readable bit W = Writable bit  |     | bit                | U = Unimplemented bit, read as '0' |                                                       |     |         |         |  |

| u = Bit is unchanged x             |     | x = Bit is unknown |                                    | -n/n = Value at POR and BOR/Value at all other Resets |     |         |         |  |

| '1' = Bit is set                   |     | '0' = Bit is clea  | ared                               |                                                       |     |         |         |  |

|                                    |     |                    |                                    |                                                       |     |         |         |  |

| bit 7-2 Unimplemented: Read as '0' |     |                    | 2                                  |                                                       |     |         |         |  |

| h:+ 4                              |     | inner een of l     |                                    |                                                       |     |         |         |  |

| bit 1 | MLC2OUI: Mirror | copy of LC2OUT bit |

|-------|-----------------|--------------------|

|       |                 |                    |

bit 0 MLC1OUT: Mirror copy of LC1OUT bit

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                    |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

| SUBLW            | Subtract W from literal                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                           |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                  |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                           |  |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal 'k'. The result is placed in the W regis-<br>ter. |  |  |  |  |

|                  | C = 0 W > k                                                                                                                        |  |  |  |  |

|                  | $C = 1$ $W \le k$                                                                                                                  |  |  |  |  |

|                  | DC = 0 W<3:0> > k<3:0>                                                                                                             |  |  |  |  |

DC = 1

$W<3:0> \le k<3:0>$

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |

| SUBWF            | Subtract W                                                                                                                                                                                 | from f                         |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                                 | JBWF f,d                       |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                          |                                |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (d                                                                                                                                                                 | $V) \rightarrow (destination)$ |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |                                |  |  |  |  |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |                                |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                                                                                               | W > f                          |  |  |  |  |

|                  | <b>C =</b> 1                                                                                                                                                                               | $W \leq f$                     |  |  |  |  |

|                  | DC = 0                                                                                                                                                                                     | W<3:0> > f<3:0>                |  |  |  |  |

|                  | DC = 1                                                                                                                                                                                     | $W<3:0> \le f<3:0>$            |  |  |  |  |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                         |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

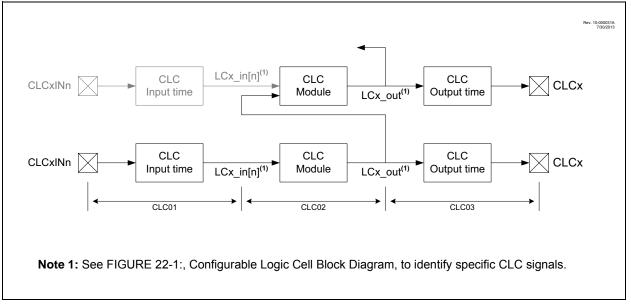

| TABLE 27-12: | CONFIGURATION LOGIC CELL (CLC) CHARACTERISTICS |

|--------------|------------------------------------------------|

|              |                                                |

| Param.<br>No. | Sym.    | Characteristic                              | Min. | Тур†     | Max. | Units    | Conditions               |

|---------------|---------|---------------------------------------------|------|----------|------|----------|--------------------------|

| CLC01*        | TCLCIN  | CLC input time                              | _    | 7        | _    | ns       |                          |

| CLC02*        | TCLC    | CLC module input to output propagation time |      | 24<br>12 |      | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |

| CLC03*        | TCLCOUT | CLC output time Rise Time                   |      | OS18     |      | —        | (Note 1)                 |

|               |         | Fall Time                                   | _    | OS19     | _    |          | (Note 1)                 |

| CLC04*        | FCLCMAX | CLC maximum switching frequency             | _    | 45       | _    | MHz      |                          |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1:See Table 27-9 for OS18 and OS19 rise and fall times.

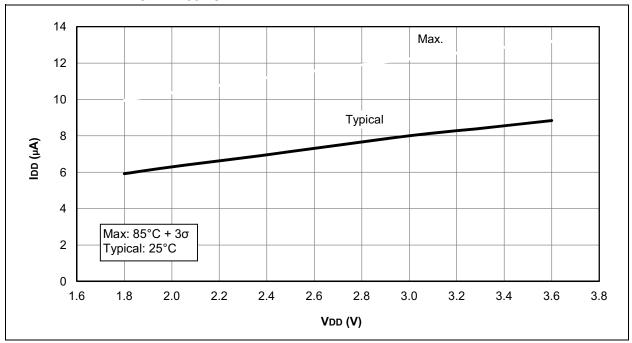

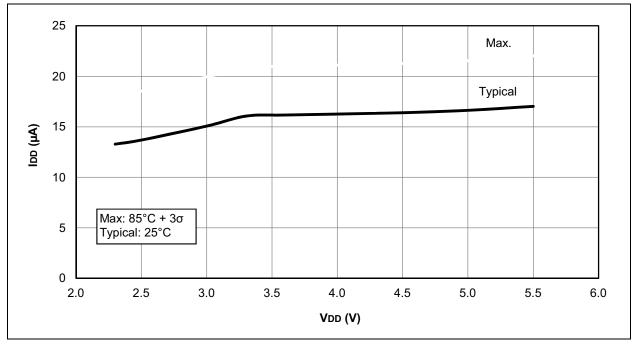

FIGURE 28-1: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 32 kHz, PIC12LF1501 ONLY

FIGURE 28-2: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 32 kHz, PIC12F1501 ONLY

## 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>