Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | ·                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | ·                                                                           |

| RAM Size                   | 64 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 4x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package    | 8-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lf1501t-i-sn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC12(L)F1501 PINOUT DESCRIPTION (CONTINUED) **TABLE 1-2:**

| Name                                   | Function | Input<br>Type | Output<br>Type | Description                                           |

|----------------------------------------|----------|---------------|----------------|-------------------------------------------------------|

| RA5/CLKIN/T1CKI/CWG1A <sup>(1)</sup> / | RA5      | TTL           | CMOS           | General purpose I/O.                                  |

| NCO1 <sup>(1)</sup> /NCO1CLK/CLC1IN1/  | CLKIN    | CMOS          | _              | External clock input (EC mode).                       |

| CLC2/PWM4                              | T1CKI    | ST            |                | Timer1 clock input.                                   |

|                                        | CWG1A    | _             | CMOS           | CWG complementary output.                             |

|                                        | NCO1     | ST            | _              | Numerically Controlled Oscillator output.             |

|                                        | NCO1CLK  | ST            |                | Numerically Controlled Oscillator Clock source input. |

|                                        | CLC1IN1  | ST            | _              | Configurable Logic Cell source input.                 |

|                                        | CLC2     | _             | CMOS           | Configurable Logic Cell source output.                |

|                                        | PWM4     | _             | CMOS           | Pulse Width Module source output.                     |

| VDD                                    | Vdd      | Power         |                | Positive supply.                                      |

| Vss                                    | Vss      | Power         | _              | Ground reference.                                     |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C<sup>™</sup> = Schmitt Trigger input with I<sup>2</sup>C levels

HV = High Voltage XTAL = Crystal

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

#### **TABLE 3-5:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| IABLE              | 3-5. 3   | PECIAL F   |               | N REGIS | IER SUI |           | CONTIN |        |         |                      | T                               |

|--------------------|----------|------------|---------------|---------|---------|-----------|--------|--------|---------|----------------------|---------------------------------|

| Address            | Name     | Bit 7      | Bit 6         | Bit 5   | Bit 4   | Bit 3     | Bit 2  | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 4             |          |            |               |         |         |           |        |        |         |                      |                                 |

| 20Ch               | WPUA     | —          | —             | WPUA5   | WPUA4   | WPUA3     | WPUA2  | WPUA1  | WPUA0   | 11 1111              | 11 1111                         |

| 20Dh<br>to<br>21Fh | _        | Unimplemen | ted           |         |         |           |        |        |         | _                    | _                               |

| Bank 5             |          |            |               |         |         |           |        |        |         |                      | •                               |

| 28Ch<br>to<br>29Fh | _        | Unimplemen | ted           |         |         |           |        |        |         | _                    | _                               |

| Bank 6             | ;        |            |               |         |         |           |        |        |         |                      |                                 |

| 30Ch<br>to<br>31Fh | _        | Unimplemen | ted           |         |         |           |        |        |         | _                    | _                               |

| Bank 7             | ,        |            |               |         |         |           |        |        |         |                      |                                 |

| 38Ch<br>to<br>390h | _        | Unimplemen | ted           |         |         |           |        |        |         | _                    | _                               |

| 391h               | IOCAP    | —          |               | IOCAP5  | IOCAP4  | IOCAP3    | IOCAP2 | IOCAP1 | IOCAP0  | 00 0000              | 00 0000                         |

| 392h               | IOCAN    | —          |               | IOCAN5  | IOCAN4  | IOCAN3    | IOCAN2 | IOCAN1 | IOCAN0  | 00 0000              | 00 0000                         |

| 393h               | IOCAF    | —          | —             | IOCAF5  | IOCAF4  | IOCAF3    | IOCAF2 | IOCAF1 | IOCAF0  | 00 0000              | 00 0000                         |

| 394h<br>to<br>39Fh | _        | Unimplemen | ted           |         |         |           |        |        |         | _                    | _                               |

| Bank 8             | 1        |            |               |         |         |           |        |        |         |                      |                                 |

| 40Ch<br>to<br>41Fh | _        | Unimplemen | ted           |         |         |           |        |        |         | _                    | _                               |

| Bank 9             |          |            |               |         |         |           |        |        |         |                      |                                 |

| 48Ch<br>to<br>497h | _        | Unimplemen | Jnimplemented |         |         |           |        |        |         | _                    | _                               |

| 498h               | NCO1ACCL |            |               |         | NCO1    | ACC<7:0>  |        |        |         | 0000 0000            | 0000 0000                       |

| 499h               | NCO1ACCH |            |               |         | NCO1A   | CC<15:8>  |        |        |         | 0000 0000            | 0000 0000                       |

| 49Ah               | NCO1ACCU |            |               |         | NCO1A   | CC<19:16> |        |        |         | 0000 0000            | 0000 0000                       |

| 49Bh               | NCO1INCL |            |               |         |         | INC<7:0>  |        |        |         | 0000 0001            | 0000 0001                       |

| 49Ch               | NCO1INCH |            |               |         | NCO1I   | NC<15:8>  |        |        |         | 0000 0000            | 0000 0000                       |

| 49Dh               | -        | Unimplemen |               |         | 1       |           |        |        |         | -                    | —                               |

| 49Eh               | NCO1CON  | N1EN       | N10E          | N1OUT   | N1POL   | —         | —      | —      | N1PFM   |                      | 00000                           |

| 49Fh               | NCO1CLK  |            | N1PWS<2:0>    |         | —       | —         | —      | N1Ck   | (S<1:0> | 000000               | 000000                          |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC12F1501 only.

2:

Unimplemented, read as '1'.

DS40001615C-page 26

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

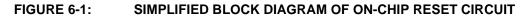

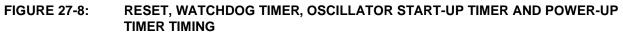

# 6.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-chip Reset Circuit is shown in Figure 6-1.

| Fosc      | Q1 Q2 Q3 Q4   | Q1 Q2 Q3 Q4   | \_\_\_<br> Q1 Q2 Q3 Q4 |                  | Q1 Q2 Q3 Q4 |             | Q1 Q2 Q3 Q4 | NNN<br>     |

|-----------|---------------|---------------|------------------------|------------------|-------------|-------------|-------------|-------------|

|           |               |               | Interru<br>during      | pt Sampled<br>Q1 |             |             |             |             |

| Interrupt |               |               |                        |                  |             |             |             |             |

| GIE       |               |               |                        |                  |             |             |             |             |

| PC        | PC-1          | PC            | PC                     | +1               | 0004h       | 0005h       |             | (           |

| Execute   | 1-Cycle Instr | uction at PC  | Inst(PC)               | NOP              | NOP         | Inst(0004h) |             |             |

| Interrupt |               |               |                        |                  |             |             |             |             |

| GIE       |               |               |                        |                  |             |             |             |             |

| PC        | PC-1          | PC            | PC+1/FSR<br>ADDR       | New PC/<br>PC+1  | 0004h       | 0005h       |             | /           |

| Execute-  | 2-Cycle Instr | uction at PC  | Inst(PC)               | NOP              | NOP         | Inst(0004h) |             |             |

| Interrupt |               |               |                        |                  |             |             |             |             |

| GIE       |               |               |                        |                  |             |             |             |             |

| PC        | PC-1          | PC            | FSR ADDR               | PC+1             | PC+2        | 0004h       | 0005h       |             |

| Execute   | 3-Cycle Instr | ruction at PC | INST(PC)               | NOP              | NOP         | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt |               |               |                        |                  |             |             |             |             |

| GIE       |               |               |                        |                  |             |             |             |             |

| PC        | PC-1          | PC            | FSR ADDR               | PC+1             | Р           | C+2         | 0004h       | 0005h       |

| Execute   | 3-Cycle Instr | uction at PC  | INST(PC)               | NOP              | NOP         | NOP         | NOP         | Inst(0004h) |

| 11.0         | U-0                                       |                   | U-0            | 11.0           |                  | 11.0             | 11.0        |

|--------------|-------------------------------------------|-------------------|----------------|----------------|------------------|------------------|-------------|

| U-0          | 0-0                                       | R/W-0/0           | 0-0            | U-0            | R/W-0/0          | U-0              | U-0         |

| _            |                                           | C1IF              | —              |                | NCO1IF           |                  |             |

| bit 7        |                                           |                   |                |                |                  |                  | bit 0       |

| Legend:      |                                           |                   |                |                |                  |                  |             |

| R = Read     | abla hit                                  | W = Writable      | hit            | II – Unimplor  | nented bit, read | ac '0'           |             |

|              |                                           |                   |                | •              | ,                |                  |             |

| u = Bit is i | unchanged                                 | x = Bit is unkn   | iown           | -n/n = Value a | at POR and BOF   | R/Value at all c | ther Resets |

| '1' = Bit is | set                                       | '0' = Bit is clea | ared           |                |                  |                  |             |

|              |                                           |                   |                |                |                  |                  |             |

| bit 7-6      | Unimplemen                                | ted: Read as '    | )'             |                |                  |                  |             |

| bit 5        | C1IF: Compa                               | rator C1 Interru  | pt Flag bit    |                |                  |                  |             |

|              | 1 = Interrupt i                           | s pending         |                |                |                  |                  |             |

|              | 0 = Interrupt i                           | s not pending     |                |                |                  |                  |             |

| bit 4-3      | Unimplemen                                | ted: Read as 'd   | )'             |                |                  |                  |             |

| bit 2        | NCO1IF: Nun                               | nerically Contro  | lled Oscillato | or Flag bit    |                  |                  |             |

|              | 1 = Interrupt i                           | •                 |                | 5              |                  |                  |             |

|              |                                           | s not pending     |                |                |                  |                  |             |

| bit 1-0      | Unimplemen                                | ted: Read as '    | )'             |                |                  |                  |             |

|              |                                           |                   |                |                |                  |                  |             |

|              |                                           |                   |                |                |                  |                  |             |

| Note:        | Interrupt flag bits a                     |                   |                |                |                  |                  |             |

|              | condition occurs, re                      |                   |                |                |                  |                  |             |

|              | its corresponding e<br>Interrupt Enable b |                   |                |                |                  |                  |             |

|              | register. User soft                       |                   |                |                |                  |                  |             |

|              | appropriate interru                       |                   |                |                |                  |                  |             |

|              | to enabling an inter                      |                   |                |                |                  |                  |             |

# REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

## 19.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 19-1 displays the Timer1 enable selections.

| TABLE 19-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 19.2 Clock Source Selection

The TMR1CS<1:0> bits of the T1CON register are used to select the clock source for Timer1. Table 19-2 displays the clock source selections.

#### 19.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 19.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 19-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | Clock Source                   |

|-------------|--------------------------------|

| 11          | LFINTOSC                       |

| 10          | External Clocking on T1CKI Pin |

| 01          | System Clock (Fosc)            |

| 00          | Instruction Clock (Fosc/4)     |

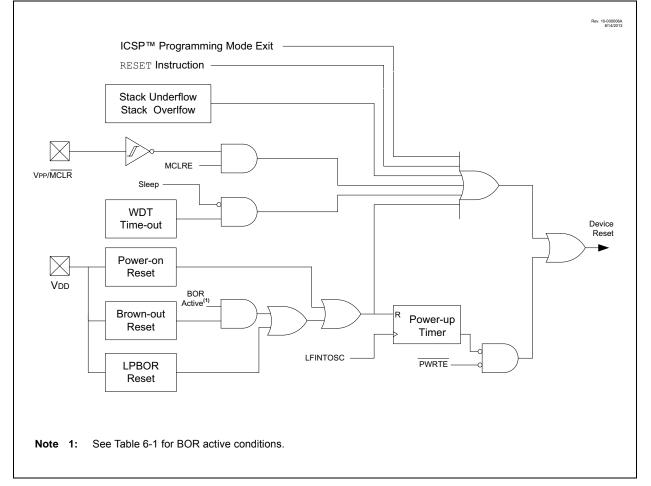

# 20.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2

See Figure 20-1 for a block diagram of Timer2.

#### FIGURE 20-1: TIMER2 BLOCK DIAGRAM

## FIGURE 20-2: TIMER2 TIMING DIAGRAM

|                                                        | 1                          | Rev. 10/00020A<br>7/30/2013 |

|--------------------------------------------------------|----------------------------|-----------------------------|

| Fosc/4                                                 |                            |                             |

| Prescale                                               | 1:4                        |                             |

| PR2                                                    | 0x03                       |                             |

| TMR2 0x00 0x01 0x02                                    | 0x03                       | 0x00 0x01 0x02              |

| T2_match                                               | Pulse Width <sup>(1)</sup> |                             |

| <b>Note 1:</b> The Pulse Width of T2_match is equal to | b the scaled inpu          | it of TMR2.                 |

#### 21.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Clear the PWMxDCH register and bits <7:6> of the PWMxDCL register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the PWMxOE bit of the PWMxCON register.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

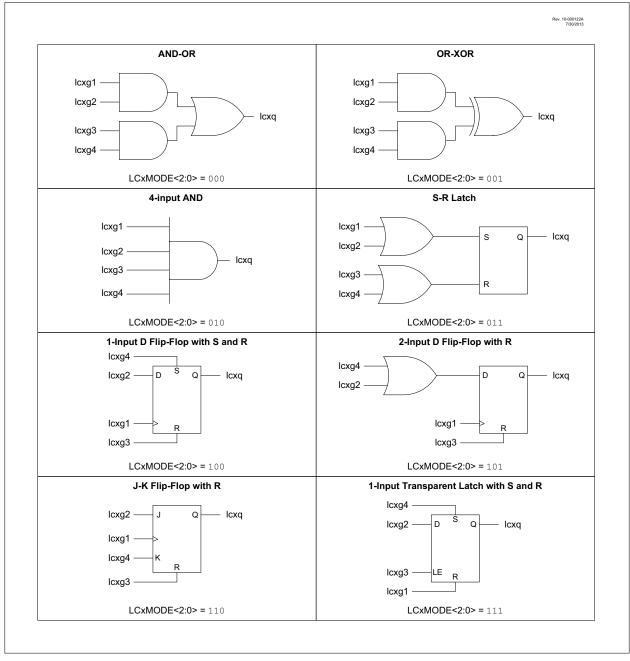

#### FIGURE 22-3: PROGRAMMABLE LOGIC FUNCTIONS

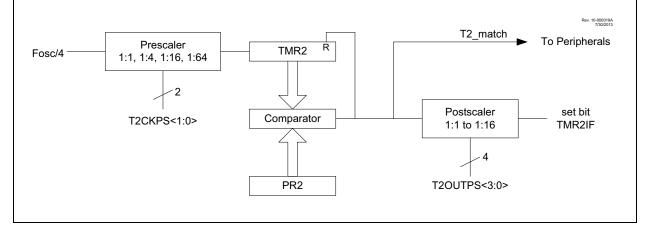

| U-0             | R/W-x/u                                  | R/W-x/u                                                                          | R/W-x/u      | U-0                       | R/W-x/u          | R/W-x/u                    | R/W-x/u     |  |  |  |

|-----------------|------------------------------------------|----------------------------------------------------------------------------------|--------------|---------------------------|------------------|----------------------------|-------------|--|--|--|

| _               |                                          | LCxD4S<2:0>(1)                                                                   |              | —                         | L                | _CxD3S<2:0> <sup>(1)</sup> | )           |  |  |  |

| bit 7           | •                                        |                                                                                  |              | ·                         |                  |                            | bit (       |  |  |  |

|                 |                                          |                                                                                  |              |                           |                  |                            |             |  |  |  |

| Legend:         |                                          |                                                                                  |              |                           |                  |                            |             |  |  |  |

| R = Readab      | le bit                                   | W = Writable k                                                                   | bit          | U = Unimplei              | mented bit, read | d as '0'                   |             |  |  |  |

| u = Bit is un   | changed                                  | x = Bit is unkn                                                                  | own          | -n/n = Value              | at POR and BO    | R/Value at all o           | ther Resets |  |  |  |

| '1' = Bit is se | et                                       | '0' = Bit is clea                                                                | ired         |                           |                  |                            |             |  |  |  |

|                 |                                          |                                                                                  |              |                           |                  |                            |             |  |  |  |

| bit 7           | Unimplem                                 | ented: Read as '0                                                                | )'           |                           |                  |                            |             |  |  |  |

| bit 6-4         | LCxD4S<2                                 | ::0>: Input Data 4                                                               | Selection Co | ntrol bits <sup>(1)</sup> |                  |                            |             |  |  |  |

|                 | 111 = LCx                                | 111 = LCx_in[3] is selected for lcxd4                                            |              |                           |                  |                            |             |  |  |  |

|                 |                                          | 110 = LCx_in[2] is selected for lcxd4                                            |              |                           |                  |                            |             |  |  |  |

|                 |                                          | _in[1] is selected                                                               |              |                           |                  |                            |             |  |  |  |

|                 |                                          | _in[0] is selected                                                               |              |                           |                  |                            |             |  |  |  |

|                 |                                          | _in[15] is selected                                                              |              |                           |                  |                            |             |  |  |  |

|                 |                                          | 010 = LCx_in[14] is selected for lcxd4<br>001 = LCx in[13] is selected for lcxd4 |              |                           |                  |                            |             |  |  |  |

|                 |                                          | in[12] is selected                                                               |              |                           |                  |                            |             |  |  |  |

| bit 3           |                                          | ented: Read as '0                                                                |              |                           |                  |                            |             |  |  |  |

| bit 2-0         | LCxD3S<2                                 | ::0>: Input Data 3                                                               | Selection Co | ntrol bits <sup>(1)</sup> |                  |                            |             |  |  |  |

|                 | $111 = LCx_in[15]$ is selected for lcxd3 |                                                                                  |              |                           |                  |                            |             |  |  |  |

|                 | $110 = LCx_in[14]$ is selected for lcxd3 |                                                                                  |              |                           |                  |                            |             |  |  |  |

|                 | 101 = LCx_in[13] is selected for lcxd3   |                                                                                  |              |                           |                  |                            |             |  |  |  |

|                 | 100 = LCx_in[12] is selected for lcxd3   |                                                                                  |              |                           |                  |                            |             |  |  |  |

|                 | 011 = LCx_in[11] is selected for lcxd3   |                                                                                  |              |                           |                  |                            |             |  |  |  |

|                 |                                          | _in[10] is selected                                                              |              |                           |                  |                            |             |  |  |  |

|                 |                                          | _in[9] is selected i                                                             |              |                           |                  |                            |             |  |  |  |

|                 | 000 = LCx                                | _in[8] is selected                                                               |              |                           |                  |                            |             |  |  |  |

# REGISTER 22-4: CLCxSEL1: MULTIPLEXER DATA 3 AND 4 SELECT REGISTER

**Note 1:** See Table 22-1 for signal names associated with inputs.

# FIGURE 26-1: GENERAL FORMAT FOR INSTRUCTIONS

| 13            | 3         8         7         6         0           OPCODE         d         f (FILE #)         1 |

|---------------|---------------------------------------------------------------------------------------------------|

|               | d = 0 for destination W                                                                           |

|               | d = 1 for destination f<br>f = 7-bit file register address                                        |

| <b>Bit-</b> 0 | oriented file register operations<br>3 10 9 7 6 0                                                 |

| Γ             | OPCODE b (BIT #) f (FILE #)                                                                       |

|               | b = 3-bit bit address<br>f = 7-bit file register address                                          |

| Lite          | ral and control operations                                                                        |

|               | leral                                                                                             |

| 13            |                                                                                                   |

|               | OPCODE k (literal)                                                                                |

|               | k = 8-bit immediate value                                                                         |

| CAL           | L and GOTO instructions only                                                                      |

| 13            |                                                                                                   |

|               | OPCODE k (literal)                                                                                |

|               | k = 11-bit immediate value                                                                        |

| MOV           | LP instruction only                                                                               |

| 13            |                                                                                                   |

|               | OPCODE k (literal)                                                                                |

|               | k = 7-bit immediate value                                                                         |

| MOV           | LB instruction only                                                                               |

| 13            | 3 5 4 0                                                                                           |

|               | OPCODE k (literal)                                                                                |

|               | k = 5-bit immediate value                                                                         |

| BRA           | instruction only                                                                                  |

| 1:            | <u>3 98</u> 0                                                                                     |

|               | OPCODE k (literal)                                                                                |

|               | k = 9-bit immediate value                                                                         |

| FSR           | Offset instructions                                                                               |

| 13            | 3 7 6 5 0                                                                                         |

|               | OPCODE n k (literal)                                                                              |

|               | n = appropriate FSR<br>k = 6-bit immediate value                                                  |

| FSR<br>13     | Increment instructions<br>3 3 2 1 0                                                               |

|               | OPCODE n m (mode                                                                                  |

|               | n = appropriate FSR<br>m = 2-bit mode value                                                       |

|               |                                                                                                   |

| OP(<br>13     | CODE only<br>3 0                                                                                  |

| Mnen   | nonic,      | Description                                   | Cycles |     | 14-Bit | Opcode | )    | Status   | Notes |

|--------|-------------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

| Oper   | Description |                                               | Cycles | MSb |        |        | LSb  | Affected | Notes |

|        |             | CONTROL OPER                                  | TIONS  |     |        |        |      |          |       |

| BRA    | k           | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW    | -           | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL   | k           | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW  | _           | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO   | k           | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE | k           | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW  | k           | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN | -           | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|        |             |                                               | TIONS  |     |        |        |      |          |       |

| CLRWDT | _           | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP    | _           | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION | _           | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET  | -           | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP  | _           | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS   | f           | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|        |             | C-COMPILER OPT                                | IMIZED |     |        |        |      |          |       |

| ADDFSR | n, k        | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW  | n mm        | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|        |             | modifier, mm                                  |        |     |        |        | kkkk |          |       |

|        | k[n]        | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | 1nmm | Z        | 2     |

| MOVWI  | n mm        | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | kkkk |          | 2, 3  |

|        |             | modifier, mm                                  |        |     |        |        |      |          |       |

|        | k[n]        | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   |      |          | 2     |

#### TABLE 26-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

| PIC12LF1501<br>PIC12F1501 |     | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode<br>Low-Power Sleep Mode, VREGPM = 1 |      |     |     |    |     |                           |  |

|---------------------------|-----|-------------------------------------------------------------------------------------------------------------|------|-----|-----|----|-----|---------------------------|--|

|                           |     |                                                                                                             |      |     |     |    |     |                           |  |

| No.                       | Vdd | Note                                                                                                        |      |     |     |    |     |                           |  |

| D026                      |     | —                                                                                                           | 0.11 | 1.5 | 9.0 | μA | 1.8 | ADC Current (Note 3),     |  |

|                           |     | _                                                                                                           | 0.12 | 2.7 | 12  | μA | 3.0 | No conversion in progress |  |

| D026                      |     | _                                                                                                           | 0.30 | 4.0 | 11  | μA | 2.3 | ADC Current (Note 3),     |  |

|                           |     |                                                                                                             | 0.35 | 5.0 | 13  | μA | 3.0 | No conversion in progress |  |

|                           |     |                                                                                                             | 0.45 | 8.0 | 16  | μA | 5.0 |                           |  |

| D026A*                    |     |                                                                                                             | 250  | _   | _   | μA | 1.8 | ADC Current (Note 3),     |  |

|                           |     |                                                                                                             | 250  | —   | —   | μA | 3.0 | Conversion in progress    |  |

| D026A*                    |     |                                                                                                             | 280  |     |     | μA | 2.3 | ADC Current (Note 3),     |  |

|                           |     |                                                                                                             | 280  | —   | —   | μA | 3.0 | Conversion in progress    |  |

|                           |     |                                                                                                             | 280  |     |     | μA | 5.0 |                           |  |

| D027                      |     | _                                                                                                           | 7    | 22  | 25  | μA | 1.8 | Comparator,               |  |

|                           |     | _                                                                                                           | 8    | 23  | 27  | μA | 3.0 | CxSP = 0                  |  |

| D027                      |     |                                                                                                             | 17   | 35  | 37  | μA | 2.3 | Comparator,               |  |

|                           |     |                                                                                                             | 18   | 37  | 38  | μA | 3.0 | CxSP = 0                  |  |

|                           |     |                                                                                                             | 19   | 38  | 40  | μA | 5.0 |                           |  |

### TABLE 27-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup> (CONTINUED)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral ∆ current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: ADC clock source is FRC.

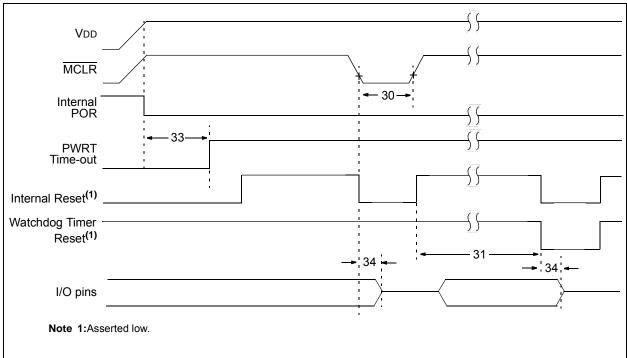

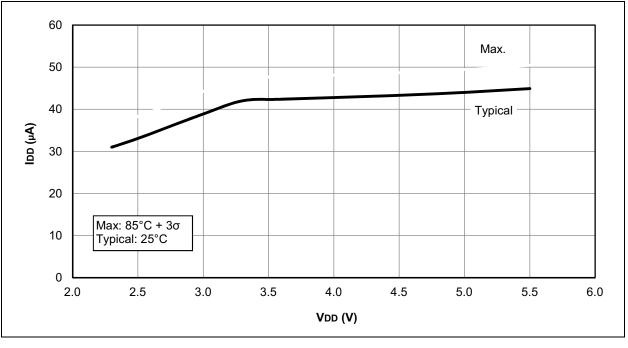

FIGURE 28-3: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 500 kHz, PIC12LF1501 ONLY

FIGURE 28-4: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 500 kHz, PIC12F1501 ONLY

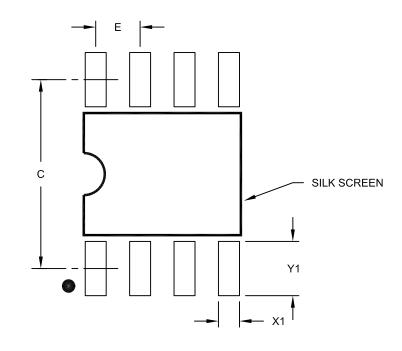

# 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units            | MILLIMETERS |      |      |  |

|-------------------------|------------------|-------------|------|------|--|

| Dimension               | Dimension Limits |             | NOM  | MAX  |  |

| Contact Pitch           | E                | 1.27 BSC    |      |      |  |

| Contact Pad Spacing     | С                |             | 5.40 |      |  |

| Contact Pad Width (X8)  | X1               |             |      | 0.60 |  |

| Contact Pad Length (X8) | Y1               |             |      | 1.55 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

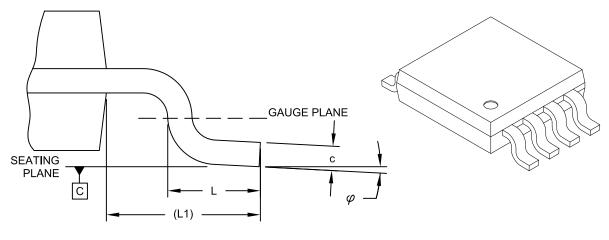

## 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL C

|                          | MILLIMETERS |            |          |      |  |

|--------------------------|-------------|------------|----------|------|--|

| Dimension Limits         |             | MIN        | NOM      | MAX  |  |

| Number of Pins           | N           |            | 8        |      |  |

| Pitch                    | е           |            | 0.65 BSC |      |  |

| Overall Height           | A           | -          | -        | 1.10 |  |

| Molded Package Thickness | A2          | 0.75       | 0.85     | 0.95 |  |

| Standoff                 | A1          | 0.00       | -        | 0.15 |  |

| Overall Width            | E           | E 4.90 BSC |          |      |  |

| Molded Package Width     | E1          | 3.00 BSC   |          |      |  |

| Overall Length           | D           | 3.00 BSC   |          |      |  |

| Foot Length              | L           | 0.40       | 0.60     | 0.80 |  |

| Footprint                | L1          | 0.95 REF   |          |      |  |

| Foot Angle               | φ           | 0°         | -        | 8°   |  |

| Lead Thickness           | С           | 0.08       | -        | 0.23 |  |

| Lead Width               | b           | 0.22       | -        | 0.40 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or

protrusions shall not exceed 0.15mm per side. 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111C Sheet 2 of 2

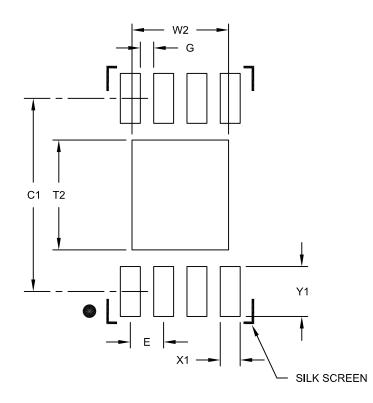

8-Lead Plastic Dual Flat, No Lead Package (MC) - 2x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | Units |      |          | MILLIMETERS |  |  |  |

|----------------------------|-------|------|----------|-------------|--|--|--|

| Dimension Limits           |       | MIN  | NOM      | MAX         |  |  |  |

| Contact Pitch              | E     |      | 0.50 BSC |             |  |  |  |

| Optional Center Pad Width  | W2    |      |          | 1.45        |  |  |  |

| Optional Center Pad Length | T2    |      |          | 1.75        |  |  |  |

| Contact Pad Spacing        | C1    |      | 2.90     |             |  |  |  |

| Contact Pad Width (X8)     | X1    |      |          | 0.30        |  |  |  |

| Contact Pad Length (X8)    | Y1    |      |          | 0.75        |  |  |  |

| Distance Between Pads      | G     | 0.20 |          |             |  |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2123B