Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-UQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1824-e-jq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-3: PIC16(L)F1828 PINOUT DESCRIPTION

| Name                                                           | Function | Input | Output | Description                                   |

|----------------------------------------------------------------|----------|-------|--------|-----------------------------------------------|

| Naille                                                         | Tunction | Туре  | Туре   | Description                                   |

| RA0/AN0/CPS0/C1IN+/VREF-/                                      | RA0      | TTL   | CMOS   | General purpose I/O.                          |

| DACOUT/ICSPDAT/ICDDAT                                          | AN0      | AN    | _      | A/D Channel 0 input.                          |

|                                                                | CPS0     | AN    |        | Capacitive sensing input 0.                   |

|                                                                | C1IN+    | AN    | —      | Comparator C1 positive input.                 |

|                                                                | VREF-    | AN    | _      | A/D and DAC Negative Voltage Reference input. |

|                                                                | DACOUT   |       | AN     | Digital-to-Analog Converter output.           |

|                                                                | ICSPDAT  | ST    | CMOS   | ICSP™ Data I/O.                               |

|                                                                | ICDDAT   | ST    | CMOS   | In-Circuit Data I/O.                          |

| RA1/AN1/CPS1/C12IN0-/VREF+/                                    | RA1      | TTL   | CMOS   | General purpose I/O.                          |

| SRI/ICSPCLK/ICDCLK                                             | AN1      | AN    |        | A/D Channel 1 input.                          |

|                                                                | CPS1     | AN    |        | Capacitive sensing input 1.                   |

|                                                                | C12IN0-  | AN    |        | Comparator C1 or C2 negative input.           |

|                                                                | VREF+    | AN    |        | A/D and DAC Positive Voltage Reference input. |

|                                                                | SRI      | ST    |        | SR latch input.                               |

|                                                                | ICSPCLK  | ST    |        | Serial Programming Clock.                     |

|                                                                | ICDCLK   | ST    |        | In-Circuit Debug Clock.                       |

| RA2/AN2/CPS2/T0CKI/INT/                                        | RA2      | ST    | CMOS   | General purpose I/O.                          |

| C1OUT/SRQ/CCP3/FLT0                                            | AN2      | AN    |        | A/D Channel 2 input.                          |

|                                                                | CPS2     | AN    |        | Capacitive sensing input 2.                   |

|                                                                | TOCKI    | ST    |        | Timer0 clock input.                           |

|                                                                | INT      | ST    |        | External interrupt.                           |

|                                                                | C10UT    | _     | CMOS   | Comparator C1 output.                         |

|                                                                | SRQ      | _     | CMOS   | SR latch non-inverting output.                |

|                                                                | CCP3     | ST    | CMOS   | Capture/Compare/PWM3.                         |

|                                                                | FLT0     | ST    |        | ECCP Auto-Shutdown Fault input.               |

| RA3/T1G <sup>(1)</sup> /VPP/MCLR                               | RA3      | TTL   |        | General purpose input.                        |

|                                                                | T1G      | ST    |        | Timer1 Gate input.                            |

|                                                                | VPP      | ΗV    |        | Programming voltage.                          |

|                                                                | MCLR     | ST    |        | Master Clear with internal pull-up.           |

| RA4/AN3/CPS3/OSC2/                                             | RA4      | TTL   | CMOS   | General purpose I/O.                          |

| CLKOUT/T1OSO/CLKR/P2B <sup>(1)</sup> /<br>T1G <sup>(1,2)</sup> | AN3      | AN    | _      | A/D Channel 3 input.                          |

| 116(.,-)                                                       | CPS3     | AN    |        | Capacitive sensing input 3.                   |

|                                                                | OSC2     | _     | CMOS   | Comparator C2 output.                         |

|                                                                | CLKOUT   | _     | CMOS   | Fosc/4 output.                                |

|                                                                | T10S0    | XTAL  | XTAL   | Timer1 oscillator connection.                 |

|                                                                | CLKR     | —     | CMOS   | Clock Reference output.                       |

|                                                                | P2B      | —     | CMOS   | PWM output.                                   |

|                                                                | T1G      | ST    | —      | Timer1 Gate input.                            |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C^{TM}$ = Schmitt Trigger input with  $I^2C$ HV = High VoltageXTAL = Crystallevels

Note 1: Pin functions can be moved using the APFCONO and APFCON1 registers (Register 12-1 and Register 12-2).

2: Default function location.

| Address             | Name                  | Bit 7                                 | Bit 6                                  | Bit 5            | Bit 4           | Bit 3          | Bit 2        | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|-----------------------|---------------------------------------|----------------------------------------|------------------|-----------------|----------------|--------------|--------|-----------|----------------------|---------------------------------|

| Bank 3              | 3                     |                                       |                                        |                  |                 |                |              |        |           |                      |                                 |

| 180h <sup>(1)</sup> | INDF0                 | Addressing th<br>(not a physic        |                                        | es contents of   | FSR0H/FSR0      | L to address   | data memory  | 1      |           | XXXX XXXX            | XXXX XXXX                       |

| 181h <sup>(1)</sup> | INDF1                 | Addressing the (not a physic)         |                                        | es contents of   | FSR1H/FSR1      | L to address   | data memory  | 1      |           | XXXX XXXX            | XXXX XXXX                       |

| 182h <sup>(1)</sup> | PCL                   | Program Cou                           | inter (PC) Lea                         | st Significant E | Byte            |                |              |        |           | 0000 0000            | 0000 0000                       |

| 183h <sup>(1)</sup> | STATUS                | _                                     | —                                      | —                | TO              | PD             | Z            | DC     | С         | 1 1000               | q quuu                          |

| 184h <sup>(1)</sup> | FSR0L                 | Indirect Data                         | Memory Addr                            | ess 0 Low Poir   | nter            |                |              |        |           | 0000 0000            | uuuu uuuu                       |

| 185h <sup>(1)</sup> | FSR0H                 | Indirect Data                         | Memory Addr                            | ess 0 High Poi   | inter           |                |              |        |           | 0000 0000            | 0000 0000                       |

| 186h <sup>(1)</sup> | FSR1L                 | Indirect Data                         | Memory Addr                            | ess 1 Low Poir   | nter            |                |              |        |           | 0000 0000            | uuuu uuuu                       |

| 187h <sup>(1)</sup> | FSR1H                 | Indirect Data                         | Memory Addr                            | ess 1 High Poi   | inter           |                |              |        |           | 0000 0000            | 0000 0000                       |

| 188h <sup>(1)</sup> | BSR                   | _                                     | —                                      | —                |                 |                | BSR<4:0>     |        |           | 0 0000               | 0 0000                          |

| 189h <sup>(1)</sup> | WREG                  | Working Reg                           | ister                                  |                  |                 |                |              |        |           | 0000 0000            | uuuu uuuu                       |

| 18Ah <sup>(1)</sup> | PCLATH                | _                                     | Write Buffer f                         | or the upper 7   | bits of the Pro | ogram Counte   | r            |        |           | -000 0000            | -000 0000                       |

| 18Bh <sup>(1)</sup> | INTCON                | GIE                                   | PEIE                                   | TMR0IE           | INTE            | IOCIE          | TMR0IF       | INTF   | IOCIF     | 0000 000x            | 0000 000u                       |

| 18Ch                | ANSELA                | _                                     | _                                      | _                | ANSA4           | _              | ANSA2        | ANSA1  | ANSA0     | 1 -111               | 1 -111                          |

| 18Dh                | ANSELB <sup>(2)</sup> | _                                     | _                                      | ANSB5            | ANSB4           | _              | _            | —      | _         | 11                   | 11                              |

| 18Eh                | ANSELC                | ANSC7 <sup>(2)</sup>                  | ANSC6 <sup>(2)</sup>                   | _                | _               | ANSC3          | ANSC2        | ANSC1  | ANSC0     | 11 1111              | 11 1111                         |

| 18Fh                | —                     | Unimplement                           | Unimplemented                          |                  |                 |                |              |        |           | _                    | _                               |

| 190h                | —                     | Unimplement                           | ed                                     |                  |                 |                |              |        |           | _                    | _                               |

| 191h                | EEADRL                | EEPROM/Pro                            | ogram Memor                            | y Address Reg    | ister Low Byte  | e              |              |        |           | 0000 0000            | 0000 0000                       |

| 192h                | EEADRH                | (4)                                   | EEPROM/Pro                             | ogram Memory     | Address Reg     | jister High By | te           |        |           | 1000 0000            | 1000 0000                       |

| 193h                | EEDATL                | EEPROM / P                            | rogram Memo                            | ry Read Data     | Register Low    | Byte           |              |        |           | XXXX XXXX            | uuuu uuuu                       |

| 194h                | EEDATH                | _                                     | —                                      | EEPROM / PI      | rogram Memo     | ry Read Data   | Register Hig | h Byte |           | xx xxxx              | uu uuuu                         |

| 195h                | EECON1                | EEPGD                                 | CFGS                                   | LWLO             | FREE            | WRERR          | WREN         | WR     | RD        | 0000 x000            | 0000 q000                       |

| 196h                | EECON2                | EEPROM co                             | EEPROM control register 2              |                  |                 |                |              |        |           | 0000 0000            | 0000 0000                       |

| 197h                | —                     | Unimplement                           | Unimplemented                          |                  |                 |                |              |        |           | —                    | _                               |

| 198h                | —                     | Unimplement                           | Unimplemented                          |                  |                 |                |              |        |           | _                    | _                               |

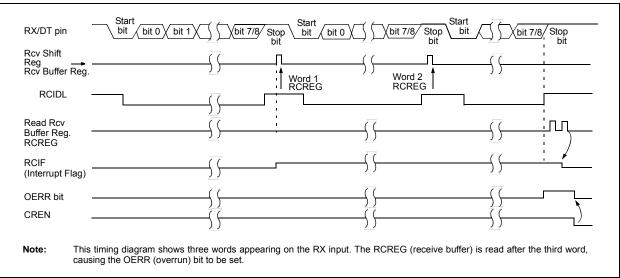

| 199h                | RCREG                 | USART Receive Data Register           |                                        |                  |                 |                |              |        | 0000 0000 | 0000 0000            |                                 |

| 19Ah                | TXREG                 | USART Transmit Data Register          |                                        |                  |                 |                |              |        | 0000 0000 | 0000 0000            |                                 |

| 19Bh                | SPBRGL                | Baud Rate Generator Data Register Low |                                        |                  |                 |                |              |        | 0000 0000 | 0000 0000            |                                 |

| 19Ch                | SPBRGH                | Baud Rate G                           | Baud Rate Generator Data Register High |                  |                 |                |              |        |           | 0000 0000            | 0000 0000                       |

| 19Dh                | RCSTA                 | SPEN                                  | RX9                                    | SREN             | CREN            | ADDEN          | FERR         | OERR   | RX9D      | 0000 000x            | 0000 000x                       |

| 19Eh                | TXSTA                 | CSRC                                  | TX9                                    | TXEN             | SYNC            | SENDB          | BRGH         | TRMT   | TX9D      | 0000 0010            | 0000 0010                       |

| 19Fh                | BAUDCON               | ABDOVF                                | RCIDL                                  | _                | SCKP            | BRG16          |              | WUE    | ABDEN     | 01-0 0-00            | 01-0 0-00                       |

#### TABLE 3-9 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

PIC16(L)F1828 only.

PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

**OSCILLATOR SWITCHING DELAYS**

#### Switch From Switch To Frequency **Oscillator Delay** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Sleep/POR Oscillator Warm-up Delay (TWARM) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC. RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> LFINTOSC DC - 32 MHz 1 cycle of each Timer1 Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> Any clock source 31 kHz 1 cycle of each Any clock source Timer1 Oscillator 32 kHz 1024 Clock Cycles (OST) PLL inactive PLL active 16-32 MHz 2 ms (approx.)

Note 1: PLL inactive.

**TABLE 5-1:**

#### TWO-SPEED START-UP MODE 5.4.1 CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Word 1 configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- · Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

When FSCM is enabled, Two-Speed Note: Start-up will automatically be enabled.

# 8.5.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 8-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

## REGISTER 8-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TMR1GIE | ADIE    | RCIE    | TXIE    | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:                                                                                                                                                        |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| R = Readable bit                                                                                                                                               |                                                                                                                                                                                                                                 | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U = Unimplemented bit, read as '0'                    |  |  |

| u = Bit is u                                                                                                                                                   | nchanged                                                                                                                                                                                                                        | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -n/n = Value at POR and BOR/Value at all other Resets |  |  |

| '1' = Bit is set '0' = Bit is cleared                                                                                                                          |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |

| bit 7                                                                                                                                                          |                                                                                                                                                                                                                                 | Timer1 Gate Interrupt Enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |  |  |

|                                                                                                                                                                | 0 = Disable                                                                                                                                                                                                                     | es the Timer1 Gate Acquisiti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | on interrupt                                          |  |  |

| bit 6                                                                                                                                                          | ADIE: A/D                                                                                                                                                                                                                       | Converter (ADC) Interrupt E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nable bit                                             |  |  |

|                                                                                                                                                                |                                                                                                                                                                                                                                 | es the ADC interrupt<br>es the ADC interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |  |  |

| bit 5                                                                                                                                                          |                                                                                                                                                                                                                                 | ART Receive Interrupt Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |  |  |

| <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul>                                                  |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |

| bit 4                                                                                                                                                          | 1 = Enable                                                                                                                                                                                                                      | RT Transmit Interrupt Enables the USART transmit interrest the USART transmit interrest the USART transmit intervention transmit int | upt                                                   |  |  |

| bit 3                                                                                                                                                          | SSP1IE: S                                                                                                                                                                                                                       | ynchronous Serial Port (MS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SP) Interrupt Enable bit                              |  |  |

|                                                                                                                                                                |                                                                                                                                                                                                                                 | es the MSSP interrupt<br>es the MSSP interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |  |  |

| bit 2                                                                                                                                                          | CCP1IE: C                                                                                                                                                                                                                       | CP1 Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |  |  |

|                                                                                                                                                                |                                                                                                                                                                                                                                 | es the CCP1 interrupt<br>es the CCP1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |  |  |

| bit 1 <b>TMR2IE:</b> TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the Timer2 to PR2 match interrupt<br>0 = Disables the Timer2 to PR2 match interrupt |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |

| bit 0                                                                                                                                                          | <ul> <li>0 = Disables the Timer2 to PR2 match interrupt</li> <li>TMR1IE: Timer1 Overflow Interrupt Enable bit</li> <li>1 = Enables the Timer1 overflow interrupt</li> <li>0 = Disables the Timer1 overflow interrupt</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |

# 8.5.7 PIR3 REGISTER

The PIR3 register contains the interrupt flag bits, as shown in Register 8-7.

Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 8-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | U-0   |

|-------|-----|---------|---------|---------|-----|---------|-------|

|       | —   | CCP4IF  | CCP3IF  | TMR6IF  | —   | TMR4IF  | —     |

| bit 7 |     |         |         |         |     |         | bit 0 |

| Legend:                                                  |                                 |                                    |                                                       |  |  |  |

|----------------------------------------------------------|---------------------------------|------------------------------------|-------------------------------------------------------|--|--|--|

| R = Readable bit                                         |                                 | W = Writable bit                   | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is u                                             | nchanged                        | x = Bit is unknown                 | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is                                             | set                             | '0' = Bit is cleared               |                                                       |  |  |  |

| bit 7-6                                                  | Unimplem                        | ented: Read as '0'                 |                                                       |  |  |  |

| bit 5                                                    | -                               | CP4 Interrupt Flag bit             |                                                       |  |  |  |

| 1 = Interrupt is pending<br>0 = Interrupt is not pending |                                 |                                    |                                                       |  |  |  |

| bit 4                                                    | CCP3IF: CCP3 Interrupt Flag bit |                                    |                                                       |  |  |  |

|                                                          |                                 | ot is pending<br>ot is not pending |                                                       |  |  |  |

| bit 3                                                    | TMR6IF: ⊤                       | MR6 to PR6 Match Interrup          | ot Flag bit                                           |  |  |  |

|                                                          |                                 | ot is pending<br>ot is not pending |                                                       |  |  |  |

| bit 2                                                    | Unimplem                        | ented: Read as '0'                 |                                                       |  |  |  |

| bit 1                                                    | TMR4IF: ⊤                       | MR4 to PR4 Match Interrup          | ot Flag bit                                           |  |  |  |

|                                                          |                                 | ot is pending<br>ot is not pending |                                                       |  |  |  |

| bit 0                                                    | Unimplemented: Read as '0'      |                                    |                                                       |  |  |  |

### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

| ; This               | write rout  | ine assumes the f | following:                                                 |

|----------------------|-------------|-------------------|------------------------------------------------------------|

| ; 1. Tł              | ne 16 bytes | of data are load  | led, starting at the address in DATA_ADDR                  |

| ; 2. Ea              | ach word of | data to be writt  | en is made up of two adjacent bytes in DATA_ADDR,          |

| ; st                 | tored in li | ttle endian forma | at                                                         |

| ; 3. A               | valid star  | ting address (the | e least significant bits = 000) is loaded in ADDRH:ADDRL   |

|                      |             |                   | in shared data memory 0x70 - 0x7F                          |

| ;                    |             |                   | -                                                          |

|                      | BCF         | INTCON,GIE        | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL     | EEADRH            | ; Bank 3                                                   |

|                      | MOVF        | ADDRH,W           | ; Load initial address                                     |

|                      | MOVWF       | EEADRH            | ;                                                          |

|                      | MOVF        | ADDRL,W           | ;                                                          |

|                      | MOVWF       | EEADRL            | ;                                                          |

|                      | MOVLW       |                   | ; Load initial data address                                |

|                      | MOVWF       | FSROL             | ;                                                          |

|                      | MOVLW       |                   | ; Load initial data address                                |

|                      | MOVWF       | FSROH             | ;                                                          |

|                      | BSF         | EECON1, EEPGD     | ; Point to program memory                                  |

|                      | BCF         |                   | ; Not configuration space                                  |

|                      | BSF         | EECON1, WREN      | ; Enable writes                                            |

|                      | BSF         | EECON1,LWLO       | ; Only Load Write Latches                                  |

| LOOP                 |             |                   |                                                            |

|                      | MOVIW       | FSR0++            | ; Load first data byte into lower                          |

|                      | MOVWF       | EEDATL            | ;                                                          |

|                      | MOVIW       | FSR0++            | ; Load second data byte into upper                         |

|                      | MOVWF       | EEDATH            | ;                                                          |

|                      |             |                   |                                                            |

|                      | MOVF        | EEADRL,W          | ; Check if lower bits of address are '000'                 |

|                      | XORLW       | 0x07              | ; Check if we're on the last of 8 addresses                |

|                      | ANDLW       | 0x07              | ;                                                          |

|                      | BTFSC       | STATUS, Z         | ; Exit if last of eight words,                             |

|                      | GOTO        | START_WRITE       | ;                                                          |

|                      |             | ~                 |                                                            |

|                      | MOVLW       | 55h               | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2            | ; Write 55h                                                |

| _ n                  | MOVLW       | 0AAh              | ;                                                          |

| Required<br>Sequence | MOVWF       | EECON2            | ; Write AAh                                                |

| qui                  | BSF         | EECON1,WR         | ; Set WR bit to begin write                                |

| sec de               | NOP         |                   | ; Any instructions here are ignored as processor           |

| - 07                 |             |                   | ; halts to begin write sequence                            |

|                      | NOP         |                   | ; Processor will stop here and wait for write to complete. |

|                      |             |                   |                                                            |

|                      |             |                   | ; After write processor continues with 3rd instruction.    |

|                      |             |                   |                                                            |

|                      | INCF        | EEADRL, F         | ; Still loading latches Increment address                  |

|                      | GOTO        | LOOP              | ; Write next latches                                       |

|                      |             |                   |                                                            |

| START_V              | WRITE       |                   |                                                            |

|                      | BCF         | EECON1,LWLO       | ; No more loading latches - Actually start Flash program   |

|                      |             |                   | ; memory write                                             |

|                      |             |                   |                                                            |

|                      | MOVLW       | 55h               | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2            | ; Write 55h                                                |

| Se Sd                | MOVLW       | 0AAh              | ;                                                          |

| uire                 | MOVWF       | EECON2            | ; Write AAh                                                |

| Required<br>Sequence | BSF         | EECON1,WR         | ; Set WR bit to begin write                                |

| ъÑ                   | NOP         |                   | ; Any instructions here are ignored as processor           |

|                      |             |                   | ; halts to begin write sequence                            |

|                      | NOP         |                   | ; Processor will stop here and wait for write complete.    |

| L                    |             |                   |                                                            |

|                      |             |                   | ; after write processor continues with 3rd instruction     |

|                      | BCF         | EECON1, WREN      | ; Disable writes                                           |

|                      | BSF         | INTCON,GIE        | ; Enable interrupts                                        |

|                      |             |                   |                                                            |

### REGISTER 11-1: EEDATL: EEPROM DATA REGISTER

| R/W-x/u             | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u         | R/W-x/u            | R/W-x/u                | R/W-x/u |

|---------------------|---------|----------------------|---------|-----------------|--------------------|------------------------|---------|

|                     |         |                      | EEDA    | T<7:0>          |                    |                        |         |

| bit 7               |         |                      |         |                 |                    |                        | bit 0   |

|                     |         |                      |         |                 |                    |                        |         |