Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1824-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**".

| R/W-0/0          | R/W-0/0                                                        | R/W-1/1                                                                                                                        | R/W-1/1        | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0         |  |

|------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|------------------|-----------------|--|

| CLKREN           | CLKROE                                                         | CLKRSLR                                                                                                                        | CLKR           | DC<1:0>           | (                | CLKRDIV<2:0>     | >               |  |

| bit 7            |                                                                |                                                                                                                                |                |                   |                  |                  | bit (           |  |

|                  |                                                                |                                                                                                                                |                |                   |                  |                  |                 |  |

| Legend:          |                                                                |                                                                                                                                |                |                   |                  |                  |                 |  |

| R = Readable     | e bit                                                          | W = Writable                                                                                                                   | bit            | -                 | nented bit, read |                  |                 |  |

| u = Bit is unc   | hanged                                                         | x = Bit is unkr                                                                                                                | nown           | -n/n = Value a    | at POR and BC    | R/Value at all   | other Resets    |  |

| '1' = Bit is set | t                                                              | '0' = Bit is clea                                                                                                              | ared           |                   |                  |                  |                 |  |

| bit 7            | <b>CLKREN:</b> R                                               | eference Clock                                                                                                                 | Module Enab    | le bit            |                  |                  |                 |  |

|                  |                                                                | ce Clock modul<br>ce Clock modul                                                                                               |                |                   |                  |                  |                 |  |

| bit 6            |                                                                | eference Clock                                                                                                                 |                |                   |                  |                  |                 |  |

|                  |                                                                | <ul> <li>1 = Reference Clock output is enabled on CLKR pin</li> <li>0 = Reference Clock output disabled on CLKR pin</li> </ul> |                |                   |                  |                  |                 |  |

| bit 5            | CLKRSLR: Reference Clock Slew Rate Control Limiting Enable bit |                                                                                                                                |                |                   |                  |                  |                 |  |

|                  | 1 = Slew Rate limiting is enabled                              |                                                                                                                                |                |                   |                  |                  |                 |  |

|                  | 0 = Slew Ra                                                    | 0 = Slew Rate limiting is disabled                                                                                             |                |                   |                  |                  |                 |  |

| bit 4-3          | CLKRDC<1                                                       | :0>: Reference                                                                                                                 | Clock Duty Cy  | ycle bits         |                  |                  |                 |  |

|                  |                                                                | 11 = Clock outputs duty cycle of 75%                                                                                           |                |                   |                  |                  |                 |  |

|                  |                                                                | outputs duty cyc<br>outputs duty cyc                                                                                           |                |                   |                  |                  |                 |  |

|                  |                                                                | outputs duty cyc                                                                                                               |                |                   |                  |                  |                 |  |

| bit 2-0          |                                                                | ::0> Reference (                                                                                                               |                | bits              |                  |                  |                 |  |

|                  | 111 = Base                                                     | clock value divi                                                                                                               | ded by 128     |                   |                  |                  |                 |  |

|                  |                                                                | clock value divi                                                                                                               | •              |                   |                  |                  |                 |  |

|                  |                                                                | 101 = Base clock value divided by 32                                                                                           |                |                   |                  |                  |                 |  |

|                  |                                                                | clock value divi                                                                                                               |                |                   |                  |                  |                 |  |

|                  |                                                                | clock value divi                                                                                                               |                |                   |                  |                  |                 |  |

|                  |                                                                | clock value divi                                                                                                               |                |                   |                  |                  |                 |  |

|                  | 000 = Base                                                     | clock value <sup>(2)</sup>                                                                                                     |                |                   |                  |                  |                 |  |

| Note 1: In       | this mode, the                                                 | 25% and 75%                                                                                                                    | duty cycle acc | curacy will be de | ependent on the  | e source clock   | duty cycle.     |  |

| <b>2:</b> Ir     | n this mode, the                                               | duty cycle will a                                                                                                              | always be equ  | ual to the source | e clock duty cyc | ele, unless a du | ity cycle of 0° |  |

| • .              |                                                                |                                                                                                                                |                |                   |                  |                  |                 |  |

#### REGISTER 6-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

- is selected.

3: To route CLKR to pin, CLKOUTEN of Configuration Word 1 = 1 is required. CLKOUTEN of Configuration

- Word 1 = 0 will result in Fosc/4. See Section 6.3 "Conflicts with the CLKR pin" for details.

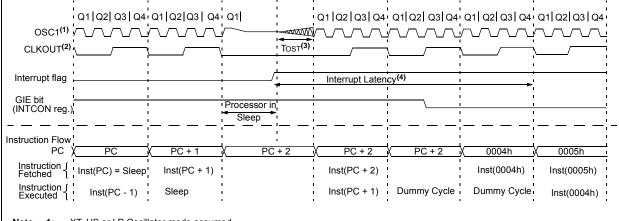

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

#### FIGURE 9-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note 1:** XT, HS or LP Oscillator mode assumed.

2: CLKOUT is not available in XT, HS, or LP Oscillator modes, but shown here for timing reference.

3: TOST = 1024 TOSC (drawing not to scale). This delay applies only to XT, HS or LP Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name                 | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|----------------------|---------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON               | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 89                  |

| IOCAF                | _       |        | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 137                 |

| IOCAN                | _       |        | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 137                 |

| IOCAP                | _       | _      | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 137                 |

| IOCBF <sup>(1)</sup> | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | _      | _      | _      | —      | 139                 |

| IOCBN <sup>(1)</sup> | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | _      | _      |        | —      | 138                 |

| IOCBP <sup>(1)</sup> | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | _      | _      | _      | —      | 138                 |

| PIE1                 | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 90                  |

| PIE2                 | OSFIE   | C2IE   | C1IE   | EEIE   | BCL1IE | _      | _      | CCP2IE | 91                  |

| PIR1                 | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 93                  |

| PIR2                 | OSFIF   | C2IF   | C1IF   | EEIF   | BCL1IF | _      |        | CCP2IF | 94                  |

| STATUS               | —       | —      | —      | TO     | PD     | Z      | DC     | С      | 22                  |

| WDTCON               |         |        | WDTPS4 | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | SWDTEN | 101                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

Note 1: PIC16(L)F1828 only.

#### 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

#### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when the write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

#### EXAMPLE 11-2: DATA EEPROM WRITE

| MOV<br>MOV<br>MOV<br>BCF     | LW DATA_EE_DAT<br>WF EEDATL<br>EECON1, CFC<br>EECON1, EE                                               | ;Data Memory Address to write<br>TA ;<br>;Data Memory Value to write<br>SS ;Deselect Configuration space<br>PGD ;Point to DATA memory |

|------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| eunende<br>BSF<br>BSF<br>BCF | LW 55h<br>WF EECON2<br>LW 0AAh<br>WF EECON2<br>EECON1, WR<br>EECON1, WR<br>EECON1, WR<br>SC EECON1, WR | ;<br>;Write AAh<br>;Set WR bit to begin write<br>E ;Enable Interrupts<br>EN ;Disable writes                                           |

|                              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    |

|------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------|--------------------------------|--------------------------------|

| Flash ADDR                   | <br>()<br>                     | PC + 1                         | EEADRH,EEADRL                  | PC + 3                   | PC + 4                         | PC + 5                         |

| Flash Data                   |                                | TR (PC)                        | R (PC + 1) EEDA                | TH,EEDATL INST           | R (PC + 3) INST                | R (PC + 4)                     |

|                              | INSTR(PC - 1)<br>executed here | BSF EECON1,RD<br>executed here | INSTR(PC + 1)<br>executed here | Forced NOP executed here | INSTR(PC + 3)<br>executed here | INSTR(PC + 4)<br>executed here |

| RD bit                       |                                |                                | /                              |                          |                                |                                |

| EEDATH<br>EEDATL<br>Register |                                |                                |                                | Χ                        |                                |                                |

| EERHLT                       | <br>  <br>1                    | <br>                           | /                              |                          |                                |                                |

#### 12.2 PORTA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-4). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize PORTA.

Reading the PORTA register (Register 12-3) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-4) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The INLVLA register (Register 12-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Characteristics: PIC16(L)F1824/8-I/E" for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 12.2.1 WEAK PULL-UPS

Each of the PORTA pins has an individually configurable internal weak pull-up. Control bits WPUA<5:0> enable or disable each pull-up (see Register 12-7). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION\_REG register.

#### 12.2.2 ANSELA REGISTER

The ANSELA register (Register 12-6) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA register must be initialized     |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | to configure an analog channel as a digital |  |  |  |  |  |

|       | input. Pins configured as analog inputs     |  |  |  |  |  |

|       | will read '0'.                              |  |  |  |  |  |

#### EXAMPLE 12-1: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0                                   | U-0 | R/W-1/1          | R/W-1/1 | U-0                                                   | U-0                | U-0   | U-0   |  |

|---------------------------------------|-----|------------------|---------|-------------------------------------------------------|--------------------|-------|-------|--|

| —                                     | _   | ANSB5            | ANSB4   |                                                       | —                  | —     | —     |  |

| bit 7                                 |     | -                |         |                                                       |                    |       | bit 0 |  |

|                                       |     |                  |         |                                                       |                    |       |       |  |

| Legend:                               |     |                  |         |                                                       |                    |       |       |  |

| R = Readable bit                      |     | W = Writable bi  | t       | U = Unimpleme                                         | ented bit, read as | s 'O' |       |  |

| u = Bit is unchang                    | ged | x = Bit is unkno | wn      | -n/n = Value at POR and BOR/Value at all other Resets |                    |       |       |  |

| '1' = Bit is set '0' = Bit is cleared |     |                  |         |                                                       |                    |       |       |  |

| DIT 7-6 | Unimplemented: Read as 0                                                                                                                                                                                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <ul> <li>ANSB&lt;5:4&gt;: Analog Select between Analog or Digital Function on pins RB&lt;5:4&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### **REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER**

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 WPUB<7:4>: Weak Pull-up Register bits<sup>(1,2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled bit 3-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-14: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | INLVLB<7:4>: PORTB Input Level Select bits                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | For RB<7:4> pins, respectively                                                                                                               |

|         | <ul><li>1 = ST input used for PORT reads and interrupt-on-change</li><li>0 = TTL input used for PORT reads and interrupt-on-change</li></ul> |

| bit 3-0 | Unimplemented: Read as '0                                                                                                                    |

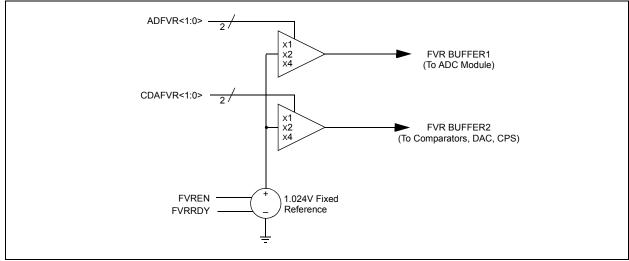

#### 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR), is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

#### 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, and DAC is routed through two independent programmable gain amplifiers. Each amplifier can be configured to amplify the reference voltage by 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 16.0 "Analog-to-Digital Converter (ADC) Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 19.0 "Comparator Module" for additional information.

#### 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 30.0** "**Electrical Specifications**" for the minimum delay requirement.

#### FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

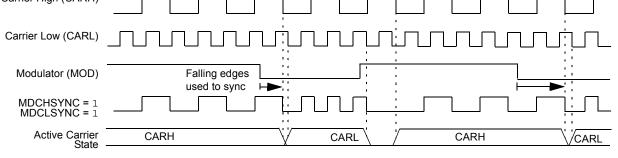

| FIGURE 23-4:                 | CARRIER LOW SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| Carrier High (CARH)          |                                                          |

| Carrier Low (CARL)           |                                                          |

| Modulator (MOD)              |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State -    |                                                          |

| FIGURE 23-5:                 | FULL SYNCHRONIZATION (MDSHSYNC = 1, MDCLSYNC = 1)        |

| Carrier High (CARH)          |                                                          |

#### 25.7.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

#### 26.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 26.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 26.4.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

### TABLE 26-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6                 | Bit 5                | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|-----------------------|----------------------|-------|--------|---------|--------|--------|---------------------|

| APFCON0 | RXDTSEL                       | SDOSEL <sup>(1)</sup> | SSSEL <sup>(1)</sup> | _     | T1GSEL | TXCKSEL | _      | _      | 117                 |

| BAUDCON | ABDOVF                        | RCIDL                 | -                    | SCKP  | BRG16  | _       | WUE    | ABDEN  | 296                 |

| INTCON  | GIE                           | PEIE                  | TMR0IE               | INTE  | IOCIE  | TMR0IF  | INTF   | IOCIF  | 89                  |

| PIE1    | TMR1GIE                       | ADIE                  | RCIE                 | TXIE  | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 90                  |

| PIR1    | TMR1GIF                       | ADIF                  | RCIF                 | TXIF  | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 93                  |

| RCSTA   | SPEN                          | RX9                   | SREN                 | CREN  | ADDEN  | FERR    | OERR   | RX9D   | 295                 |

| TXREG   | EUSART Transmit Data Register |                       |                      | 287*  |        |         |        |        |                     |

| TXSTA   | CSRC                          | TX9                   | TXEN                 | SYNC  | SENDB  | BRGH    | TRMT   | TX9D   | 294                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

Note 1: PIC16(L)F1824 only.

#### 27.4 Current Ranges

The Capacitive Sensing Oscillator can operate within several different current ranges, depending on the Voltage Reference mode and current range selections. Within each of the two Voltage Reference modes there are four current ranges.

Selection between the Voltage Reference modes is controlled by the CPSRM bit of the CPSCON0 register. Clearing this bit selects the Fixed Voltage References provided by the Capacitive Sensing Oscillator module. Setting this bit selects the variable voltage references supplied by the Fixed Voltage Reference (FVR) module and the Digital-to-Analog Converter (DAC) module. See **Section 27.3 "Voltage Reference Modes**" for more information on configuring the voltage references. Selecting the current range within the voltage reference mode is controlled by configuring the CPSRNG<1:0> bits in the CPSCON0 register. See Table 27-1 for proper current mode selection. The Noise Detection mode is unique in that it disables the constant current source associated with the selected input pin, but leaves the rest of the oscillator circuitry and pin structure active. This eliminates the oscillation frequency on the analog pin and greatly reduces the current consumed by the Oscillator module. When noise is introduced onto the pin, the oscillator is driven at the frequency determined by the noise. This produces a detectable signal at the comparator stage, indicating the presence of activity on the pin. Figure 27-2 shows a more detailed drawing of the constant current sources and comparators associated with the oscillator and input pin.

| CPSRM | Voltage Reference Mode | CPSRNG<1:0> | Current Range <sup>(1)</sup> |

|-------|------------------------|-------------|------------------------------|

|       |                        | 00          | Off                          |

| 0     | Fixed                  | 01          | Low                          |

| 0     | Fixed                  | 10          | Medium                       |

|       |                        | 11          | High                         |

|       |                        | 00          | Noise Detection              |

| 1     |                        | 01          | Low                          |

| Ţ     | Variable               | 10          | Medium                       |

|       |                        | 11          | High                         |

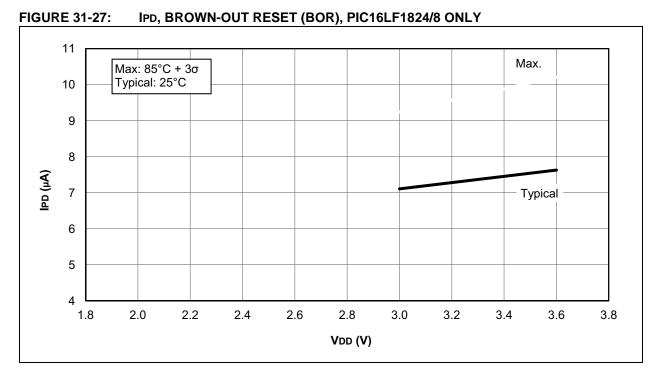

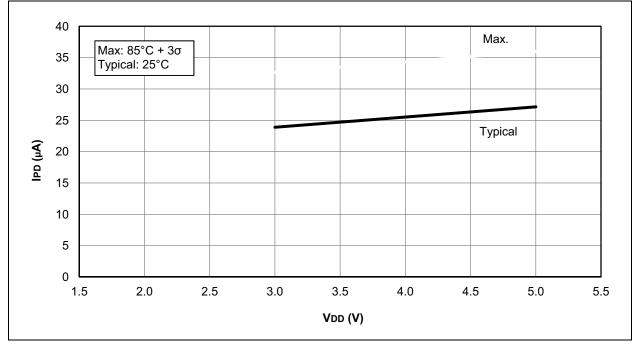

Note 1: See Power-Down Currents (IPD) in Section 30.3 "DC Characteristics: PIC16(L)F1824/8-I/E (Power-Down)" for more information.

| LSLF                             | Logical Left Shift                                                                                                                                                                                                                          | MOVF             | Move f                                                                                                                                                                                                                                                                            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                          | [ <i>label</i> ]LSLF f{,d}                                                                                                                                                                                                                  | Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |

| Operands:                        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                          | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                |

| Operation:                       | $(f < 7 >) \rightarrow C$                                                                                                                                                                                                                   | Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |

|                                  | $(f<6:0>) \rightarrow dest<7:1>$<br>0 $\rightarrow dest<0>$                                                                                                                                                                                 | Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Status Affected:<br>Description: | C, Z<br>The contents of register 'f' are shifted<br>one bit to the left through the Carry flag.<br>A '0' is shifted into the LSb. If 'd' is '0',<br>the result is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'. | Description:     | The contents of register f is moved to<br>a destination dependent upon the<br>status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ , the<br>destination is file register f itself. $d = 1$<br>is useful to test a file register since<br>status flag Z is affected. |

|                                  | C                                                                                                                                                                                                                                           | Words:           | 1                                                                                                                                                                                                                                                                                 |

|                                  |                                                                                                                                                                                                                                             | Cycles:          | 1                                                                                                                                                                                                                                                                                 |

|                                  |                                                                                                                                                                                                                                             | Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                       |

| LSRF                             | Logical Right Shift                                                                                                                                                                                                                         |                  | After Instruction<br>W = value in FSR register                                                                                                                                                                                                                                    |

| Syntax:                          | [ <i>label</i> ] LSRF f {,d}                                                                                                                                                                                                                |                  | Z = 1                                                                                                                                                                                                                                                                             |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in \left[0,1\right] \end{array}$                                                                                                                                                          |

| Operation:       | $\begin{array}{l} 0 \rightarrow dest < 7 > \\ (f < 7:1 >) \rightarrow dest < 6:0 >, \\ (f < 0 >) \rightarrow C, \end{array}$                                                                                                         |

| Status Affected: | C, Z                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is stored back in register 'f'. |

|                  |                                                                                                                                                                                                                                      |

| 0- | register f | ⊢ C | 1 |

|----|------------|-----|---|

|    | Tegister i |     | J |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |  |

| Operands:        | None                                                                                                                                                  |  |  |  |

| Operation:       | $TOS \to PC$                                                                                                                                          |  |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                      |                  |                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      | RLF              | Rotate Left f through Carry                                                                                                                                                       |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                          |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                          | Operation:       | See description below                                                                                                                                                             |

|                  |                                                                                                                                                                               | Status Affected: | С                                                                                                                                                                                 |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is |

| Words:           | 1                                                                                                                                                                             |                  | stored back in register 'f'.                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                                                             |                  |                                                                                                                                                                                   |

| Example:         | CALL TABLE;W contains table                                                                                                                                                   | Words:           | 1                                                                                                                                                                                 |

|                  | <pre>;offset value ,W now has table value</pre>                                                                                                                               | Cycles:          | 1                                                                                                                                                                                 |

| TABLE            | •                                                                                                                                                                             | Example:         | RLF REG1,0                                                                                                                                                                        |

|                  | •<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table                                                                         |                  | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                                                                              |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                        |                  |                                                                                                                                                                                   |

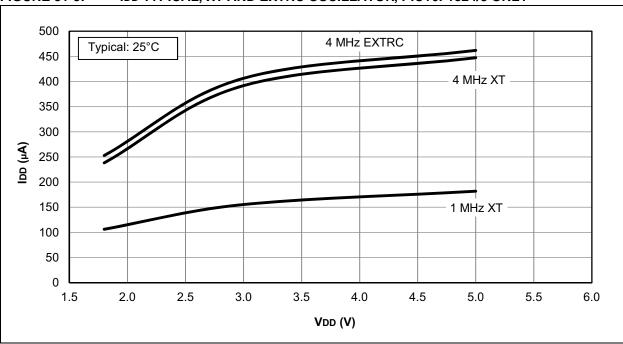

FIGURE 31-6: IDD MAXIMUM, XT AND EXTRC OSCILLATOR, PIC16F1824/8 ONLY

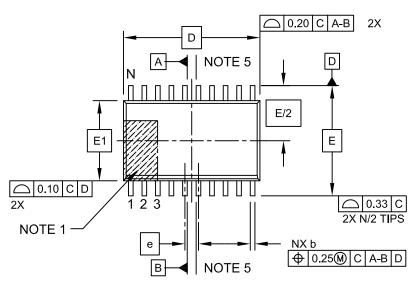

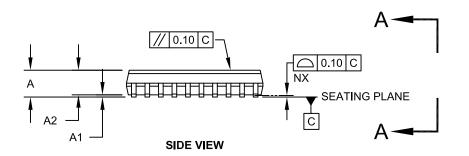

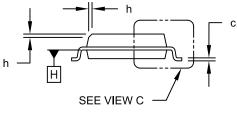

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2