Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1824-e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

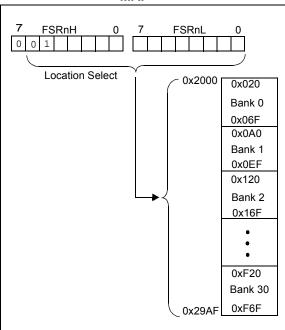

#### 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

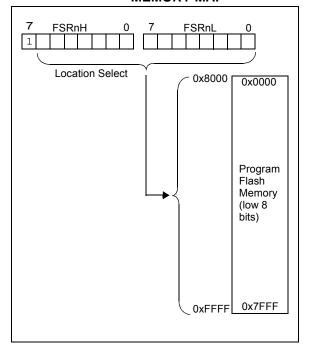

#### 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-11: PROGRAM FLASH MEMORY MAP

### REGISTER 6-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-1/1     | R/W-0/0 | R/W-0/0 | R/W-0/0      | R/W-0/0 |

|---------|---------|---------|-------------|---------|---------|--------------|---------|

| CLKREN  | CLKROE  | CLKRSLR | CLKRDC<1:0> |         | (       | CLKRDIV<2:0> | •       |

| bit 7   |         |         |             |         |         |              | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **CLKREN:** Reference Clock Module Enable bit 1 = Reference Clock module is enabled 0 = Reference Clock module is disabled bit 6 **CLKROE:** Reference Clock Output Enable bit<sup>(3)</sup> 1 = Reference Clock output is enabled on CLKR pin 0 = Reference Clock output disabled on CLKR pin bit 5 **CLKRSLR:** Reference Clock Slew Rate Control Limiting Enable bit 1 = Slew Rate limiting is enabled 0 = Slew Rate limiting is disabled bit 4-3 CLKRDC<1:0>: Reference Clock Duty Cycle bits 11 = Clock outputs duty cycle of 75% 10 = Clock outputs duty cycle of 50% 01 = Clock outputs duty cycle of 25% 00 = Clock outputs duty cycle of 0% bit 2-0 CLKRDIV<2:0> Reference Clock Divider bits 111 = Base clock value divided by 128 110 = Base clock value divided by 64 101 = Base clock value divided by 32 100 = Base clock value divided by 16 011 = Base clock value divided by 8

> 010 = Base clock value divided by 4 001 = Base clock value divided by 2<sup>(1)</sup>

000 = Base clock value<sup>(2)</sup>

Note 1: In this mode, the 25% and 75% duty cycle accuracy will be dependent on the source clock duty cycle.

- 2: In this mode, the duty cycle will always be equal to the source clock duty cycle, unless a duty cycle of 0% is selected.

- 3: To route CLKR to pin, CLKOUTEN of Configuration Word 1 = 1 is required. CLKOUTEN of Configuration Word 1 = 0 will result in Fosc/4. See Section 6.3 "Conflicts with the CLKR pin" for details.

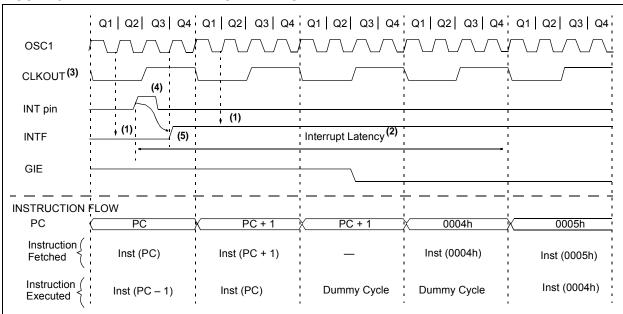

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-5 TcY. Synchronous latency = 3-4 TcY, where TcY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is not available in all oscillator modes.

- 4: For minimum width of INT pulse, refer to the AC specifications in Section 30.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

### 8.5.3 PIE2 REGISTER

The PIE2 register contains the interrupt enable bits, as shown in Register 8-3.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### REGISTER 8-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|---------|---------|---------|-----|-----|---------|

| OSFIE   | C2IE    | C1IE    | EEIE    | BCL1IE  | _   | _   | CCP2IE  |

| bit 7   |         |         |         |         |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | OSFIE: Oscillator Fail Interrupt Enable bit  1 = Enables the Oscillator Fail interrupt  0 = Disables the Oscillator Fail interrupt                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | C2IE: Comparator C2 Interrupt Enable bit  1 = Enables the Comparator C2 interrupt  0 = Disables the Comparator C2 interrupt                                      |

| bit 5   | C1IE: Comparator C1 Interrupt Enable bit  1 = Enables the Comparator C1 interrupt  0 = Disables the Comparator C1 interrupt                                      |

| bit 4   | <b>EEIE:</b> EEPROM Write Completion Interrupt Enable bit  1 = Enables the EEPROM Write Completion interrupt  0 = Disables the EEPROM Write Completion interrupt |

| bit 3   | BCL1IE: MSSP Bus Collision Interrupt Enable bit  1 = Enables the MSSP Bus Collision Interrupt  0 = Disables the MSSP Bus Collision Interrupt                     |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 0   | CCP2IE: CCP2 Interrupt Enable bit  1 = Enables the CCP2 Interrupt  0 = Disables the CCP2 Interrupt                                                               |

#### **EXAMPLE 11-2: DATA EEPROM WRITE**

```

BANKSEL EEADRL

MOVLW

DATA_EE_ADDR

;

MOVWF

EEADRL

;Data Memory Address to write

MOVLW

DATA_EE_DATA

MOVWF

EEDATL

;Data Memory Value to write

BCF

EECON1, CFGS

;Deselect Configuration space

EECON1, EEPGD ; Point to DATA memory

BCF

;Enable writes

EECON1, WREN

BSF

BCF

INTCON, GIE

;Disable INTs.

MOVLW

55h

MOVWF

EECON2

;Write 55h

MOVLW

0AAh

MOVWF

EECON2

;Write AAh

BSF

EECON1, WR

;Set WR bit to begin write

INTCON, GIE

;Enable Interrupts

BSF

BCF

EECON1, WREN

;Disable writes

BTFSC

EECON1, WR

;Wait for write to complete

GOTO

;Done

```

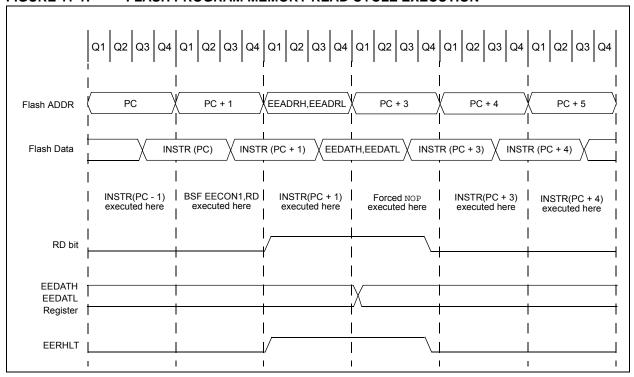

#### FIGURE 11-1: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

### REGISTER 11-6: EECON2: EEPROM CONTROL 2 REGISTER

| W-0/0                     | W-0/0 | W-0/0 | W-0/0 | W-0/0 | W-0/0 | W-0/0 | W-0/0 |  |  |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| EEPROM Control Register 2 |       |       |       |       |       |       |       |  |  |

| bit 7                     |       |       |       |       | _     |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

S = Bit can only be set x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

#### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 11.2.2 "Writing to the Data EEPROM Memory"** for more information.

TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7                                               | Bit 6 | Bit 5  | Bit 4 | Bit 3   | Bit 2  | Bit 1 | Bit 0  | Register on Page |

|--------|-----------------------------------------------------|-------|--------|-------|---------|--------|-------|--------|------------------|

| EECON1 | EEPGD                                               | CFGS  | LWLO   | FREE  | WRERR   | WREN   | WR    | RD     | 114              |

| EECON2 | EEPROM Control Register 2 (not a physical register) |       |        |       |         |        |       |        |                  |

| EEADRL | EEADRL<7:0>                                         |       |        |       |         |        |       |        | 113              |

| EEADRH | (1) EEADRH<6:0                                      |       |        |       |         |        |       |        | 113              |

| EEDATL |                                                     |       |        | EEDAT | TL<7:0> |        |       |        | 113              |

| EEDATH | _                                                   | _     |        |       | EEDAT   | H<5:0> |       |        | 113              |

| INTCON | GIE                                                 | PEIE  | TMR0IE | INTE  | IOCIE   | TMR0IF | INTF  | IOCIF  | 89               |

| PIE2   | OSFIE                                               | C2IE  | C1IE   | EEIE  | BCL1IE  | _      | _     | CCP2IE | 91               |

| PIR2   | OSFIF                                               | C2IF  | C1IF   | EEIF  | BCL1IF  | _      | _     | CCP2IF | 94               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by data EEPROM module.

Page provides register information.

Note 1: Unimplemented, read as '1'.

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|---------|---------|-----|-----|-----|-------|

| _     | _   | ANSB5   | ANSB4   | _   | _   | _   | _     |

| bit 7 |     |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-4 ANSB<5:4>: Analog Select between Analog or Digital Function on pins RB<5:4>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

bit 3-0 **Unimplemented:** Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 WPUB<7:4>: Weak Pull-up Register bits<sup>(1,2)</sup>

1 = Pull-up enabled0 = Pull-up disabled

bit 3-0 **Unimplemented:** Read as '0'

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-14: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 INLVLB<7:4>: PORTB Input Level Select bits

For RB<7:4> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

bit 3-0 **Unimplemented:** Read as '0

### REGISTER 12-20: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| U-0 <sup>(3)</sup><br>R/W-1/1 <sup>(2)</sup> | U <sub>-0</sub> (3)<br>R/W-1/1 <sup>(2)</sup> | R/W-0/0 <sup>(3)</sup><br>R/W-1/1 <sup>(2)</sup> |

|----------------------------------------------|-----------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| INLVLC7 <sup>(1)</sup>                       | INLVLC6 <sup>(1)</sup>                        | INLVLC5                                          | INLVLC4                                          | INLVLC3                                          | INLVLC2                                          | INLVLC1                                          | INLVLC0                                          |

| bit 7                                        |                                               |                                                  |                                                  |                                                  |                                                  |                                                  | bit 0                                            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits<sup>(1)</sup>

For RC<7:0> pins, respectively

${\tt 1}$  = ST input used for PORT reads and Interrupt-on-Change

0 = TTL input used for PORT reads and Interrupt-on-Change

Note 1: INLVLC<7:6> available on PIC16(L)F1828 only. Otherwise, they are unimplemented and read as '0'.

2: PIC16(L)F1828 only, Reset default value.

3: PIC16(L)F1824 only, Reset default value.

TABLE 12-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|--------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|------------------|

| ANSELC | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _       | _       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 133              |

| INLVLC | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 134              |

| LATC   | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 132              |

| PORTC  | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 132              |

| TRISC  | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 132              |

| WPUC   | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 133              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations, read as '0'. Shaded cells are not used by PORTC.

**Note 1:** PIC16(L)F1828 only.

#### 24.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

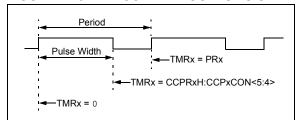

Figure 24-3 shows a typical waveform of the PWM signal.

#### 24.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for CCP modules ECCP1, ECCP2, CCP3 and CCP4.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- · CCPRxL registers

- · CCPxCON registers

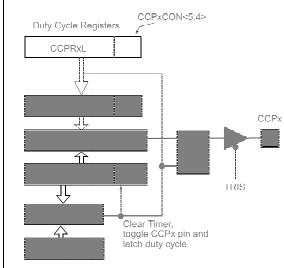

Figure 24-4 shows a simplified block diagram of PWM operation.

- **Note 1:** The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- **2:** Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 24-3: CCP PWM OUTPUT SIGNAL

## FIGURE 24-4: SIMPLIFIED PWM BLOCK DIAGRAM

- Note 1: The 8 bit timer TMRx register is concatenated with the 2-bit internal system clock (FOSC), or 2 bits of the prescaler, to create the 10-bit time

- 2: In PWM mode, CCPRxH is a read-only register.

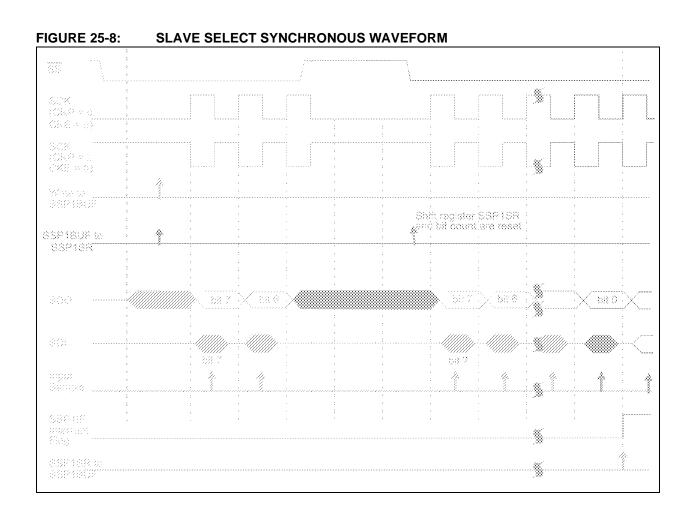

**FIGURE 25-7: SPI DAISY-CHAIN CONNECTION** SCK SCK SPI Master SDO SDI SPI Slave #1 SDI SDO General I/O SS SCK SDI SPI Slave #2 SDO SS SCK SDI SPI Slave #3 SDO SS

#### 25.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSP1STAT register is set. The received address is loaded into the SSP1BUF register, and an  $\overline{ACK}$  pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 25.5.6** "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSP1BUF register which also loads the SSP1SR register. Then the SCL pin should be released by setting the CKP bit of the SSP1CON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This  $\overline{ACK}$  value is copied to the ACKSTAT bit of the SSP1CON2 register. If ACKSTAT is set (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the not  $\overline{ACK}$  is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSP1BUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP1 interrupt is generated for each data transfer byte. The SSP1IF bit must be cleared by software and the SSP1STAT register is used to determine the status of the byte. The SSP1IF bit is set on the falling edge of the ninth clock pulse.

#### 25.5.3.1 Slave Mode Bus Collision

A slave receives a read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSP1CON3 register is set, the BCL1IF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCL1IF bit to handle a slave bus collision.

#### 25.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 25-18 can be used as a reference to this list.

- Master sends a Start condition on SDA and SCL.

- S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the Slave setting SSP1IF bit.

- Slave hardware generates an ACK and sets SSP1IF.

- 5. SSP1IF bit is cleared by user.

- Software reads the received address from SSP1BUF, clearing BF.

- R/W is set so CKP was automatically cleared after the ACK.

- The slave software loads the transmit data into SSP1BUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSP1IF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSP1IF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master  $\overline{\mathsf{ACK}}$ s the clock will be stretched.

- **2:** ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSP1IF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

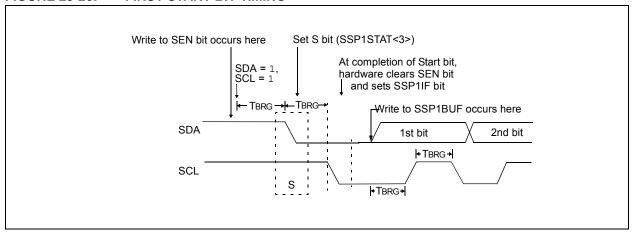

# 25.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN bit of the SSP1CON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSP1STAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSP1ADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSP1CON2 register will be automatically cleared

by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCL1IF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

**2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

#### FIGURE 25-26: FIRST START BIT TIMING

SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>CTM OPERATION **TABLE 25-3:**

| Name                  | Bit 7                                                            | Bit 6                  | Bit 5   | Bit 4   | Bit 3     | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values on<br>Page: |

|-----------------------|------------------------------------------------------------------|------------------------|---------|---------|-----------|---------|---------|---------|-----------------------------|

| INLVLB <sup>(1)</sup> | INLVLB7                                                          | INLVLB6                | INLVLB5 | INLVLB4 | _         | _       | _       | _       | 128                         |

| INLVLC                | INLVLC7 <sup>(1)</sup>                                           | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3   | INLVLC2 | INLVLC1 | INLVLC0 | 134                         |

| INTCON                | GIE                                                              | PEIE                   | TMR0IE  | INTE    | IOCIE     | TMR0IF  | INTF    | IOCIF   | 89                          |

| PIE1                  | TMR1GIE                                                          | ADIE                   | RCIE    | TXIE    | SSP1IE    | CCP1IE  | TMR2IE  | TMR1IE  | 90                          |

| PIE2                  | OSFIE                                                            | C2IE                   | C1IE    | EEIE    | BCL1IE    | _       | _       | CCP2IE  | 91                          |

| PIR1                  | TMR1GIF                                                          | ADIF                   | RCIF    | TXIF    | SSP1IF    | CCP1IF  | TMR2IF  | TMR1IF  | 93                          |

| PIR2                  | OSFIF                                                            | C2IF                   | C1IF    | EEIF    | BCL1IF    | _       | _       | CCP2IF  | 94                          |

| SSP1ADD               | ADD7                                                             | ADD6                   | ADD5    | ADD4    | ADD3      | ADD2    | ADD1    | ADD0    | 284                         |

| SSP1BUF               | SSP1BUF Synchronous Serial Port Receive Buffer/Transmit Register |                        |         |         |           | 234*    |         |         |                             |

| SSP1CON1              | WCOL                                                             | SSPOV                  | SSPEN   | CKP     | SSPM<3:0> |         |         | 281     |                             |

| SSP1CON2              | GCEN                                                             | ACKSTAT                | ACKDT   | ACKEN   | RCEN      | PEN     | RSEN    | SEN     | 282                         |

| SSP1CON3              | ACKTIM                                                           | PCIE                   | SCIE    | BOEN    | SDAHT     | SBCDE   | AHEN    | DHEN    | 283                         |

| SSP1MSK               | MSK7                                                             | MSK6                   | MSK5    | MSK4    | MSK3      | MSK2    | MSK1    | MSK0    | 284                         |

| SSP1STAT              | SMP                                                              | CKE                    | D/Ā     | Р       | S         | R/W     | UA      | BF      | 280                         |

| TRISB <sup>(1)</sup>  | TRISB7                                                           | TRISB6                 | TRISB5  | TRISB4  | _         | _       | _       | _       | 127                         |

| TRISC <sup>(2)</sup>  | _                                                                |                        | TRISC5  | TRISC4  | TRISC3    | TRISC2  | TRISC1  | TRISC0  | 127                         |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C™ mode.

Page provides register information. PIC16(L)F1828 only. Note

1:

Unshaded cells apply to PIC16(L)F1824 only.

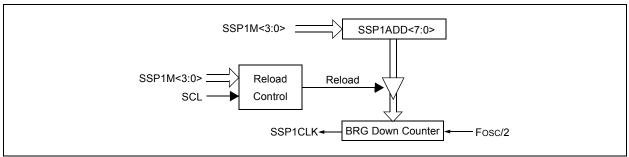

#### 25.7 Baud Rate Generator

The MSSP1 module has a Baud Rate Generator available for clock generation in both  $I^2C$  and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSP1ADD register (Register 25-6). When a write occurs to SSP1BUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 25-40 triggers the value from SSP1ADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP1 is being operated in.

Table 25-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSP1ADD.

### **EQUATION 25-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

FIGURE 25-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSP1ADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

TABLE 25-4: MSSP1 CLOCK RATE W/BRG

| Fosc   | FcY   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical and timing specifications in Table 30-4 and Figure 30-7 to ensure the system is designed to support the I/O requirements.

### 26.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 26-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 26.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the TX/CK I/O pin as an input.

Note 1: If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 26.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 26.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 26.1.2.5 "Receive Overrun Error" for more information on overrun errors.

### 26.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- · RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

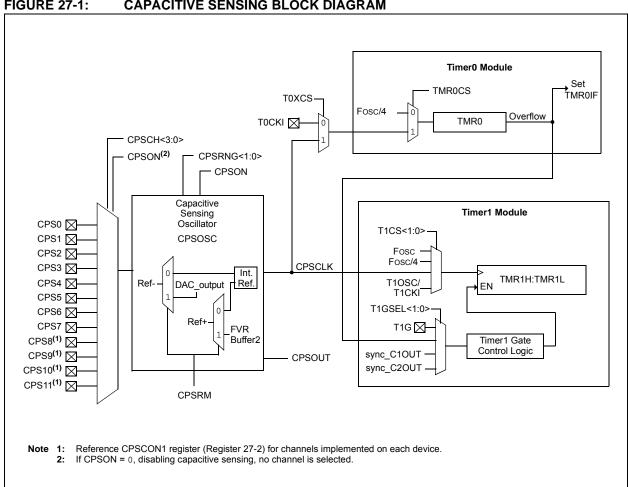

### 27.0 CAPACITIVE SENSING (CPS) **MODULE**

The Capacitive Sensing (CPS) module allows for an interaction with an end user without a mechanical interface. In a typical application, the CPS module is attached to a pad on a Printed Circuit Board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the capacitive sensing module. The CPS module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- · Multiple current ranges

- · Multiple voltage reference modes

- Multiple timer resources

- · Software control

- · Operation during Sleep

#### **FIGURE 27-1:** CAPACITIVE SENSING BLOCK DIAGRAM

| BCF              | Bit Clear f                                                            |  |  |

|------------------|------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BCF f,b                                                      |  |  |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$ |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                              |  |  |

| Status Affected: | None                                                                   |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                    |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                                            |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BRA label<br>[ label ] BRA \$+k                                                                                                                                                                                     |  |  |  |

| Operands:        | $-256 \le label - PC + 1 \le 255$<br>$-256 \le k \le 255$                                                                                                                                                                     |  |  |  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                |

| Operation:       | skip if $(f < b >) = 1$                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. |

| BRW              | Relative Branch with W                                                                                                                                                                        |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BRW                                                                                                                                                                                 |  |  |

| Operands:        | None                                                                                                                                                                                          |  |  |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                   |  |  |

| Status Affected: | None                                                                                                                                                                                          |  |  |

| Description:     | Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction is a 2-cycle instruction |  |  |

| BSF              | Bit Set f                            |

|------------------|--------------------------------------|

| Syntax:          | [ label ] BSF f,b                    |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is set.      |

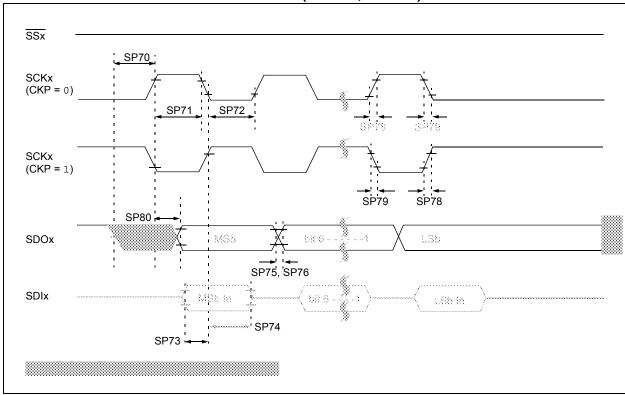

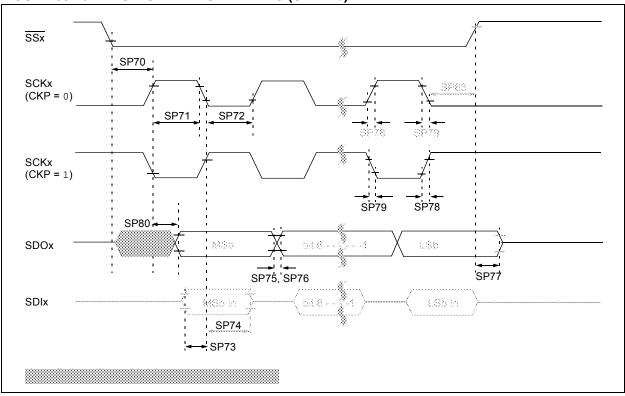

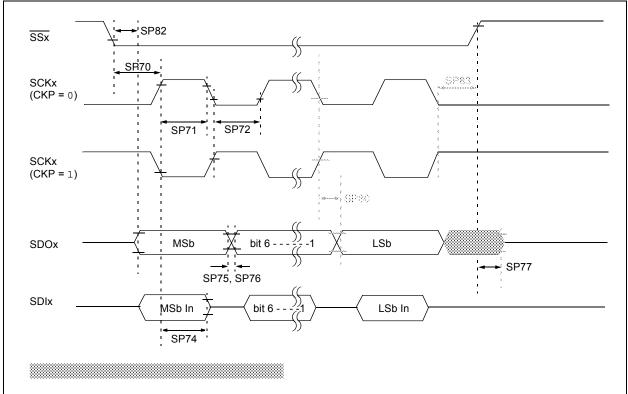

FIGURE 30-16: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

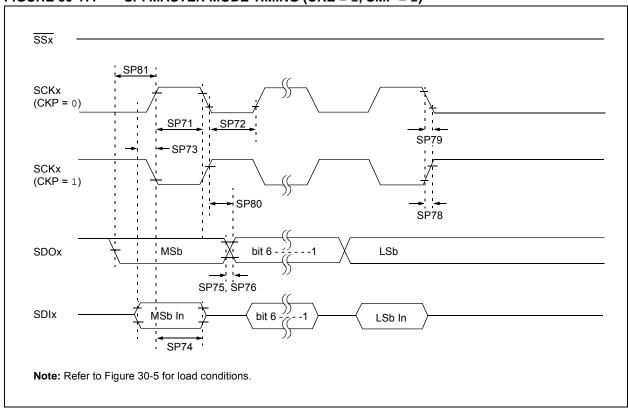

FIGURE 30-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

FIGURE 30-19: SPI SLAVE MODE TIMING (CKE = 1)

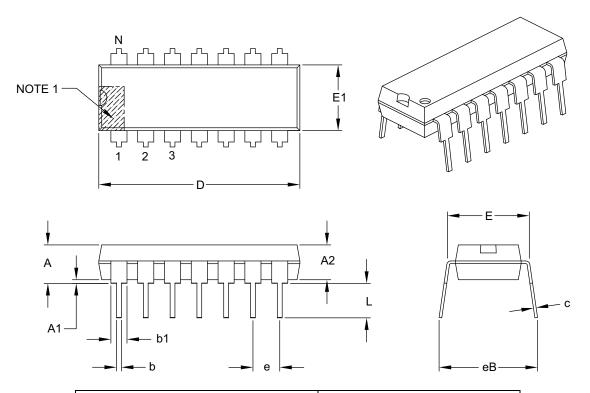

### 33.4 Package Details

The following sections give the technical details of the packages.

### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units       |          | INCHES |      |  |

|----------------------------|-------------|----------|--------|------|--|

| Dimen:                     | sion Limits | MIN      | NOM    | MAX  |  |

| Number of Pins             | N           |          | 14     |      |  |

| Pitch                      |             | .100 BSC |        |      |  |

| Top to Seating Plane       | Α           | _        | _      | .210 |  |

| Molded Package Thickness   | A2          | .115     | .130   | .195 |  |

| Base to Seating Plane      | A1          | .015     | _      | _    |  |

| Shoulder to Shoulder Width | Е           | .290     | .310   | .325 |  |

| Molded Package Width       | E1          | .240     | .250   | .280 |  |

| Overall Length             | D           | .735     | .750   | .775 |  |

| Tip to Seating Plane       | L           | .115     | .130   | .150 |  |

| Lead Thickness             | С           | .008     | .010   | .015 |  |

| Upper Lead Width           | b1          | .045     | .060   | .070 |  |

| Lower Lead Width           | b           | .014     | .018   | .022 |  |

| Overall Row Spacing §      | eB          | _        | _      | .430 |  |

#### Notes.

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B