Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1824-e-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

Г

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### **REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

| Note 1: | The C and DC bits operate as Borrow         |

|---------|---------------------------------------------|

|         | and Digit Borrow out bits, respectively, in |

|         | subtraction.                                |

| U-0              | U-0                                     | U-0               | R-1/q | R-1/q                          | R/W-0/u                            | R/W-0/u           | R/W-0/u          |  |  |  |

|------------------|-----------------------------------------|-------------------|-------|--------------------------------|------------------------------------|-------------------|------------------|--|--|--|

| _                | _                                       | _                 | TO    | PD                             | Z                                  | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |

| bit 7 bit 0      |                                         |                   |       |                                |                                    |                   |                  |  |  |  |

|                  |                                         |                   |       |                                |                                    |                   |                  |  |  |  |

| Legend:          |                                         |                   |       |                                |                                    |                   |                  |  |  |  |

| R = Readable b   | R = Readable bit W = Writable bit       |                   |       |                                | U = Unimplemented bit, read as '0' |                   |                  |  |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   |       | -n/n = Value a                 | at POR and BOI                     | R/Value at all c  | ther Resets      |  |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared  | q = Value depends on condition |                                    |                   |                  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                                                                 |

| bit 3   | PD: Power-down bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                                                               |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                               |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                                                             |

| bit 0   | C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                              |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

| Address             | Name                | Bit 7                            | Bit 6                                                                                                  | Bit 5            | Bit 4         | Bit 3        | Bit 2       | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on all<br>other |

|---------------------|---------------------|----------------------------------|--------------------------------------------------------------------------------------------------------|------------------|---------------|--------------|-------------|-------|-----------|----------------------|-----------------------|

| Bank 4              |                     |                                  |                                                                                                        |                  |               |              |             |       |           |                      | Resets                |

| 200h <sup>(1)</sup> | INDF0               | Addressing th<br>(not a physical |                                                                                                        | es contents of   | FSR0H/FSR0    | L to address | data memory | '     |           | XXXX XXXX            | XXXX XXXX             |

| 201h <sup>(1)</sup> | INDF1               | Addressing th                    | ddressing this location uses contents of FSR1H/FSR1L to address data memory<br>to a physical register) |                  |               |              |             |       |           | XXXX XXXX            | xxxx xxxx             |

| 202h <sup>(1)</sup> | PCL                 |                                  | ,<br>,                                                                                                 | st Significant E | 3vte          |              |             |       |           | 0000 0000            | 0000 0000             |

| 203h <sup>(1)</sup> | STATUS              | _                                | _                                                                                                      | _                | TO            | PD           | Z           | DC    | С         | 1 1000               | q quuu                |

| 204h <sup>(1)</sup> | FSR0L               | Indirect Data                    | Memory Addr                                                                                            | ess 0 Low Poir   | nter          |              |             |       | 1         | 0000 0000            | uuuu uuuu             |

| 205h <sup>(1)</sup> | FSR0H               | Indirect Data                    | Memory Addr                                                                                            | ess 0 High Poi   | nter          |              |             |       |           | 0000 0000            | 0000 0000             |

| 206h <sup>(1)</sup> | FSR1L               | Indirect Data                    | Memory Addr                                                                                            | ess 1 Low Poir   | nter          |              |             |       |           | 0000 0000            | uuuu uuuu             |

| 207h <sup>(1)</sup> | FSR1H               | Indirect Data                    | Memory Addr                                                                                            | ess 1 High Poi   | nter          |              |             |       |           | 0000 0000            | 0000 0000             |

| 208h <sup>(1)</sup> | BSR                 | _                                | _                                                                                                      | _                |               |              | BSR<4:0>    |       |           | 0 0000               | 0 0000                |

| 209h <sup>(1)</sup> | WREG                | Working Reg                      | ister                                                                                                  |                  |               |              |             |       |           | 0000 0000            | uuuu uuuu             |

| 20Ah <sup>(1)</sup> | PCLATH              | _                                | Write Buffer for the upper 7 bits of the Program Counter                                               |                  |               |              |             |       | -000 0000 | -000 0000            |                       |

| 20Bh <sup>(1)</sup> | INTCON              | GIE                              | PEIE                                                                                                   | TMR0IE           | INTE          | IOCIE        | TMR0IF      | INTF  | IOCIF     | 0000 000x            | 0000 000u             |

| 20Ch                | WPUA                | _                                | _                                                                                                      | WPUA5            | WPUA4         | WPUA3        | WPUA2       | WPUA1 | WPUA0     | 11 1111              | 11 1111               |

| 20Dh                | WPUB <sup>(2)</sup> | WPUB7                            | WPUB6                                                                                                  | WPUB5            | WPUB4         | _            | _           | _     | _         | 1111                 | 1111                  |

| 20Eh                | WPUC                | WPUC7 <sup>(2)</sup>             | WPUC6 <sup>(2)</sup>                                                                                   | WPUC5            | WPUC4         | WPUC3        | WPUC2       | WPUC1 | WPUC0     | 1111 1111            | 1111 1111             |

| 20Fh                | —                   | Unimplement                      | ed                                                                                                     |                  |               |              |             |       |           | _                    | —                     |

| 210h                | _                   | Unimplement                      | ed                                                                                                     |                  |               |              |             |       |           | _                    | _                     |

| 211h                | SSP1BUF             | Synchronous                      | Serial Port Re                                                                                         | eceive Buffer/T  | ransmit Regis | ster         |             |       |           | xxxx xxxx            | uuuu uuuu             |

| 212h                | SSP1ADD             |                                  |                                                                                                        |                  | ADD<7         | :0>          |             |       |           | 0000 0000            | 0000 0000             |

| 213h                | SSP1MSK             |                                  |                                                                                                        |                  | MSK<7         | :0>          |             |       |           | 1111 1111            | 1111 1111             |

| 214h                | SSP1STAT            | SMP                              | CKE                                                                                                    | D/A              | Р             | S            | R/W         | UA    | BF        | 0000 0000            | 0000 0000             |

| 215h                | SSP1CON1            | WCOL                             | SSPOV                                                                                                  | SSPEN            | CKP           |              | SSPM        | <3:0> |           | 0000 0000            | 0000 0000             |

| 216h                | SSP1CON2            | GCEN                             | ACKSTAT                                                                                                | ACKDT            | ACKEN         | RCEN         | PEN         | RSEN  | SEN       | 0000 0000            | 0000 0000             |

| 217h                | SSP1CON3            | ACKTIM                           | PCIE                                                                                                   | SCIE             | BOEN          | SDAHT        | SBCDE       | AHEN  | DHEN      | 0000 0000            | 0000 0000             |

| 218h                | _                   | Unimplement                      | Unimplemented                                                                                          |                  |               |              |             |       | _         | _                    |                       |

| 219h                | _                   | Unimplemented                    |                                                                                                        |                  |               |              |             | _     | _         |                      |                       |

| 21Ah                | _                   | Unimplemented                    |                                                                                                        |                  |               |              |             | _     | _         |                      |                       |

| 21Bh                | _                   | Unimplemented                    |                                                                                                        |                  |               |              |             | _     | _         |                      |                       |

| 21Ch                | _                   | Unimplement                      | ed                                                                                                     |                  |               |              |             |       |           | _                    | _                     |

|                     | _                   | Unimplement                      | ed                                                                                                     |                  |               |              |             |       |           | _                    | _                     |

| 21Dh                |                     |                                  | Unimplemented                                                                                          |                  |               |              |             |       |           |                      |                       |

| 21Dh<br>21Eh        | —                   | Unimplement                      | ed                                                                                                     |                  |               |              |             |       |           | —                    | —                     |

### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$Legend: \quad x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

3: PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

© 2010-2015 Microchip Technology Inc.

# 5.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

### 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability

of crystal oscillator sources

The oscillator module can be configured in one of eight clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC).

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz).

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Word 1. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high frequency clock sources, designated LFINTOSC, MFINTOSC, and HFINTOSC. (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables of **Section 30.0** "**Electrical Specifications**".

### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word 1. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 Oscillator and RC).

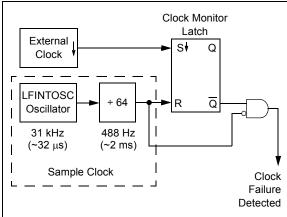

FIGURE 5-9: FSCM BLOCK DIAGRAM

### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

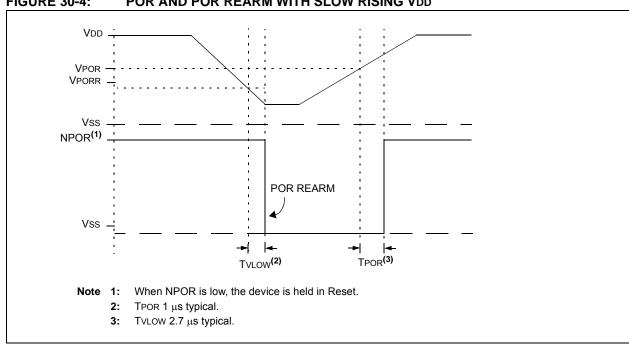

### 7.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 7.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 7.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 7-3 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 7-3 for more information.

| BOREN<br>Config bits | SBOREN | Device Mode | BOR Mode | Device<br>Operation upon<br>release of POR | Device<br>Operation upon<br>wake-up from<br>Sleep |  |

|----------------------|--------|-------------|----------|--------------------------------------------|---------------------------------------------------|--|

| BOR_ON (11)          | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>         |                                                   |  |

| BOR_NSLEEP (10)      | Х      | Awake       | Active   | - Waits for BOR ready                      |                                                   |  |

| BOR_NSLEEP (10)      | Х      | Sleep       | Disabled |                                            |                                                   |  |

| BOR_SBOREN (01)      | 1      | х           | Active   | Begins immediately                         |                                                   |  |

| BOR_SBOREN (01)      | 0      | х           | Disabled | Begins immediately                         |                                                   |  |

| BOR_OFF (00)         | Х      | х           | Disabled | Begins immediately                         |                                                   |  |

### TABLE 7-1: BOR OPERATING MODES

**Note 1:** In these specific cases, "Release of POR" and the "Wake-up from Sleep", there is no delay in start-up. The BOR Ready flag (BORRDY = 1) will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 7.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 7.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 7.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

| EXA      | MPLE 11-4:                                           | ERASING ON                                                                                    | E ROW OF PROGRAM MEMORY                                                                                                                                                                                                                                                                                                                         |

|----------|------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; Th     | is row erase                                         | routine assumes                                                                               | the following:                                                                                                                                                                                                                                                                                                                                  |

| ; 1.     | A valid add                                          | ress within the                                                                               | erase block is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                            |

| ; 2.     | ADDRH and AI                                         | DDRL are located                                                                              | l in shared data memory 0x70 - 0x7F                                                                                                                                                                                                                                                                                                             |

|          | BCF<br>BANKSEL<br>MOVF<br>MOVF<br>MOVF<br>BSF<br>BCF | INTCON,GIE<br>EEADRL<br>ADDRL,W<br>EEADRL<br>ADDRH,W<br>EEADRH<br>EECON1,EEPGD<br>EECON1,CFGS | <pre>; Disable ints so required sequences will execute properly ; Load lower 8 bits of erase address boundary ; Load upper 6 bits of erase address boundary ; Point to program memory ; Not configuration space</pre>                                                                                                                           |

|          | BSF                                                  | EECON1, FREE                                                                                  | ; Specify an erase operation                                                                                                                                                                                                                                                                                                                    |

|          | BSF                                                  | EECON1,WREN                                                                                   | ; Enable writes                                                                                                                                                                                                                                                                                                                                 |

| Required | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP         | 55h<br>EECON2<br>OAAh<br>EECON2<br>EECON1,WR                                                  | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor<br/>; halts to begin erase sequence<br/>; Processor will stop here and wait for erase complete.<br/>; after erase processor continues with 3rd instruction</pre> |

|          | BCF<br>BSF                                           | EECONI, WREN<br>INTCON, GIE                                                                   | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                         |

|          |                                                      |                                                                                               | -                                                                                                                                                                                                                                                                                                                                               |

| Name    | Bit 7 | Bit 6  | Bit 5 | Bit 4     | Bit 3       | Bit 2 | Bit 1      | Bit 0  | Register<br>on page |

|---------|-------|--------|-------|-----------|-------------|-------|------------|--------|---------------------|

| FVRCON  | FVREN | FVRRDY | TSEN  | TSRNG     | CDAFVR<1:0> |       | ADFVR<1:0> |        | 141                 |

| DACCON0 | DACEN | DACLPS | DACOE | _         | DACPSS<1:0> |       | _          | DACNSS | 159                 |

| DACCON1 | —     | —      | _     | DACR<4:0> |             |       |            |        | 159                 |

### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the DAC module.

### 22.1 Timer2/4/6 Operation

The clock input to the Timer2/4/6 modules is the system instruction clock (Fosc/4).

TMRx increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, TxCKPS<1:0> of the TxCON register. The value of TMRx is compared to that of the Period register, PRx, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMRx to 00h on the next cycle and drives the output counter/postscaler (see Section 22.2 "Timer2/4/6 Interrupt").

The TMRx and PRx registers are both directly readable and writable. The TMRx register is cleared on any device Reset, whereas the PRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMRx register

- · a write to the TxCON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

### 22.2 Timer2/4/6 Interrupt

Timer2/4/6 can also generate an optional device interrupt. The Timer2/4/6 output signal (TMRx-to-PRx match) provides the input for the 4-bit counter/postscaler. This counter generates the TMRx match interrupt flag which is latched in TMRxIF of the PIRx register. The interrupt is enabled by setting the TMRx Match Interrupt Enable bit, TMRxIE of the PIEx register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, TxOUTPS<3:0>, of the TxCON register.

### 22.3 Timer2/4/6 Output

The unscaled output of TMRx is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode. Additional information is provided in **Section 25.1 "Master SSP (MSSP1) Module Overview"**.

### 22.4 Timer2/4/6 Operation During Sleep

The Timer2/4/6 timers cannot be operated while the processor is in Sleep mode. The contents of the TMRx and PRx registers will remain unchanged while the processor is in Sleep mode.

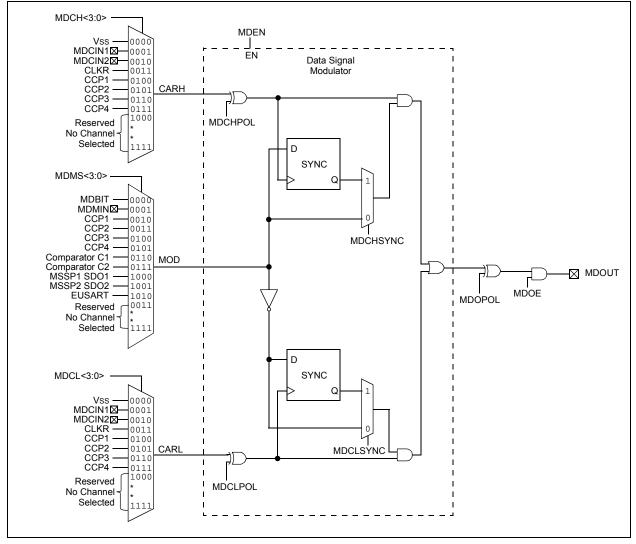

# 23.0 DATA SIGNAL MODULATOR

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal. Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- · Carrier Source Polarity Select

- Carrier Source Pin Disable

- Programmable Modulator Data

- · Modulator Source Pin Disable

- Modulated Output Polarity Select

- Slew Rate Control

Figure 23-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

## 24.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

This family of devices contains two Enhanced Capture/ Compare/PWM modules (ECCP1 and ECCP2) and two standard Capture/Compare/PWM modules (CCP3 and CCP4).

The capture and compare functions are identical for all four CCP modules (ECCP1, ECCP2, CCP3, and CCP4). The only differences between CCP modules are in the Pulse-Width Modulation (PWM) function. The standard PWM function is identical in modules, CCP3 and CCP4. In CCP modules ECCP1 and ECCP2, the Enhanced PWM function has slight variations from one another. Full-Bridge ECCP modules have four available I/O pins while Half-Bridge ECCP modules only have two available I/O pins. See Table 24-1 for more information.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to ECCP1, ECCP2, CCP3 and CCP4. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

| TABLE 24-1: | PWM RESOURCES |

|-------------|---------------|

|-------------|---------------|

| Device Name     | ECCP1                       | ECCP2                       | CCP3         | CCP4         |

|-----------------|-----------------------------|-----------------------------|--------------|--------------|

| PIC16(L)F1824/8 | Enhanced PWM<br>Full-Bridge | Enhanced PWM<br>Half-Bridge | Standard PWM | Standard PWM |

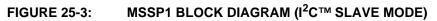

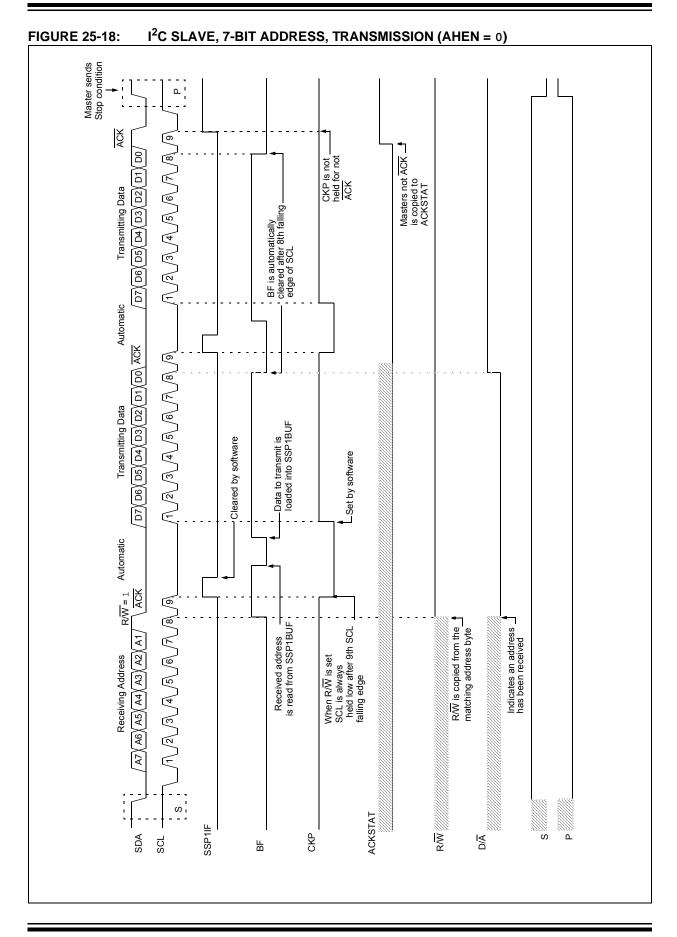

### 25.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP1 module configured as an  $I^2C$  Slave in 10-bit Addressing mode.

Figure 25-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSP1STAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSP1BUF clearing the BF flag.

- 7. Slave loads low address into SSP1ADD, releasing SCL.

- 8. Master sends matching low address byte to the Slave; UA bit is set.

**Note:** Updates to the SSP1ADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSP1IF is set.

- **Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSP1ADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSP1BUF clearing BF.

- 12. Slave loads high address into SSP1ADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSP1CON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSP1BUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 25.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSP1ADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 25-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 25-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

# 28.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>™</sup> refer to the "*PIC16F/LF182X/PIC12F/LF1822 Memory Programming Specification*" (DS41390).

### 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

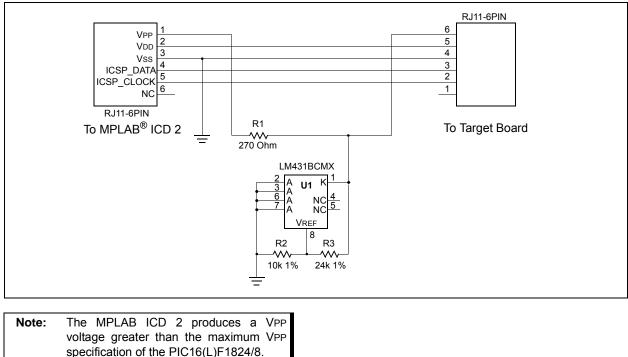

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

© 2010-2015 Microchip Technology Inc.

### FIGURE 30-4: POR AND POR REARM WITH SLOW RISING VDD

| Param<br>No. | Symbol                | Characteristic                                                           | Min.      | Тур†        | Max. | Units | Conditions |  |

|--------------|-----------------------|--------------------------------------------------------------------------|-----------|-------------|------|-------|------------|--|

| SP70*        | TssL2scH,<br>TssL2scL | $\overline{SSx}\downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ input | 2.25 Tcy  |             | —    | ns    |            |  |

| SP71*        | TscH                  | SCKx input high time (Slave mo                                           | de)       | Tcy + 20    |      | _     | ns         |  |

| SP72*        | TscL                  | SCKx input low time (Slave mod                                           | e)        | Tcy + 20    | _    | _     | ns         |  |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDIx data input to                                         | SCKx edge | 100         |      | —     | ns         |  |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDIx data input to SCKx edge                                |           | 100         |      | —     | ns         |  |

| SP75*        | TDOR                  | SDO data output rise time                                                | 3.0-5.5V  | _           | 10   | 25    | ns         |  |

|              |                       | 1.8-5.5V                                                                 | —         | 25          | 50   | ns    |            |  |

| SP76*        | TDOF                  | SDOx data output fall time                                               |           | —           | 10   | 25    | ns         |  |

| SP77*        | TssH2doZ              | SSx↑ to SDOx output high-impe                                            | dance     | 10          | _    | 50    | ns         |  |

| SP78*        | TscR                  | SCKx output rise time                                                    | 3.0-5.5V  | _           | 10   | 25    | ns         |  |

|              |                       | (Master mode)                                                            | 1.8-5.5V  | _           | 25   | 50    | ns         |  |

| SP79*        | TscF                  | SCKx output fall time (Master mo                                         | ode)      | _           | 10   | 25    | ns         |  |

| SP80*        | TscH2doV,             | SDOx data output valid after                                             | 3.0-5.5V  | —           | _    | 50    | ns         |  |

|              | TscL2doV              | SCKx edge                                                                | 1.8-5.5V  | —           | —    | 145   | ns         |  |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDOx data output setup to SCK                                            | Тсу       |             | -    | ns    |            |  |

| SP82*        | TssL2doV              | SDOx data output valid after SS                                          | ↓ edge    | _           | —    | 50    | ns         |  |

| SP83*        | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx edge                                                    |           | 1.5Tcy + 40 | _    | —     | ns         |  |

### TABLE 30-14: SPI MODE REQUIREMENTS

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

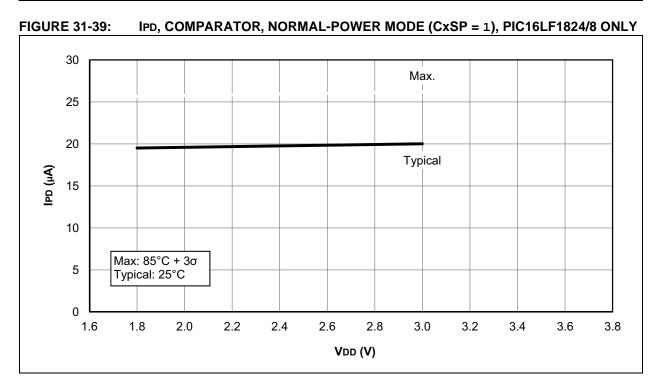

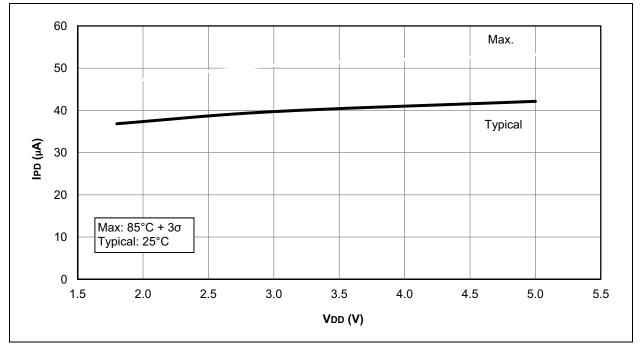

FIGURE 31-40: IPD, COMPARATOR, NORMAL-POWER MODE (CxSP = 1), PIC16F1824/8 ONLY

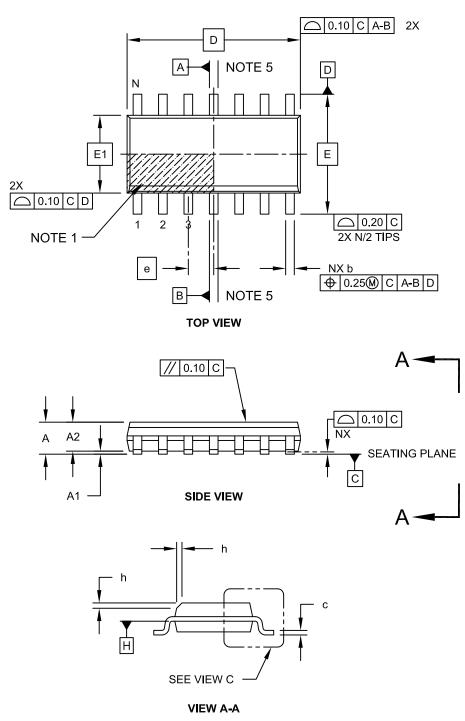

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2