#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1824t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-6: PIC16(L)F1824/8 MEMORY MAP, BANKS 16-23

|      | BANK 16       | •    | BANK 17       |      | BANK 18       |      | BANK 19       |      | BANK 20       |      | BANK 21       |      | BANK 22       |      | BANK 23       |

|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|

| 800h | INDF0         | 880h | INDF0         | 900h | INDF0         | 980h | INDF0         | A00h | INDF0         | A80h | INDF0         | B00h | INDF0         | B80h | INDF0         |

| 801h | INDF1         | 881h | INDF1         | 901h | INDF1         | 981h | INDF1         | A01h | INDF1         | A81h | INDF1         | B01h | INDF1         | B81h | INDF1         |

| 802h | PCL           | 882h | PCL           | 902h | PCL           | 982h | PCL           | A02h | PCL           | A82h | PCL           | B02h | PCL           | B82h | PCL           |

| 803h | STATUS        | 883h | STATUS        | 903h | STATUS        | 983h | STATUS        | A03h | STATUS        | A83h | STATUS        | B03h | STATUS        | B83h | STATUS        |

| 804h | FSR0L         | 884h | FSR0L         | 904h | FSR0L         | 984h | FSR0L         | A04h | FSR0L         | A84h | FSR0L         | B04h | FSR0L         | B84h | FSR0L         |

| 805h | FSR0H         | 885h | FSR0H         | 905h | FSR0H         | 985h | FSR0H         | A05h | FSR0H         | A85h | FSR0H         | B05h | FSR0H         | B85h | FSR0H         |

| 806h | FSR1L         | 886h | FSR1L         | 906h | FSR1L         | 986h | FSR1L         | A06h | FSR1L         | A86h | FSR1L         | B06h | FSR1L         | B86h | FSR1L         |

| 807h | FSR1H         | 887h | FSR1H         | 907h | FSR1H         | 987h | FSR1H         | A07h | FSR1H         | A87h | FSR1H         | B07h | FSR1H         | B87h | FSR1H         |

| 808h | BSR           | 888h | BSR           | 908h | BSR           | 988h | BSR           | A08h | BSR           | A88h | BSR           | B08h | BSR           | B88h | BSR           |

| 809h | WREG          | 889h | WREG          | 909h | WREG          | 989h | WREG          | A09h | WREG          | A89h | WREG          | B09h | WREG          | B89h | WREG          |

| 80Ah | PCLATH        | 88Ah | PCLATH        | 90Ah | PCLATH        | 98Ah | PCLATH        | A0Ah | PCLATH        | A8Ah | PCLATH        | B0Ah | PCLATH        | B8Ah | PCLATH        |

| 80Bh | INTCON        | 88Bh | INTCON        | 90Bh | INTCON        | 98Bh | INTCON        | A0Bh | INTCON        | A8Bh | INTCON        | B0Bh | INTCON        | B8Bh | INTCON        |

| 80Ch | _             | 88Ch |               | 90Ch | —             | 98Ch | _             | A0Ch | _             | A8Ch | _             | B0Ch | -             | B8Ch | _             |

| 80Dh | —             | 88Dh | -             | 90Dh | —             | 98Dh | —             | A0Dh | —             | A8Dh | —             | B0Dh | -             | B8Dh | _             |

| 80Eh | —             | 88Eh | —             | 90Eh | —             | 98Eh | _             | A0Eh | —             | A8Eh | —             | B0Eh | —             | B8Eh |               |

| 80Fh | —             | 88Fh | -             | 90Fh | —             | 98Fh | —             | A0Fh | —             | A8Fh | —             | B0Fh | -             | B8Fh | _             |

| 810h | —             | 890h | —             | 910h | _             | 990h | _             | A10h | —             | A90h | —             | B10h | —             | B90h | —             |

| 811h | —             | 891h | —             | 911h | _             | 991h | _             | A11h | —             | A91h | —             | B11h | —             | B91h | —             |

| 812h | _             | 892h | _             | 912h | _             | 992h |               | A12h | —             | A92h | —             | B12h | —             | B92h |               |

| 813h | —             | 893h | _             | 913h |               | 993h | -             | A13h | —             | A93h | —             | B13h | _             | B93h |               |

| 814h | _             | 894h | _             | 914h |               | 994h |               | A14h | —             | A94h | —             | B14h | _             | B94h | —             |

| 815h | —             | 895h | —             | 915h | _             | 995h | _             | A15h | —             | A95h | —             | B15h | —             | B95h | _             |

| 816h | —             | 896h | —             | 916h | _             | 996h | —             | A16h | —             | A96h | —             | B16h | —             | B96h | —             |

| 817h | —             | 897h | _             | 917h |               | 997h |               | A17h | —             | A97h | _             | B17h | _             | B97h | —             |

| 818h | —             | 898h | _             | 918h |               | 998h |               | A18h | —             | A98h | _             | B18h | _             | B98h | —             |

| 819h | —             | 899h | _             | 919h |               | 999h | -             | A19h | —             | A99h | —             | B19h | _             | B99h |               |

| 81Ah | _             | 89Ah | _             | 91Ah |               | 99Ah | _             | A1Ah | —             | A9Ah | —             | B1Ah | _             | B9Ah | _             |

| 81Bh | _             | 89Bh | _             | 91Bh |               | 99Bh |               | A1Bh | —             | A9Bh | —             | B1Bh | _             | B9Bh | —             |

| 81Ch | —             | 89Ch | _             | 91Ch |               | 99Ch |               | A1Ch | —             | A9Ch | _             | B1Ch | _             | B9Ch | —             |

| 81Dh | _             | 89Dh | _             | 91Dh |               | 99Dh | _             | A1Dh | —             | A9Dh | _             | B1Dh | _             | B9Dh | —             |

| 81Eh | _             | 89Eh | _             | 91Eh |               | 99Eh | _             | A1Eh | —             | A9Eh | _             | B1Eh | _             | B9Eh | —             |

| 81Fh | —             | 89Fh | —             | 91Fh | _             | 99Fh | —             | A1Fh | —             | A9Fh | —             | B1Fh | —             | B9Fh | —             |

| 820h |               | 8A0h |               | 920h |               | 9A0h |               | A20h |               | AA0h |               | B20h |               | BA0h |               |

|      |               |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

|      | Unimplemented |

|      | Read as '0'   |

|      |               |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

| 86Fh |               | 8EFh |               | 96Fh |               | 9EFh |               | A6Fh |               | AEFh |               | B6Fh |               | BEFh |               |

| 870h |               | 8F0h |               | 970h |               | 9F0h |               | A70h |               | AF0h |               | B70h |               | BF0h |               |

|      | Accesses      |

|      | 70h – 7Fh     |

| 87Fh |               | 8FFh |               | 97Fh |               | 9FFh |               | A7Fh |               | AFFh |               | B7Fh |               | BFFh |               |

**Legend:** = Unimplemented data memory locations, read as '0'.

#### 3.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-4 through 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit = 0 (Configuration Word 2). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.4.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

#### FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

| TOSH:TOSL 0x0F | STKPTR = 0x1F Stack Reset Disabled<br>(STVREN = 0)                                    |

|----------------|---------------------------------------------------------------------------------------|

| √ 0x0E         |                                                                                       |

| 0x0D           |                                                                                       |

| 0x0C           |                                                                                       |

| 0x0B           |                                                                                       |

| 0x0A           | Initial Stock Configuration                                                           |

| 0x09           | Initial Stack Configuration:                                                          |

| 0x08           | After Reset, the stack is empty. The empty stack is initialized so the Stack          |

| 0x07           | Pointer is pointing at 0x1F. If the Stack<br>Overflow/Underflow Reset is enabled, the |

| 0x06           | TOSH/TOSL registers will return '0'. If<br>the Stack Overflow/Underflow Reset is      |

| 0x05           | disabled, the TOSH/TOSL registers will<br>return the contents of stack address 0x0F.  |

| 0x04           |                                                                                       |

| 0x03           |                                                                                       |

| 0x02           |                                                                                       |

| 0x01           |                                                                                       |

| 0x00           |                                                                                       |

| TOSH:TOSL 0x1F | 0x0000 STKPTR = 0x1F Stack Reset Enabled<br>(STVREN = 1)                              |

|                | N                                                                                     |

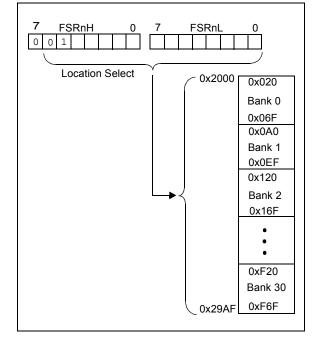

# 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

#### 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-11: PROGRAM FLASH MEMORY MAP

# 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Word 1

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Word 1.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch, which may     |

|-------|-------------------------------------------|

|       | occur from Two-Speed Start-up or          |

|       | Fail-Safe Clock Monitor, does not update  |

|       | the SCS bits of the OSCCON register. The  |

|       | user can monitor the OSTS bit of the      |

|       | OSCSTAT register to determine the current |

|       | system clock source.                      |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 Oscillator.

# 5.3.3 TIMER1 OSCILLATOR

The Timer1 Oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 21.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 Oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

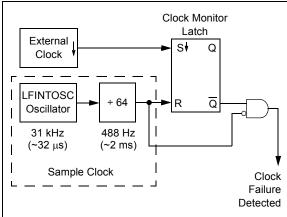

# 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word 1. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 Oscillator and RC).

FIGURE 5-9: FSCM BLOCK DIAGRAM

#### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

# 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again become set by hardware.

#### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

| R-1/q                                                                                                                                                                  | R-0/q                                                                                                                                                                         | R-q/q                              | R-0/q          | R-0/q          | R-q/q                    | R-0/0            | R-0/q        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|--------------------------|------------------|--------------|

| T10SCR                                                                                                                                                                 | PLLR                                                                                                                                                                          | OSTS                               | HFIOFR         | HFIOFL         | MFIOFR                   | LFIOFR           | HFIOFS       |

| bit 7                                                                                                                                                                  |                                                                                                                                                                               |                                    |                |                |                          |                  | bit 0        |

|                                                                                                                                                                        |                                                                                                                                                                               |                                    |                |                |                          |                  |              |

| Legend:                                                                                                                                                                |                                                                                                                                                                               |                                    |                |                |                          |                  |              |

| R = Readable                                                                                                                                                           | bit                                                                                                                                                                           | W = Writable                       | bit            | U = Unimpler   | nented bit, reac         | 1 as '0'         |              |

| u = Bit is uncha                                                                                                                                                       | anged                                                                                                                                                                         | x = Bit is unkr                    | nown           | -n/n = Value a | at POR and BO            | R/Value at all o | other Resets |

| '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                               | '0' = Bit is cle                   | ared           | q = Condition  | al                       |                  |              |

| bit 7 <b>T1OSCR:</b> Timer1 Oscillator Ready bit<br><u>If T1OSCEN = 1</u> :<br>1 = Timer1 oscillator is ready<br>0 = Timer1 oscillator is not ready<br>If T1OSCEN = 0: |                                                                                                                                                                               |                                    |                |                |                          |                  |              |

| bit 6                                                                                                                                                                  | 1 = Timer1 of<br><b>PLLR</b> 4xPLL<br>1 = 4xPLL is<br>0 = 4xPLL is                                                                                                            | s ready                            | always ready   |                |                          |                  |              |

| bit 5                                                                                                                                                                  | <b>OSTS:</b> Oscilla<br>1 = Running                                                                                                                                           | ator Start-up Ti<br>from the clock | defined by the |                | oits of the Confi<br>00) | guration Word    | 1            |

| bit 4                                                                                                                                                                  | 0 = Running from an internal oscillator (FOSC<2:0> = 100)<br>bit 4 HFIOFR: High-Frequency Internal Oscillator Ready bit<br>1 = HFINTOSC is ready<br>0 = HFINTOSC is not ready |                                    |                |                |                          |                  |              |

| bit 3                                                                                                                                                                  |                                                                                                                                                                               |                                    |                |                |                          |                  |              |

| bit 2                                                                                                                                                                  | t 2 MFIOFR: Medium-Frequency Internal Oscillator Ready bit<br>1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready                                                              |                                    |                |                |                          |                  |              |

| bit 1                                                                                                                                                                  | LFIOFR: Low-Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready                                                                     |                                    |                |                |                          |                  |              |

| bit 0                                                                                                                                                                  |                                                                                                                                                                               |                                    |                |                |                          |                  |              |

# REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

#### 8.5.5 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 8-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-------|-------|---------|---------|---------|---------|

| TMR1GIF | ADIF    | RCIF  | TXIF  | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  |

| bit 7   |         |       |       |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | TMR1GIF: Timer1 Gate Interrupt Flag bit                   |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                    |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                    |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                   |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 3 | SSP1IF: Synchronous Serial Port (MSSP) Interrupt Flag bit |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                           |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                  |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

|       |                                                           |

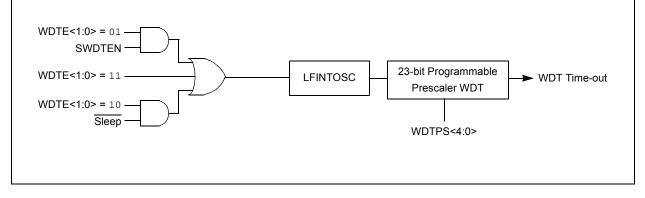

# **10.0 WATCHDOG TIMER**

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1ms to 256 seconds (typical)

- Multiple Reset conditions

- Operation during Sleep

#### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

# PIC16(L)F1824/8

| EXA      | /IPLE 11-4:                                           | ERASING ON                                                                                    | E ROW OF PROGRAM MEMORY                                                                                                                                                                                                                                                                                                                         |

|----------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; Thi    | s row erase                                           | routine assumes                                                                               | the following:                                                                                                                                                                                                                                                                                                                                  |

| ; 1.     | A valid add                                           | ress within the                                                                               | erase block is loaded in ADDRH:ADDRL                                                                                                                                                                                                                                                                                                            |

| ; 2.     | ADDRH and AI                                          | DDRL are located                                                                              | l in shared data memory 0x70 - 0x7F                                                                                                                                                                                                                                                                                                             |

|          | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>BSF<br>BCF | INTCON,GIE<br>EEADRL<br>ADDRL,W<br>EEADRL<br>ADDRH,W<br>EEADRH<br>EECON1,EEPGD<br>EECON1,CFGS | <pre>; Disable ints so required sequences will execute properly ; Load lower 8 bits of erase address boundary ; Load upper 6 bits of erase address boundary ; Point to program memory ; Not configuration space</pre>                                                                                                                           |

|          | BSF                                                   | EECON1, FREE                                                                                  | ; Specify an erase operation                                                                                                                                                                                                                                                                                                                    |

|          | BSF                                                   | EECON1,WREN                                                                                   | ; Enable writes                                                                                                                                                                                                                                                                                                                                 |

| Required | NOP                                                   | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1,WR                                                  | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; Any instructions here are ignored as processor<br/>; halts to begin erase sequence<br/>; Processor will stop here and wait for erase complete.<br/>; after erase processor continues with 3rd instruction</pre> |

|          | BCF<br>BSF                                            | EECONI,WREN<br>INTCON,GIE                                                                     | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                         |

|          |                                                       |                                                                                               |                                                                                                                                                                                                                                                                                                                                                 |

# 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |

|-------|------------------------------------------|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |

|       | Refer to Section 16.2.6 "A/D Conver-     |  |  |  |

|       | sion Procedure".                         |  |  |  |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | CCPx/ECCPx |

|-----------------|------------|

| PIC16(L)F1824/8 | CCP4       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 24.0** "Capture/Compare/PWM **Modules**" for more information.

### 26.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCON register. In Synchronous mode, the BRGH bit is ignored.

Table 26-3 contains the formulas for determining the baud rate. Example 26-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 26-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

# EXAMPLE 26-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPBRGH:SPBRGL:

C

| $X = \frac{Fosc}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $= \frac{\frac{16000000}{9600}}{64} - 1$                                |

| $= [25.042] = 25$ Calculated Baud Rate $= \frac{16000000}{64(25+1)}$    |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                | _                             | -                           | _                | _          | _                           | _                 | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | —                | —                             | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404             | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615             | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —                |            | —                           |

| 10417  | 10417            | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556            | -3.55                         | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | —                | _                             | —                           | —                | _          | —                           | 115.2k            | 0.00       | 1                           | —                | _          | —                           |

# TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00                          | 6666                        | 300.0             | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0              | 0.00       | 2303                        |

| 1200   | 1200              | -0.02                         | 3332                        | 1200              | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200               | 0.00       | 575                         |

| 2400   | 2401              | -0.04                         | 832                         | 2399              | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400               | 0.00       | 287                         |

| 9600   | 9615              | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417  | 10417             | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 57.14k            | -0.79                         | 34                          | 56.818            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 117.6k            | 2.12                          | 16                          | 113.636           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |

| 1200   | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —                | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | _                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | _                             | _          | _                           | _                | _          | _                           | 115.2k            | 0.00       | 1                           | —                | _          | _                           |

# 26.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 26.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 26-7), and asynchronously if the device is in Sleep mode (Figure 26-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 26.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### 26.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | the corresponding ANSEL bit must be        |  |  |  |  |  |

|       | cleared for the receiver to function.      |  |  |  |  |  |

#### 26.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

#### 26.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 26.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

# 26.4.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                     | U-0  | R/W-0/0        | R/W-0/0          | R-0/0            | R/W-0/0     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|----------------|------------------|------------------|-------------|

| CPSON            | CPSRM                                                                                                                                                                                                                                                                                                                                                                                      | _                                                       | _    | CPSRN          | NG<1:0>          | CPSOUT           | T0XCS       |

| bit 7            | •                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |      |                |                  |                  | bit (       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |      |                |                  |                  |             |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |      |                |                  |                  |             |

| R = Readable     |                                                                                                                                                                                                                                                                                                                                                                                            | W = Writable                                            |      | •              | nented bit, read |                  |             |

| u = Bit is unch  | 0                                                                                                                                                                                                                                                                                                                                                                                          | x = Bit is unki                                         |      | -n/n = Value a | it POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                            | '0' = Bit is cle                                        | ared |                |                  |                  |             |

| bit 7            | 1 = CPS mo                                                                                                                                                                                                                                                                                                                                                                                 | bacitive Sensing<br>dule is enabled<br>dule is disabled |      | able bit       |                  |                  |             |

| bit 6            | <b>CPSRM:</b> Capacitive Sensing Reference Mode bit<br>1 = Capacitive Sensing module is in Variable Voltage Reference mode.<br>0 = Capacitive Sensing module is in Fixed Voltage Reference mode                                                                                                                                                                                            |                                                         |      |                |                  |                  |             |

| bit 5-4          | Unimplemer                                                                                                                                                                                                                                                                                                                                                                                 | nted: Read as '                                         | 0'   |                |                  |                  |             |

| bit 3-2          | <b>CPSRNG&lt;1:0&gt;:</b> Capacitive Sensing Current Range bits<br><u>If CPSRM = 0 (Fixed Voltage Reference mode):</u><br>00 = Oscillator is off<br>01 = Oscillator is in low range<br>10 = Oscillator is in medium range<br>11 = Oscillator is in high range                                                                                                                              |                                                         |      |                |                  |                  |             |

|                  | <u>If CPSRM = 1 (Variable Voltage Reference mode):</u><br>00 = Oscillator is on. Noise Detection mode. No Charge/Discharge current is supplied.<br>01 = Oscillator is in low range<br>10 = Oscillator is in medium range<br>11 = Oscillator is in high range                                                                                                                               |                                                         |      |                |                  |                  |             |

| bit 1            | <b>CPSOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out of the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                                                         |                                                         |      |                |                  |                  |             |

| bit 0            | <b>TOXCS:</b> Timer0 External Clock Source Select bit<br><u>If TMR0CS = 1:</u><br>The T0XCS bit controls which clock external to the core/Timer0 module supplies Timer0:<br>1 = Timer0 clock source is the capacitive sensing oscillator<br>0 = Timer0 clock source is the T0CKI pin<br><u>If TMR0CS = 0:</u><br>Timer0 clock source is controlled by the core/Timer0 module and is Fosc/4 |                                                         |      |                |                  |                  | ):          |

# REGISTER 27-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

# 28.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>™</sup> refer to the "*PIC16F/LF182X/PIC12F/LF1822 Memory Programming Specification*" (DS41390).

# 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

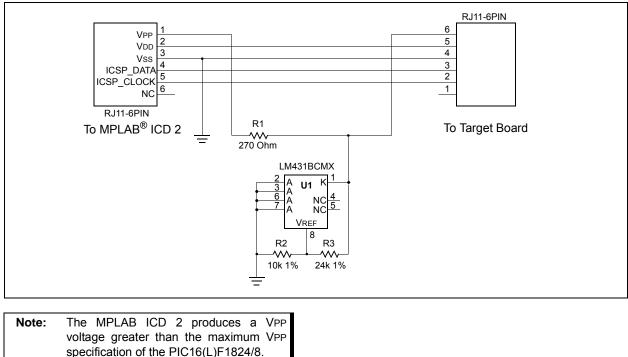

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

© 2010-2015 Microchip Technology Inc.

# PIC16(L)F1824/1828

# FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-c        | oriented file                                | regi<br>8 | ister o<br>7 | ope<br>6 | erat       | ions    |           | 0    |

|---------------|----------------------------------------------|-----------|--------------|----------|------------|---------|-----------|------|

|               | PCODE                                        | -         | d            | Ē        |            | f (FII  | _E #)     |      |

| Ċ             | = 0 for des<br>= 1 for des<br>= 7-bit file r | tinati    | on f         |          | ss         |         |           |      |

| Bit-ori<br>13 | ented file r                                 | -         | ter op<br>9  | era<br>7 |            |         |           | 0    |

|               | OPCODE                                       |           | b (Bl        | T #      | <b>#</b> ) | f (F    | ILE #)    |      |

|               | e = 3-bit bit a<br>= 7-bit file r            |           |              | dre      | SS         |         |           |      |

| Litera        | and contro                                   | ol op     | eratio       | ons      | 5          |         |           |      |

| Gener         | al                                           |           |              |          |            |         |           |      |

| 13            |                                              |           | 8            | 7        |            |         |           | 0    |

|               | OPCODE                                       |           |              |          |            | k (lit  | eral)     |      |

| k             | = 8-bit imm                                  | edia      | te val       | ue       |            |         |           |      |

| CALL a        | and Goto in                                  | struc     | tions        | onl      | у          |         |           |      |

| 13            | 11                                           | 10        |              |          |            |         |           | 0    |

| (             | PCODE                                        |           |              | k        | c (lit     | eral)   |           |      |

|               | = 11-bit imr                                 |           |              | 7        | 6          |         |           | 0    |

| 15            | OPCODE                                       |           |              | <u>/</u> |            | k (lite | eral)     | 0    |

|               | = 7-bit imm                                  |           | te val       | ue       | <u> </u>   |         |           |      |

| MOVLE         | instruction                                  | only      |              |          | 5          | 4       |           | 0    |

|               | OPCODE                                       |           |              |          |            | k       | (literal) | )    |

|               | = 5-bit imm                                  |           | te valı      | ue       |            |         |           |      |

| BRA in<br>13  | struction on                                 | ly        | 98           | ,        |            |         |           | 0    |

| 15            | OPCODE                                       |           | 3 0          | ,        |            | k (lit  | eral)     | 0    |

| Lk            | x = 9-bit imm                                | nedia     | te val       | ue       |            |         | ,         |      |

| FSR C         | Offset instruc                               | ctions    | 6            |          |            |         |           |      |

| 13            | 000005                                       |           | 7            | 6        | 5          |         | /!·/ I)   | 0    |

|               | OPCODE                                       |           |              | n        |            | K       | (literal) |      |

|               | n = appropri<br>k = 6-bit imn                |           |              | ue       |            |         |           |      |