Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

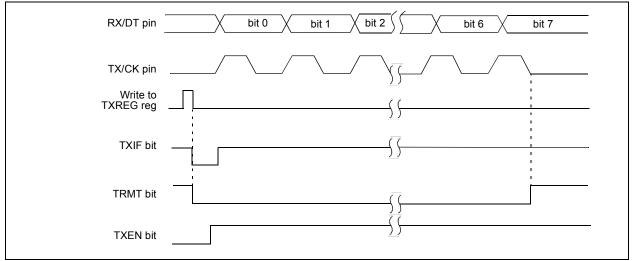

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1828t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Data EEPROM memory<sup>(1)</sup>

| Note 1: | The                      | data                | FF          | PROM      | men   | norv | and    | the  |

|---------|--------------------------|---------------------|-------------|-----------|-------|------|--------|------|

|         |                          |                     |             |           |       | -    |        |      |

|         | met                      | nod to              | aco         | cess Flas | sh me | emor | y thro | ugh  |

|         | the                      | EECC                | N           | register  | s is  | des  | cribed | d in |

|         | Sec                      | tion 1 <sup>-</sup> | <b>I.</b> 0 | "Data El  | EPRO  | DM a | nd Fl  | ash  |

|         | Program Memory Control". |                     |             |           |       |      |        |      |

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

## 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1824/8 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device                         | Program Memory Space (Words) | Last Program Memory Address |

|--------------------------------|------------------------------|-----------------------------|

| PIC16(L)F1824<br>PIC16(L)F1828 | 4,096                        | 0FFFh                       |

# PIC16(L)F1824/8

| Address             | Name                | Bit 7                                                                                                  | Bit 6                | Bit 5            | Bit 4           | Bit 3        | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |

|---------------------|---------------------|--------------------------------------------------------------------------------------------------------|----------------------|------------------|-----------------|--------------|-------------|-------|-------|----------------------|---------------------------------|--|

| Bank 4              |                     |                                                                                                        |                      |                  |                 |              |             |       |       |                      |                                 |  |

|                     | INDF0               | Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physical register) |                      |                  |                 |              |             |       |       |                      | XXXX XXXX                       |  |

| 201h <sup>(1)</sup> | INDF1               |                                                                                                        | nis location use     | es contents of   | FSR1H/FSR1      | L to address | data memory | /     |       | XXXX XXXX            | xxxx xxxx                       |  |

| 202h <sup>(1)</sup> | PCL                 |                                                                                                        | ,<br>,               | st Significant E | lyte            |              |             |       |       | 0000 0000            | 0000 0000                       |  |

| 203h <sup>(1)</sup> | STATUS              | _                                                                                                      | _                    | _                | TO              | PD           | Z           | DC    | С     | 1 1000               | q quuu                          |  |

| 204h <sup>(1)</sup> | FSR0L               | Indirect Data                                                                                          | Memory Addr          | ess 0 Low Poir   | nter            |              | I           | I     | 1     | 0000 0000            | uuuu uuuu                       |  |

| 205h <sup>(1)</sup> | FSR0H               | Indirect Data                                                                                          | Memory Addr          | ess 0 High Poi   | nter            |              |             |       |       | 0000 0000            | 0000 0000                       |  |

| 206h <sup>(1)</sup> | FSR1L               | Indirect Data                                                                                          | Memory Addr          | ess 1 Low Poir   | nter            |              |             |       |       | 0000 0000            | uuuu uuuu                       |  |

| 207h <sup>(1)</sup> | FSR1H               | Indirect Data                                                                                          | Memory Addr          | ess 1 High Poi   | nter            |              |             |       |       | 0000 0000            | 0000 0000                       |  |

| 208h <sup>(1)</sup> | BSR                 | _                                                                                                      | _                    | _                |                 |              | BSR<4:0>    |       |       | 0 0000               | 0 0000                          |  |

| 209h <sup>(1)</sup> | WREG                | Working Reg                                                                                            | ister                |                  |                 |              |             |       |       | 0000 0000            | uuuu uuuu                       |  |

| 20Ah <sup>(1)</sup> | PCLATH              | _                                                                                                      | Write Buffer f       | or the upper 7   | bits of the Pro | ogram Counte | r           |       |       | -000 0000            | -000 0000                       |  |

| 20Bh <sup>(1)</sup> | INTCON              | GIE                                                                                                    | PEIE                 | TMR0IE           | INTE            | IOCIE        | TMR0IF      | INTF  | IOCIF | 0000 000x            | 0000 000u                       |  |

| 20Ch                | WPUA                | _                                                                                                      | _                    | WPUA5            | WPUA4           | WPUA3        | WPUA2       | WPUA1 | WPUA0 | 11 1111              | 11 1111                         |  |

| 20Dh                | WPUB <sup>(2)</sup> | WPUB7                                                                                                  | WPUB6                | WPUB5            | WPUB4           | _            | _           | _     |       | 1111                 | 1111                            |  |

| 20Eh                | WPUC                | WPUC7 <sup>(2)</sup>                                                                                   | WPUC6 <sup>(2)</sup> | WPUC5            | WPUC4           | WPUC3        | WPUC2       | WPUC1 | WPUC0 | 1111 1111            | 1111 1111                       |  |

| 20Fh                | —                   | Unimplement                                                                                            | ed                   |                  |                 |              |             |       |       | _                    | —                               |  |

| 210h                | _                   | Unimplement                                                                                            | ed                   |                  |                 |              |             |       |       | _                    | _                               |  |

| 211h                | SSP1BUF             | Synchronous                                                                                            | Serial Port Re       | eceive Buffer/T  | ransmit Regis   | ster         |             |       |       | xxxx xxxx            | uuuu uuuu                       |  |

| 212h                | SSP1ADD             |                                                                                                        |                      |                  | ADD<7           | :0>          |             |       |       | 0000 0000            | 0000 0000                       |  |

| 213h                | SSP1MSK             |                                                                                                        |                      |                  | MSK<7           | :0>          |             |       |       | 1111 1111            | 1111 1111                       |  |

| 214h                | SSP1STAT            | SMP                                                                                                    | CKE                  | D/A              | Р               | S            | R/W         | UA    | BF    | 0000 0000            | 0000 0000                       |  |

| 215h                | SSP1CON1            | WCOL                                                                                                   | SSPOV                | SSPEN            | CKP             |              | SSPM        | <3:0> |       | 0000 0000            | 0000 0000                       |  |

| 216h                | SSP1CON2            | GCEN                                                                                                   | ACKSTAT              | ACKDT            | ACKEN           | RCEN         | PEN         | RSEN  | SEN   | 0000 0000            | 0000 0000                       |  |

| 217h                | SSP1CON3            | ACKTIM                                                                                                 | PCIE                 | SCIE             | BOEN            | SDAHT        | SBCDE       | AHEN  | DHEN  | 0000 0000            | 0000 0000                       |  |

| 218h                | _                   | Unimplement                                                                                            | ed                   |                  |                 |              |             |       |       | _                    | _                               |  |

| 219h                | _                   | Unimplemented                                                                                          |                      |                  |                 |              |             |       |       | _                    | _                               |  |

| 21Ah                | _                   | Unimplemented                                                                                          |                      |                  |                 |              |             |       |       | _                    | _                               |  |

| 21Bh                | _                   | Unimplement                                                                                            | Unimplemented        |                  |                 |              |             |       |       |                      | _                               |  |

| 21Ch                | _                   | Unimplement                                                                                            | Unimplemented        |                  |                 |              |             |       |       |                      |                                 |  |

| 21Dh                | _                   | Unimplement                                                                                            | Unimplemented        |                  |                 |              |             |       |       |                      |                                 |  |

|                     |                     | Unimplement                                                                                            | Jnimplemented        |                  |                 |              |             |       |       |                      |                                 |  |

| 21Eh                | _                   | Unimplement                                                                                            | eu                   | Unimplemented    |                 |              |             |       |       |                      |                                 |  |

### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$Legend: \quad x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

3: PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

© 2010-2015 Microchip Technology Inc.

# PIC16(L)F1824/8

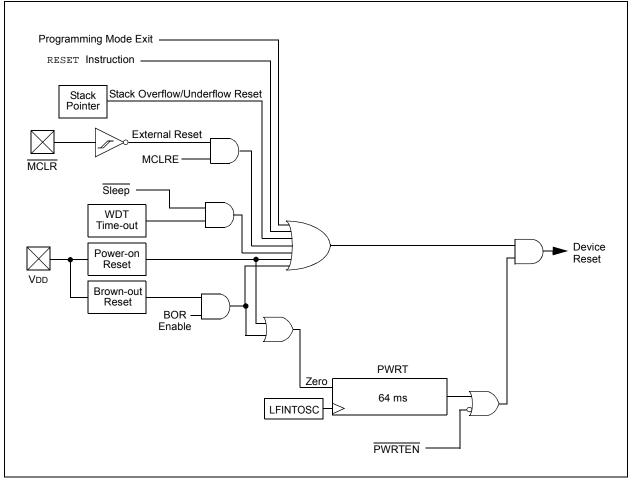

# 7.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- · Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 7-1.

### FIGURE 7-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 12.4.3 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the lowest number in the following lists.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the priority list.

<u>RC0</u>

- 1. SCL (MSSP) (PIC16(L)F1824 only)

- 2. SCK (MSSP) (PIC16(L)F1824 only)

- 3. P1D

RC1

- 1. SDA (MSSP) (PIC16(L)F1824 only)

- 2. P1C

- 3. CCP4 (PIC16(L)F1828 only)

### <u>RC2</u>

- 1. SDO (MSSP) (PIC16(L)F1824 only)

- 2. P1D

- 3. P2B

<u>RC3</u>

- 1. SS (MSSP) (PIC16(L)F1824 only)

- 2. CCP2

- 3. P1C

- 4. P2A

### <u>RC4</u>

- 1. MDOUT

- 2. SRNQ

- 3. C2OUT

- 4. TX/CK

- 5. P1B

<u>RC5</u>

- 1. RX/DT

- 2. CCP1/P1A

RC6 (PIC16(L)F1828 only)

- 1. SS (MSSP)

- 2. CCP4

RC7 (PIC16(L)F1828 only)

1. SDO (MSSP)

### 16.2 ADC Operation

### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |  |  |  |

|       | Refer to Section 16.2.6 "A/D Conver-     |  |  |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |  |  |

### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

### 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | CCPx/ECCPx |  |  |  |  |  |

|-----------------|------------|--|--|--|--|--|

| PIC16(L)F1824/8 | CCP4       |  |  |  |  |  |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 24.0** "Capture/Compare/PWM **Modules**" for more information.

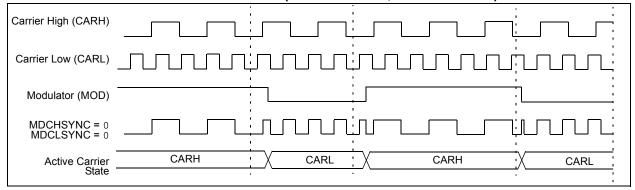

### EXAMPLE 23-1: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

| Carrier High (CARH)          |                                     |

|------------------------------|-------------------------------------|

| Carrier Low (CARL)           |                                     |

| Modulator (MOD)              |                                     |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                     |

| Active Carrier<br>State      | CARH / both CARL / CARH / both CARL |

### 24.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

### 24.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name    | Bit 7                                                                         | Bit 6                 | Bit 5         | Bit 4        | Bit 3      | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|-------------------------------------------------------------------------------|-----------------------|---------------|--------------|------------|---------|---------|---------|---------------------|

| APFCON1 | —                                                                             | —                     | -             | —            | P1DSEL     | P1CSEL  | P2BSEL  | CCP2SEL | 118                 |

| CCPxCON | PxM<                                                                          | 1:0> <b>(1)</b>       | DCxB          | <1:0>        |            | CCPxM<  | <3:0>   |         | 225                 |

| CCPRxL  | Capture/Cor                                                                   | mpare/PWM             | Register x Lo | ow Byte (LSE | 3)         |         |         |         | 203*                |

| CCPRxH  | Capture/Cor                                                                   | mpare/PWM             | Register x H  | igh Byte (MS | B)         |         |         |         | 203*                |

| CMxCON0 | CxON                                                                          | CxOUT                 | CxOE          | CxPOL        | —          | CxSP    | CxHYS   | CxSYNC  | 171                 |

| CMxCON1 | CxINTP                                                                        | CxINTN                | CxPCI         | H<1:0>       | —          |         | CxNCI   | H<1:0>  | 172                 |

| INLVLA  | _                                                                             | _                     | INLVLA5       | INLVLA4      | INLVLA3    | INLVLA2 | INLVLA1 | INLVLA0 | 123                 |

| INLVLC  | INLVLC7(2)                                                                    | INLVLC6(2)            | INLVLC5       | INLVLC4      | INLVLC3    | INLVLC2 | INLVLC1 | INLVLC0 | 134                 |

| INTCON  | GIE                                                                           | PEIE                  | TMR0IE        | INTE         | IOCIE      | TMR0IF  | INTF    | IOCIF   | 89                  |

| PIE1    | TMR1GIE                                                                       | ADIE                  | RCIE          | TXIE         | SSP1IE     | CCP1IE  | TMR2IE  | TMR1IE  | 90                  |

| PIE2    | OSFIE                                                                         | C2IE                  | C1IE          | EEIE         | BCL1IE     | _       | —       | CCP2IE  | 91                  |

| PIE3    | _                                                                             | _                     | CCP4IE        | CCP3IE       | TMR6IE     | _       | TMR4IE  | _       | 92                  |

| PIR1    | TMR1GIF                                                                       | ADIF                  | RCIF          | TXIF         | SSP1IF     | CCP1IF  | TMR2IF  | TMR1IF  | 93                  |

| PIR2    | OSFIF                                                                         | C2IF                  | C1IF          | EEIF         | BCL1IF     | _       | —       | CCP2IF  | 94                  |

| PIR3    | _                                                                             | _                     | CCP4IF        | CCP3IF       | TMR6IF     | _       | TMR4IF  | _       | 95                  |

| T1CON   | TMR1CS1                                                                       | TMR1CS0               | T1CKPS1       | T1CKPS0      | T1OSCEN    | T1SYNC  | —       | TMR10N  | 186                 |

| T1GCON  | TMR1GE                                                                        | T1GPOL                | T1GTM         | T1GSPM       | T1GGO/DONE | T1GVAL  | T1GSS1  | T1GSS0  | 187                 |

| TMR1L   | . Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                       |               |              |            |         |         |         |                     |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register    |                       |               |              |            |         |         |         | 182*                |

| TRISA   | —                                                                             | —                     | TRISA5        | TRISA4       | TRISA3     | TRISA2  | TRISA1  | TRISA0  | 121                 |

| TRISC   | TRISC7 <sup>(2)</sup>                                                         | TRISC6 <sup>(2)</sup> | TRISC5        | TRISC4       | TRISC3     | TRISC2  | TRISC1  | TRISC0  | 132                 |

### TABLE 24-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

**Legend:** — = unimplemented locations, read as '0'. Shaded cells are not used by the Capture.

\* Page provides register information.

**Note 1:** Applies to ECCP modules only.

2: PIC16(L)F1828 only.

# PIC16(L)F1824/8

| R/W-0/0                                                                                                                                                      | R/W-0/0                         | R/W-0/0                              | R/W-0/0   | R/W-0/0           | R/W-0/0                                              | R/W-0/0        | R/W-0/0        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------|-----------|-------------------|------------------------------------------------------|----------------|----------------|--|--|--|

| PxRSEN                                                                                                                                                       |                                 |                                      | PxDC<6:0> |                   |                                                      |                |                |  |  |  |

| bit 7                                                                                                                                                        |                                 |                                      |           |                   |                                                      |                | bit 0          |  |  |  |

|                                                                                                                                                              |                                 |                                      |           |                   |                                                      |                |                |  |  |  |

| Legend:                                                                                                                                                      |                                 |                                      |           |                   |                                                      |                |                |  |  |  |

| R = Readabl                                                                                                                                                  | e bit                           | W = Writable                         | bit       | U = Unimplen      | nented bit, read                                     | d as '0'       |                |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Valu                                                                                                          |                                 |                                      |           |                   | n/n = Value at POR and BOR/Value at all other Resets |                |                |  |  |  |

| '1' = Bit is se                                                                                                                                              | t                               | '0' = Bit is cle                     | ared      |                   |                                                      |                |                |  |  |  |

|                                                                                                                                                              |                                 |                                      |           |                   |                                                      |                |                |  |  |  |

| bit 7                                                                                                                                                        | PxRSEN: P                       | WM Restart Ena                       | able bit  |                   |                                                      |                |                |  |  |  |

|                                                                                                                                                              |                                 | uto-shutdown, th<br>M restarts auton |           | oit clears automa | atically once the                                    | e shutdown eve | ent goes away; |  |  |  |

| 0 = Upon auto-shutdown, CCPxASE must be cleared in software to restart the PWM                                                                               |                                 |                                      |           |                   |                                                      |                |                |  |  |  |

| bit 6-0                                                                                                                                                      | PxDC<6:0>: PWM Delay Count bits |                                      |           |                   |                                                      |                |                |  |  |  |

| PxDCx = Number of Fosc/4 (4 * Tosc) cycles between the scheduled time when a PWM signa<br>should transition active and the actual time it transitions active |                                 |                                      |           |                   |                                                      |                |                |  |  |  |

### REGISTER 24-4: PWMxCON: ENHANCED PWM CONTROL REGISTER

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

### 26.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 26-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

### 26.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the TX/CK I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

## 26.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 26.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See <b>Section 26.1.2.5</b> |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | "Receive Overrun Error" for more                                                                                                              |  |  |  |  |  |  |

|       | information on overrun errors.                                                                                                                |  |  |  |  |  |  |

### 26.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

| Name                  | Bit 7                  | Bit 6                  | Bit 5                | Bit 4       | Bit 3        | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|------------------------|------------------------|----------------------|-------------|--------------|---------|---------|---------|---------------------|

| APFCON0               | RXDTSEL                | SDOSEL <sup>(2)</sup>  | SSSEL <sup>(2)</sup> | —           | T1GSEL       | TXCKSEL | _       | —       | 117                 |

| BAUDCON               | ABDOVF                 | RCIDL                  | _                    | SCKP        | BRG16        | _       | WUE     | ABDEN   | 296                 |

| INLVLA <sup>(3)</sup> | _                      | _                      | INLVLA5              | INLVLA4     | INLVLA3      | INLVLA2 | INLVLA1 | INLVLA0 | 123                 |

| INLVLB <sup>(1)</sup> | INLVLB7                | INLVLB6                | INLVLB5              | INLVLB4     | _            | _       | _       | _       | 128                 |

| INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5              | INLVLC4     | INLVLC3      | INLVLC2 | INLVLC1 | INLVLC0 | 134                 |

| INTCON                | GIE                    | PEIE                   | TMR0IE               | INTE        | IOCIE        | TMR0IF  | INTF    | IOCIF   | 89                  |

| PIE1                  | TMR1GIE                | ADIE                   | RCIE                 | TXIE        | SSP1IE       | CCP1IE  | TMR2IE  | TMR1IE  | 90                  |

| PIR1                  | TMR1GIF                | ADIF                   | RCIF                 | TXIF        | SSP1IF       | CCP1IF  | TMR2IF  | TMR1IF  | 93                  |

| RCREG                 |                        |                        | EUS                  | SART Receiv | e Data Regis | ster    |         |         | 290*                |

| RCSTA                 | SPEN                   | RX9                    | SREN                 | CREN        | ADDEN        | FERR    | OERR    | RX9D    | 295                 |

| SPBRGL                | BRG7                   | BRG6                   | BRG5                 | BRG4        | BRG3         | BRG2    | BRG1    | BRG0    | 297*                |

| SPBRGH                | BRG15                  | BRG14                  | BRG13                | BRG12       | BRG11        | BRG10   | BRG9    | BRG8    | 297*                |

| TRISA <sup>(3)</sup>  | _                      | _                      | TRISA5               | TRISA4      | TRISA3       | TRISA2  | TRISA1  | TRISA0  | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                 | TRISB6                 | TRISB5               | TRISB4      | _            | —       | _       | —       | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5               | TRISC4      | TRISC3       | TRISC2  | TRISC1  | TRISC0  | 127                 |

| TXSTA                 | CSRC                   | TX9                    | TXEN                 | SYNC        | SENDB        | BRGH    | TRMT    | TX9D    | 294                 |

### TABLE 26-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

Note 1: PIC16(L)F1828 only.

2: PIC16(L)F1824 only.

**3:** Unshaded cells apply to PIC16(L)F1828 only.

### TABLE 26-3: BAUD RATE FORMULAS

| C    | onfiguration B | lits |                     | Baud Rate Formula |

|------|----------------|------|---------------------|-------------------|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Baud Rate Formula |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0              | 1    | 8-bit/Asynchronous  |                   |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |

| 1    | 0              | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1              | x    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair

### TABLE 26-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF | RCIDL | _     | SCKP  | BRG16 | —     | WUE   | ABDEN | 296                 |

| RCSTA   | SPEN   | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 295                 |

| SPBRGL  | BRG7   | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 297*                |

| SPBRGH  | BRG15  | BRG14 | BRG13 | BRG12 | BRG11 | BRG10 | BRG9  | BRG8  | 297*                |

| TXSTA   | CSRC   | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 294                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

|        |                  |            |                             |                  | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>G16 =</b> 0 |                             |                  |            |                             |  |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|----------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz |            |                             | Fosc           | : = 3.686      | 4 MHz                       | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                | _          | -                           | _                | _          | _                           | _              | _              | _                           | 300              | 0.16       | 207                         |  |

| 1200   | —                | —          | —                           | 1202             | 0.16       | 207                         | 1200           | 0.00           | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00           | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00           | 23                          | —                |            | —                           |  |

| 10417  | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53           | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19231            | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00           | 11                          | —                | _          | _                           |  |

| 57.6k  | 55556            | -3.55      | 8                           | —                | _          | _                           | 57.60k         | 0.00           | 3                           | —                | _          | _                           |  |

| 115.2k | —                | _          | —                           | —                | _          | —                           | 115.2k         | 0.00           | 1                           | —                | _          | —                           |  |

# TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC     | G16 = 1    |                             |                |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz |            | Fosc = 20.000 MHz           |                |            | Fosc                        | : = 18.43      | 2 MHz      | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00       | 6666                        | 300.0          | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.0          | 0.00       | 2303                        |

| 1200   | 1200              | -0.02      | 3332                        | 1200           | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200           | 0.00       | 575                         |

| 2400   | 2401              | -0.04      | 832                         | 2399           | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2400           | 0.00       | 287                         |

| 9600   | 9615              | 0.16       | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417             | 0.00       | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16       | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k            | -0.79      | 34                          | 56.818         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.6k            | 2.12       | 16                          | 113.636        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           |

|        |                |                  |                             |                | SYNC             | <b>C</b> = 0, BRGH          | I = 0, BRG     | <b>616 =</b> 1 |                             |                  |            |                             |  |

|--------|----------------|------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|----------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fos            | Fosc = 8.000 MHz |                             |                | Fosc = 4.000 MHz |                             |                | : = 3.686      | 4 MHz                       | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9          | -0.02            | 1666                        | 300.1          | 0.04             | 832                         | 300.0          | 0.00           | 767                         | 300.5            | 0.16       | 207                         |  |

| 1200   | 1199           | -0.08            | 416                         | 1202           | 0.16             | 207                         | 1200           | 0.00           | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404           | 0.16             | 207                         | 2404           | 0.16             | 103                         | 2400           | 0.00           | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615           | 0.16             | 51                          | 9615           | 0.16             | 25                          | 9600           | 0.00           | 23                          | —                | _          | _                           |  |

| 10417  | 10417          | 0.00             | 47                          | 10417          | 0.00             | 23                          | 10473          | 0.53           | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19.23k         | 0.16             | 25                          | 19.23k         | 0.16             | 12                          | 19.20k         | 0.00           | 11                          | —                | _          | _                           |  |

| 57.6k  | 55556          | -3.55            | 8                           | _              | _                | _                           | 57.60k         | 0.00           | 3                           | —                | _          | _                           |  |

| 115.2k | _              | _                | _                           | _              | _                | _                           | 115.2k         | 0.00           | 1                           | —                | _          | _                           |  |

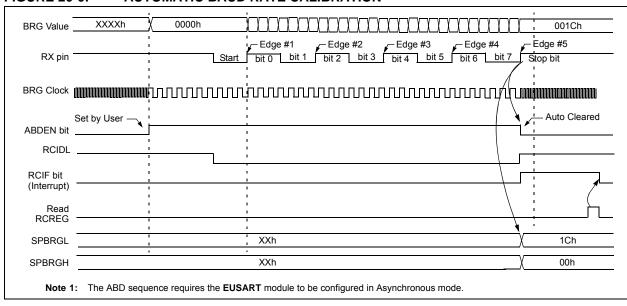

### 26.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 26-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 26-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 26-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 26.3.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| TABLE 26-6:BRG COUNTER CLOCK RATES |

|------------------------------------|

|------------------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

### FIGURE 26-6: AUTOMATIC BAUD RATE CALIBRATION

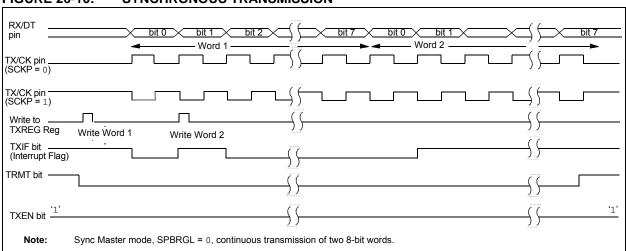

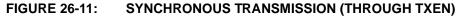

#### **FIGURE 26-10:** SYNCHRONOUS TRANSMISSION

#### **TABLE 26-7:** SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                         | Bit 6                 | Bit 5                | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register on<br>Page |

|---------|-------------------------------|-----------------------|----------------------|-------|--------|---------|--------|--------|---------------------|

| APFCON0 | RXDTSEL                       | SDOSEL <sup>(1)</sup> | SSSEL <sup>(1)</sup> | —     | T1GSEL | TXCKSEL | —      | —      | 117                 |

| BAUDCON | ABDOVF                        | RCIDL                 | —                    | SCKP  | BRG16  | _       | WUE    | ABDEN  | 296                 |

| INTCON  | GIE                           | PEIE                  | TMR0IE               | INTE  | IOCIE  | TMR0IF  | INTF   | IOCIF  | 89                  |

| PIE1    | TMR1GIE                       | ADIE                  | RCIE                 | TXIE  | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 90                  |

| PIR1    | TMR1GIF                       | ADIF                  | RCIF                 | TXIF  | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 93                  |

| RCSTA   | SPEN                          | RX9                   | SREN                 | CREN  | ADDEN  | FERR    | OERR   | RX9D   | 295                 |

| SPBRGL  | BRG7                          | BRG6                  | BRG5                 | BRG4  | BRG3   | BRG2    | BRG1   | BRG0   | 297*                |

| SPBRGH  | BRG15                         | BRG14                 | BRG13                | BRG12 | BRG11  | BRG10   | BRG9   | BRG8   | 297*                |

| TXREG   | EUSART Transmit Data Register |                       |                      |       |        |         | 287*   |        |                     |

| TXSTA   | CSRC                          | TX9                   | TXEN                 | SYNC  | SENDB  | BRGH    | TRMT   | TX9D   | 294                 |

— = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

Page provides register information.

PIC16(L)F1824 only.

Legend:

Note 1:

# 29.0 INSTRUCTION SET SUMMARY

Each PIC16 instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

### TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number. (0-1)                                                                                                                                                         |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                       |

### TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-out bit    |

| С     | Carry bit       |

| DC    | Digit carry bit |

| Z     | Zero bit        |

| PD    | Power-down bit  |

## 30.3 DC Characteristics: PIC16(L)F1824/8-I/E (Power-Down)

| PIC16LF1 | 824/8                   |                      |                | rd Operating temper | •      | -40°C ≤                                                                                                                        | $TA \le +85^\circ$ | h <b>erwise stated)</b><br>°C for industrial<br>5°C for extended |  |  |

|----------|-------------------------|----------------------|----------------|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------|--|--|

| PIC16F18 | 24/8                    |                      |                | rd Operating temper |        | litions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                    |                                                                  |  |  |

| Param    |                         |                      | Tunt Max. Max. |                     | 11-24- |                                                                                                                                | Conditions         |                                                                  |  |  |

| No.      | Device Characteristics  | Min.                 | Тур†           | +85°C               | +125°C | Units                                                                                                                          | Vdd                | Note                                                             |  |  |

|          | Power-down Base Current | (IPD) <sup>(2)</sup> |                | •                   |        |                                                                                                                                |                    |                                                                  |  |  |

| D022     |                         | _                    | 0.02           | 1.0                 | 2.4    | μA                                                                                                                             | 1.8                | WDT, BOR, FVR, and T1OSC                                         |  |  |

|          |                         | —                    | 0.03           | 1.5                 | 3.0    | μA                                                                                                                             | 3.0                | disabled, all Peripherals Inactive                               |  |  |

| D022     |                         | _                    | 18             | 37                  | 44     | μA                                                                                                                             | 1.8                | WDT, BOR, FVR, and T1OSC                                         |  |  |

|          |                         | _                    | 20             | 42                  | 48     | μA                                                                                                                             | 3.0                | disabled, all Peripherals Inactive                               |  |  |

|          |                         | —                    | 22             | 45                  | 65     | μA                                                                                                                             | 5.0                |                                                                  |  |  |

| D023     |                         |                      | 0.2            | 2.0                 | 3.0    | μA                                                                                                                             | 1.8                | LPWDT Current (Note 1)                                           |  |  |

|          |                         | —                    | 0.5            | 2.0                 | 4.0    | μA                                                                                                                             | 3.0                |                                                                  |  |  |

| D023     |                         | —                    | 18             | 38                  | 44     | μA                                                                                                                             | 1.8                | LPWDT Current (Note 1)                                           |  |  |

|          |                         |                      | 21             | 43                  | 48     | μA                                                                                                                             | 3.0                |                                                                  |  |  |

|          |                         | —                    | 22             | 46                  | 65     | μA                                                                                                                             | 5.0                |                                                                  |  |  |

| D023A    |                         |                      | 12             | 22                  | 25     | μA                                                                                                                             | 1.8                | FVR current                                                      |  |  |

|          |                         | —                    | 13             | 24                  | 27     | μA                                                                                                                             | 3.0                |                                                                  |  |  |

| D023A    |                         | _                    | 33             | 62                  | 65     | μA                                                                                                                             | 1.8                | FVR current                                                      |  |  |

|          |                         | _                    | 40             | 72                  | 75     | μA                                                                                                                             | 3.0                |                                                                  |  |  |

|          |                         | —                    | 68             | 115                 | 120    | μA                                                                                                                             | 5.0                |                                                                  |  |  |

| D024     |                         | —                    | 7.0            | 14                  | 16     | μA                                                                                                                             | 3.0                | BOR Current (Note 1)                                             |  |  |

| D024     |                         | —                    | 24             | 47                  | 50     | μA                                                                                                                             | 3.0                | BOR Current (Note 1)                                             |  |  |

|          |                         | —                    | 29             | 55                  | 70     | μA                                                                                                                             | 5.0                |                                                                  |  |  |

| D025     |                         | _                    | 0.65           | 3.5                 | 4.0    | μA                                                                                                                             | 1.8                | T1OSC Current (Note 1)                                           |  |  |

|          |                         | _                    | 2.3            | 4.0                 | 4.5    | μA                                                                                                                             | 3.0                |                                                                  |  |  |

| D025     |                         | _                    | 19             | 39                  | 45     | μA                                                                                                                             | 1.8                | T1OSC Current (Note 1)                                           |  |  |

|          |                         | _                    | 21             | 43                  | 59     | μA                                                                                                                             | 3.0                |                                                                  |  |  |

|          |                         | —                    | 23             | 55                  | 75     | μA                                                                                                                             | 5.0                |                                                                  |  |  |

| D026     |                         | _                    | 0.03           | 1.5                 | 3.0    | μA                                                                                                                             | 1.8                | A/D Current (Note 1, 3),                                         |  |  |

|          |                         | _                    | 0.04           | 2.0                 | 3.5    | μA                                                                                                                             | 3.0                | no conversion in progress                                        |  |  |

| D026     |                         | _                    | 18             | 38                  | 45     | μA                                                                                                                             | 1.8                | A/D Current (Note 1, 3),                                         |  |  |

|          |                         | _                    | 20             | 43                  | 49     | μA                                                                                                                             | 3.0                | no conversion in progress                                        |  |  |

|          |                         | —                    | 22             | 46                  | 65     | μA                                                                                                                             | 5.0                |                                                                  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

**3:** A/D oscillator source is FRC.

### TABLE 30-2: OSCILLATOR PARAMETERS

|              | r <b>d Operati</b> n<br>ng Tempera | ng Conditions (unless otherwise stature $-40^{\circ}C \le TA \le +125^{\circ}C$ | tated)             |      |      |      |       |                                                                               |

|--------------|------------------------------------|---------------------------------------------------------------------------------|--------------------|------|------|------|-------|-------------------------------------------------------------------------------|

| Param<br>No. | Sym.                               | Characteristic                                                                  | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                    |

| OS08         | HFosc                              | Internal Calibrated HFINTOSC                                                    | ±2%                | _    | 16.0 | _    | MHz   | $0^{\circ}C \leq TA \leq \text{+}60^{\circ}C,  \text{VDD} \geq 2.5 \text{V}$  |

|              |                                    | Frequency <sup>(1)</sup>                                                        | ±3%                |      | 16.0 |      | MHz   | $60^{\circ}C \leq TA \leq +85^{\circ}C, \ V\text{DD} \geq 2.5V$               |

|              |                                    |                                                                                 | ±5%                | —    | 16.0 |      | MHz   | $-40^\circ C \le T A \le +125^\circ C$                                        |

| OS08A        | MFosc                              | Internal Calibrated MFINTOSC                                                    | ±2%                | —    | 500  |      | kHz   | $0^{\circ}C \leq TA \leq \text{+}60^{\circ}C, \ V\text{DD} \geq 2.5V$         |

|              |                                    | Frequency <sup>(1)</sup>                                                        | ±3%                | _    | 500  |      | kHz   | $60^{\circ}C \leq TA \leq \text{+}85^{\circ}C,  \text{VDD} \geq 2.5 \text{V}$ |

|              |                                    |                                                                                 | ±5%                | —    | 500  |      | kHz   | $-40^\circ C \le T A \le +125^\circ C$                                        |

| OS09         | LFosc                              | Internal LFINTOSC Frequency                                                     | ±25%               | —    | 31   |      | kHz   | $-40^\circ C \le T A \le +125^\circ C$                                        |

| OS10*        | TIOSC ST                           | HFINTOSC<br>Wake-up from Sleep Start-up Time                                    | _                  | —    | 5    | 8    | μS    |                                                                               |

|              |                                    | MFINTOSC<br>Wake-up from Sleep Start-up Time                                    | _                  |      | 20   | 30   | μS    |                                                                               |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible.  $0.1 \ \mu\text{F}$  and  $0.01 \ \mu\text{F}$  values in parallel are recommended.

### TABLE 30-3: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.7V to 5.5V)

| Param<br>No. | Sym.                | Characteristic                | Min.   | Тур† | Max.   | Units | Conditions |