#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1828t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

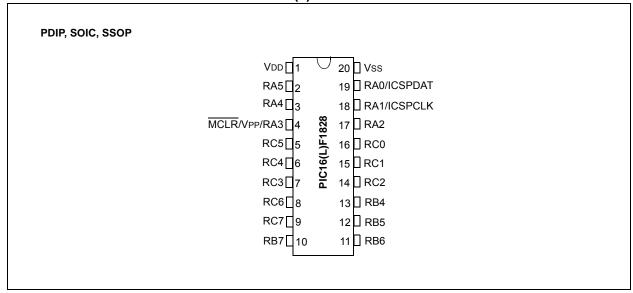

#### FIGURE 3: 20-PIN DIAGRAM FOR PIC16(L)F1828

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

Г

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### **REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

| Note 1: | The C and DC bits operate as Borrow         |

|---------|---------------------------------------------|

|         | and Digit Borrow out bits, respectively, in |

|         | subtraction.                                |

| U-0              | U-0   | U-0               | R-1/q | R-1/q          | R/W-0/u          | R/W-0/u           | R/W-0/u          |

|------------------|-------|-------------------|-------|----------------|------------------|-------------------|------------------|

| _                | _     | —                 | TO    | PD             | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7            |       |                   |       |                |                  |                   | bit 0            |

|                  |       |                   |       |                |                  |                   |                  |

| Legend:          |       |                   |       |                |                  |                   |                  |

| R = Readable b   | bit   | W = Writable I    | bit   | U = Unimpler   | mented bit, read | as '0'            |                  |

| u = Bit is uncha | inged | x = Bit is unkn   | iown  | -n/n = Value a | at POR and BOI   | R/Value at all c  | ther Resets      |

| '1' = Bit is set |       | '0' = Bit is clea | ared  | q = Value de   | pends on condit  | ion               |                  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                                                                 |

| bit 3   | PD: Power-down bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                                                               |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                               |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                                                             |

| bit 0   | C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                              |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

### TABLE 3-5:PIC16F1824/PIC16F1828 MEMORY MAP, BANKS 8-15

|      | L 5-5. II                    | 0101 | 1024/110101                  | 1020 |                              | <b>1</b> 71, | DANKO U-13                   | ,    |                              |      |                              |      |                              |      |                              |

|------|------------------------------|------|------------------------------|------|------------------------------|--------------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|

|      | BANK 8                       |      | BANK 9                       |      | BANK 10                      |              | BANK 11                      |      | BANK 12                      |      | BANK 13                      |      | BANK 14                      |      | BANK 15                      |

| 400h | INDF0                        | 480h | INDF0                        | 500h | INDF0                        | 580h         | INDF0                        | 600h | INDF0                        | 680h | INDF0                        | 700h | INDF0                        | 780h | INDF0                        |

| 401h | INDF1                        | 481h | INDF1                        | 501h | INDF1                        | 581h         | INDF1                        | 601h | INDF1                        | 681h | INDF1                        | 701h | INDF1                        | 781h | INDF1                        |

| 402h | PCL                          | 482h | PCL                          | 502h | PCL                          | 582h         | PCL                          | 602h | PCL                          | 682h | PCL                          | 702h | PCL                          | 782h | PCL                          |

| 403h | STATUS                       | 483h | STATUS                       | 503h | STATUS                       | 583h         | STATUS                       | 603h | STATUS                       | 683h | STATUS                       | 703h | STATUS                       | 783h | STATUS                       |

| 404h | FSR0L                        | 484h | FSR0L                        | 504h | FSR0L                        | 584h         | FSR0L                        | 604h | FSR0L                        | 684h | FSR0L                        | 704h | FSR0L                        | 784h | FSR0L                        |

| 405h | FSR0H                        | 485h | FSR0H                        | 505h | FSR0H                        | 585h         | FSR0H                        | 605h | FSR0H                        | 685h | FSR0H                        | 705h | FSR0H                        | 785h | FSR0H                        |

| 406h | FSR1L                        | 486h | FSR1L                        | 506h | FSR1L                        | 586h         | FSR1L                        | 606h | FSR1L                        | 686h | FSR1L                        | 706h | FSR1L                        | 786h | FSR1L                        |

| 407h | FSR1H                        | 487h | FSR1H                        | 507h | FSR1H                        | 587h         | FSR1H                        | 607h | FSR1H                        | 687h | FSR1H                        | 707h | FSR1H                        | 787h | FSR1H                        |

| 408h | BSR                          | 488h | BSR                          | 508h | BSR                          | 588h         | BSR                          | 608h | BSR                          | 688h | BSR                          | 708h | BSR                          | 788h | BSR                          |

| 409h | WREG                         | 489h | WREG                         | 509h | WREG                         | 589h         | WREG                         | 609h | WREG                         | 689h | WREG                         | 709h | WREG                         | 789h | WREG                         |

| 40Ah | PCLATH                       | 48Ah | PCLATH                       | 50Ah | PCLATH                       | 58Ah         | PCLATH                       | 60Ah | PCLATH                       | 68Ah | PCLATH                       | 70Ah | PCLATH                       | 78Ah | PCLATH                       |

| 40Bh | INTCON                       | 48Bh | INTCON                       | 50Bh | INTCON                       | 58Bh         | INTCON                       | 60Bh | INTCON                       | 68Bh | INTCON                       | 70Bh | INTCON                       | 78Bh | INTCON                       |

| 40Ch | —                            | 48Ch | —                            | 50Ch | —                            | 58Ch         | —                            | 60Ch | —                            | 68Ch | —                            | 70Ch | —                            | 78Ch | —                            |

| 40Dh | —                            | 48Dh | —                            | 50Dh | —                            | 58Dh         | —                            | 60Dh | —                            | 68Dh | —                            | 70Dh | —                            | 78Dh | —                            |

| 40Eh | _                            | 48Eh | _                            | 50Eh |                              | 58Eh         |                              | 60Eh | _                            | 68Eh | _                            | 70Eh |                              | 78Eh | _                            |

| 40Fh | —                            | 48Fh | —                            | 50Fh | —                            | 58Fh         | —                            | 60Fh | —                            | 68Fh | —                            | 70Fh | —                            | 78Fh | —                            |

| 410h | _                            | 490h | _                            | 510h |                              | 590h         |                              | 610h | _                            | 690h | _                            | 710h |                              | 790h | _                            |

| 411h | —                            | 491h | —                            | 511h | —                            | 591h         | _                            | 611h | —                            | 691h | —                            | 711h | —                            | 791h | —                            |

| 412h | —                            | 492h | —                            | 512h | —                            | 592h         | —                            | 612h | —                            | 692h | —                            | 712h | —                            | 792h | —                            |

| 413h | —                            | 493h | —                            | 513h | —                            | 593h         | _                            | 613h | —                            | 693h | —                            | 713h | —                            | 793h | —                            |

| 414h | —                            | 494h | _                            | 514h | _                            | 594h         | _                            | 614h | _                            | 694h | _                            | 714h | _                            | 794h | _                            |

| 415h | TMR4                         | 495h | —                            | 515h | —                            | 595h         | _                            | 615h | —                            | 695h | —                            | 715h | —                            | 795h | —                            |

| 416h | PR4                          | 496h | _                            | 516h | _                            | 596h         | _                            | 616h | _                            | 696h | —                            | 716h | —                            | 796h | —                            |

| 417h | T4CON                        | 497h | —                            | 517h | —                            | 597h         | —                            | 617h | —                            | 697h | —                            | 717h | —                            | 797h | —                            |

| 418h | _                            | 498h | _                            | 518h |                              | 598h         |                              | 618h | _                            | 698h | _                            | 718h |                              | 798h | _                            |

| 419h | —                            | 499h | —                            | 519h | —                            | 599h         | _                            | 619h | —                            | 699h | —                            | 719h | —                            | 799h | —                            |

| 41Ah | _                            | 49Ah | _                            | 51Ah |                              | 59Ah         |                              | 61Ah | _                            | 69Ah | _                            | 71Ah |                              | 79Ah | _                            |

| 41Bh | —                            | 49Bh | —                            | 51Bh | —                            | 59Bh         | —                            | 61Bh | —                            | 69Bh | —                            | 71Bh | —                            | 79Bh | —                            |

| 41Ch | TMR6                         | 49Ch | —                            | 51Ch | _                            | 59Ch         | _                            | 61Ch | —                            | 69Ch | —                            | 71Ch | _                            | 79Ch | —                            |

| 41Dh | PR6                          | 49Dh | _                            | 51Dh |                              | 59Dh         |                              | 61Dh | _                            | 69Dh | _                            | 71Dh |                              | 79Dh | _                            |

| 41Eh | T6CON                        | 49Eh | _                            | 51Eh |                              | 59Eh         |                              | 61Eh | _                            | 69Eh | _                            | 71Eh |                              | 79Eh | _                            |

| 41Fh | —                            | 49Fh | —                            | 51Fh |                              | 59Fh         |                              | 61Fh | _                            | 69Fh | —                            | 71Fh | _                            | 79Fh |                              |

| 420h |                              | 4A0h |                              | 520h |                              | 5A0h         |                              | 620h |                              | 6A0h |                              | 720h |                              | 7A0h |                              |

|      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |              | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |

|      |                              |      |                              | 1    |                              |              |                              |      |                              |      |                              |      |                              |      |                              |

| 46Fh |                              | 4EFh |                              | 56Fh |                              | 5EFh         |                              | 66Fh |                              | 6EFh |                              | 76Fh |                              | 7EFh |                              |

| 470h |                              | 4F0h |                              | 570h |                              | 5F0h         |                              | 670h |                              | 6F0h |                              | 770h |                              | 7F0h |                              |

|      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |              | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |

| 4756 |                              | 4FFh |                              | 575h | 7.511 7.111                  | 5FFh         |                              | 67Fh |                              | AEEh |                              | 77Fh |                              | 7FFh | / // //                      |

| 47Fh |                              | 466  |                              | 57Fh |                              | SEEN         |                              | 07FN |                              | 6FFh |                              | //FN |                              | /۲۲Ո |                              |

Legend: = Unimplemented data memory locations, read as '0'.

| IABLE               | 3-9. 3 |                |                                                                                                           | REGIST           |                 |              |          |       |         | 1                    |                                 |

|---------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------|----------|-------|---------|----------------------|---------------------------------|

| Address             | Name   | Bit 7          | Bit 6                                                                                                     | Bit 5            | Bit 4           | Bit 3        | Bit 2    | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 8              |        |                |                                                                                                           |                  |                 |              |          |       |         |                      |                                 |

| 400h <sup>(1)</sup> | INDF0  |                | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                  |                 |              |          |       |         |                      | xxxx xxxx                       |

| 401h <sup>(1)</sup> | INDF1  |                | dressing this location uses contents of FSR1H/FSR1L to address data memory<br>t a physical register)      |                  |                 |              |          |       |         |                      | XXXX XXXX                       |

| 402h <sup>(1)</sup> | PCL    | Program Cou    | inter (PC) Lea                                                                                            | st Significant E | Byte            |              |          |       |         | 0000 0000            | 0000 0000                       |

| 403h <sup>(1)</sup> | STATUS | _              | _                                                                                                         | _                | TO              | PD           | Z        | DC    | С       | 1 1000               | q quuu                          |

| 404h <sup>(1)</sup> | FSR0L  | Indirect Data  | Memory Addr                                                                                               | ess 0 Low Poi    | nter            |              |          |       |         | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(1)</sup> | FSR0H  | Indirect Data  | Memory Addr                                                                                               | ess 0 High Po    | inter           |              |          |       |         | 0000 0000            | 0000 0000                       |

| 406h <sup>(1)</sup> | FSR1L  | Indirect Data  | Memory Addr                                                                                               | ess 1 Low Poi    | nter            |              |          |       |         | 0000 0000            | uuuu uuuu                       |

| 407h <sup>(1)</sup> | FSR1H  | Indirect Data  | Memory Addr                                                                                               | ess 1 High Poi   | inter           |              |          |       |         | 0000 0000            | 0000 0000                       |

| 408h <sup>(1)</sup> | BSR    | _              | _                                                                                                         | _                |                 |              | BSR<4:0> |       |         | 0 0000               | 0 0000                          |

| 409h <sup>(1)</sup> | WREG   | Working Reg    | ister                                                                                                     | •                |                 |              |          |       |         | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1)</sup> | PCLATH | _              | Write Buffer f                                                                                            | or the upper 7   | bits of the Pro | ogram Counte | er       |       |         | -000 0000            | -000 0000                       |

| 40Bh <sup>(1)</sup> | INTCON | GIE            | PEIE                                                                                                      | TMR0IE           | INTE            | IOCIE        | TMR0IF   | INTF  | IOCIF   | 0000 000x            | 0000 000u                       |

| 40Ch                | _      | Unimplement    | ed                                                                                                        | •                | •               | •            | •        |       |         | _                    | _                               |

| 40Dh                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 40Eh                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 40Fh                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 410h                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 411h                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 412h                | —      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    |                                 |

| 413h                | —      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 414h                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| 415h                | TMR4   | Timer4 Modu    | le Register                                                                                               |                  |                 |              |          |       |         | 0000 0000            | 0000 0000                       |

| 416h                | PR4    | Timer4 Perio   | d Register                                                                                                |                  |                 |              |          |       |         | 1111 1111            | 1111 1111                       |

| 417h                | T4CON  | _              |                                                                                                           | T4OUTF           | PS<3:0>         |              | TMR4ON   | T4CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 418h                | _      | Unimplement    | ed                                                                                                        |                  |                 |              | •        |       |         | _                    | _                               |

| 419h                | —      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    |                                 |

| 41Ah                | —      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | —                    | _                               |

| 41Bh                | —      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | —                    | _                               |

| 41Ch                | TMR6   | Timer6 Modu    | le Register                                                                                               |                  |                 |              |          |       |         | 0000 0000            | 0000 0000                       |

| 41Dh                | PR6    | Timer6 Perio   | d Register                                                                                                |                  |                 |              |          |       |         | 1111 1111            | 1111 1111                       |

| 41Eh                | T6CON  | _              |                                                                                                           | T6OUTF           | PS<3:0>         |              | TMR6ON   | T6CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh                | _      | Unimplement    | ed                                                                                                        |                  |                 |              |          |       |         | _                    | _                               |

| l egend.            |        | n 11 = unchang |                                                                                                           | donondo on os    | ndition - ur    | implemented  |          | 4     |         |                      |                                 |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

**3:** PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

© 2010-2015 Microchip Technology Inc.

|                              | 3-9: 5 |                                                                                                           |                                             |                  |                 |              |          |       |       |                      |                                 |

|------------------------------|--------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|-----------------|--------------|----------|-------|-------|----------------------|---------------------------------|

| Address                      | Name   | Bit 7                                                                                                     | Bit 6                                       | Bit 5            | Bit 4           | Bit 3        | Bit 2    | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Banks 9                      | 9-30   |                                                                                                           |                                             |                  |                 |              |          |       |       |                      |                                 |

| x00h/<br>x80h <sup>(1)</sup> |        |                                                                                                           |                                             |                  |                 |              |          |       |       | XXXX XXXX            | XXXX XXXX                       |

| x00h/<br>x81h <sup>(1)</sup> | INDF1  | Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                                             |                  |                 |              |          |       |       | XXXX XXXX            | XXXX XXXX                       |

| x02h/<br>x82h <sup>(1)</sup> | PCL    | Program Cou                                                                                               | inter (PC) Lea                              | st Significant B | yte             |              |          |       |       | 0000 0000            | 0000 0000                       |

| x03h/<br>x83h <sup>(1)</sup> | STATUS | _                                                                                                         | _                                           | —                | TO              | PD           | Z        | DC    | С     | 1 1000               | q quuu                          |

| x04h/<br>x84h <sup>(1)</sup> | FSR0L  | Indirect Data                                                                                             | Memory Addr                                 | ess 0 Low Poir   | nter            |              |          |       |       | 0000 0000            | uuuu uuuu                       |

| x05h/<br>x85h <b>(1)</b>     | FSR0H  | Indirect Data                                                                                             | Indirect Data Memory Address 0 High Pointer |                  |                 |              |          |       |       |                      | 0000 0000                       |

| x06h/<br>x86h <sup>(1)</sup> | FSR1L  | Indirect Data                                                                                             | Indirect Data Memory Address 1 Low Pointer  |                  |                 |              |          |       |       |                      | uuuu uuuu                       |

| x07h/<br>x87h <sup>(1)</sup> | FSR1H  | Indirect Data                                                                                             | Memory Addr                                 | ess 1 High Poi   | nter            |              |          |       |       | 0000 0000            | 0000 0000                       |

| x08h/<br>x88h <b>(1)</b>     | BSR    | —                                                                                                         | _                                           | —                |                 |              | BSR<4:0> |       |       | 0 0000               | 0 0000                          |

| x09h/<br>x89h <sup>(1)</sup> | WREG   | Working Reg                                                                                               | ister                                       |                  |                 |              |          |       |       | 0000 0000            | uuuu uuuu                       |

| x0Ah/<br>x8Ah <sup>(1)</sup> | PCLATH | —                                                                                                         | Write Buffer f                              | or the upper 7   | bits of the Pro | ogram Counte | er       |       |       | -000 0000            | -000 0000                       |

| x0Bh/<br>x8Bh <b>(1)</b>     | INTCON | GIE                                                                                                       | PEIE                                        | TMR0IE           | INTE            | IOCIE        | TMR0IF   | INTF  | IOCIF | 0000 000x            | 0000 000u                       |

| x0Ch/<br>x8Ch                | _      | Unimplemented                                                                                             |                                             |                  |                 |              |          |       |       | _                    | -                               |

| x1Fh/<br>x9Fh                |        |                                                                                                           |                                             |                  |                 |              |          |       |       |                      |                                 |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$Legend: \quad x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

**3:** PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

#### 5.2.1.4 4xPLL

The oscillator module contains a 4xPLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4xPLL must fall within specifications. See the PLL Clock Timing Specifications in **Section 30.0 "Electrical Specifications"**.

The 4xPLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Word 2 to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Word 2 is programmed to a '1', then the value of SPLLEN is ignored.

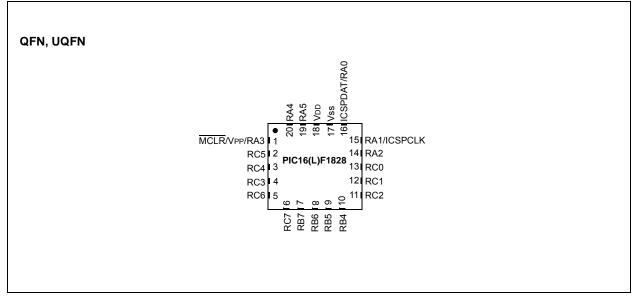

#### 5.2.1.5 TIMER1 Oscillator

The Timer1 Oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 Oscillator can be used as an alternate system clock source and can be selected during run-time using clock switching. Refer to **Section 5.3 "Clock Switching"** for more information.

# FIGURE 5-5: QUARTZ CRYSTAL

OPERATION (TIMER1 OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

#### 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The outputs of the 16 MHz HFINTOSC postscaler and the LFINTOSC connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4xPLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (Default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

- Note: Following any Reset, the IRCF<3:0> bits of the OSCCON register are set to '0111' and the frequency selection is set to 500 kHz. The user can modify the IRCF bits to select a different frequency.

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4xPLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Word 1 must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Word 1 (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Word 2 must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Word 2, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

#### 8.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 9.0 "Power-Down Mode (Sleep)" for more details.

### 8.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

### 8.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the Shadow registers:

- W register

- STATUS register (except for TO and PD)

- · BSR register

- · FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding Shadow register should be modified and the value will be restored when exiting the ISR. The Shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

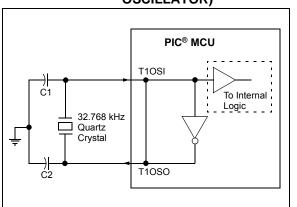

#### FIGURE 13-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM (PORTA EXAMPLE)

| TABLE 16-1: | ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| ADC Clock Period (TAD)        |     |                             | Device Frequency (Fosc)     |                             |                             |                             |                               |  |  |

|-------------------------------|-----|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|--|--|

| ADC<br>Clock Source ADCS<2:0> |     | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                         |  |  |

| Fosc/2                        | 000 | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                        |  |  |

| Fosc/4                        | 100 | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                        |  |  |

| Fosc/8                        | 001 | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>         |  |  |

| Fosc/16                       | 101 | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/32                       | 010 | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(3)</sup>        |  |  |

| Fosc/64                       | 110 | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(3)</sup>      | 64.0 μs <sup>(3)</sup>        |  |  |

| Frc                           | x11 | 1.0-6.0 μs <sup>(1,4)</sup>   |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The FRC source has a typical TAD time of 1.6  $\mu$ s for VDD.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

### 21.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 21-1 displays the Timer1 enable selections.

TABLE 21-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

### 21.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 21-2 displays the clock source selections.

#### 21.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1

gate

- C1 or C2 comparator input to Timer1 gate

#### 21.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T1OSCEN | Clock Source                    |  |  |  |

|---------|---------|---------|---------------------------------|--|--|--|

| 0       | 1       | x       | System Clock (Fosc)             |  |  |  |

| 0       | 0       | x       | Instruction Clock (Fosc/4)      |  |  |  |

| 1       | 1       | x       | Capacitive Sensing Oscillator   |  |  |  |

| 1       | 0       | 0       | External Clocking on T1CKI Pin  |  |  |  |

| 1       | 0       | 1       | Osc.Circuit On T1OSI/T1OSO Pins |  |  |  |

#### TABLE 21-2: CLOCK SOURCE SELECTIONS

© 2010-2015 Microchip Technology Inc.

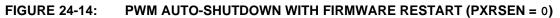

#### 24.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the CCPxAS register. A shutdown event may be generated by:

- A logic '0' on the FLT0 pin

- A logic '1' on a Comparator (Cx) output

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the CCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see **Section 24.4.4 "Auto-restart Mode"**).

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the CCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or FLT0 pin event, a software shutdown can be triggered in firmware by setting the CCPxASE bit of the CCPxAS register to '1'. The Auto-Restart feature tracks the active status of a shutdown caused by a comparator output or FLT0 pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

#### REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-00                  | R/W-0/0                         | R/W-0/0                                                                                                                                                           | R/W-0/0         | R/W-0/0                                  | R/W-0/0            | R/W-0/0            | R/W-0/0         |  |  |  |  |  |  |

|-------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------|--------------------|--------------------|-----------------|--|--|--|--|--|--|

| PxN                     | 1<1:0> <sup>(1)</sup>           | DCxB                                                                                                                                                              | <1:0>           |                                          | CCPx               | vl<3:0>            |                 |  |  |  |  |  |  |

| bit 7                   |                                 |                                                                                                                                                                   |                 |                                          |                    |                    | bit (           |  |  |  |  |  |  |

|                         |                                 |                                                                                                                                                                   |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

| Legend:<br>R = Readable | bit                             | W = Writable bi                                                                                                                                                   | ·               |                                          | ented bit, read as | · 'O'              |                 |  |  |  |  |  |  |

| u = Bit is unch         |                                 | x = Bit is unkno                                                                                                                                                  |                 | •                                        | -                  | /alue at all other | Reset           |  |  |  |  |  |  |

| '1' = Bit is set        | 0                               | '0' = Bit is clear                                                                                                                                                |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 |                                                                                                                                                                   |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

| bit 7-6                 | <b>PxM&lt;1:0&gt;:</b> En       | hanced PWM Ou                                                                                                                                                     | tput Configurat | ion bits <sup>(1)</sup>                  |                    |                    |                 |  |  |  |  |  |  |

|                         | Capture mode:<br>Unused         | Capture mode:                                                                                                                                                     |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | Compare mode                    | <u>e:</u>                                                                                                                                                         |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | Unused                          | _                                                                                                                                                                 |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 | <u>&gt; = 00, 01, 10:</u>                                                                                                                                         | · .             |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 | • ·                                                                                                                                                               | e/Compare inpi  | ıt; PxB, PxC, PxD                        | assigned as poi    | rt pins            |                 |  |  |  |  |  |  |

|                         | If CCPxM<3:2×<br>00 = Single of |                                                                                                                                                                   | lated: PxB. Px  | C, PxD assigned a                        | as port pins       |                    |                 |  |  |  |  |  |  |

|                         | 01 = Full-Bri                   | dge output forwar                                                                                                                                                 | d; PxD modula   | ted; PxA active; P                       | xB, PxC inactive   |                    |                 |  |  |  |  |  |  |

|                         |                                 |                                                                                                                                                                   |                 | with dead-band co<br>ted: PxC active: P  |                    |                    | t pins          |  |  |  |  |  |  |

| bit 5-4                 |                                 | <ul> <li>11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive</li> <li>DCxB&lt;1:0&gt;: PWM Duty Cycle Least Significant bits</li> </ul> |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | Capture mode:                   | Capture mode:                                                                                                                                                     |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | Unused                          |                                                                                                                                                                   |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 | Compare mode:<br>Unused                                                                                                                                           |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 | <u>PWM mode:</u>                                                                                                                                                  |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 | the two LSbs of t                                                                                                                                                 | he PWM duty o   | cycle. The eight M                       | Sbs are found in   | CCPRxL.            |                 |  |  |  |  |  |  |

| bit 3-0                 | CCPxM<3:0>:                     | ECCPx Mode Se                                                                                                                                                     | elect bits      |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | •                               | 0000 = Capture/Compare/PWM off (resets ECCPx module)                                                                                                              |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | 0001 = Rese                     | rved<br>pare mode: toggle                                                                                                                                         | e output on mat | ch                                       |                    |                    |                 |  |  |  |  |  |  |

|                         | 0011 = Rese                     |                                                                                                                                                                   |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | 0100 = Capt                     | ure mode: every f                                                                                                                                                 | alling edge     |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | •                               | ure mode: every r                                                                                                                                                 |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | •                               | ure mode: every 4                                                                                                                                                 | 0 0             |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | 0111 = Captu                    | ure mode: every 1                                                                                                                                                 | 6th rising edge | •                                        |                    |                    |                 |  |  |  |  |  |  |

|                         | 1000 = Comp                     | pare mode: initiali                                                                                                                                               | ze ECCPx pin    | ow; set output on                        | compare match      | (set CCPxIF)       |                 |  |  |  |  |  |  |

|                         |                                 |                                                                                                                                                                   |                 | nigh; clear output                       |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 | •                                                                                                                                                                 |                 | terrupt only; ECCF<br>(ECCPx resets T    | •                  |                    | conversion if A |  |  |  |  |  |  |

|                         |                                 | dule is enabled) <sup>(1</sup>                                                                                                                                    |                 |                                          |                    | ir bit, starts A/D |                 |  |  |  |  |  |  |

|                         | CCP Modules                     | only:                                                                                                                                                             |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | 11xx = PWM                      |                                                                                                                                                                   |                 |                                          |                    |                    |                 |  |  |  |  |  |  |

|                         | ECCP modules                    |                                                                                                                                                                   |                 |                                          | L.                 |                    |                 |  |  |  |  |  |  |

|                         |                                 |                                                                                                                                                                   | -               | kB, PxD active-hig<br>kB, PxD active-lov |                    |                    |                 |  |  |  |  |  |  |

|                         |                                 |                                                                                                                                                                   | •               | B, PxD active-lov                        |                    |                    |                 |  |  |  |  |  |  |

|                         | 1111 = PWM                      | l mode: PxA, PxC                                                                                                                                                  | active-low; Px  | B, PxD active-low                        |                    |                    |                 |  |  |  |  |  |  |

**Note 1:** These bits are not implemented on CCP3 or CCP4.

© 2010-2015 Microchip Technology Inc.

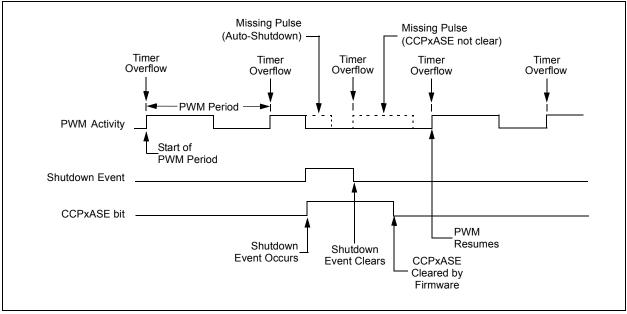

## 25.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- · Serial Data (SDA)

Figure 25-2 and Figure 25-3 shows the block diagram of the MSSP1 module when operating in I<sup>2</sup>C Mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 25-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode

(master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 25-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

### 25.7 Baud Rate Generator

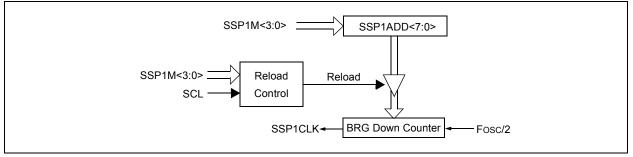

The MSSP1 module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSP1ADD register (Register 25-6). When a write occurs to SSP1BUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 25-40 triggers the value from SSP1ADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP1 is being operated in.

Table 25-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSP1ADD.

#### **EQUATION 25-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

#### FIGURE 25-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSP1ADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### TABLE 25-4: MSSP1 CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical and timing specifications in Table 30-4 and Figure 30-7 to ensure the system is designed to support the I/O requirements.

## 26.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 26.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 26.4.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 26.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP