Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1824-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"**, for more information.

## 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See section **Section 3.4 "Stack"** for more details.

## 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one data pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.5 "Indirect Addressing"** for more details.

## 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0** "Instruction Set Summary" for more details.

## 6.0 REFERENCE CLOCK MODULE

The reference clock module provides the ability to send a divided clock to the clock output pin of the device (CLKR) and provide a secondary internal clock source to the modulator module. This module is available in all oscillator configurations and allows the user to select a greater range of clock sub-multiples to drive external devices in the application. The reference clock module includes the following features:

- System clock is the source

- Available in all oscillator configurations

- · Programmable clock divider

- Output enable to a port pin

- · Selectable duty cycle

- Slew rate control

The reference clock module is controlled by the CLKRCON register (Register 6-1) and is enabled when setting the CLKREN bit. To output the divided clock signal to the CLKR port pin, the CLKROE bit must be set. The CLKRDIV<2:0> bits enable the selection of 8 different clock divider options. The CLKRDC<1:0> bits can be used to modify the duty cycle of the output clock<sup>(1)</sup>. The CLKRSLR bit controls slew rate limiting.

Note 1: If the base clock rate is selected without a divider, the output clock will always have a duty cycle equal to that of the source clock, unless a 0% duty cycle is selected. If the clock divider is set to base clock/2, then 25% and 75% duty cycle accuracy will be dependent upon the source clock.

For information on using the reference clock output with the modulator module, see **Section 23.0 "Data Signal Modulator"**.

## 6.1 Slew Rate

The slew rate limitation on the output port pin can be disabled. The Slew Rate limitation can be removed by clearing the CLKRSLR bit in the CLKRCON register.

### 6.2 Effects of a Reset

Upon any device Reset, the reference clock module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

## 6.3 Conflicts with the CLKR pin

There are two cases when the reference clock output signal cannot be output to the CLKR pin, if:

- LP, XT, or HS oscillator mode is selected.

- CLKOUT function is enabled.

Even if either of these cases are true, the module can still be enabled and the reference clock signal may be used in conjunction with the modulator module.

#### 6.3.1 OSCILLATOR MODES

If LP, XT, or HS oscillator modes are selected, the OSC2/CLKR pin must be used as an oscillator input pin and the CLKR output cannot be enabled. See **Section 5.2 "Clock Source Types"** for more information on different oscillator modes.

#### 6.3.2 CLKOUT FUNCTION

The CLKOUT function has a higher priority than the reference clock module. <u>Therefore</u>, if the CLKOUT function is enabled by the CLKOUTEN bit in Configuration Word 1, FOSC/4 will always be output on the port pin. Reference **Section 4.0** "**Device Configuration**" for more information.

## 6.4 Operation During Sleep

As the reference clock module relies on the system clock as its source, and the system clock is disabled in Sleep, the module does not function in Sleep, even if an external clock source or the Timer1 clock source is configured as the system clock. The module outputs will remain in their current state until the device exits Sleep.

|        |        |        | REGIOTE |       |           |       |       |        |                     |

|--------|--------|--------|---------|-------|-----------|-------|-------|--------|---------------------|

| Name   | Bit 7  | Bit 6  | Bit 5   | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

| BORCON | SBOREN |        |         | _     |           | _     | _     | BORRDY | 77                  |

| PCON   | STKOVF | STKUNF |         | _     | RMCLR     | RI    | POR   | BOR    | 81                  |

| STATUS | _      | _      | _       | TO    | PD        | Z     | DC    | С      | 22                  |

| WDTCON |        | _      |         | V     | VDTPS<4:0 | >     |       | SWDTEN | 101                 |

## TABLE 7-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

| U-0             | U-0                                 | R/W-0/0                                                       | R/W-1/1                            | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |

|-----------------|-------------------------------------|---------------------------------------------------------------|------------------------------------|-----------------|------------------|-----------------|--------------|

| _               |                                     | WDTPS4                                                        | WDTPS3                             | WDTPS2          | WDTPS1           | WDTPS0          | SWDTEN       |

| bit 7           |                                     |                                                               | 1                                  | •               | •                | •               | bit 0        |

|                 |                                     |                                                               |                                    |                 |                  |                 | ,            |

| Legend:         |                                     |                                                               |                                    |                 |                  |                 |              |

| R = Readab      | le bit                              | W = Writable                                                  | bit                                | U = Unimpler    | mented bit, read | d as '0'        |              |

| u = Bit is un   | changed                             | x = Bit is unk                                                | nown                               | -m/n = Value    | at POR and BO    | DR/Value at all | other Resets |

| '1' = Bit is se | et                                  | '0' = Bit is cle                                              | ared                               |                 |                  |                 |              |

|                 |                                     |                                                               |                                    |                 |                  |                 |              |

| bit 7-6         | Unimpleme                           | nted: Read as '                                               | 0'                                 |                 |                  |                 |              |

| bit 5-1         | WDTPS<4:0                           | )>: Watchdog Ti                                               | imer Period Se                     | elect bits      |                  |                 |              |

|                 | Bit Value =                         | Prescale Rate                                                 |                                    |                 |                  |                 |              |

|                 |                                     | 32 (Interval 1 m                                              |                                    |                 |                  |                 |              |

|                 |                                     | 64 (Interval 2 m<br>128 (Interval 4                           |                                    |                 |                  |                 |              |

|                 |                                     | 256 (Interval 8                                               | 21 /                               |                 |                  |                 |              |

|                 | 00100 = <b>1</b> :                  | 512 (Interval 16                                              | 6 ms typ)                          |                 |                  |                 |              |

|                 |                                     | 1024 (Interval 3                                              |                                    |                 |                  |                 |              |

|                 |                                     | 2048 (Interval 6<br>4096 (Interval 1                          |                                    |                 |                  |                 |              |

|                 |                                     | 8192 (Interval 2                                              | <b>21</b>                          |                 |                  |                 |              |

|                 |                                     | 16384 (Interval                                               |                                    |                 |                  |                 |              |

|                 |                                     | 32768 (Interval 65536 (Interva                                |                                    | at value)       |                  |                 |              |

|                 | 01100 = <b>1</b> :                  | $131072(2^{17})$ (h                                           | nterval 4s tvp)                    |                 |                  |                 |              |

|                 | 01101 = <b>1</b> :                  | 262144 (2 <sup>18</sup> ) (li                                 | nterval 8s tvp)                    |                 |                  |                 |              |

|                 | 01110 = 1:                          | 524288 (2 <sup>19</sup> ) (li<br>1048576 (2 <sup>20</sup> ) ( | nterval 16s typ                    | ))<br>)         |                  |                 |              |

|                 | 10000 = 1                           | 2097152 (2 <sup>21</sup> ) (                                  | Interval 32s ty<br>Interval 64s ty | (p)             |                  |                 |              |

|                 | 10001 = 1:                          | 4194304 (2 <sup>22</sup> ) (                                  | Interval 128s                      | typ)            |                  |                 |              |

|                 | 10010 = <b>1</b> :                  | 8388608 (2 <sup>23</sup> ) (                                  | Interval 256s                      | typ)            |                  |                 |              |

|                 | 10011 = R                           | eserved. Result                                               | s in minimum                       | interval (1·32) |                  |                 |              |

|                 | •                                   |                                                               |                                    |                 |                  |                 |              |

|                 | •                                   |                                                               |                                    |                 |                  |                 |              |

|                 | •<br>11111 - P                      | eserved. Result                                               | e in minimum                       | interval (1.32) |                  |                 |              |

| bit 0           |                                     | Software Enable                                               |                                    | ( )             | bit              |                 |              |

| bit 0           | If WDTE<1:                          |                                                               |                                    | atchoog miner   | bit              |                 |              |

|                 | This bit is ig                      |                                                               |                                    |                 |                  |                 |              |

|                 | If WDTE<1:0                         |                                                               |                                    |                 |                  |                 |              |

|                 | 1 = WDT is<br>0 = WDT is            |                                                               |                                    |                 |                  |                 |              |

|                 | 0 = WDT IS<br><u>If WDTE&lt;1:(</u> |                                                               |                                    |                 |                  |                 |              |

|                 | This bit is ig                      |                                                               |                                    |                 |                  |                 |              |

|                 |                                     |                                                               |                                    |                 |                  |                 |              |

## REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

| ; This               | write rout  | ine assumes the f | following:                                                 |

|----------------------|-------------|-------------------|------------------------------------------------------------|

| ; 1. Tł              | ne 16 bytes | of data are load  | led, starting at the address in DATA_ADDR                  |

| ; 2. Ea              | ach word of | data to be writt  | en is made up of two adjacent bytes in DATA_ADDR,          |

| ; st                 | tored in li | ttle endian forma | at                                                         |

| ; 3. A               | valid star  | ting address (the | e least significant bits = 000) is loaded in ADDRH:ADDRL   |

|                      |             |                   | in shared data memory 0x70 - 0x7F                          |

| ;                    |             |                   | -                                                          |

|                      | BCF         | INTCON,GIE        | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL     | EEADRH            | ; Bank 3                                                   |

|                      | MOVF        | ADDRH,W           | ; Load initial address                                     |

|                      | MOVWF       | EEADRH            | ;                                                          |

|                      | MOVF        | ADDRL,W           | ;                                                          |

|                      | MOVWF       | EEADRL            | ;                                                          |

|                      | MOVLW       |                   | ; Load initial data address                                |

|                      | MOVWF       | FSROL             | ;                                                          |

|                      | MOVLW       |                   | ; Load initial data address                                |

|                      | MOVWF       | FSROH             | ;                                                          |

|                      | BSF         | EECON1, EEPGD     | ; Point to program memory                                  |

|                      | BCF         |                   | ; Not configuration space                                  |

|                      | BSF         | EECON1, WREN      | ; Enable writes                                            |

|                      | BSF         | EECON1,LWLO       | ; Only Load Write Latches                                  |

| LOOP                 |             |                   |                                                            |

|                      | MOVIW       | FSR0++            | ; Load first data byte into lower                          |

|                      | MOVWF       | EEDATL            | ;                                                          |

|                      | MOVIW       | FSR0++            | ; Load second data byte into upper                         |

|                      | MOVWF       | EEDATH            | ;                                                          |

|                      |             |                   |                                                            |

|                      | MOVF        | EEADRL,W          | ; Check if lower bits of address are '000'                 |

|                      | XORLW       | 0x07              | ; Check if we're on the last of 8 addresses                |

|                      | ANDLW       | 0x07              | ;                                                          |

|                      | BTFSC       | STATUS, Z         | ; Exit if last of eight words,                             |

|                      | GOTO        | START_WRITE       | ;                                                          |

|                      |             | ~                 |                                                            |

|                      | MOVLW       | 55h               | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2            | ; Write 55h                                                |

| _ n                  | MOVLW       | 0AAh              | ;                                                          |

| Required<br>Sequence | MOVWF       | EECON2            | ; Write AAh                                                |

| qui                  | BSF         | EECON1,WR         | ; Set WR bit to begin write                                |

| sec de               | NOP         |                   | ; Any instructions here are ignored as processor           |

| - 07                 |             |                   | ; halts to begin write sequence                            |

|                      | NOP         |                   | ; Processor will stop here and wait for write to complete. |

|                      |             |                   |                                                            |

|                      |             |                   | ; After write processor continues with 3rd instruction.    |

|                      |             |                   |                                                            |

|                      | INCF        | EEADRL, F         | ; Still loading latches Increment address                  |

|                      | GOTO        | LOOP              | ; Write next latches                                       |

|                      |             |                   |                                                            |

| START_V              | WRITE       |                   |                                                            |

|                      | BCF         | EECON1,LWLO       | ; No more loading latches - Actually start Flash program   |

|                      |             |                   | ; memory write                                             |

|                      |             |                   |                                                            |

|                      | MOVLW       | 55h               | ; Start of required write sequence:                        |

|                      | MOVWF       | EECON2            | ; Write 55h                                                |

| Se Sd                | MOVLW       | 0AAh              | ;                                                          |

| uire                 | MOVWF       | EECON2            | ; Write AAh                                                |

| Required<br>Sequence | BSF         | EECON1,WR         | ; Set WR bit to begin write                                |

| ъÑ                   | NOP         |                   | ; Any instructions here are ignored as processor           |

|                      |             |                   | ; halts to begin write sequence                            |

|                      | NOP         |                   | ; Processor will stop here and wait for write complete.    |

| L                    |             |                   |                                                            |

|                      |             |                   | ; after write processor continues with 3rd instruction     |

|                      | BCF         | EECON1, WREN      | ; Disable writes                                           |

|                      | BSF         | INTCON,GIE        | ; Enable interrupts                                        |

|                      |             |                   |                                                            |

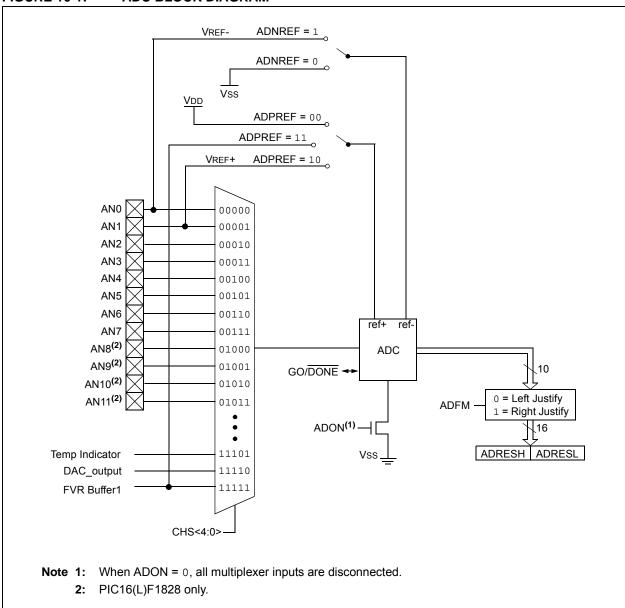

## 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

### FIGURE 16-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

#### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (sync\_C1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (sync\_C2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 19.4.1 "Comparator Output Synchronization"**.

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 Gate source to be measured. See Figure 21-6 for timing details.

### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 Gate is not enabled (TMR1GE bit is cleared).

#### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

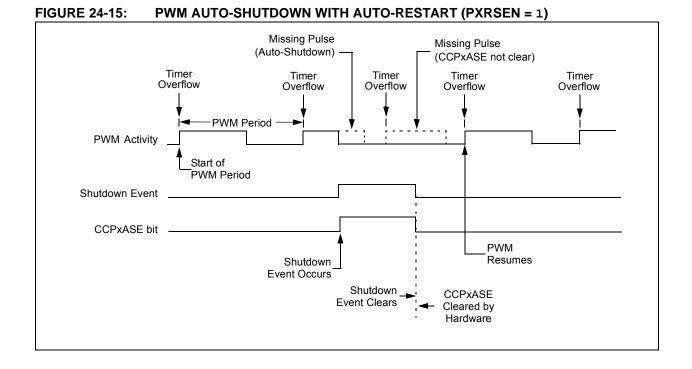

## 24.4.4 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit in the PWMxCON register. If auto-restart is enabled, the CCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the CCPxASE bit will be cleared via hardware and normal operation will resume.

| Name     | Bit 7                  | Bit 6                  | Bit 5      | Bit 4    | Bit 3     | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|------------------------|------------------------|------------|----------|-----------|---------|---------|---------|---------------------|

| APFCON1  | _                      | _                      | _          | _        | P1DSEL    | P1CSEL  | P2BSEL  | CCP2SEL | 118                 |

| CCPxCON  | PxM<                   | 1:0> <b>(1)</b>        | DCxE       | 8<1:0>   |           | CCPx    | N<3:0>  |         | 225                 |

| CCPxAS   | CCPxASE                | (                      | CCPxAS<2:0 | >        | PSSxA     | C<1:0>  | PSSxB   | D<1:0>  | 227                 |

| CCPTMRS0 | C4TSE                  | L<1:0>                 | C3TSE      | L<1:0>   | C2TSE     | L<1:0>  | C1TSE   | EL<1:0> | 226                 |

| INLVLA   | —                      | _                      | INLVLA5    | INLVLA4  | INLVLA3   | INLVLA2 | INLVLA1 | INLVLA0 | 123                 |

| INLVLC   | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5    | INLVLC4  | INLVLC3   | INLVLC2 | INLVLC1 | INLVLC0 | 134                 |

| INTCON   | GIE                    | PEIE                   | TMR0IE     | INTE     | IOCIE     | TMR0IF  | INTF    | IOCIF   | 89                  |

| PIE1     | TMR1GIE                | ADIE                   | RCIE       | TXIE     | SSP1IE    | CCP1IE  | TMR2IE  | TMR1IE  | 90                  |

| PIE2     | OSFIE                  | C2IE                   | C1IE       | EEIE     | BCLIE     | _       | —       | CCP2IE  | 91                  |

| PIE3     | —                      | _                      | CCP4IE     | CCP3IE   | TMR6IE    | _       | TMR4IE  | —       | 92                  |

| PIR1     | TMR1GIF                | ADIF                   | RCIF       | TXIF     | SSP1IF    | CCP1IF  | TMR2IF  | TMR1IF  | 93                  |

| PIR2     | OSFIF                  | C2IF                   | C1IF       | EEIF     | BCLIF     | _       | —       | CCP2IF  | 94                  |

| PIR3     | —                      | _                      | CCP4IF     | CCP3IF   | TMR6IF    | _       | TMR4IF  | —       | 95                  |

| PRx      | Timer2/4/6 P           | eriod Registe          | er         |          |           |         |         |         | 189*                |

| PSTRxCON | —                      | _                      | —          | STRxSYNC | STRxD     | STRxC   | STRxB   | STRxA   | 229                 |

| PWMxCON  | PxRSEN                 |                        |            |          | PxDC<6:0> |         |         |         | 228                 |

| TxCON    | —                      |                        | TxOUT      | PS<3:0>  |           | TMRxON  | TxCKP   | 'S<:0>1 | 191                 |

| TRISA    | _                      | -                      | TRISA5     | TRISA4   | TRISA3    | TRISA2  | TRISA1  | TRISA0  | 121                 |

| TRISC    | TRISC7 <sup>(2)</sup>  | TRISC6 <sup>(2)</sup>  | TRISC5     | TRISC4   | TRISC3    | TRISC2  | TRISC1  | TRISC0  | 132                 |

### TABLE 24-10: SUMMARY OF REGISTERS ASSOCIATED WITH ENHANCED PWM

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

**Note 1:** Applies to ECCP modules only.

2: PIC16(L)F1828 only.

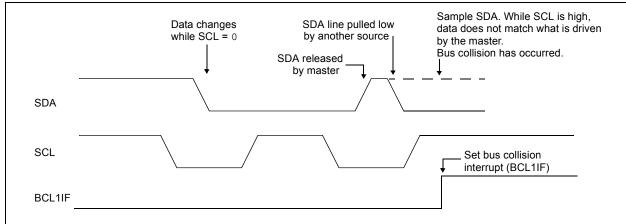

#### FIGURE 25-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

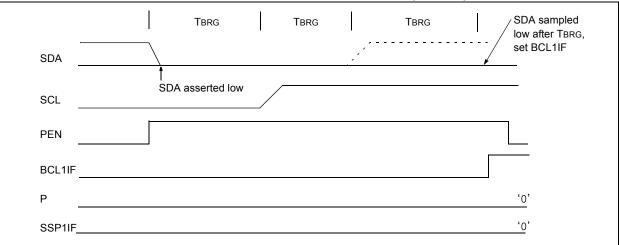

#### 25.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 25-33).

- b) SCL is sampled low before SDA is asserted low (Figure 25-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCL1IF flag is set and

- the MSSP1 module is reset to its Idle state (Figure 25-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 25-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

**Note:** The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

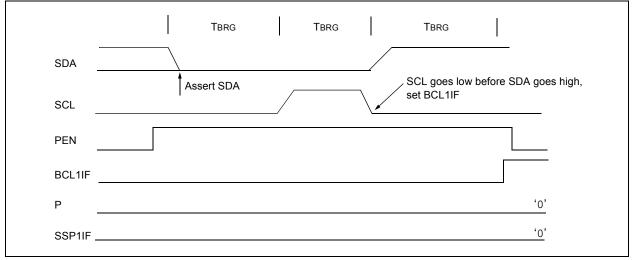

#### 25.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSP1ADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 25-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 25-39).

### FIGURE 25-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 25-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

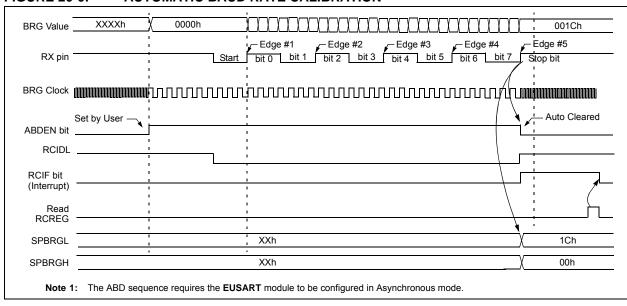

#### 26.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 26-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 26-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 26-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 26.3.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| TABLE 26-6:BRG COUNTER CLOCK RATES |

|------------------------------------|

|------------------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

### FIGURE 26-6: AUTOMATIC BAUD RATE CALIBRATION

## 26.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

#### 26.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 26-7), and asynchronously if the device is in Sleep mode (Figure 26-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 26.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

### TABLE 30-6: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|              | ng Temperatur | e -40°C ≤ IA∶<br>I        | ≤ +125°C                    |                                                             | Γ            |        |        | l     |                                    |

|--------------|---------------|---------------------------|-----------------------------|-------------------------------------------------------------|--------------|--------|--------|-------|------------------------------------|

| Param<br>No. | Sym.          |                           | Characteristic              |                                                             | Min.         | Тур†   | Max.   | Units | Conditions                         |

| 40*          | T⊤0H          | T0CKI High F              | Pulse Width                 | ulse Width No Prescaler                                     |              | _      | -      | ns    |                                    |

|              |               |                           |                             | With Prescaler                                              | 10           | _      |        | ns    |                                    |

| 41*          | T⊤0L          | T0CKI Low P               | ulse Width                  | No Prescaler                                                | 0.5 Tcy + 20 | —      |        | ns    |                                    |

|              |               |                           |                             | With Prescaler                                              | 10           | —      | _      | ns    |                                    |

| 42*          | TT0P          | T0CKI Period              | l                           |                                                             |              | -      | —      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H          | T1CKI High                | Synchronous, No Prescaler   |                                                             | 0.5 Tcy + 20 | —      |        | ns    |                                    |

|              |               | Time                      | Synchronous, with Prescaler |                                                             | 15           | —      | _      | ns    |                                    |

|              |               |                           | Asynchronous                |                                                             | 30           | _      |        | ns    |                                    |

| 46*          | T⊤1L          | T1CKI Low                 | Synchronous, I              | No Prescaler                                                | 0.5 Tcy + 20 | —      |        | ns    |                                    |

|              |               | Time                      | Synchronous, v              | with Prescaler                                              | 15           | —      | _      | ns    |                                    |

|              |               |                           | Asynchronous                |                                                             | 30           | _      |        | ns    |                                    |

| 47*          | TT1P          | T1CKI Input<br>Period     | Synchronous                 | Synchronous 3                                               |              |        | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |               |                           | Asynchronous                |                                                             | 60           | _      |        | ns    |                                    |

| 48           | FT1           |                           |                             | ator Input Frequency Range<br>abled by setting bit T1OSCEN) |              | 32.768 | 33.1   | kHz   |                                    |

| 49*          | TCKEZTMR1     | Delay from E<br>Increment | xternal Clock E             | dge to Timer                                                | 2 Tosc       | _      | 7 Tosc | —     | Timers in Sync<br>mode             |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwi

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

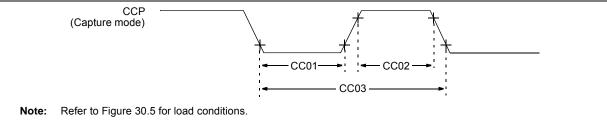

### FIGURE 30-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

## TABLE 30-7: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

|              | Standard Operating Conditions (unless otherwise stated)Dperating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                     |                |                       |      |       |            |                    |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|---------------------|----------------|-----------------------|------|-------|------------|--------------------|--|--|--|--|

| Param<br>No. | Sym.                                                                                                                 | Characteris         | Min.           | Тур†                  | Max. | Units | Conditions |                    |  |  |  |  |

| CC01*        | TccL                                                                                                                 | CCP Input Low Time  | No Prescaler   | 0.5Tcy + 20           | _    | —     | ns         |                    |  |  |  |  |

|              |                                                                                                                      |                     | With Prescaler | 20                    | _    | _     | ns         |                    |  |  |  |  |

| CC02*        | ТссН                                                                                                                 | CCP Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | _     | ns         |                    |  |  |  |  |

|              |                                                                                                                      |                     | With Prescaler | 20                    | _    | _     | ns         |                    |  |  |  |  |

| CC03*        | TccP                                                                                                                 | CCP Input Period    |                | <u>3Tcy + 40</u><br>N | _    | —     | ns         | N = prescale value |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

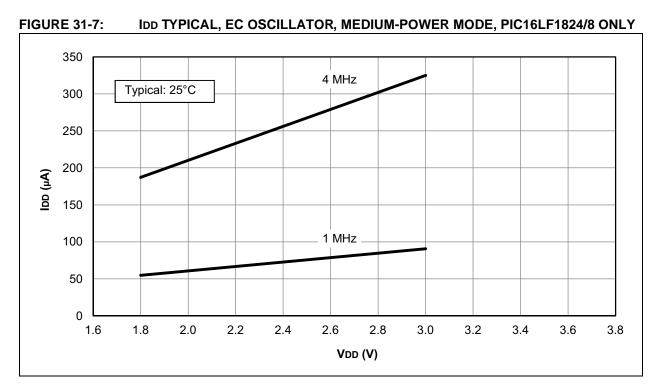

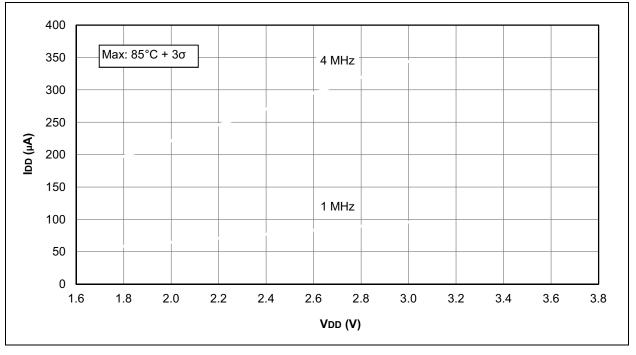

FIGURE 31-8: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1824/8 ONLY

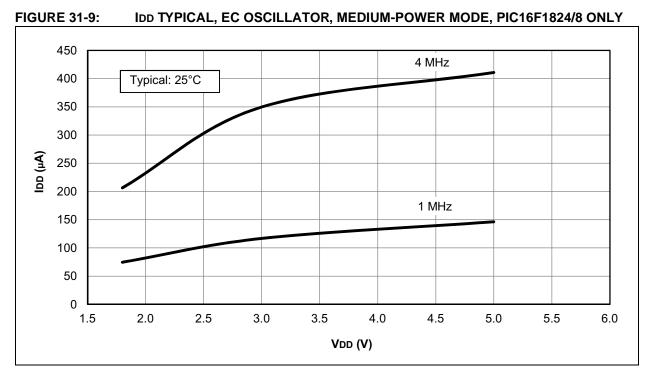

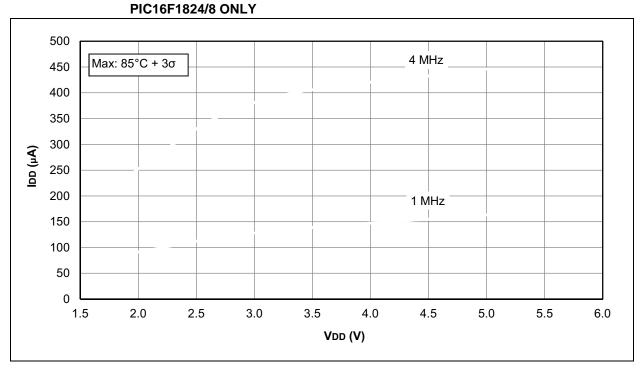

FIGURE 31-10: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE,

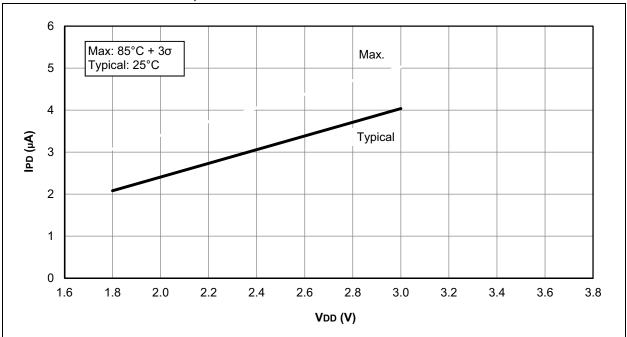

FIGURE 31-31: IPD, CAPACITIVE SENSING (CPS) MODULE, LOW-CURRENT RANGE, CPSRM = 0, PIC16LF1824/8 ONLY

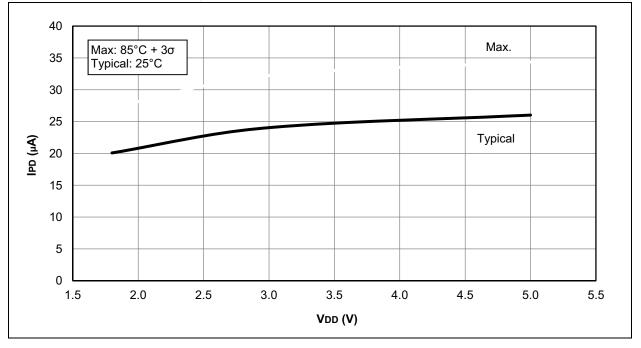

FIGURE 31-32: IPD, CAPACITIVE SENSING (CPS) MODULE, LOW-CURRENT RANGE, CPSRM = 0, PIC16F1824/8 ONLY

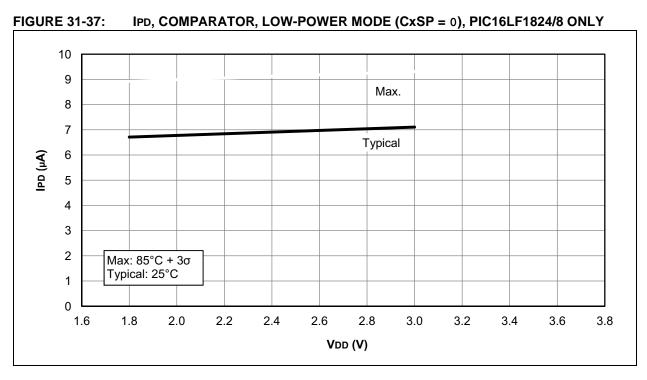

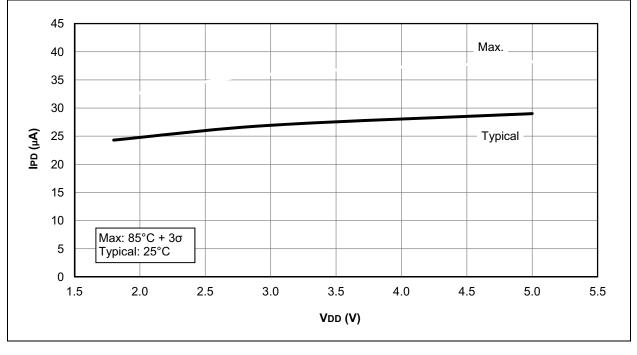

FIGURE 31-38: IPD, COMPARATOR, LOW-POWER MODE (CxSP = 0), PIC16F1824/8 ONLY

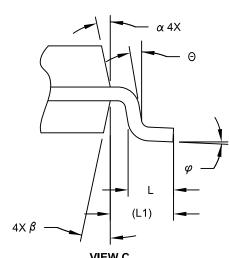

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| v | • | - | v | a. | C |  |

|---|---|---|---|----|---|--|

|   |   |   |   |    |   |  |

|   |   |   |   |    |   |  |

|                          | Units     | l N  | <b>ILLIMETER</b> | s    |

|--------------------------|-----------|------|------------------|------|

| Dimension Lin            | nits      | MIN  | NOM              | MAX  |

| Number of Pins           | N         |      | 14               |      |

| Pitch                    | е         |      | 1.27 BSC         |      |

| Overall Height           | A         | -    | -                | 1.75 |

| Molded Package Thickness | A2        | 1.25 | -                | -    |

| Standoff §               | A1        | 0.10 | -                | 0.25 |

| Overall Width            | E         |      | 6.00 BSC         |      |

| Molded Package Width     | E1        |      | 3.90 BSC         |      |

| Overall Length           | D         |      | 8.65 BSC         |      |

| Chamfer (Optional)       | h         | 0.25 | -                | 0.50 |

| Foot Length              | L         | 0.40 | -                | 1.27 |

| Footprint                | L1        |      | 1.04 REF         |      |

| Lead Angle               | Θ         | 0°   | -                | -    |

| Foot Angle               | $\varphi$ | 0°   | -                | 8°   |

| Lead Thickness           | С         | 0.10 | -                | 0.25 |

| Lead Width               | b         | 0.31 | -                | 0.51 |

| Mold Draft Angle Top     | α         | 5°   | -                | 15°  |

| Mold Draft Angle Bottom  | β         | 5°   | -                | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

## 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units    |      |           |      |

|-------------------------|----------|------|-----------|------|

| Dimensio                | n Limits | MIN  | NOM       | MAX  |

| Number of Terminals     | Ν        |      | 20        |      |

| Pitch                   | е        |      | 0.50 BSC  |      |

| Overall Height          | Α        | 0.45 | 0.50      | 0.55 |

| Standoff                | A1       | 0.00 | 0.02      | 0.05 |

| Terminal Thickness      | A3       |      | 0.127 REF |      |

| Overall Width           | E        |      | 4.00 BSC  | _    |

| Exposed Pad Width       | E2       | 2.60 | 2.70      | 2.80 |

| Overall Length          | D        |      | 4.00 BSC  |      |

| Exposed Pad Length      | D2       | 2.60 | 2.70      | 2.80 |

| Terminal Width          | b        | 0.20 | 0.25      | 0.30 |

| Terminal Length         | L        | 0.30 | 0.40      | 0.50 |

| Terminal-to-Exposed-Pad | K        | 0.20 | -         | -    |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2