Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1824-e-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

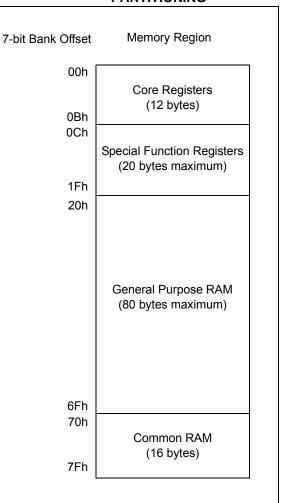

# 3.2.2 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

# 3.2.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh)

#### 3.2.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.5.2** "**Linear Data Memory**" for more information.

#### 3.2.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

# 3.2.5 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-3.

#### TABLE 3-3: MEMORY MAP TABLES

| Device        | Banks | Table No. |

|---------------|-------|-----------|

| PIC16(L)F1824 | 0-7   | Table 3-4 |

| PIC16(L)F1828 | 8-15  | Table 3-5 |

|               | 16-23 | Table 3-6 |

|               | 24-31 | Table 3-7 |

|               | 31    | Table 3-8 |

# 5.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

# 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources

The oscillator module can be configured in one of eight clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC).

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz).

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Word 1. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high frequency clock sources, designated LFINTOSC, MFINTOSC, and HFINTOSC. (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

#### 8.5.4 PIE3 REGISTER

The PIE3 register contains the interrupt enable bits, as shown in Register 8-4.

**Note 1:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 8-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | U-0   |

|-------|-----|---------|---------|---------|-----|---------|-------|

| —     | —   | CCP4IE  | CCP3IE  | TMR6IE  | —   | TMR4IE  | —     |

| bit 7 |     |         |         |         |     |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                     |

|---------|------------------------------------------------|

| bit 5   | CCP4IE: CCP4 Interrupt Enable bit              |

|         | 1 = Enables the CCP4 interrupt                 |

|         | 0 = Disables the CCP4 interrupt                |

| bit 4   | CCP3IE: CCP3 Interrupt Enable bit              |

|         | <ol> <li>Enables the CCP3 interrupt</li> </ol> |

|         | 0 = Disables the CCP3 interrupt                |

| bit 3   | TMR6IE: TMR6 to PR6 Match Interrupt Enable bit |

|         | 1 = Enables the TMR6 to PR6 Match interrupt    |

|         | 0 = Disables the TMR6 to PR6 Match interrupt   |

| bit 2   | Unimplemented: Read as '0'                     |

| bit 1   | TMR4IE: TMR4 to PR4 Match Interrupt Enable bit |

|         | 1 = Enables the TMR4 to PR4 Match interrupt    |

|         | 0 = Disables the TMR4 to PR4 Match interrupt   |

| bit 0   | Unimplemented: Read as '0'                     |

|         |                                                |

#### 8.5.5 PIR1 REGISTER

The PIR1 register contains the interrupt flag bits, as shown in Register 8-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 8-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-------|-------|---------|---------|---------|---------|

| TMR1GIF | ADIF    | RCIF  | TXIF  | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  |

| bit 7   |         |       |       |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | TMR1GIF: Timer1 Gate Interrupt Flag bit                   |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                    |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 5 | RCIF: USART Receive Interrupt Flag bit                    |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 4 | TXIF: USART Transmit Interrupt Flag bit                   |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 3 | SSP1IF: Synchronous Serial Port (MSSP) Interrupt Flag bit |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit                           |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit                  |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                |

|       | 1 = Interrupt is pending                                  |

|       | 0 = Interrupt is not pending                              |

|       |                                                           |

# REGISTER 12-2: APFCON1: ALTERNATE PIN FUNCTION CONTROL REGISTER 1

| U-0                                                                                           | U-0                              | U-0                | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------------------------------------------------------------|----------------------------------|--------------------|-----|---------|---------|---------|---------|--|

| _                                                                                             | _                                | _                  | _   | P1DSEL  | P1CSEL  | P2BSEL  | CCP2SEL |  |

| bit 7                                                                                         |                                  |                    |     |         |         |         | bit 0   |  |

|                                                                                               |                                  |                    |     |         |         |         |         |  |

| Legend:                                                                                       |                                  |                    |     |         |         |         |         |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                          |                                  |                    |     |         |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                                  |                    |     |         |         |         |         |  |

| '1' = Bit is set                                                                              |                                  | '0' = Bit is clear | ed  |         |         |         |         |  |

|                                                                                               |                                  |                    |     |         |         |         |         |  |

| bit 7-4                                                                                       | t 7-4 Unimplemented: Read as '0' |                    |     |         |         |         |         |  |

| bit 3                                                                                         | P1DSEL: Pin S                    | Selection          |     |         |         |         |         |  |

|                                                                                               |                                  | tion is on RC2     |     |         |         |         |         |  |

|                                                                                               | 1 = P1D func                     | tion is on RC0     |     |         |         |         |         |  |

| bit 2                                                                                         | P1CSEL: Pin S                    |                    |     |         |         |         |         |  |

|                                                                                               |                                  | tion is on RC3     |     |         |         |         |         |  |

|                                                                                               |                                  | tion is on RC1     |     |         |         |         |         |  |

| bit 1                                                                                         | P2BSEL: Pin S                    |                    |     |         |         |         |         |  |

|                                                                                               |                                  | tion is on RC2     |     |         |         |         |         |  |

|                                                                                               | 1 = P2B func                     | tion is on RA4     |     |         |         |         |         |  |

| bit 0                                                                                         | CCP2SEL: Pin                     | Selection          |     |         |         |         |         |  |

|                                                                                               |                                  | A function is on   |     |         |         |         |         |  |

|                                                                                               | 1 = CCP2/P2                      | 2A function is on  | RA5 |         |         |         |         |  |

#### **REGISTER 12-9: PORTB: PORTB REGISTER**

| R/W-x/u                                 | R/W-x/u | R/W-x/u      | R/W-x/u | U-0                                                   | U-0 | U-0 | U-0   |  |

|-----------------------------------------|---------|--------------|---------|-------------------------------------------------------|-----|-----|-------|--|

| RB7                                     | RB6     | RB5          | RB4     | —                                                     | —   | —   | —     |  |

| bit 7                                   |         | ·            |         |                                                       |     |     | bit 0 |  |

|                                         |         |              |         |                                                       |     |     |       |  |

| Legend:                                 |         |              |         |                                                       |     |     |       |  |

| R = Readable                            | bit     | W = Writable | bit     | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is unchanged x = Bit is unknown |         |              | nown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| '1' = Bit is set '0' = Bit is cleared   |         |              |         |                                                       |     |     |       |  |

|                                         |         |              |         |                                                       |     |     |       |  |

| bit 7-4 | <b>RB&lt;7:4&gt;</b> : PORTB General Purpose I/O Pin bits |

|---------|-----------------------------------------------------------|

|         | 1 = Port pin is > Vін                                     |

|         | 0 = Port pin is < VIL                                     |

| bit 3-0 | Unimplemented: Read as '0'                                |

#### REGISTER 12-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| ol bits        |

|----------------|

| t (tri-stated) |

| out            |

| ``             |

bit 3-0 Unimplemented: Read as '0'

# REGISTER 12-11: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| LATB7   | LATB6   | LATB5   | LATB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | LATB<7:4>: PORTB Output Latch Value bits <sup>(1)</sup> |

|---------|---------------------------------------------------------|

|---------|---------------------------------------------------------|

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

# 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |  |  |  |  |  |  |

|       | Refer to Section 16.2.6 "A/D Conver-     |  |  |  |  |  |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |  |  |  |  |  |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

# 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

# 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | CCPx/ECCPx |  |  |  |

|-----------------|------------|--|--|--|

| PIC16(L)F1824/8 | CCP4       |  |  |  |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 24.0** "Capture/Compare/PWM **Modules**" for more information.

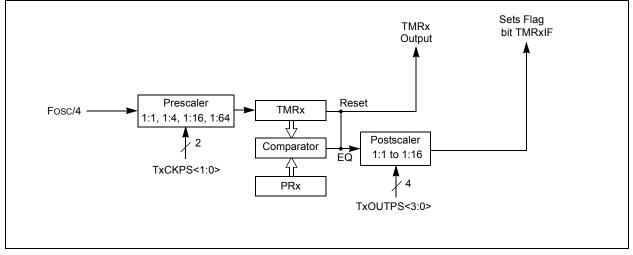

# 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is<br>used to designate Timer2, Timer4, or<br>Timer6. For example, TxCON references |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | T2CON, T4CON, or T6CON. PRx references PR2, PR4, or PR6.                                                                  |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSPx modules (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

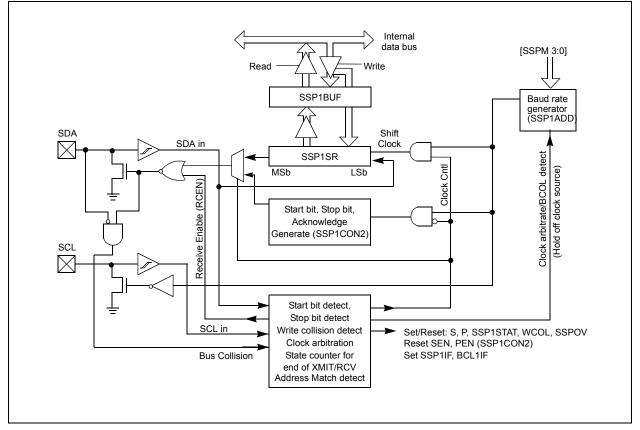

The  $I^2C$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- · Selectable SDA hold times

Figure 25-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 25-3 is a diagram of the  $I^2C$  interface module in Slave mode.

# FIGURE 25-2: MSSP1 BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

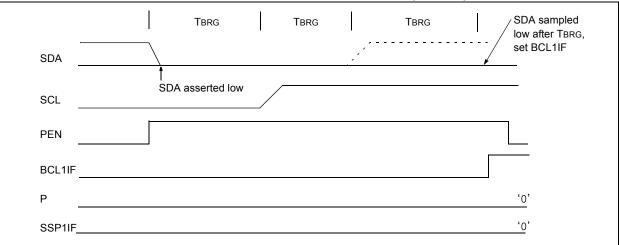

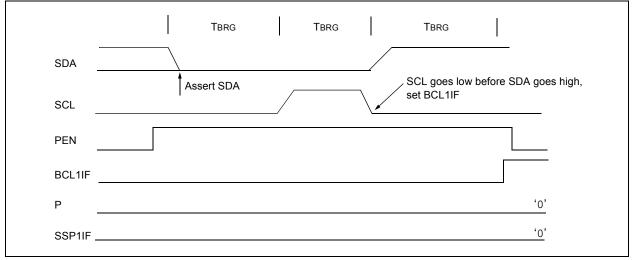

#### 25.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSP1ADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 25-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 25-39).

# FIGURE 25-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

# FIGURE 25-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 26.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 26.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

# 26.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

26.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

# 26.4.1.4 Synchronous Master Transmission Setup:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

# FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-c        | oriented file                                | regi<br>8 | ister o<br>7 | ope<br>6 | erat       | ions    |           | 0    |

|---------------|----------------------------------------------|-----------|--------------|----------|------------|---------|-----------|------|

|               | PCODE                                        | -         | d            | Ē        |            | f (FII  | _E #)     |      |

| Ċ             | = 0 for des<br>= 1 for des<br>= 7-bit file r | tinati    | on f         |          | ss         |         |           |      |

| Bit-ori<br>13 | ented file r                                 | -         | ter op<br>9  | era<br>7 |            |         |           | 0    |

|               | OPCODE                                       |           | b (Bl        | T #      | <b>#</b> ) | f (F    | ILE #)    |      |

|               | e = 3-bit bit a<br>= 7-bit file r            |           |              | dre      | SS         |         |           |      |

| Litera        | and contro                                   | ol op     | eratio       | ons      | 5          |         |           |      |

| Gener         | al                                           |           |              |          |            |         |           |      |

| 13            |                                              |           | 8            | 7        |            |         |           | 0    |

|               | OPCODE                                       |           |              |          |            | k (lit  | eral)     |      |

| k             | = 8-bit imm                                  | edia      | te val       | ue       |            |         |           |      |

| CALL a        | and Goto in                                  | struc     | tions        | onl      | у          |         |           |      |

| 13            | 11                                           | 10        |              |          |            |         |           | 0    |

| (             | PCODE                                        |           |              | k        | k (lit     | eral)   |           |      |

|               | = 11-bit imr                                 |           |              | 7        | 6          |         |           | 0    |

| 15            | OPCODE                                       |           |              | <u>/</u> |            | k (lite | eral)     | 0    |

|               | = 7-bit imm                                  |           | te val       | ue       | <u> </u>   |         |           |      |

| MOVLE         | instruction                                  | only      |              |          | 5          | 4       |           | 0    |

|               | OPCODE                                       |           |              |          |            | k       | (literal) | )    |

|               | = 5-bit imm                                  |           | te valı      | ue       |            |         |           |      |

| BRA in<br>13  | struction on                                 | ly        | 98           | ,        |            |         |           | 0    |

| 15            | OPCODE                                       |           | 3 0          | ,        |            | k (lit  | eral)     | 0    |

| Lk            | x = 9-bit imm                                | nedia     | te val       | ue       |            |         | ,         |      |

| FSR C         | Offset instruc                               | ctions    | 6            |          |            |         |           |      |

| 13            | 000005                                       |           | 7            | 6        | 5          |         | /!·/ I)   | 0    |

|               | OPCODE                                       |           |              | n        |            | K       | (literal) |      |

|               | n = appropri<br>k = 6-bit imn                |           |              | ue       |            |         |           |      |

| fsr In<br>13  | crement ins                                  | tructi    | ions         |          |            | 32      | 1         | 0    |

|               | OPCODE                                       |           |              |          |            | n       | m (m      | ode) |

|               | n = appropri<br>n = 2-bit mo                 |           |              |          |            |         |           |      |

|               | DE only                                      |           |              |          |            |         |           | 0    |

| 13            |                                              | ~         | OPCO         |          | -          |         |           | 0    |

|               |                                              | C         |              | יטכ      | -          |         |           |      |

|              |        |                                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |        |            |                                               |  |

|--------------|--------|-------------------------------------------------------------------------|------------------------------------------------------|------|--------|------------|-----------------------------------------------|--|

| Param<br>No. | Sym.   | Characteristic                                                          | Min.                                                 | Max. | Units  | Conditions |                                               |  |

|              |        | Program Memory High Voltage<br>Programming Specifications               |                                                      |      |        |            |                                               |  |

| D110         | Vінн   | Voltage on MCLR/VPP/RA5 pin                                             | 8.0                                                  | _    | 9.0    | V          | (Note 3, 4)                                   |  |

| D111         | IDDVPP | Programming/Erase Current on VPP,<br>High Voltage Programming           | _                                                    | —    | 10     | mA         |                                               |  |

| D112         | VBE    | VDD for Bulk Erase                                                      | 2.7                                                  | _    | VDDMAX | V          |                                               |  |

| D113         | VPEW   | VDD for Write or Row Erase                                              | VDDMIN                                               | —    | VDDMAX | V          |                                               |  |

| D114         | IPPPGM | Programming/Erase Current on VPP,<br>Low Voltage Programming            | —                                                    | 1.0  | _      | mA         |                                               |  |

| D115         | IDDPGM | Programming/Erase Current on VDD,<br>High or Low Voltage<br>Programming | _                                                    | 5.0  | _      | mA         |                                               |  |

|              |        | Data EEPROM Memory                                                      |                                                      |      |        |            |                                               |  |

| D116         | ED     | Byte Endurance                                                          | 100K                                                 | —    | _      | E/W        | -40°C to +85°C                                |  |

| D117         | Vdrw   | VDD for Read/Write                                                      | VDDMIN                                               | —    | VDDMAX | V          |                                               |  |

| D118         | TDEW   | Erase/Write Cycle Time                                                  | —                                                    | 4.0  | 5.0    | ms         |                                               |  |

| D119         | TRETD  | Characteristic Retention                                                | —                                                    | 40   | —      | Year       | Provided no other specifications are violated |  |

| D120         | TREF   | Number of Total Erase/Write Cycles<br>before Refresh <sup>(2)</sup>     | 1M                                                   | 10M  | —      | E/W        | -40°C to +85°C                                |  |

|              |        | Program Flash Memory                                                    |                                                      |      |        |            |                                               |  |

| D121         | Eр     | Cell Endurance                                                          | 10K                                                  | —    | _      | E/W        | -40°C to +85°C (Note 1)                       |  |

| D122         | VPRW   | VDD for Read/Write                                                      | VDDMIN                                               | —    | VDDMAX | V          |                                               |  |

| D123         | Tiw    | Self-timed Write Cycle Time                                             | —                                                    | 2    | 2.5    | ms         |                                               |  |

| D124         | TRETD  | Characteristic Retention                                                | —                                                    | 40   | —      | Year       | Provided no other specifications are violated |  |

# 30.5 Memory Programming Requirements

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

2: Refer to Section 11.2 "Using the Data EEPROM" for a more detailed discussion on data EEPROM endurance.

**3:** Required only if single-supply programming is disabled.

4: The MPLAB<sup>®</sup> ICD 2 does not support variable VPP output. Circuitry to limit the ICD 2 VPP voltage must be placed between the ICD 2 and target system when programming or debugging with the ICD 2.

# TABLE 30-12: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |               |                                                              |          |   |     |    |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------|----------|---|-----|----|--|--|--|--|

| Param. No. Symbol Characteristic Min. Max. Units Condition                                                           |               |                                                              |          |   |     |    |  |  |  |  |

| US120                                                                                                                | TCKH2DTV      | SYNC XMIT (Master and Slave)<br>Clock high to data-out valid | 3.0-5.5V | _ | 80  | ns |  |  |  |  |

|                                                                                                                      |               |                                                              | 1.8-5.5V | — | 100 | ns |  |  |  |  |

| US121                                                                                                                | TCKRF         | Clock out rise time and fall time                            | 3.0-5.5V | — | 45  | ns |  |  |  |  |

|                                                                                                                      | (Master mode) |                                                              | 1.8-5.5V | — | 50  | ns |  |  |  |  |

| US122                                                                                                                | TDTRF         | Data-out rise time and fall time                             | 3.0-5.5V | — | 45  | ns |  |  |  |  |

|                                                                                                                      |               |                                                              | 1.8-5.5V | _ | 50  | ns |  |  |  |  |

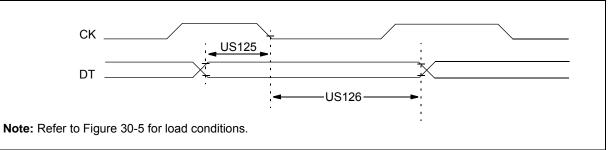

# FIGURE 30-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 30-13: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                                |    |      |       |            |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|----|------|-------|------------|--|

| Param.<br>No.                                                                                                        | Symbol   | cymbol Characteristic                                                          |    | Max. | Units | Conditions |  |

| US125                                                                                                                | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before CK $\downarrow$ (DT hold time) | 10 | _    | ns    |            |  |

| US126                                                                                                                | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15 | —    | ns    |            |  |

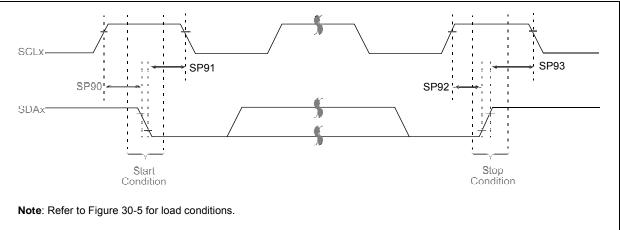

# FIGURE 30-20: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

| TABLE 30-15: | I <sup>2</sup> C <sup>™</sup> BUS START/STOP BITS REQUIREMENTS |

|--------------|----------------------------------------------------------------|

|--------------|----------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                   |  |

|--------------|---------|-----------------|--------------|------|-----|------|-------|------------------------------|--|

| SP90*        | Tsu:sta | Start condition | 100 kHz mode | 4700 | —   | —    | ns    | Only relevant for Repeated   |  |

|              |         | Setup time      | 400 kHz mode | 600  | —   | _    |       | Start Condition              |  |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | —   | —    | ns    | After this period, the first |  |

|              |         | Hold time       | 400 kHz mode | 600  |     | _    |       | clock pulse is generated     |  |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | —   | —    | ns    |                              |  |

|              |         | Setup time      | 400 kHz mode | 600  | 10  | 25   |       |                              |  |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | 25  | 50   | ns    |                              |  |

|              |         | Hold time       | 400 kHz mode | 600  | 10  | 25   |       |                              |  |

\* These parameters are characterized but not tested.

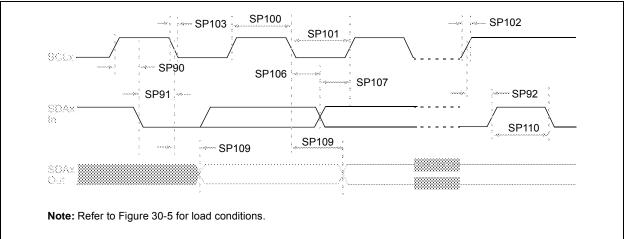

# FIGURE 30-21: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

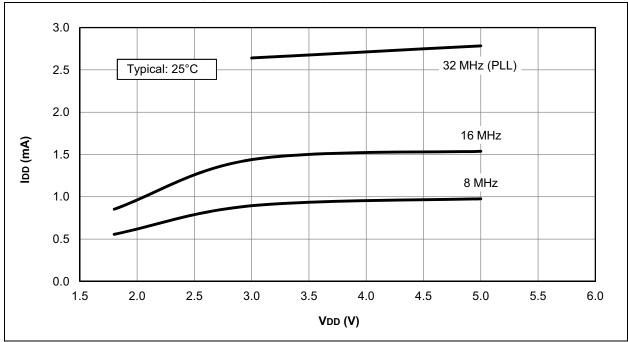

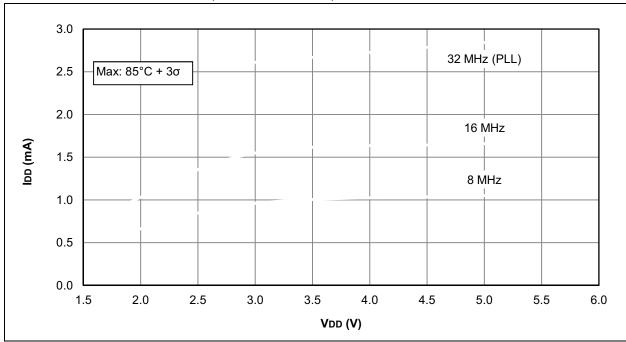

#### FIGURE 31-17: IDD TYPICAL, HFINTOSC MODE, PIC16F1824/8 ONLY

#### FIGURE 31-18: IDD MAXIMUM, HFINTOSC MODE, PIC16F1824/8 ONLY

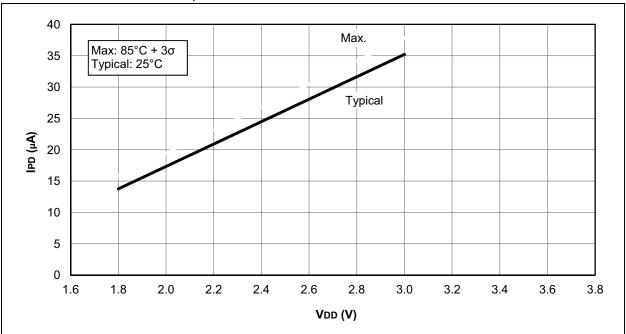

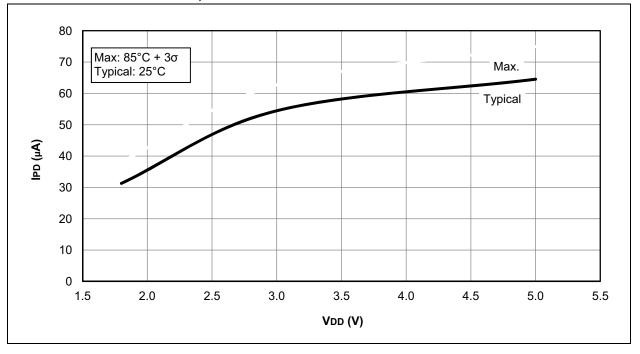

FIGURE 31-35: IPD, CAPACITIVE SENSING (CPS) MODULE, HIGH-CURRENT RANGE, CPSRM = 0, PIC16LF1824/8 ONLY

FIGURE 31-36: IPD, CAPACITIVE SENSING (CPS) MODULE, HIGH-CURRENT RANGE, CPSRM = 0, PIC16F1824/8 ONLY

# 32.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 32.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 32.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 32.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 32.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

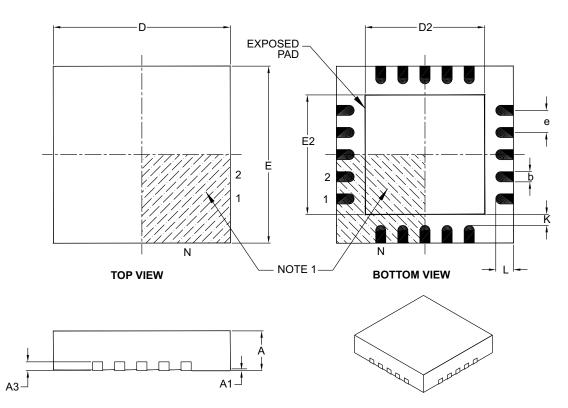

# 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS      |          |          |      |  |  |

|------------------------|------------------|----------|----------|------|--|--|

|                        | Dimension Limits |          |          | MAX  |  |  |

| Number of Pins         | N                | 20       |          |      |  |  |

| Pitch                  | е                |          | 0.50 BSC |      |  |  |

| Overall Height         | A                | 0.80     | 0.90     | 1.00 |  |  |

| Standoff               | A1               | 0.00     | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3               | 0.20 REF |          |      |  |  |

| Overall Width          | E                | 4.00 BSC |          |      |  |  |

| Exposed Pad Width      | E2               | 2.60     | 2.70     | 2.80 |  |  |

| Overall Length         | D                | 4.00 BSC |          |      |  |  |

| Exposed Pad Length     | D2               | 2.60     | 2.70     | 2.80 |  |  |

| Contact Width          | b                | 0.18     | 0.25     | 0.30 |  |  |

| Contact Length         |                  | 0.30     | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad |                  | 0.20     | -        | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B