#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

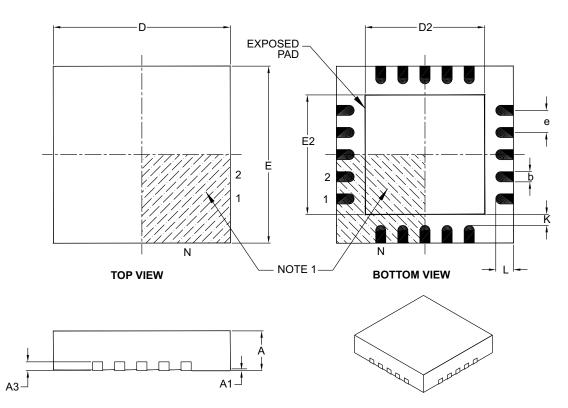

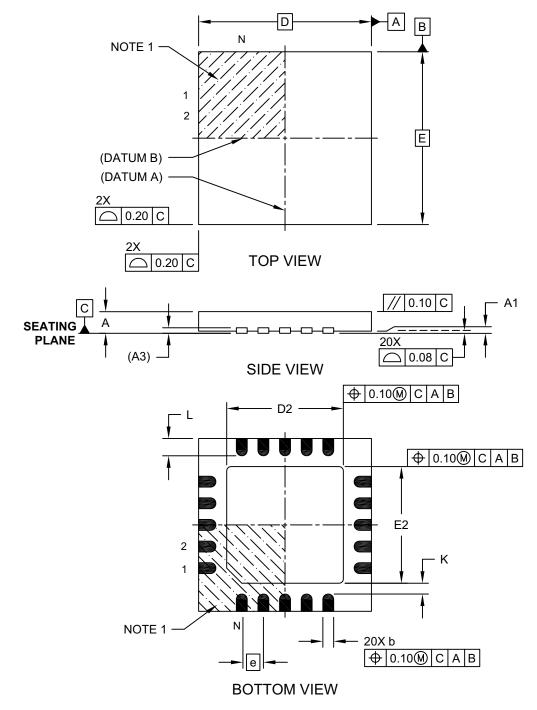

| Package / Case             | 16-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1824-i-jq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

The PIC16(L)F1824/8 are described within this data sheet. They are available in 14/20 pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1824/8 devices. Tables 1-2 and 1-3 show the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1:DEVICE PERIPHERALSUMMARY

| Peripheral               |             | PIC16(L)F1824 | PIC16(L)F1828 |  |  |

|--------------------------|-------------|---------------|---------------|--|--|

| ADC                      |             | ٠             | •             |  |  |

| Capacitive Sensing Mod   | dule (CSM)  | •             | •             |  |  |

| Data EEPROM              |             | ٠             | •             |  |  |

| Digital-to-Analog Conve  | erter (DAC) | ٠             | •             |  |  |

| Digital Signal Modulator | · (DSM)     | ٠             | •             |  |  |

| EUSART                   |             | •             | •             |  |  |

| Fixed Voltage Reference  | e (FVR)     | ٠             | •             |  |  |

| SR Latch                 |             | •             | •             |  |  |

| Capture/Compare/PWN      | I Modules   |               |               |  |  |

|                          | ECCP1       | ٠             | •             |  |  |

|                          | ECCP2       | ٠             | •             |  |  |

|                          | CCP3        | ٠             | •             |  |  |

|                          | CCP4        | •             | •             |  |  |

| Comparators              |             |               |               |  |  |

|                          | C1          | ٠             | •             |  |  |

|                          | C2          | •             | •             |  |  |

| Master Synchronous Se    | erial Ports |               |               |  |  |

|                          | MSSP        | •             | •             |  |  |

| Timers                   |             |               |               |  |  |

|                          | Timer0      | •             | •             |  |  |

|                          | Timer1      | •             | •             |  |  |

|                          | Timer2      | •             | •             |  |  |

|                          | Timer4      | •             | •             |  |  |

|                          | Timer6      | ٠             | •             |  |  |

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

Г

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### **REGISTER 3-1:** STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

| Note 1: | The C and DC bits operate as Borrow         |

|---------|---------------------------------------------|

|         | and Digit Borrow out bits, respectively, in |

|         | subtraction.                                |

| U-0                                     | U-0 | U-0                                                   | R-1/q           | R-1/q | R/W-0/u     | R/W-0/u           | R/W-0/u          |

|-----------------------------------------|-----|-------------------------------------------------------|-----------------|-------|-------------|-------------------|------------------|

| _                                       | _   | —                                                     | TO              | PD    | Z           | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                                   |     |                                                       |                 | bit 0 |             |                   |                  |

|                                         |     |                                                       |                 |       |             |                   |                  |

| Legend:                                 |     |                                                       |                 |       |             |                   |                  |

| R = Readable bit W = Writable bit       |     | U = Unimplemented bit, read as '0'                    |                 |       |             |                   |                  |

| u = Bit is unchanged x = Bit is unknown |     | -n/n = Value at POR and BOR/Value at all other Resets |                 |       | ther Resets |                   |                  |

| '1' = Bit is set '0' = Bit is cleared   |     | q = Value de                                          | pends on condit | ion   |             |                   |                  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-out bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = After power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                                                                                 |

| bit 3   | PD: Power-down bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                                                               |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                               |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                                                             |

| bit 0   | C: Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                              |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

## 7.11 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- Stack Overflow Reset (STKOVF)

- Stack Underflow Reset (STKUNF)

- MCLR Reset (RMCLR)

The PCON register bits are shown in Register 7-2.

### REGISTER 7-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|------------|------------|------------|------------|

| STKOVF     | STKUNF     | —   | —   | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |     |            |            |            | bit 0      |

| Legend:                                                                                                   |                                |                              |                                                                  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|------------------------------------------------------------------|--|--|--|

| HC = Bit is cleared by hardware                                                                           |                                |                              | HS = Bit is set by hardware                                      |  |  |  |

| R = Readable                                                                                              | e bit                          | W = Writable bit             | U = Unimplemented bit, read as '0'                               |  |  |  |

| u = Bit is unc                                                                                            | hanged                         | x = Bit is unknown           | -m/n = Value at POR and BOR/Value at all other Resets            |  |  |  |

| '1' = Bit is set                                                                                          |                                | '0' = Bit is cleared         | q = Value depends on condition                                   |  |  |  |

|                                                                                                           |                                |                              |                                                                  |  |  |  |

| bit 7                                                                                                     | STKOVF: S                      | tack Overflow Flag bit       |                                                                  |  |  |  |

|                                                                                                           | 1 = A Stack                    | Overflow occurred            |                                                                  |  |  |  |

|                                                                                                           | 0 = A Stack                    | Overflow has not occurred    | or set to '0' by firmware                                        |  |  |  |

| bit 6                                                                                                     | STKUNF: S                      | tack Underflow Flag bit      |                                                                  |  |  |  |

|                                                                                                           | 1 = A Stack                    | Underflow occurred           |                                                                  |  |  |  |

| 0 = A Stack Underflow has not occurred or set to '0' by firmware                                          |                                |                              |                                                                  |  |  |  |

| bit 5-4                                                                                                   | Unimplemented: Read as '0'     |                              |                                                                  |  |  |  |

| bit 3                                                                                                     | RMCLR: MCLR Reset Flag bit     |                              |                                                                  |  |  |  |

| $1 = A \overline{MCLR}$ Reset has not occurred or set to '1' by firmware                                  |                                |                              |                                                                  |  |  |  |

| $0 = A \overline{MCLR}$ Reset has occurred (set to '0' in hardware when a $\overline{MCLR}$ Reset occurs) |                                |                              |                                                                  |  |  |  |

| bit 2                                                                                                     | RI: RESET Instruction Flag bit |                              |                                                                  |  |  |  |

|                                                                                                           |                                |                              | executed or set to '1' by firmware                               |  |  |  |

|                                                                                                           | 0 = A RESET                    | r instruction has been execu | ited (set to '0' in hardware upon executing a RESET instruction) |  |  |  |

| bit 1                                                                                                     | POR: Powe                      | r-on Reset Status bit        |                                                                  |  |  |  |

|                                                                                                           | 1 = No Pow                     | ower-on Reset occurred       |                                                                  |  |  |  |

| 0 = A Power-on Reset occurred (must be set in s                                                           |                                |                              | pe set in software after a Power-on Reset occurs)                |  |  |  |

| bit 0                                                                                                     | BOR: Brown                     | n-out Reset Status bit       |                                                                  |  |  |  |

|                                                                                                           | 1 = No Brow                    | vn-out Reset occurred        |                                                                  |  |  |  |

|                                                                                                           | 0 = A Brown                    | n-out Reset occurred (must   | be set in software after a Power-on Reset or Brown-out Reset     |  |  |  |

|                                                                                                           | occurs)                        |                              |                                                                  |  |  |  |

|                                                                                                           |                                |                              |                                                                  |  |  |  |

## 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | LEEDATL    | ;                    |

|---------|------------|----------------------|

| MOVF    | EEDATL, W  | ;EEDATL not changed  |

|         |            | ;from previous write |

| BSF     | EECON1, RD | ;YES, Read the       |

|         |            | ;value written       |

| XORWF   | EEDATL, W  | ;                    |

| BTFSS   | STATUS, Z  | ;Is data the same    |

| GOTO    | WRITE_ERR  | ;No, handle error    |

| :       |            | ;Yes, continue       |

| 1       |            |                      |

## 13.0 INTERRUPT-ON-CHANGE

The PORTA pins can be configured to operate as Interrupt-on-Change (IOC) pins. On the PIC16(L)F1828 devices, the PORTB pins can also be configured to operate as IOC pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

## 13.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 13.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 13.3 Interrupt Flags

The IOCAFx and IOCBFx bits located in the IOCAF and IOCBF registers, respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx and IOCBFx bits.

## 13.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx and IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

| FIGURE 21-6:           | TIMER1 GATE SINGLE                      | -PULSE AND TOGGLE COMBINED MODE                     |

|------------------------|-----------------------------------------|-----------------------------------------------------|

| TMR1 <u>GE</u>         |                                         |                                                     |

| T1GPOL                 |                                         |                                                     |

| T1GSPM                 |                                         |                                                     |

| T1GTM                  |                                         |                                                     |

| T1GG <u>O/</u><br>DONE | Set by software<br>Counting enabled of  | Cleared by hardware on falling edge of T1GVAL       |

| T1G_IN                 | rising edge of T10                      |                                                     |

| тіскі                  |                                         |                                                     |

| T1GVAL                 |                                         |                                                     |

| Timer1                 | Ν                                       | <u>N + 1</u> <u>N + 2</u> <u>N + 3</u> <u>N + 4</u> |

| TMR1GIF                | <ul> <li>Cleared by software</li> </ul> | Set by hardware on<br>falling edge of T1GVAL —      |

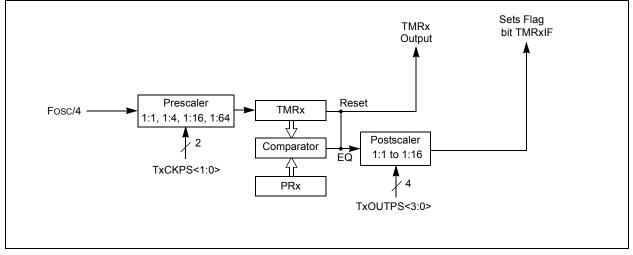

## 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is<br>used to designate Timer2, Timer4, or<br>Timer6. For example, TxCON references |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | T2CON, T4CON, or T6CON. PRx references PR2, PR4, or PR6.                                                                  |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSPx modules (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

## 25.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a chip select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 25-1 shows the block diagram of the MSSP1 module when operating in SPI Mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 25-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 25-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

During each SPI clock cycle, a full duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and

saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

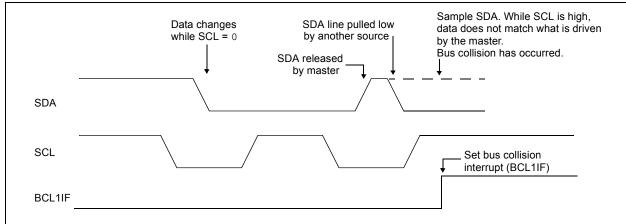

#### FIGURE 25-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### 25.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 25-33).

- b) SCL is sampled low before SDA is asserted low (Figure 25-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCL1IF flag is set and

- the MSSP1 module is reset to its Idle state (Figure 25-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 25-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

**Note:** The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### REGISTER 25-2: SSP1CON1: SSP1 CONTROL REGISTER 1

| R/C/HS-0/0              | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0                                                                                                                                                                                                      | R/W-0/0                                                                                                                             | R/W-0/0                                                                | R/W-0/0                                                                                            | R/W-0/0                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------|

| WCOL                    | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | СКР                                                                                                                                                                                                          |                                                                                                                                     | SSP                                                                    | M<3:0>                                                                                             |                                              |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                     |                                                                        |                                                                                                    | bit (                                        |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                     |                                                                        |                                                                                                    |                                              |

| Legend:                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                              |                                                                                                                                     |                                                                        |                                                                                                    |                                              |

| R = Readable bit        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                              | •                                                                                                                                   | ited bit, read as '0'                                                  |                                                                                                    |                                              |

| u = Bit is unchan       | ged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x = Bit is unknowr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                              |                                                                                                                                     | OR and BOR/Value                                                       |                                                                                                    |                                              |

| '1' = Bit is set        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                              | HS = Bit is set by                                                                                                                  | / hardware                                                             | C = User cleared                                                                                   |                                              |