Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

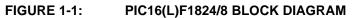

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 16-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 16-QFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1824t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADL |                        |                 | 1-4-1 |                 | 10-1 11   | ALLO       |          |                             |                                                                 |                                        | 1024)              | -           |           |         |                        |

|------|------------------------|-----------------|-------|-----------------|-----------|------------|----------|-----------------------------|-----------------------------------------------------------------|----------------------------------------|--------------------|-------------|-----------|---------|------------------------|

| ОЛ   | 14-Pin PDIP/SOIC/TSSOP | 16-Pin QFN/UQFN | A/D   | Reference       | Cap Sense | Comparator | SR Latch | Timers                      | ECCP                                                            | EUSART                                 | ASSM               | Interrupt   | Modulator | Pull-up | Basic                  |

| RA0  | 13                     | 12              | AN0   | VREF-<br>DACOUT | CPS0      | C1IN+      | —        |                             |                                                                 | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | —                  | IOC         | —         | Y       | ICSPDAT<br>ICDDAT      |

| RA1  | 12                     | 11              | AN1   | VREF+           | CPS1      | C12IN0-    | SRI      | _                           |                                                                 | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | _                  | IOC         | _         | Y       | ICSPCLK<br>ICDCLK      |

| RA2  | 11                     | 10              | AN2   | —               | CPS2      | C10UT      | SRQ      | TOCKI                       | CCP3<br>FLT0                                                    | _                                      | —                  | INT/<br>IOC | —         | Y       | —                      |

| RA3  | 4                      | 3               | _     | —               | —         | —          | —        | T1G <sup>(1)</sup>          | _                                                               | —                                      | <u>SS</u> (1)      | IOC         | —         | Y       | MCLR<br>VPP            |

| RA4  | 3                      | 2               | AN3   | —               | CPS3      | _          | _        | T1G <sup>(1)</sup><br>T1OSO | P2B <sup>(1)</sup>                                              | _                                      | SDO <sup>(1)</sup> | IOC         | _         | Y       | OSC2<br>CLKOUT<br>CLKR |

| RA5  | 2                      | 1               | —     | —               | _         | _          | _        | T1CKI<br>T1OSI              | CCP2<br>P2A <sup>(1)</sup>                                      |                                        | —                  | IOC         | —         | Y       | OSC1<br>CLKIN          |

| RC0  | 10                     | 9               | AN4   | —               | CPS4      | C2IN+      | —        | _                           | P1D <sup>(1)</sup>                                              |                                        | SCL<br>SCK         |             | —         | Y       | —                      |

| RC1  | 9                      | 8               | AN5   | —               | CPS5      | C12IN1-    | _        | _                           | CCP4<br>P1C <sup>(1)</sup>                                      |                                        | SDA<br>SDI         |             | —         | Y       | —                      |

| RC2  | 8                      | 7               | AN6   | —               | CPS6      | C12IN2-    | _        | _                           | P1D <sup>(1)</sup><br>P2B <sup>(1)</sup>                        |                                        | SDO <sup>(1)</sup> | -           | MDCIN1    | Y       | —                      |

| RC3  | 7                      | 6               | AN7   | —               | CPS7      | C12IN3-    | —        | —                           | CCP2 <sup>(1)</sup><br>P1C <sup>(1)</sup><br>P2A <sup>(1)</sup> | _                                      | SS <sup>(1)</sup>  | _           | MDMIN     | Y       | —                      |

| RC4  | 6                      | 5               | —     | —               | _         | C2OUT      | SRNQ     | _                           | P1B                                                             | TX <sup>(1)</sup><br>CK <sup>(1)</sup> | —                  |             | MDOUT     | Y       | —                      |

| RC5  | 5                      | 4               | —     | —               | _         | _          |          | _                           | CCP1<br>P1A                                                     | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | _                  |             | MDCIN2    | Y       | —                      |

| Vdd  | 1                      | 16              | —     | —               | —         | —          | —        | —                           | —                                                               | —                                      | _                  | —           | —         | —       | Vdd                    |

| Vss  | 14                     | 13              | _     | —               | —         | —          | —        | —                           | _                                                               | —                                      | —                  | _           | —         | —       | Vss                    |

#### TABLE 1: 14-PIN AND 16-PIN ALLOCATION TABLE (PIC16(L)F1824)

Note 1: Pin function is selectable via the APFCON0 or APFCON1 registers.

### TABLE 1-3: PIC16(L)F1828 PINOUT DESCRIPTION

| Name                                                           | Function | Input | Output | Description                                   |  |  |

|----------------------------------------------------------------|----------|-------|--------|-----------------------------------------------|--|--|

| Naille                                                         | Tunction | Туре  | Туре   |                                               |  |  |

| RA0/AN0/CPS0/C1IN+/VREF-/                                      | RA0      | TTL   | CMOS   | General purpose I/O.                          |  |  |

| DACOUT/ICSPDAT/ICDDAT                                          | AN0      | AN    | _      | A/D Channel 0 input.                          |  |  |

|                                                                | CPS0     | AN    |        | Capacitive sensing input 0.                   |  |  |

|                                                                | C1IN+    | AN    | —      | Comparator C1 positive input.                 |  |  |

|                                                                | VREF-    | AN    | _      | A/D and DAC Negative Voltage Reference input. |  |  |

|                                                                | DACOUT   |       | AN     | Digital-to-Analog Converter output.           |  |  |

|                                                                | ICSPDAT  | ST    | CMOS   | ICSP™ Data I/O.                               |  |  |

|                                                                | ICDDAT   | ST    | CMOS   | In-Circuit Data I/O.                          |  |  |

| RA1/AN1/CPS1/C12IN0-/VREF+/                                    | RA1      | TTL   | CMOS   | General purpose I/O.                          |  |  |

| SRI/ICSPCLK/ICDCLK                                             | AN1      | AN    |        | A/D Channel 1 input.                          |  |  |

|                                                                | CPS1     | AN    |        | Capacitive sensing input 1.                   |  |  |

|                                                                | C12IN0-  | AN    |        | Comparator C1 or C2 negative input.           |  |  |

|                                                                | VREF+    | AN    |        | A/D and DAC Positive Voltage Reference input. |  |  |

|                                                                | SRI      | ST    |        | SR latch input.                               |  |  |

|                                                                | ICSPCLK  | ST    |        | Serial Programming Clock.                     |  |  |

|                                                                | ICDCLK   | ST    |        | In-Circuit Debug Clock.                       |  |  |

| RA2/AN2/CPS2/T0CKI/INT/                                        | RA2      | ST    | CMOS   | General purpose I/O.                          |  |  |

| C1OUT/SRQ/CCP3/FLT0                                            | AN2      | AN    |        | A/D Channel 2 input.                          |  |  |

|                                                                | CPS2     | AN    |        | Capacitive sensing input 2.                   |  |  |

|                                                                | TOCKI    | ST    |        | Timer0 clock input.                           |  |  |

|                                                                | INT      | ST    |        | External interrupt.                           |  |  |

|                                                                | C10UT    | _     | CMOS   | Comparator C1 output.                         |  |  |

|                                                                | SRQ      | _     | CMOS   | SR latch non-inverting output.                |  |  |

|                                                                | CCP3     | ST    | CMOS   | Capture/Compare/PWM3.                         |  |  |

|                                                                | FLT0     | ST    |        | ECCP Auto-Shutdown Fault input.               |  |  |

| RA3/T1G <sup>(1)</sup> /VPP/MCLR                               | RA3      | TTL   |        | General purpose input.                        |  |  |

|                                                                | T1G      | ST    |        | Timer1 Gate input.                            |  |  |

|                                                                | VPP      | ΗV    |        | Programming voltage.                          |  |  |

|                                                                | MCLR     | ST    |        | Master Clear with internal pull-up.           |  |  |

| RA4/AN3/CPS3/OSC2/                                             | RA4      | TTL   | CMOS   | General purpose I/O.                          |  |  |

| CLKOUT/T1OSO/CLKR/P2B <sup>(1)</sup> /<br>T1G <sup>(1,2)</sup> | AN3      | AN    | _      | A/D Channel 3 input.                          |  |  |

| 116(.,-)                                                       | CPS3     | AN    |        | Capacitive sensing input 3.                   |  |  |

|                                                                | OSC2     | _     | CMOS   | Comparator C2 output.                         |  |  |

|                                                                | CLKOUT   | _     | CMOS   | Fosc/4 output.                                |  |  |

|                                                                | T10S0    | XTAL  | XTAL   | Timer1 oscillator connection.                 |  |  |

|                                                                | CLKR     | —     | CMOS   | Clock Reference output.                       |  |  |

|                                                                | P2B      | —     | CMOS   | PWM output.                                   |  |  |

|                                                                | T1G      | ST    | —      | Timer1 Gate input.                            |  |  |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C^{TM}$ = Schmitt Trigger input with  $I^2C$ HV = High VoltageXTAL = Crystallevels

Note 1: Pin functions can be moved using the APFCONO and APFCON1 registers (Register 12-1 and Register 12-2).

2: Default function location.

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

**OSCILLATOR SWITCHING DELAYS**

#### Switch From Switch To Frequency **Oscillator Delay** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Sleep/POR Oscillator Warm-up Delay (TWARM) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC. RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> LFINTOSC DC - 32 MHz 1 cycle of each Timer1 Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> Any clock source 31 kHz 1 cycle of each Any clock source Timer1 Oscillator 32 kHz 1024 Clock Cycles (OST) PLL inactive PLL active 16-32 MHz 2 ms (approx.)

Note 1: PLL inactive.

**TABLE 5-1:**

#### TWO-SPEED START-UP MODE 5.4.1 CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Word 1 configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- · Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

When FSCM is enabled, Two-Speed Note: Start-up will automatically be enabled.

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

###

#### FIGURE 5-8: TWO-SPEED START-UP

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

#### 8.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, interrupt-on-change and external INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R-0/0                |

|---------|---------|---------|---------|---------|---------|---------|----------------------|

| GIE     | PEIE    | TMR0IE  | INTE    | IOCIE   | TMR0IF  | INTF    | IOCIF <sup>(1)</sup> |

| bit 7   |         |         |         |         |         |         | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | GIE: Global Interrupt Enable bit                                                                                                                                                                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Enables all active interrupts<br>0 = Disables all interrupts                                                                                                                                                                  |

| bit 6   | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                            |

| bit 5   | <b>TMR0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                                                      |

| bit 4   | INTE: INT External Interrupt Enable bit<br>1 = Enables the INT external interrupt<br>0 = Disables the INT external interrupt                                                                                                      |

| bit 3   | IOCIE: Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                                                                                                              |

| bit 2   | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                                                       |

| bit 1   | INTF: INT External Interrupt Flag bit<br>1 = The INT external interrupt occurred<br>0 = The INT external interrupt did not occur                                                                                                  |

| bit 0   | <ul> <li>IOCIF: Interrupt-on-Change Interrupt Flag bit<sup>(1)</sup></li> <li>1 = When at least one of the interrupt-on-change pins changed state</li> <li>0 = None of the interrupt-on-change pins have changed state</li> </ul> |

| Note 1: | The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCxF registe                                                                                                                           |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCxF register have been cleared by software.

| U-0             | U-0                                 | R/W-0/0                                                       | R/W-1/1                            | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |

|-----------------|-------------------------------------|---------------------------------------------------------------|------------------------------------|-----------------|------------------|-----------------|--------------|

| _               |                                     | WDTPS4                                                        | WDTPS3                             | WDTPS2          | WDTPS1           | WDTPS0          | SWDTEN       |

| bit 7           |                                     |                                                               | 1                                  | •               | •                | •               | bit 0        |

|                 |                                     |                                                               |                                    |                 |                  |                 | ,            |

| Legend:         |                                     |                                                               |                                    |                 |                  |                 |              |

| R = Readab      | le bit                              | W = Writable                                                  | bit                                | U = Unimpler    | mented bit, read | d as '0'        |              |

| u = Bit is un   | changed                             | x = Bit is unk                                                | nown                               | -m/n = Value    | at POR and BO    | DR/Value at all | other Resets |

| '1' = Bit is se | et                                  | '0' = Bit is cle                                              | ared                               |                 |                  |                 |              |

|                 |                                     |                                                               |                                    |                 |                  |                 |              |

| bit 7-6         | Unimpleme                           | nted: Read as '                                               | 0'                                 |                 |                  |                 |              |

| bit 5-1         | WDTPS<4:0                           | )>: Watchdog Ti                                               | imer Period Se                     | elect bits      |                  |                 |              |

|                 | Bit Value =                         | Prescale Rate                                                 |                                    |                 |                  |                 |              |

|                 |                                     | 32 (Interval 1 m                                              |                                    |                 |                  |                 |              |

|                 |                                     | 64 (Interval 2 m<br>128 (Interval 4                           |                                    |                 |                  |                 |              |

|                 |                                     | 256 (Interval 8                                               | 21 /                               |                 |                  |                 |              |

|                 | 00100 = <b>1</b> :                  | 512 (Interval 16                                              | 6 ms typ)                          |                 |                  |                 |              |

|                 |                                     | 1024 (Interval 3                                              |                                    |                 |                  |                 |              |

|                 |                                     | 2048 (Interval 6<br>4096 (Interval 1                          |                                    |                 |                  |                 |              |

|                 |                                     | 8192 (Interval 2                                              | <b>21</b>                          |                 |                  |                 |              |

|                 |                                     | 16384 (Interval                                               |                                    |                 |                  |                 |              |

|                 |                                     | 32768 (Interval 65536 (Interva                                |                                    | at value)       |                  |                 |              |

|                 | 01100 = <b>1</b> :                  | $131072(2^{17})$ (h                                           | nterval 4s tvp)                    |                 |                  |                 |              |

|                 | 01101 = <b>1</b> :                  | 262144 (2 <sup>18</sup> ) (li                                 | nterval 8s tvp)                    |                 |                  |                 |              |

|                 | 01110 = 1:                          | 524288 (2 <sup>19</sup> ) (li<br>1048576 (2 <sup>20</sup> ) ( | nterval 16s typ                    | ))<br>)         |                  |                 |              |

|                 | 10000 = 1                           | 2097152 (2 <sup>21</sup> ) (                                  | Interval 32s ty<br>Interval 64s ty | (p)             |                  |                 |              |

|                 | 10001 = 1:                          | 4194304 (2 <sup>22</sup> ) (                                  | Interval 128s                      | typ)            |                  |                 |              |

|                 | 10010 = <b>1</b> :                  | 8388608 (2 <sup>23</sup> ) (                                  | Interval 256s                      | typ)            |                  |                 |              |

|                 | 10011 = R                           | eserved. Result                                               | s in minimum                       | interval (1·32) |                  |                 |              |

|                 | •                                   |                                                               |                                    |                 |                  |                 |              |

|                 | •                                   |                                                               |                                    |                 |                  |                 |              |

|                 | •<br>11111 - D                      | eserved. Result                                               | e in minimum                       | interval (1.32) |                  |                 |              |

| bit 0           |                                     | Software Enable                                               |                                    | ( )             | bit              |                 |              |

| bit 0           | If WDTE<1:                          |                                                               |                                    | atchoog miner   | bit              |                 |              |

|                 | This bit is ig                      |                                                               |                                    |                 |                  |                 |              |

|                 | If WDTE<1:0                         |                                                               |                                    |                 |                  |                 |              |

|                 | 1 = WDT is<br>0 = WDT is            |                                                               |                                    |                 |                  |                 |              |

|                 | 0 = WDT IS<br><u>If WDTE&lt;1:(</u> |                                                               |                                    |                 |                  |                 |              |

|                 | This bit is ig                      |                                                               |                                    |                 |                  |                 |              |

|                 |                                     |                                                               |                                    |                 |                  |                 |              |

### REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

#### EXAMPLE 11-2: DATA EEPROM WRITE

| MOV<br>MOV<br>MOV<br>BCF     | LW DATA_EE_DAT<br>WF EEDATL<br>EECON1, CFC<br>EECON1, EE                                               | ;Data Memory Address to write<br>TA ;<br>;Data Memory Value to write<br>SS ;Deselect Configuration space<br>PGD ;Point to DATA memory |

|------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| eunende<br>BSF<br>BSF<br>BCF | LW 55h<br>WF EECON2<br>LW 0AAh<br>WF EECON2<br>EECON1, WR<br>EECON1, WR<br>EECON1, WR<br>SC EECON1, WR | ;<br>;Write AAh<br>;Set WR bit to begin write<br>E ;Enable Interrupts<br>EN ;Disable writes                                           |

|                              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4              | Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4                    |

|------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------|--------------------------------|--------------------------------|

| Flash ADDR                   | <br>()<br>                     | PC + 1                         | (EEADRH,EEADRL)                | PC + 3                   | PC + 4                         | PC + 5                         |

| Flash Data                   |                                | TR (PC)                        | R (PC + 1) EEDA                | TH,EEDATL INST           | R (PC + 3) INST                | R (PC + 4)                     |

|                              | INSTR(PC - 1)<br>executed here | BSF EECON1,RD<br>executed here | INSTR(PC + 1)<br>executed here | Forced NOP executed here | INSTR(PC + 3)<br>executed here | INSTR(PC + 4)<br>executed here |

| RD bit                       |                                |                                | /                              |                          |                                |                                |

| EEDATH<br>EEDATL<br>Register |                                |                                |                                | Χ                        |                                |                                |

| EERHLT                       | <br>  <br>1                    | <br>                           | /                              |                          |                                |                                |

|        |         | -       |         |         |       |       | -     |       |                     |

|--------|---------|---------|---------|---------|-------|-------|-------|-------|---------------------|

| Name   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

| ANSELB | —       | —       | ANSB5   | ANSB4   | —     | —     | _     | —     | 128                 |

| INLVLB | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —     | —     | _     | —     | 128                 |

| LATB   | LATB7   | LATB6   | LATB5   | LATB4   | —     | —     | _     | —     | 127                 |

| PORTB  | RB7     | RB6     | RB5     | RB4     | —     | —     | _     | —     | 127                 |

| TRISB  | TRISB7  | TRISB6  | TRISB5  | TRISB4  | —     | —     | _     | —     | 127                 |

| WPUB   | WPUB7   | WPUB6   | WPUB5   | WPUB4   | —     | —     | _     | —     | 128                 |

TABLE 12-3:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTB<sup>(1)</sup>

Legend: x = unknown, u = unchanged, - = unimplemented locations, read as '0'. Shaded cells are not used by PORTB. Note 1: PIC16(L)F1828 only.

#### **19.3 Comparator Hysteresis**

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

### 19.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 19.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from either comparator, C1 or C2, can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagrams (Figure 19-2 and Figure 19-2) and the Timer1 Block Diagram (Figure 20-1) for more information.

#### **19.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a Falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

| Note: | Although a comparator is disabled, an      |

|-------|--------------------------------------------|

|       | interrupt can be generated by changing     |

|       | the output polarity with the CxPOL bit of  |

|       | the CMxCON0 register, or by switching      |

|       | the comparator on or off with the CxON bit |

|       | of the CMxCON0 register.                   |

### 19.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC\_output

- FVR Buffer2

- Vss (Ground)

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

### 23.1 DSM Operation

The DSM module can be enabled by setting the MDEN bit in the MDCON register. Clearing the MDEN bit in the MDCON register, disables the DSM module by automatically switching the carrier high and carrier low signals to the Vss signal source. The modulator signal source is also switched to the MDBIT in the MDCON register. This not only assures that the DSM module is inactive, but that it is also consuming the least amount of current.

The values used to select the carrier high, carrier low, and modulator sources held by the modulation source, modulation high carrier, and modulation low carrier control registers are not affected when the MDEN bit is cleared and the DSM module is disabled. The values inside these registers remain unchanged while the DSM is inactive. The sources for the carrier high, carrier low and modulator signals will once again be selected when the MDEN bit is set and the DSM module is again enabled and active.

The modulated output signal can be disabled without shutting down the DSM module. The DSM module will remain active and continue to mix signals, but the output value will not be sent to the MDOUT pin. During the time that the output is disabled, the MDOUT pin will remain low. The modulated output can be disabled by clearing the MDOE bit in the MDCON register.

#### 23.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources:

- CCP1 Signal

- CCP2 Signal

- CCP3 Signal

- CCP4 Signal

- MSSP1 SDO1 Signal (SPI mode only)

- MSSP2 SDO2 Signal (SPI mode only)

- · Comparator C1 Signal

- · Comparator C2 Signal

- EUSART TX Signal

- External Signal on MDMIN1 pin

- MDBIT bit in the MDCON register

The modulator signal is selected by configuring the MDMS <3:0> bits in the MDSRC register.

#### 23.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources:

- CCP1 signal

- · CCP2 signal

- · CCP3 signal

- CCP4 signal

- · Reference clock module signal

- · External signal on MDCIN1 pin

- · External signal on MDCIN2 pin

- Vss

The carrier high signal is selected by configuring the MDCH <3:0> bits in the MDCARH register. The carrier low signal is selected by configuring the MDCL <3:0> bits in the MDCARL register.

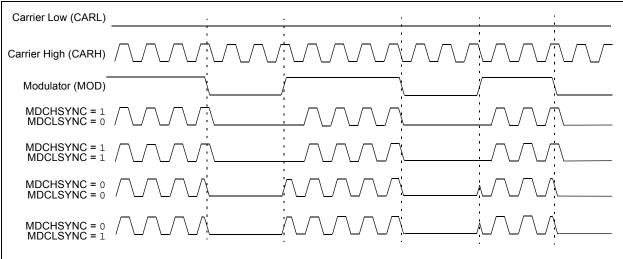

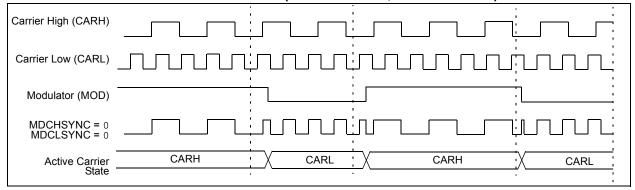

#### 23.4 Carrier Synchronization

During the time when the DSM switches between carrier high and carrier low signal sources, the carrier data in the modulated output signal can become truncated. To prevent this, the carrier signal can be synchronized to the modulator signal. When synchronization is enabled, the carrier pulse that is being mixed at the time of the transition is allowed to transition low before the DSM switches over to the next carrier source.

Synchronization is enabled separately for the carrier high and carrier low signal sources. Synchronization for the carrier high signal can be enabled by setting the MDCHSYNC bit in the MDCARH register. Synchronization for the carrier low signal can be enabled by setting the MDCLSYNC bit in the MDCARL register.

Figure 23-1 through Figure 23-5 show timing diagrams of using various synchronization methods.

#### EXAMPLE 23-1: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

| Carrier High (CARH)          |                                     |

|------------------------------|-------------------------------------|

| Carrier Low (CARL)           |                                     |

| Modulator (MOD)              |                                     |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                     |

| Active Carrier<br>State      | CARH / both CARL / CARH / both CARL |

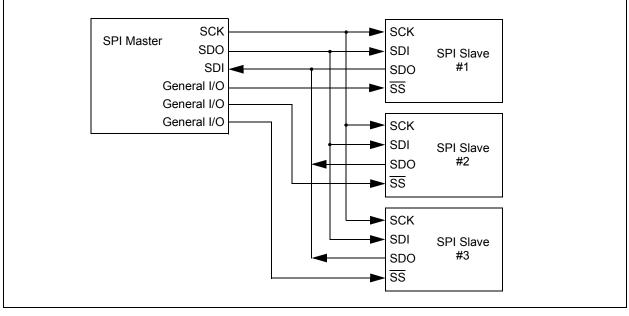

#### FIGURE 25-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 25.2.1 SPI MODE REGISTERS

The MSSP1 module has five registers for SPI mode operation. These are:

- MSSP1 STATUS Register (SSP1STAT)

- MSSP1 Control Register 1 (SSP1CON1)

- MSSP1 Control Register 3 (SSP1CON3)

- MSSP1 Data Buffer Register (SSP1BUF)

- MSSP1 Address Register (SSP1ADD)

- MSSP1 Shift Register (SSP1SR) (Not directly accessible)

SSP1CON1 and SSP1STAT are the control and STATUS registers in SPI mode operation. The SSP1CON1 register is readable and writable. The lower six bits of the SSP1STAT are read-only. The upper two bits of the SSP1STAT are read/write.

In SPI master mode, SSP1ADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 25.7 "Baud Rate Generator"**.

SSP1SR is the shift register used for shifting data in and out. SSP1BUF provides indirect access to the SSP1SR register. SSP1BUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSP1SR and SSP1BUF together create a buffered receiver. When SSP1SR receives a complete byte, it is transferred to SSP1BUF and the SSP1IF interrupt is set.

During transmission, the SSP1BUF is not buffered. A write to SSP1BUF will write to both SSP1BUF and SSP1SR.

| R/W-0/0              | R-0/0                                                                                                                                      | R/W-0/0                                                     | R/S/HS-0/0                    | R/S/HS-0/0                   | R/S/HS-0/0        | R/S/HS-0/0       | R/W/HS-0/0   |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------|------------------------------|-------------------|------------------|--------------|--|--|--|--|

| GCEN                 | ACKSTAT                                                                                                                                    | ACKDT                                                       | ACKEN                         | RCEN                         | PEN               | RSEN             | SEN          |  |  |  |  |

| bit 7                |                                                                                                                                            |                                                             |                               |                              |                   |                  | bit C        |  |  |  |  |

|                      |                                                                                                                                            |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| Legend:              |                                                                                                                                            |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| R = Readable         | bit                                                                                                                                        | W = Writable                                                | bit                           | U = Unimpler                 | mented bit, read  | d as '0'         |              |  |  |  |  |

| u = Bit is unchanged |                                                                                                                                            | x = Bit is unk                                              | nown                          | -n/n = Value                 | at POR and BO     | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is set     |                                                                                                                                            | '0' = Bit is cle                                            | ared                          | HC = Cleared                 | d by hardware     | S = User set     |              |  |  |  |  |

|                      |                                                                                                                                            |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| bit 7                |                                                                                                                                            | eral Call Enable                                            | •                             | • •                          |                   |                  |              |  |  |  |  |

|                      |                                                                                                                                            | iterrupt when a<br>call address dis                         | •                             | ddress (0x00 d               | or 00h) is receiv | ed in the SSP1   | ISR          |  |  |  |  |

| bit 6                |                                                                                                                                            | cknowledge St                                               |                               | mode only)                   |                   |                  |              |  |  |  |  |

|                      | <ul> <li>1 = Acknowledge was not received</li> <li>0 = Acknowledge was received</li> </ul>                                                 |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| bit 5                |                                                                                                                                            | -                                                           | -                             |                              |                   |                  |              |  |  |  |  |

| DIL D                |                                                                                                                                            | ACKDT: Acknowledge Data bit (in I <sup>2</sup> C mode only) |                               |                              |                   |                  |              |  |  |  |  |

|                      | <u>In Receive mode:</u><br>Value transmitted when the user initiates an Acknowledge sequence at the end of a receive                       |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 1 = Not Acknowledge                                                                                                                        |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 0 = Acknowle                                                                                                                               | •                                                           |                               | 0                            |                   |                  |              |  |  |  |  |

| bit 4                | <b>ACKEN:</b> Acknowledge Sequence Enable bit (in I <sup>2</sup> C Master mode only)                                                       |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | In Master Receive mode:                                                                                                                    |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit.<br>Automatically cleared by hardware.                  |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      |                                                                                                                                            | edge sequence                                               |                               |                              |                   |                  |              |  |  |  |  |

| bit 3                | RCEN: Rece                                                                                                                                 | ive Enable bit                                              | (in I <sup>2</sup> C Master   | mode only)                   |                   |                  |              |  |  |  |  |

|                      | 1 = Enables Receive mode for $I^2C$                                                                                                        |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 0 = Receive i                                                                                                                              |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| bit 2                | -                                                                                                                                          | ondition Enable                                             | e bit (in I <sup>2</sup> C Ma | ster mode only               | y)                |                  |              |  |  |  |  |

|                      | <u>SCK Release Control:</u><br>1 = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware.                         |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 1 = Initiate Stop condition of SDA and SCL pins. Automatically cleared by hardware.<br>0 = Stop condition Idle                             |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| bit 1                | RSEN: Repe                                                                                                                                 | ated Start Con                                              | dition Enabled                | bit (in I <sup>2</sup> C Mas | ster mode only)   |                  |              |  |  |  |  |

|                      | 1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.                                              |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 0 = Repeated Start condition Idle                                                                                                          |                                                             |                               |                              |                   |                  |              |  |  |  |  |

| bit 0                |                                                                                                                                            | ondition Enable                                             | ed bit (in I <sup>2</sup> C M | laster mode or               | ıly)              |                  |              |  |  |  |  |

|                      | In Master mode:                                                                                                                            |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | <ul> <li>1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = Start condition Idle</li> </ul> |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | In Slave mod                                                                                                                               |                                                             |                               |                              |                   |                  |              |  |  |  |  |

|                      | 1 = Clock stre                                                                                                                             | etching is enab                                             |                               | ave transmit a               | nd slave receive  | e (stretch enabl | ed)          |  |  |  |  |

|                      | 0 = Clock stre                                                                                                                             | etching is disal                                            | bled                          |                              |                   |                  |              |  |  |  |  |

| Note 1: For          | bits ACKEN. F                                                                                                                              | RCEN, PEN, R                                                | SEN, SEN: If t                | he I <sup>2</sup> C module   | is not in the Idl | e mode, this bi  | t may not be |  |  |  |  |

#### REGISTER 25-3: SSP1CON2: SSP1 CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSP1BUF may not be written (or writes to the SSP1BUF are disabled).

| Mnemonic,<br>Operands |      |                               |               | 14-Bit Opcode |      |      |      | Status   |       |

|-----------------------|------|-------------------------------|---------------|---------------|------|------|------|----------|-------|

|                       |      | Description                   | Cycles        | MSb           |      |      | LSb  | Affected | Notes |

|                       |      | BYTE-ORIENTED FILE F          | REGISTER OPE  | RATIC         | NS   |      |      |          |       |

| ADDWF                 | f, d | Add W and f                   | 1             | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC                | f, d | Add with Carry W and f        | 1             | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF                 | f, d | AND W with f                  | 1             | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF                  | f, d | Arithmetic Right Shift        | 1             | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF                  | f, d | Logical Left Shift            | 1             | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF                  | f, d | Logical Right Shift           | 1             | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF                  | f    | Clear f                       | 1             | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | _    | Clear W                       | 1             | 00            | 0001 | 0000 | 00xx | Z        |       |

| COMF                  | f, d | Complement f                  | 1             | 00            | 1001 | dfff | ffff | Z        | 2     |

| DECF                  | f, d | Decrement f                   | 1             | 00            | 0011 | dfff | ffff | Z        | 2     |

| INCF                  | f, d | Increment f                   | 1             | 00            | 1010 | dfff | ffff | Z        | 2     |

| IORWF                 | f, d | Inclusive OR W with f         | 1             | 00            | 0100 | dfff | ffff | Z        | 2     |

| MOVF                  | f, d | Move f                        | 1             | 00            | 1000 | dfff | ffff | Z        | 2     |

| MOVWF                 | f    | Move W to f                   | 1             | 00            | 0000 | 1fff | ffff |          | 2     |

| RLF                   | f, d | Rotate Left f through Carry   | 1             | 00            |      | dfff |      | С        | 2     |

| RRF                   | f, d | Rotate Right f through Carry  | 1             | 00            | 1100 | dfff |      | C        | 2     |

| SUBWF                 | f, d | Subtract W from f             | 1             | 00            |      | dfff |      | -        | 2     |

| SUBWFB                | f, d | Subtract with Borrow W from f | 1             | 11            |      | dfff |      | C, DC, Z | 2     |

| SWAPF                 | f, d | Swap nibbles in f             | 1             | 00            |      | dfff |      | 0,20,2   | 2     |

| XORWF                 | f, d | Exclusive OR W with f         | 1             | 00            |      | dfff |      | Z        | 2     |

|                       | ,    | BYTE ORIENTED S               | SKIP OPERATIO | ONS           |      |      |      |          |       |

| DECFSZ                | f, d | Decrement f, Skip if 0        | 1(2)          | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ                | f, d | Increment f, Skip if 0        | 1(2)          | 00            | 1111 | dfff | ffff |          | 1, 2  |

|                       |      | BIT-ORIENTED FILE R           | EGISTER OPER  |               | IS   |      |      |          |       |

| BCF                   | f, b | Bit Clear f                   | 1             | 01            | 00bb | bfff | ffff |          | 2     |

| BSF                   | f, b | Bit Set f                     | 1             | 01            | 01bb | bfff | ffff |          | 2     |

|                       |      | BIT-ORIENTED S                |               | NS            | 1    |      |      |          |       |

| BTFSC                 | f, b | Bit Test f, Skip if Clear     | 1 (2)         | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS                 | f, b | Bit Test f, Skip if Set       | 1 (2)         | 01            | 11bb | bfff | ffff |          | 1, 2  |

|                       |      | LITERAL O                     | PERATIONS     |               |      |      |      |          |       |

| ADDLW                 | k    | Add literal and W             | 1             | 11            | 1110 | kkkk | kkkk | C, DC, Z |       |

| ANDLW                 | k    | AND literal with W            | 1             | 11            | 1001 | kkkk | kkkk | Z        |       |

| IORLW                 | k    | Inclusive OR literal with W   | 1             | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLB                 | k    | Move literal to BSR           | 1             | 00            | 0000 | 001k | kkkk |          |       |

| MOVLP                 | k    | Move literal to PCLATH        | 1             | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW                 | k    | Move literal to W             | 1             | 11            | 0000 | kkkk | kkkk |          |       |

| SUBLW                 | k    | Subtract W from literal       | 1             | 11            | 1100 | kkkk | kkkk | C, DC, Z |       |

| CODL                  |      |                               |               |               |      |      |      |          |       |

### TABLE 29-3: PIC16F/LF1824/1828 ENHANCED INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

### 30.3 DC Characteristics: PIC16(L)F1824/8-I/E (Power-Down)

| PIC16LF1824/8<br>PIC16F1824/8 |                         |                      | Operating temperature |      |     | ditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended<br>ditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |                                    |  |

|-------------------------------|-------------------------|----------------------|-----------------------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------|--|

|                               |                         |                      |                       |      |     |                                                                                                                                                                                                                                                                                                          |     |                                    |  |

| No.                           | Device Characteristics  | Min.                 | Vdd                   | Note |     |                                                                                                                                                                                                                                                                                                          |     |                                    |  |

|                               | Power-down Base Current | (IPD) <sup>(2)</sup> |                       | •    | •   |                                                                                                                                                                                                                                                                                                          |     |                                    |  |

| D022                          |                         | _                    | 0.02                  | 1.0  | 2.4 | μA                                                                                                                                                                                                                                                                                                       | 1.8 | WDT, BOR, FVR, and T1OSC           |  |

|                               |                         | —                    | 0.03                  | 1.5  | 3.0 | μA                                                                                                                                                                                                                                                                                                       | 3.0 | disabled, all Peripherals Inactive |  |

| D022                          |                         | _                    | 18                    | 37   | 44  | μA                                                                                                                                                                                                                                                                                                       | 1.8 | WDT, BOR, FVR, and T1OSC           |  |

|                               |                         | _                    | 20                    | 42   | 48  | μA                                                                                                                                                                                                                                                                                                       | 3.0 | disabled, all Peripherals Inactive |  |

|                               |                         | —                    | 22                    | 45   | 65  | μA                                                                                                                                                                                                                                                                                                       | 5.0 |                                    |  |

| D023                          |                         |                      | 0.2                   | 2.0  | 3.0 | μA                                                                                                                                                                                                                                                                                                       | 1.8 | LPWDT Current (Note 1)             |  |

|                               |                         | —                    | 0.5                   | 2.0  | 4.0 | μA                                                                                                                                                                                                                                                                                                       | 3.0 |                                    |  |

| D023                          |                         | —                    | 18                    | 38   | 44  | μA                                                                                                                                                                                                                                                                                                       | 1.8 | LPWDT Current (Note 1)             |  |

|                               |                         |                      | 21                    | 43   | 48  | μA                                                                                                                                                                                                                                                                                                       | 3.0 |                                    |  |

|                               |                         | —                    | 22                    | 46   | 65  | μA                                                                                                                                                                                                                                                                                                       | 5.0 |                                    |  |

| D023A                         |                         |                      | 12                    | 22   | 25  | μA                                                                                                                                                                                                                                                                                                       | 1.8 | FVR current                        |  |

|                               |                         | —                    | 13                    | 24   | 27  | μA                                                                                                                                                                                                                                                                                                       | 3.0 |                                    |  |

| D023A                         |                         | _                    | 33                    | 62   | 65  | μA                                                                                                                                                                                                                                                                                                       | 1.8 | FVR current                        |  |

|                               |                         | _                    | 40                    | 72   | 75  | μA                                                                                                                                                                                                                                                                                                       | 3.0 |                                    |  |

|                               |                         | —                    | 68                    | 115  | 120 | μA                                                                                                                                                                                                                                                                                                       | 5.0 |                                    |  |

| D024                          |                         | —                    | 7.0                   | 14   | 16  | μA                                                                                                                                                                                                                                                                                                       | 3.0 | BOR Current (Note 1)               |  |

| D024                          |                         | —                    | 24                    | 47   | 50  | μA                                                                                                                                                                                                                                                                                                       | 3.0 | BOR Current (Note 1)               |  |

|                               |                         | —                    | 29                    | 55   | 70  | μA                                                                                                                                                                                                                                                                                                       | 5.0 |                                    |  |

| D025                          |                         | _                    | 0.65                  | 3.5  | 4.0 | μA                                                                                                                                                                                                                                                                                                       | 1.8 | T1OSC Current (Note 1)             |  |

|                               |                         | —                    | 2.3                   | 4.0  | 4.5 | μA                                                                                                                                                                                                                                                                                                       | 3.0 |                                    |  |

| D025                          |                         | —                    | 19                    | 39   | 45  | μA                                                                                                                                                                                                                                                                                                       | 1.8 | T1OSC Current (Note 1)             |  |