Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

|                            |                                                                             |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1824t-i-sl |

TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| IABLE               | <u>5-3.</u> 5         | LOIALI                                | ON CITO                                                                                              | KEGISTI          | LIX SOWIN      | יאולי (טל     | )            | راحا.   |           |                      |                           |

|---------------------|-----------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|------------------|----------------|---------------|--------------|---------|-----------|----------------------|---------------------------|

| Address             | Name                  | Bit 7                                 | Bit 6                                                                                                | Bit 5            | Bit 4          | Bit 3         | Bit 2        | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

| Bank 3              |                       |                                       |                                                                                                      |                  |                |               |              |         |           |                      |                           |

| 180h <sup>(1)</sup> | INDF0                 | Addressing to (not a physic           |                                                                                                      | es contents of   | FSR0H/FSR0     | L to address  | data memory  | 1       |           | xxxx xxxx            | xxxx xxxx                 |

| 181h <sup>(1)</sup> | INDF1                 |                                       | ddressing this location uses contents of FSR1H/FSR1L to address data memory not a physical register) |                  |                |               |              |         |           | xxxx xxxx            | xxxx xxxx                 |

| 182h <sup>(1)</sup> | PCL                   | Program Cou                           | ınter (PC) Lea                                                                                       | st Significant E | Byte           |               |              |         |           | 0000 0000            | 0000 0000                 |

| 183h <sup>(1)</sup> | STATUS                | _                                     | _                                                                                                    | _                | TO             | PD            | Z            | DC      | С         | 1 1000               | q quuu                    |

| 184h <sup>(1)</sup> | FSR0L                 | Indirect Data                         | Memory Addr                                                                                          | ess 0 Low Poir   | nter           | •             | •            | •       | •         | 0000 0000            | uuuu uuuu                 |

| 185h <sup>(1)</sup> | FSR0H                 | Indirect Data                         | Memory Addr                                                                                          | ess 0 High Poi   | nter           |               |              |         |           | 0000 0000            | 0000 0000                 |

| 186h <sup>(1)</sup> | FSR1L                 | Indirect Data                         | Memory Addr                                                                                          | ess 1 Low Poir   | nter           |               |              |         |           | 0000 0000            | uuuu uuuu                 |

| 187h <sup>(1)</sup> | FSR1H                 | Indirect Data                         | Memory Addr                                                                                          | ess 1 High Poi   | nter           |               |              |         |           | 0000 0000            | 0000 0000                 |

| 188h <sup>(1)</sup> | BSR                   | _                                     | _                                                                                                    | _                |                |               | BSR<4:0>     |         |           | 0 0000               | 0 0000                    |

| 189h <sup>(1)</sup> | WREG                  | Working Reg                           | ister                                                                                                |                  |                |               |              |         |           | 0000 0000            | uuuu uuuu                 |

| 18Ah <sup>(1)</sup> | PCLATH                | _                                     | Write Buffer for the upper 7 bits of the Program Counter                                             |                  |                |               |              |         | -000 0000 | -000 0000            |                           |

| 18Bh <sup>(1)</sup> | INTCON                | GIE                                   | PEIE                                                                                                 | TMR0IE           | INTE           | IOCIE         | TMR0IF       | INTF    | IOCIF     | 0000 000x            | 0000 000u                 |

| 18Ch                | ANSELA                | _                                     | _                                                                                                    | _                | ANSA4          | _             | ANSA2        | ANSA1   | ANSA0     | 1 -111               | 1 -111                    |

| 18Dh                | ANSELB <sup>(2)</sup> | _                                     | _                                                                                                    | ANSB5            | ANSB4          | _             | _            | _       | _         | 11                   | 11                        |

| 18Eh                | ANSELC                | ANSC7 <sup>(2)</sup>                  | ANSC6 <sup>(2)</sup>                                                                                 | _                | _              | ANSC3         | ANSC2        | ANSC1   | ANSC0     | 11 1111              | 11 1111                   |

| 18Fh                | _                     | Unimplement                           | ted                                                                                                  |                  | •              |               |              |         |           | _                    | _                         |

| 190h                | _                     | Unimplement                           | ted                                                                                                  |                  |                |               |              |         |           | _                    | _                         |

| 191h                | EEADRL                | EEPROM/Pro                            | ogram Memor                                                                                          | y Address Reg    | ister Low Byte | 9             |              |         |           | 0000 0000            | 0000 0000                 |

| 192h                | EEADRH                | _(4)                                  | EEPROM/Pro                                                                                           | ogram Memory     | Address Reg    | ister High By | te           |         |           | 1000 0000            | 1000 0000                 |

| 193h                | EEDATL                | EEPROM / P                            | rogram Memo                                                                                          | ry Read Data I   | Register Low   | Byte          |              |         |           | xxxx xxxx            | uuuu uuuu                 |

| 194h                | EEDATH                | _                                     | _                                                                                                    | EEPROM / Pr      | ogram Memo     | ry Read Data  | Register Hig | jh Byte |           | xx xxxx              | uu uuuu                   |

| 195h                | EECON1                | EEPGD                                 | CFGS                                                                                                 | LWLO             | FREE           | WRERR         | WREN         | WR      | RD        | 0000 x000            | 0000 q000                 |

| 196h                | EECON2                | EEPROM co                             | ntrol register 2                                                                                     |                  |                |               |              |         |           | 0000 0000            | 0000 0000                 |

| 197h                | _                     | Unimplement                           | ted                                                                                                  |                  |                |               |              |         |           | _                    | _                         |

| 198h                | _                     | Unimplement                           | ted                                                                                                  |                  |                |               |              |         |           | _                    | _                         |

| 199h                | RCREG                 | USART Rece                            | eive Data Regi                                                                                       | ster             |                |               |              |         |           | 0000 0000            | 0000 0000                 |

| 19Ah                | TXREG                 | USART Tran                            | smit Data Reg                                                                                        | ister            |                |               |              |         |           | 0000 0000            | 0000 0000                 |

| 19Bh                | SPBRGL                | Baud Rate Generator Data Register Low |                                                                                                      |                  |                |               |              |         | 0000 0000 | 0000 0000            |                           |

| 19Ch                | SPBRGH                | Baud Rate G                           | enerator Data                                                                                        | Register High    |                |               |              |         |           | 0000 0000            | 0000 0000                 |

| 19Dh                | RCSTA                 | SPEN                                  | RX9                                                                                                  | SREN             | CREN           | ADDEN         | FERR         | OERR    | RX9D      | 0000 000x            | 0000 000x                 |

| 19Eh                | TXSTA                 | CSRC                                  | TX9                                                                                                  | TXEN             | SYNC           | SENDB         | BRGH         | TRMT    | TX9D      | 0000 0010            | 0000 0010                 |

| 19Fh                | BAUDCON               | ABDOVF                                | RCIDL                                                                                                | _                | SCKP           | BRG16         | _            | WUE     | ABDEN     | 01-0 0-00            | 01-0 0-00                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

3: PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

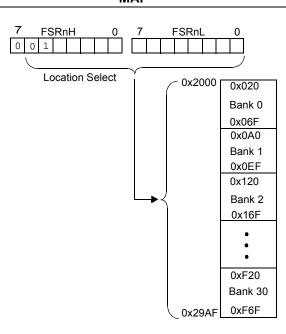

#### 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-10: LINEAR DATA MEMORY MAP

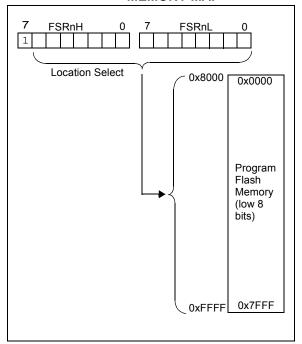

#### 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-11: PROGRAM FLASH MEMORY MAP

# 7.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 7.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting" (DS00607).

### 7.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- BOR is always off

Refer to Table 7-3 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 7-3 for more information.

TABLE 7-1: BOR OPERATING MODES

| BOREN<br>Config bits | SBOREN | Device Mode | BOR Mode | Device<br>Operation upon<br>release of POR | Device<br>Operation upon<br>wake-up from<br>Sleep |

|----------------------|--------|-------------|----------|--------------------------------------------|---------------------------------------------------|

| BOR_ON (11)          | х      | Х           | Active   | Waits for B                                | OR ready <sup>(1)</sup>                           |

| BOR_NSLEEP (10)      | х      | Awake       | Active   | W " ( BOB   I                              |                                                   |

| BOR_NSLEEP (10)      | Х      | Sleep       | Disabled | vvaits for i                               | BOR ready                                         |

| BOR_SBOREN (01)      | 1      | X           | Active   | Begins immediately                         |                                                   |

| BOR_SBOREN (01)      | 0      | X           | Disabled | Begins immediately                         |                                                   |

| BOR_OFF (00)         | х      | X           | Disabled | Begins in                                  | nmediately                                        |

**Note 1:** In these specific cases, "Release of POR" and the "Wake-up from Sleep", there is no delay in start-up. The BOR Ready flag (BORRDY = 1) will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

## 7.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 7.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 7.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### REGISTER 12-15: PORTC: PORTC REGISTER

| R/W-x/u            | R/W-x/u            | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|--------------------|--------------------|---------|---------|---------|---------|---------|---------|

| RC7 <sup>(1)</sup> | RC6 <sup>(1)</sup> | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     |

| bit 7              |                    |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup>

1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: RC<7:6> available on PIC16(L)F1828 only. Otherwise, they are unimplemented and read as '0'.

#### REGISTER 12-16: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits<sup>(1)</sup>

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

Note 1: TRISC<7:6> available on PIC16(L)F1828 only. Otherwise, they are unimplemented and read as '0'.

### REGISTER 12-17: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u              | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| LATC7 <sup>(1)</sup> | LATC6 <sup>(1)</sup> | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1, 2)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

2: LATC<7:6> available on PIC16(L)F1828 only. Otherwise, they are unimplemented and read as '0'.

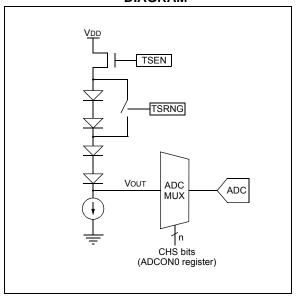

# 15.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between of -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, "Use and Calibration of the Internal Temperature Indicator" (DS01333) for more details regarding the calibration process.

## 15.1 Circuit Operation

Figure 15-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 15-1 describes the output characteristics of the temperature indicator.

## **EQUATION 15-1: VOUT RANGES**

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See Section 14.0 "Fixed Voltage Reference (FVR)" for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register (Register 14-1). When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

FIGURE 15-1: TEMPERATURE CIRCUIT DIAGRAM

# 15.2 Minimum Operating VDD vs. Minimum Sensing Temperature

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 15-1 shows the recommended minimum VDD vs. range setting.

TABLE 15-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

### 15.3 Temperature Output

The output of the circuit is measured using the internal analog-to-digital converter. A channel is reserved for the temperature circuit output. Refer to **Section 16.0** "Analog-to-Digital Converter (ADC) Module" for detailed information.

## 15.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu s$  after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu s$  between sequential conversions of the temperature indicator output.

#### 16.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 16.3 "A/D Acquisition Requirements".

#### **EXAMPLE 16-1: A/D CONVERSION**

```

; This code block configures the ADC

; for polling, Vdd and Vss references, Frc

; clock and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

B'11110000' ;Right justify, Frc

MOVLW

;clock

MOVWF

ADCON1

;Vdd and Vss Vref

BANKSEL TRISA

BSF

TRISA,0 ;Set RAO to input

BANKSEL ANSEL

BSF

ANSEL,0 ;Set RAO to analog

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

;Turn ADC On

MOVWE

ADCON0

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

ADRESH

BANKSEL

ADRESH,W ;Read upper 2 bits

MOVF

RESULTHI

MOVWF

;store in GPR space

BANKSEL

ADRESL

ADRESL,W

MOVF

;Read lower 8 bits

RESULTLO ;Store in GPR space

MOVWF

```

# REGISTER 16-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| _       | _       | _       | _       | _       | _       | ADRE    | S<9:8>  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared

bit 7-2 **Reserved**: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits

Upper two bits of 10-bit conversion result

### REGISTER 16-6: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| ADRES<7:0> |         |         |         |         |         |         |         |  |

| bit 7 bit  |         |         |         |         |         |         |         |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 ADRES<7:0>: ADC Result Register bits

Lower eight bits of 10-bit conversion result

## 21.11 Timer1 Control Registers

#### REGISTER 21-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u                 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | U-0 | R/W-0/u |

|-------------------------|---------|---------|---------|---------|---------|-----|---------|

| TMR1CS<1:0> T1CKPS<1:0> |         | T10SCEN | T1SYNC  | _       | TMR10N  |     |         |

| bit 7                   |         |         |         |         |         |     | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 TMR1CS<1:0>: Timer1 Clock Source Select bits

11 = Timer1 clock source is Capacitive Sensing Oscillator (CAPOSC)

10 = Timer1 clock source is pin or oscillator:

If T10SCEN = 0:

External clock from T1CKI pin (on the rising edge)

If T1OSCEN =  $\underline{1}$ :

Crystal oscillator on T1OSI/T1OSO pins 01 = Timer1 clock source is system clock (Fosc)

00 = Timer1 clock source is instruction clock (Fosc/4)

bit 5-4 T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value

T10SCEN: LP Oscillator Enable Control bit

1 = Dedicated Timer1 oscillator circuit enabled0 = Dedicated Timer1 oscillator circuit disabled

bit 2 T1SYNC: Timer1 Synchronization Control bit

1 = Do not synchronize synchronous clock input

0 = Synchronize asynchronous clock input with system clock (Fosc)

bit 1 **Unimplemented:** Read as '0'

bit 0 TMR1ON: Timer1 On bit

bit 3

1 = Enables Timer1

0 = Stops Timer1 and clears Timer1 gate flip-flop

#### 24.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 24-4.

### **EQUATION 24-4: PWM RESOLUTION**

Resolution =

$$\frac{log[4(PRx+1)]}{log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# TABLE 24-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

# TABLE 24-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 24-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### REGISTER 24-1: CCPxCON: CCPx CONTROL REGISTER

| R/W-00                            | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------------------|---------|------------|---------|---------|---------|---------|---------|

| PxM<1:0> <sup>(1)</sup> DCxB<1:0> |         | CCPxM<3:0> |         |         |         |         |         |

| bit 7                             |         |            |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset

'1' = Bit is set '0' = Bit is cleared

bit 7-6 PxM<1:0>: Enhanced PWM Output Configuration bits<sup>(1)</sup>

Capture mode:

Unused

Compare mode:

Unused

If CCPxM<3:2> = 00, 01, 10:

xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins

If CCPxM<3:2> = 11:

00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins

01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive

10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins

11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive

bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits

Capture mode:

Unused

Compare mode:

Unused

PWM mode

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0 CCPxM<3:0>: ECCPx Mode Select bits

0000 = Capture/Compare/PWM off (resets ECCPx module)

0001 = Reserved

0010 = Compare mode: toggle output on match

0011 = Reserved

0100 = Capture mode: every falling edge

0101 = Capture mode: every rising edge

0110 = Capture mode: every 4th rising edge

0111 = Capture mode: every 16th rising edge

1000 = Compare mode: initialize ECCPx pin low; set output on compare match (set CCPxIF)

1001 = Compare mode: initialize ECCPx pin high; clear output on compare match (set CCPxIF)

1010 = Compare mode: generate software interrupt only; ECCPx pin reverts to I/O state

1011 = Compare mode: Special Event Trigger (ECCPx resets Timer, sets CCPxIF bit, starts A/D conversion if A/D module is enabled)<sup>(1)</sup>

#### CCP Modules only:

11xx = PWM mode

### ECCP modules only:

1100 = PWM mode: PxA, PxC active-high; PxB, PxD active-high

1101 = PWM mode: PxA, PxC active-high; PxB, PxD active-low

1110 = PWM mode: PxA, PxC active-low; PxB, PxD active-high

1111 = PWM mode: PxA, PxC active-low; PxB, PxD active-low

Note 1: These bits are not implemented on CCP3 or CCP4.

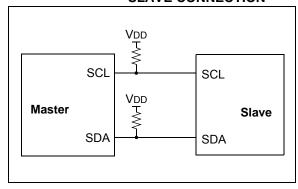

#### 25.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus (I²C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- · Serial Data (SDA)

Figure 25-2 and Figure 25-3 shows the block diagram of the MSSP1 module when operating in I<sup>2</sup>C Mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 25-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

FIGURE 25-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last  $\overline{ACK}$  bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### 25.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge ( $\overline{ACK}$ ) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an ACK is placed in the ACKSTAT bit of the SSP1CON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overline{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSP1CON2 register is set/cleared to determine the response.

Slave hardware will generate an  $\overline{ACK}$  response if the AHEN and DHEN bits of the SSP1CON3 register are clear

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSP1STAT register or the SSPOV bit of the SSP1CON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCL on the bus, the ACKTIM bit of the SSP1CON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

### 25.5 I<sup>2</sup>C Slave Mode Operation

The MSSP1 Slave mode operates in one of four modes selected in the SSP1M bits of SSP1CON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSP1IF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 25.5.1 SLAVE MODE ADDRESSES

The SSP1ADD register (Register 25-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSP1BUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 25-5) affects the address matching process. See **Section 25.5.9** "**SSP1 Mask Register**" for more information.

# 25.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

# 25.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSP1ADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSP1ADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSP1ADD. Even if there is not an address match; SSP1IF and UA are set, and SCL is held low until SSP1ADD is updated to receive a high byte again. When SSP1ADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the  $R/\overline{W}$  bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

# 25.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP1 module configured as an I<sup>2</sup>C Slave in 10-bit Addressing mode.

Figure 25-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- Bus starts Idle.

- Master sends Start condition; S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSP1STAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- Software reads received address from SSP1BUF clearing the BF flag.

- Slave loads low address into SSP1ADD, releasing SCL.

- Master sends matching low address byte to the Slave; UA bit is set.

**Note:** Updates to the SSP1ADD register are not allowed until after the ACK sequence.

Slave sends ACK and SSP1IF is set.

**Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSP1ADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- Slave reads the received matching address from SSP1BUF clearing BF.

- 12. Slave loads high address into SSP1ADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSP1CON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- Slave reads the received byte from SSP1BUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

# 25.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSP1ADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 25-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 25-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVWI ++INDFn<br>[ label ] MOVWIINDFn<br>[ label ] MOVWI INDFn++<br>[ label ] MOVWI INDFn<br>[ label ] MOVWI k[FSRn]                                                                                                           |

| Operands:        | $n \in [0,1]$<br>-32 \le k \le 31                                                                                                                                                                                                        |

| Operation:       | W → INDFn Effective address is determined by • FSR + 1 (preincrement) • FSR - 1 (predecrement) • FSR + k (relative offset) After the Move, the FSR value will be either: • FSR + 1 (all increments) • FSR - 1 (all decrements) Unchanged |

| Status Affected: | None                                                                                                                                                                                                                                     |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h - FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP                                      | No Operation                                                                                                                 |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                  | [ label ] NOP                                                                                                                |

| Operands:                                | None                                                                                                                         |

| Operation:                               | No operation                                                                                                                 |

| Status Affected:                         | None                                                                                                                         |

| Description:                             | No operation.                                                                                                                |

| Words:                                   | 1                                                                                                                            |

| Cycles:                                  | 1                                                                                                                            |

| Example:                                 | NOP                                                                                                                          |

| Syntax:                                  | [ label ] OPTION                                                                                                             |

| Syntax:                                  | [ label ] OPTION                                                                                                             |

| Operands:                                | None                                                                                                                         |

| Operarius.                               | None                                                                                                                         |

| Operation:                               | $(W) \rightarrow OPTION\_REG$                                                                                                |

| •                                        |                                                                                                                              |

| Operation:                               | $(W) \rightarrow OPTION\_REG$                                                                                                |

| Operation:<br>Status Affected:           | <ul><li>(W) → OPTION_REG</li><li>None</li><li>Move data from W register to</li></ul>                                         |

| Operation:<br>Status Affected:           | <ul><li>(W) → OPTION_REG</li><li>None</li><li>Move data from W register to</li></ul>                                         |

| Operation: Status Affected: Description: | <ul> <li>(W) → OPTION_REG</li> <li>None</li> <li>Move data from W register to OPTION_REG register.</li> </ul>                |

| Operation: Status Affected: Description: | <ul> <li>(W) → OPTION_REG</li> <li>None</li> <li>Move data from W register to OPTION_REG register.</li> </ul> Software Reset |

| RESET            | Software Reset                                                           |

|------------------|--------------------------------------------------------------------------|

| Syntax:          | [ label ] RESET                                                          |

| Operands:        | None                                                                     |

| Operation:       | Execute a device Reset. Resets the nRI flag of the PCON register.        |

| Status Affected: | None                                                                     |

| Description:     | This instruction provides a way to execute a hardware Reset by software. |

| RETFIE           | Return from Interrupt                                                                                                                                                                            |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                 |  |  |  |  |

| Operands:        | None                                                                                                                                                                                             |  |  |  |  |

| Operation:       | $TOS \rightarrow PC,$ $1 \rightarrow GIE$                                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed and Top-of-Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a 2-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                           |  |  |  |  |

|                  | After Interrupt PC = TOS GIE = 1                                                                                                                                                                 |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                               |

| Operands:        | None                                                                                                                                         |

| Operation:       | $TOS \to PC$                                                                                                                                 |

| Status Affected: | None                                                                                                                                         |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a 2-cycle instruction. |

|                  |                                                                                                                                              |

|                  |                                                                                                                                              |

| RETLW            | Return with literal in W                                                                                                                                          |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETLW k                                                                                                                                                   |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                               |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                              |  |  |  |  |

| Description:     | The W register is loaded with the 8-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a 2-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                 |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                 |  |  |  |  |

| Example:         | CALL TABLE;W contains table ;offset value • ;W now has table value                                                                                                |  |  |  |  |

| TABLE            | ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;  RETLW k1 ; End of table                                                                                    |  |  |  |  |

|                  | Before Instruction $W = 0x07$                                                                                                                                     |  |  |  |  |

After Instruction

W =

value of k8

| RLF              | Rotate Left f through Carry                                                                                                                                                                           |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] RLF f,d                                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                     |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                     |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                     |  |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                            |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                 |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                       |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | After Instruction  REG1 = 1110 0110                                                                                                                                                                   |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                     |  |  |  |  |  |  |

#### **TABLE 30-2: OSCILLATOR PARAMETERS**

Standard Operating Conditions (unless otherwise stated) Operating Temperature  $-40^{\circ}C \leq TA \leq +125^{\circ}C$ Param Freq. Svm. Characteristic Min. Typ† Max. Units **Conditions** No. **Tolerance OS08** Internal Calibrated HFINTOSC  $0^{\circ}C \le TA \le +60^{\circ}C, VDD \ge 2.5V$ **HFosc** ±2% 16.0 MHz Frequency<sup>(1)</sup>  $60^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}, \text{ VDD} \ge 2.5\text{V}$ ±3% 16.0 MHz ±5% -40°C  $\leq$  TA  $\leq$  +125°C 16.0 MHz OS08A MFosc Internal Calibrated MFINTOSC 500  $0^{\circ}C \le TA \le +60^{\circ}C$ ,  $VDD \ge 2.5V$ ±2% kHz Frequency<sup>(1)</sup> ±3% 500 kHz  $60^{\circ}C \le TA \le +85^{\circ}C, \ VDD \ge 2.5V$ ±5% 500 kHz -40°C ≤ TA ≤ +125°C OS09 **LFosc** Internal LFINTOSC Frequency -40°C ≤ TA ≤ +125°C ±25% 31 kHz OS10\* Tiosc st **HFINTOSC** 5 8  $\mu \textbf{S}$ Wake-up from Sleep Start-up Time **MFINTOSC** Wake-up from Sleep Start-up Time 20 30 μS

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible.  $0.1~\mu F$  and  $0.01~\mu F$  values in parallel are recommended.

#### TABLE 30-3: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.7V to 5.5V)

| Param<br>No. | Sym.         | Characteristic                | Min.   | Тур† | Max.   | Units | Conditions |

|--------------|--------------|-------------------------------|--------|------|--------|-------|------------|

| F10          | Fosc         | Oscillator Frequency Range    | 4      |      | 8      | MHz   |            |

| F11          | Fsys         | On-Chip VCO System Frequency  | 16     | _    | 32     | MHz   |            |

| F12          | Trc          | PLL Start-up Time (Lock Time) | _      | _    | 2      | ms    |            |

| F13*         | $\Delta$ CLK | CLKOUT Stability (Jitter)     | -0.25% | _    | +0.25% | %     |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>†</sup> Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

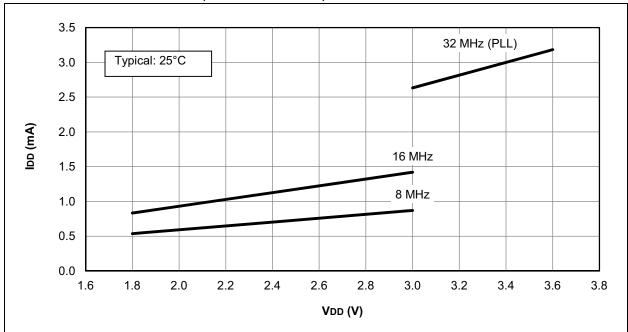

FIGURE 31-16: IDD MAXIMUM, HFINTOSC MODE, PIC16LF1824/8 ONLY

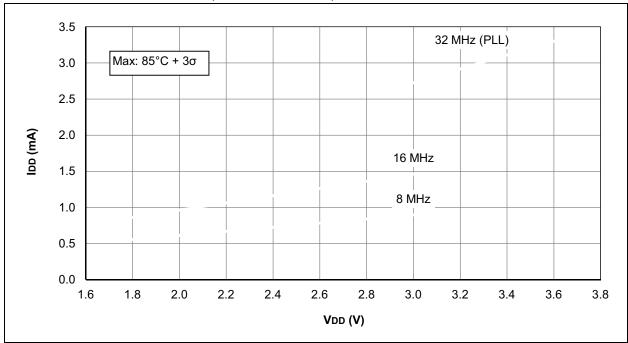

FIGURE 31-47: POR RELEASE VOLTAGE

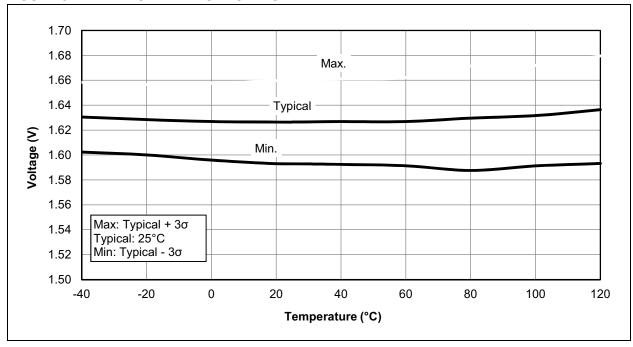

FIGURE 31-48: POR REARM VOLTAGE, PIC16F1824/8 ONLY

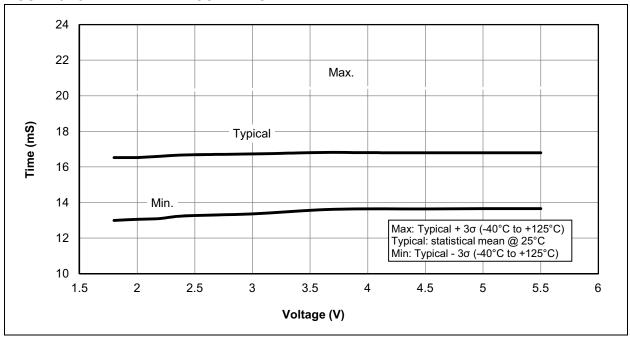

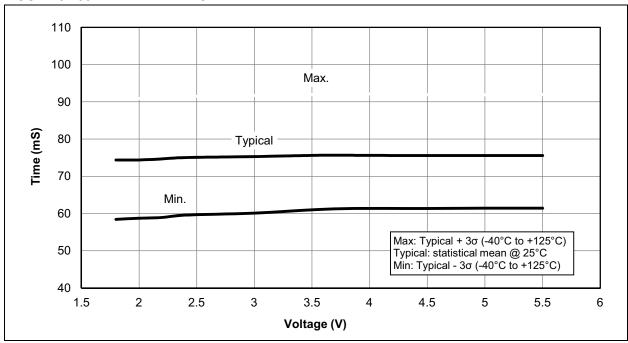

FIGURE 31-52: WDT TIME-OUT PERIOD

FIGURE 31-53: PWRT PERIOD

## 33.0 PACKAGING INFORMATION

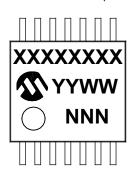

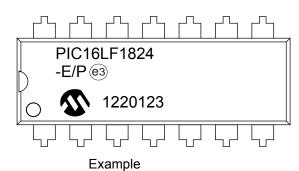

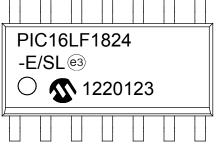

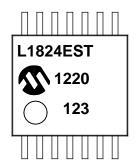

# 33.1 Package Marking Information

14-Lead PDIP (300 mil)

14-Lead SOIC (3.90 mm)

14-Lead TSSOP (4.4 mm)

# Example

\_ \_

Example

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.