Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 11                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1824t-i-st |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

| Note: | The DEBUG bit in Configuration Word is      |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

| IGURE 5-7:               | INTERNAL OSCILLATOR SWITCH TIMING                                    |

|--------------------------|----------------------------------------------------------------------|

|                          |                                                                      |

| 3598709C/                | LFINTOSC (FBCM and WOT (Faahlad)                                     |

| HFINTOSC/                | Circiliance Onlay <sup>201</sup> Scopela Sync                        |

| LFINTOSC                 |                                                                      |

| IRCF <3:0>               | $\neq 0$ $\chi = 0$                                                  |

| System Clock             |                                                                      |

| < 1012X (2010) (2010)    |                                                                      |

| 20730100500<br>207201050 | LFW/TCCC (EXher FCCM of WDT shebied)                                 |

| HFINTOSC/                |                                                                      |

| LFINTOSC                 |                                                                      |

| IRCF <3:0>               | $\neq 0$ $\chi = 0$                                                  |

| System Clock             |                                                                      |

| s ann an an ar ar        |                                                                      |

| 1.8.813 (1973/9»-        | EFINITOSCIMPINITOSC<br>LEINITOSCI uma difumista WET or ESCRE anabist |

| 08999030                 |                                                                      |

| BENTOSO/<br>MENTOSO      |                                                                      |

| \$P.CF <3:0>             |                                                                      |

| System Clock             |                                                                      |

| Soie to See              | Table 5-1, "Oscillutor Switching Delays" for more information.       |

### 9.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 7.10 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

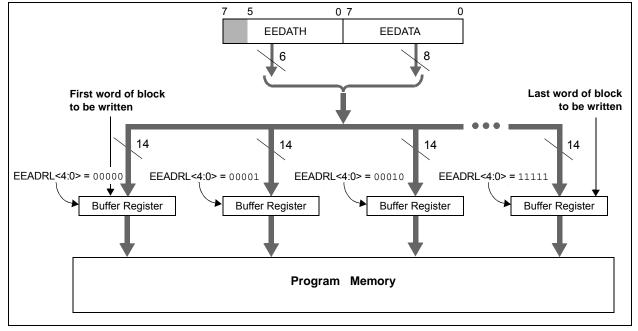

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the write operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2ms, only during the cycle in which the write takes place (i.e., the last word of the block write). This is not Sleep mode, as the clocks and peripherals will

continue to run. The processor does not stall when LWLO = 1, loading the write latches. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

### 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | LEEDATL    | ;                    |

|---------|------------|----------------------|

| MOVF    | EEDATL, W  | ;EEDATL not changed  |

|         |            | ;from previous write |

| BSF     | EECON1, RD | ;YES, Read the       |

|         |            | ;value written       |

| XORWF   | EEDATL, W  | ;                    |

| BTFSS   | STATUS, Z  | ;Is data the same    |

| GOTO    | WRITE_ERR  | ;No, handle error    |

| :       |            | ;Yes, continue       |

| 1       |            |                      |

| U-0                                                                  | U-0   | R/W-x/u                                                       | R/W-x/u | U-0         | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------------------------------------------------------|-------|---------------------------------------------------------------|---------|-------------|---------|---------|---------|

| _                                                                    | —     | LATA5                                                         | LATA4   |             | LATA2   | LATA1   | LATA0   |

| bit 7                                                                | •     |                                                               |         |             |         | •       | bit 0   |

|                                                                      |       |                                                               |         |             |         |         |         |

| Legend:                                                              |       |                                                               |         |             |         |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                                                               |         |             |         |         |         |

| u = Bit is uncha                                                     | anged | x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |         | ther Resets |         |         |         |

| '1' = Bit is set                                                     |       | '0' = Bit is clea                                             | ared    |             |         |         |         |

| bit 7-6 | Unimplemented: Read as '0                                 |

|---------|-----------------------------------------------------------|

| bit 5-4 | LATA<5:4>: RA<5:4> Output Latch Value bits <sup>(1)</sup> |

| bit 3   | Unimplemented: Read as '0                                 |

| bit 2-0 | LATA<2:0>: RA<2:0> Output Latch Value bits <sup>(1)</sup> |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

### REGISTER 12-6: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   | _   | ANSA4   | _   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on pins RA4, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul>                     |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to                                                                                                                                                                                                           |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| U-0 <sup>(3)</sup><br>R/W-1/1 <sup>(2)</sup> | U-0 <sup>(3)</sup><br>R/W-1/1 <sup>(2)</sup> | R/W-0/0 <b>(3)</b><br>R/W-1/1 <b>(2)</b> | R/W-0/0 <sup>(3)</sup><br>R/W-1/1 <sup>(2)</sup> | R/W-0/0 <b>(3)</b><br>R/W-1/1 <b>(2)</b> | R/W-0/0 <b>(3)</b><br>R/W-1/1 <b>(2)</b> | R/W-0/0 <b>(3)</b><br>R/W-1/1 <b>(2)</b> | R/W-0/0 <sup>(3)</sup><br>R/W-1/1 <sup>(2)</sup> |

|----------------------------------------------|----------------------------------------------|------------------------------------------|--------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|--------------------------------------------------|

| INLVLC7 <sup>(1)</sup>                       | INLVLC6 <sup>(1)</sup>                       | INLVLC5                                  | INLVLC4                                          | INLVLC3                                  | INLVLC2                                  | INLVLC1                                  | INLVLC0                                          |

| bit 7                                        | •                                            |                                          |                                                  |                                          |                                          | •                                        | bit 0                                            |

|                                              |                                              |                                          |                                                  |                                          |                                          |                                          |                                                  |

### REGISTER 12-20: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits<sup>(1)</sup> For RC<7:0> pins, respectively 1 = ST input used for PORT reads and Interrupt-on-Change 0 = TTL input used for PORT reads and Interrupt-on-Change

Note 1: INLVLC<7:6> available on PIC16(L)F1828 only. Otherwise, they are unimplemented and read as '0'.

- **2:** PIC16(L)F1828 only, Reset default value.

- 3: PIC16(L)F1824 only, Reset default value.

### TABLE 12-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELC | ANSC7(1)               | ANSC6 <sup>(1)</sup>   | _       | _       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 133                 |

| INLVLC | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 134                 |

| LATC   | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 132                 |

| PORTC  | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 132                 |

| TRISC  | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 132                 |

| WPUC   | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 133                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations, read as '0'. Shaded cells are not used by PORTC. Note 1: PIC16(L)F1828 only.

### 16.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 16.3 "A/D Acquisition Requirements".

### EXAMPLE 16-1: A/D CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, Frc ;clock and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;Right justify, Frc MOVLW ;clock MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL ADCON0 B'00000001' ;Select channel ANO MOVLW ;Turn ADC On MOVWE ADCON0 SampleTime ; Acquisiton delay CALL ADCON0, ADGO ; Start conversion BSF BTFSC ADCON0, ADGO ; Is conversion done? GOTO \$-1 ;No, test again ADRESH ; BANKSEL ADRESH,W ;Read upper 2 bits MOVF RESULTHI MOVWF ;store in GPR space BANKSEL ADRESL ; ADRESL,W MOVF ;Read lower 8 bits RESULTLO ;Store in GPR space MOVWE

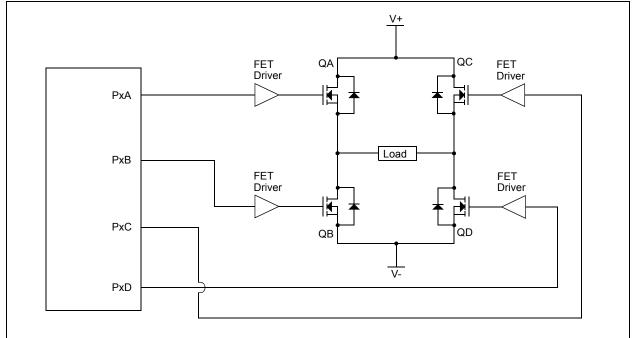

### 24.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 24-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 24-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 24-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

FIGURE 24-10: EXAMPLE OF FULL-BRIDGE APPLICATION

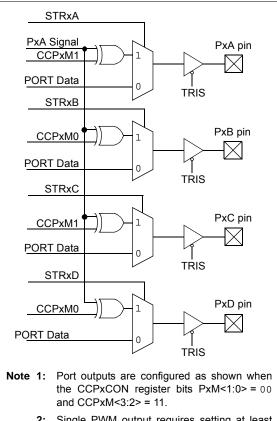

### 24.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCPxM<3:2> = 11 and PxM<1:0> = 00 of the CCPxCON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STRx<D:A> bits of the PSTRxCON register, as shown in Table 24-9.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCPxM<1:0> bits of the CCPxCON register select the PWM output polarity for the Px<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 24.4.3 "Enhanced PWM Auto-shutdown mode"**. An autoshutdown event will only affect pins that have PWM outputs enabled.

FIGURE 24-18: SIMPLIFIED STEERING BLOCK DIAGRAM

**2:** Single PWM output requires setting at least one of the STRx bits.

### 25.7 Baud Rate Generator

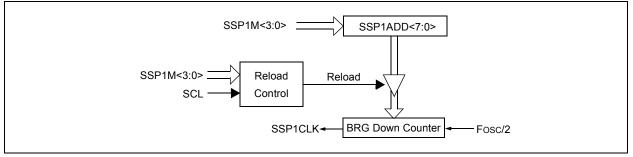

The MSSP1 module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSP1ADD register (Register 25-6). When a write occurs to SSP1BUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 25-40 triggers the value from SSP1ADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP1 is being operated in.

Table 25-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSP1ADD.

#### **EQUATION 25-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

### FIGURE 25-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSP1ADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

### TABLE 25-4: MSSP1 CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical and timing specifications in Table 30-4 and Figure 30-7 to ensure the system is designed to support the I/O requirements.

### TABLE 26-3: BAUD RATE FORMULAS

| Configuration Bits |       |      |                     | Boud Boto Formula |  |  |

|--------------------|-------|------|---------------------|-------------------|--|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula |  |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  |                   |  |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                   |  |  |

| 1                  | 0     | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |  |

| 1                  | 1     | x    | 16-bit/Synchronous  |                   |  |  |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair

### TABLE 26-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF | RCIDL | _     | SCKP  | BRG16 | —     | WUE   | ABDEN | 296                 |

| RCSTA   | SPEN   | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 295                 |

| SPBRGL  | BRG7   | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 297*                |

| SPBRGH  | BRG15  | BRG14 | BRG13 | BRG12 | BRG11 | BRG10 | BRG9  | BRG8  | 297*                |

| TXSTA   | CSRC   | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 294                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

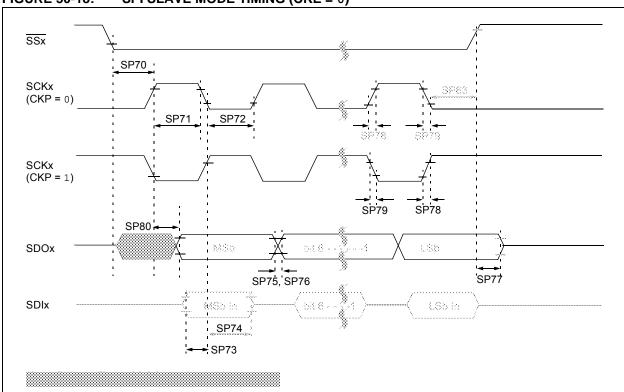

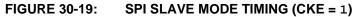

### FIGURE 30-18: SPI SLAVE MODE TIMING (CKE = 0)

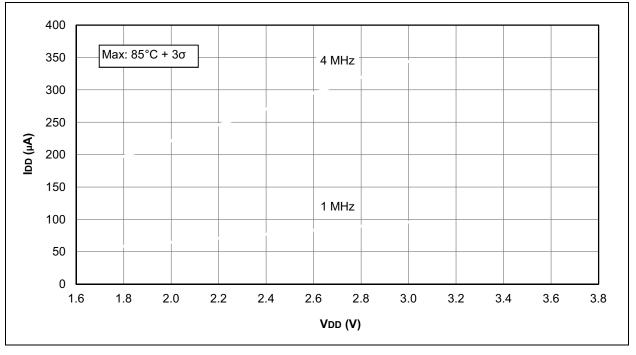

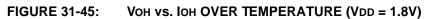

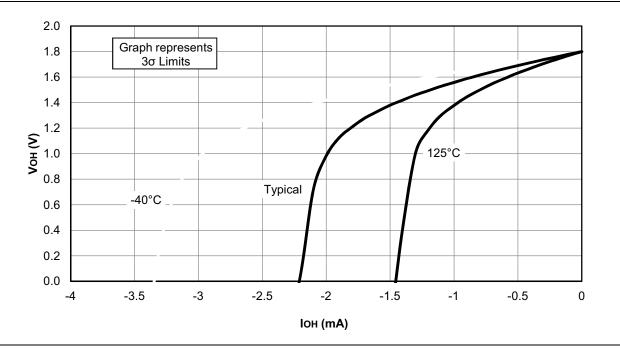

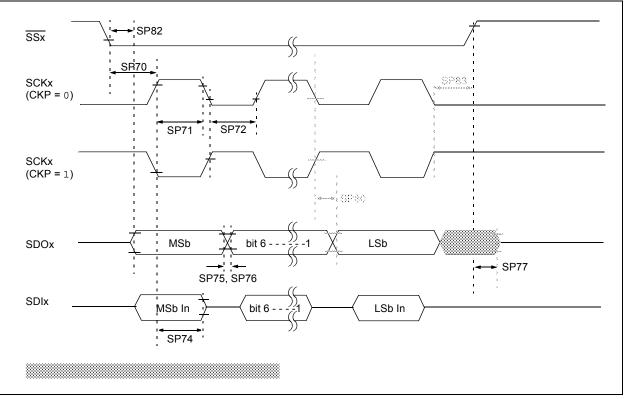

## 31.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

FIGURE 31-8: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1824/8 ONLY