Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1828-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

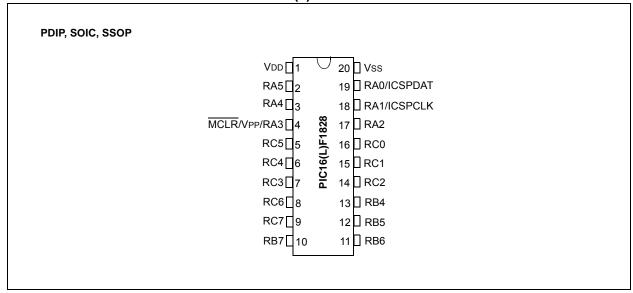

#### FIGURE 3: 20-PIN DIAGRAM FOR PIC16(L)F1828

## TABLE 3-6: PIC16(L)F1824/8 MEMORY MAP, BANKS 16-23

|      | BANK 16       | •    | BANK 17       |      | BANK 18       |      | BANK 19       |      | BANK 20       |      | BANK 21       |      | BANK 22       |      | BANK 23       |

|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|------|---------------|

| 800h | INDF0         | 880h | INDF0         | 900h | INDF0         | 980h | INDF0         | A00h | INDF0         | A80h | INDF0         | B00h | INDF0         | B80h | INDF0         |

| 801h | INDF1         | 881h | INDF1         | 901h | INDF1         | 981h | INDF1         | A01h | INDF1         | A81h | INDF1         | B01h | INDF1         | B81h | INDF1         |

| 802h | PCL           | 882h | PCL           | 902h | PCL           | 982h | PCL           | A02h | PCL           | A82h | PCL           | B02h | PCL           | B82h | PCL           |

| 803h | STATUS        | 883h | STATUS        | 903h | STATUS        | 983h | STATUS        | A03h | STATUS        | A83h | STATUS        | B03h | STATUS        | B83h | STATUS        |

| 804h | FSR0L         | 884h | FSR0L         | 904h | FSR0L         | 984h | FSR0L         | A04h | FSR0L         | A84h | FSR0L         | B04h | FSR0L         | B84h | FSR0L         |

| 805h | FSR0H         | 885h | FSR0H         | 905h | FSR0H         | 985h | FSR0H         | A05h | FSR0H         | A85h | FSR0H         | B05h | FSR0H         | B85h | FSR0H         |

| 806h | FSR1L         | 886h | FSR1L         | 906h | FSR1L         | 986h | FSR1L         | A06h | FSR1L         | A86h | FSR1L         | B06h | FSR1L         | B86h | FSR1L         |

| 807h | FSR1H         | 887h | FSR1H         | 907h | FSR1H         | 987h | FSR1H         | A07h | FSR1H         | A87h | FSR1H         | B07h | FSR1H         | B87h | FSR1H         |

| 808h | BSR           | 888h | BSR           | 908h | BSR           | 988h | BSR           | A08h | BSR           | A88h | BSR           | B08h | BSR           | B88h | BSR           |

| 809h | WREG          | 889h | WREG          | 909h | WREG          | 989h | WREG          | A09h | WREG          | A89h | WREG          | B09h | WREG          | B89h | WREG          |

| 80Ah | PCLATH        | 88Ah | PCLATH        | 90Ah | PCLATH        | 98Ah | PCLATH        | A0Ah | PCLATH        | A8Ah | PCLATH        | B0Ah | PCLATH        | B8Ah | PCLATH        |

| 80Bh | INTCON        | 88Bh | INTCON        | 90Bh | INTCON        | 98Bh | INTCON        | A0Bh | INTCON        | A8Bh | INTCON        | B0Bh | INTCON        | B8Bh | INTCON        |

| 80Ch | _             | 88Ch |               | 90Ch | —             | 98Ch | _             | A0Ch | _             | A8Ch | _             | B0Ch | -             | B8Ch | _             |

| 80Dh | —             | 88Dh | -             | 90Dh | —             | 98Dh | —             | A0Dh | —             | A8Dh | —             | B0Dh | -             | B8Dh | _             |

| 80Eh | —             | 88Eh | —             | 90Eh | —             | 98Eh | _             | A0Eh | —             | A8Eh | —             | B0Eh | —             | B8Eh |               |

| 80Fh | —             | 88Fh | -             | 90Fh | —             | 98Fh | —             | A0Fh | —             | A8Fh | —             | B0Fh | -             | B8Fh | _             |

| 810h | —             | 890h | —             | 910h | _             | 990h | _             | A10h | —             | A90h | —             | B10h | —             | B90h | —             |

| 811h | —             | 891h | —             | 911h | _             | 991h | _             | A11h | —             | A91h | —             | B11h | —             | B91h | —             |

| 812h | _             | 892h | _             | 912h | _             | 992h |               | A12h | —             | A92h | —             | B12h | —             | B92h |               |

| 813h | —             | 893h | _             | 913h |               | 993h | -             | A13h | —             | A93h | —             | B13h | _             | B93h |               |

| 814h | _             | 894h | _             | 914h |               | 994h |               | A14h | —             | A94h | —             | B14h | _             | B94h | —             |

| 815h | —             | 895h | _             | 915h | _             | 995h | _             | A15h | —             | A95h | —             | B15h | —             | B95h | _             |

| 816h | —             | 896h | —             | 916h | _             | 996h | —             | A16h | —             | A96h | —             | B16h | —             | B96h | —             |

| 817h | —             | 897h | _             | 917h |               | 997h |               | A17h | —             | A97h | _             | B17h | _             | B97h | —             |

| 818h | —             | 898h | _             | 918h |               | 998h |               | A18h | —             | A98h | _             | B18h | _             | B98h | —             |

| 819h | —             | 899h | _             | 919h |               | 999h | -             | A19h | —             | A99h | —             | B19h | _             | B99h |               |

| 81Ah | _             | 89Ah | _             | 91Ah |               | 99Ah | _             | A1Ah | —             | A9Ah | —             | B1Ah | _             | B9Ah | _             |

| 81Bh | _             | 89Bh | _             | 91Bh |               | 99Bh |               | A1Bh | —             | A9Bh | —             | B1Bh | _             | B9Bh | —             |

| 81Ch | —             | 89Ch | _             | 91Ch |               | 99Ch |               | A1Ch | —             | A9Ch | _             | B1Ch | _             | B9Ch | —             |

| 81Dh | _             | 89Dh | _             | 91Dh |               | 99Dh | _             | A1Dh | —             | A9Dh | _             | B1Dh | _             | B9Dh | —             |

| 81Eh | _             | 89Eh | _             | 91Eh |               | 99Eh | _             | A1Eh | —             | A9Eh | _             | B1Eh | _             | B9Eh | —             |

| 81Fh | —             | 89Fh | —             | 91Fh | _             | 99Fh | —             | A1Fh | —             | A9Fh | —             | B1Fh | —             | B9Fh | —             |

| 820h |               | 8A0h |               | 920h |               | 9A0h |               | A20h |               | AA0h |               | B20h |               | BA0h |               |

|      |               |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

|      | Unimplemented |

|      | Read as '0'   |

|      |               |      |               |      |               |      |               |      |               |      |               |      |               |      |               |

| 86Fh |               | 8EFh |               | 96Fh |               | 9EFh |               | A6Fh |               | AEFh |               | B6Fh |               | BEFh |               |

| 870h |               | 8F0h |               | 970h |               | 9F0h |               | A70h |               | AF0h |               | B70h |               | BF0h |               |

|      | Accesses      |

|      | 70h – 7Fh     |

| 87Fh |               | 8FFh |               | 97Fh |               | 9FFh |               | A7Fh |               | AFFh |               | B7Fh |               | BFFh |               |

**Legend:** = Unimplemented data memory locations, read as '0'.

| TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |        |                                  |                                            |                  |                 |              |             |       |       |                      |                                 |  |

|----------------------------------------------------------|--------|----------------------------------|--------------------------------------------|------------------|-----------------|--------------|-------------|-------|-------|----------------------|---------------------------------|--|

| Address                                                  | Name   | Bit 7                            | Bit 6                                      | Bit 5            | Bit 4           | Bit 3        | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |

| Banks 9                                                  | 9-30   |                                  |                                            |                  |                 |              |             |       |       |                      |                                 |  |

| x00h/<br>x80h <sup>(1)</sup>                             | INDF0  | Addressing th<br>(not a physical |                                            | es contents of   | FSR0H/FSR0      | L to address | data memory | /     |       | XXXX XXXX            | XXXX XXXX                       |  |

| x00h/<br>x81h <sup>(1)</sup>                             | INDF1  | Addressing th<br>(not a physical |                                            | es contents of   | FSR1H/FSR1      | L to address | data memory | 1     |       | XXXX XXXX            | XXXX XXXX                       |  |

| x02h/<br>x82h <sup>(1)</sup>                             | PCL    | Program Cou                      | inter (PC) Lea                             | st Significant B | yte             |              |             |       |       | 0000 0000            | 0000 0000                       |  |

| x03h/<br>x83h <sup>(1)</sup>                             | STATUS | _                                |                                            |                  |                 |              |             |       |       | 1 1000               | q quuu                          |  |

| x04h/<br>x84h <sup>(1)</sup>                             | FSR0L  | Indirect Data                    | ndirect Data Memory Address 0 Low Pointer  |                  |                 |              |             |       |       |                      |                                 |  |

| x05h/<br>x85h <b>(1)</b>                                 | FSR0H  | Indirect Data                    | ndirect Data Memory Address 0 High Pointer |                  |                 |              |             |       |       |                      |                                 |  |

| x06h/<br>x86h <sup>(1)</sup>                             | FSR1L  | Indirect Data                    | Memory Addr                                | ess 1 Low Poir   | nter            |              |             |       |       | 0000 0000            | uuuu uuuu                       |  |

| x07h/<br>x87h <sup>(1)</sup>                             | FSR1H  | Indirect Data                    | Memory Addr                                | ess 1 High Poi   | nter            |              |             |       |       | 0000 0000            | 0000 0000                       |  |

| x08h/<br>x88h <b>(1)</b>                                 | BSR    | —                                | _                                          | —                |                 |              | BSR<4:0>    |       |       | 0 0000               | 0 0000                          |  |

| x09h/<br>x89h <sup>(1)</sup>                             | WREG   | Working Reg                      | ister                                      |                  |                 |              |             |       |       | 0000 0000            | uuuu uuuu                       |  |

| x0Ah/<br>x8Ah <sup>(1)</sup>                             | PCLATH | —                                | Write Buffer f                             | or the upper 7   | bits of the Pro | ogram Counte | er          |       |       | -000 0000            | -000 0000                       |  |

| x0Bh/<br>x8Bh <b>(1)</b>                                 | INTCON | GIE                              | PEIE                                       | TMR0IE           | INTE            | IOCIE        | TMR0IF      | INTF  | IOCIF | 0000 000x            | 0000 000u                       |  |

| x0Ch/<br>x8Ch                                            | _      | Unimplement                      | ed                                         |                  |                 |              |             |       |       | _                    | -                               |  |

| x1Fh/<br>x9Fh                                            |        |                                  |                                            |                  |                 |              |             |       |       |                      |                                 |  |

#### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$Legend: \quad x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. \\ Shaded locations are unimplemented, read as '0'.$

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

**3:** PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

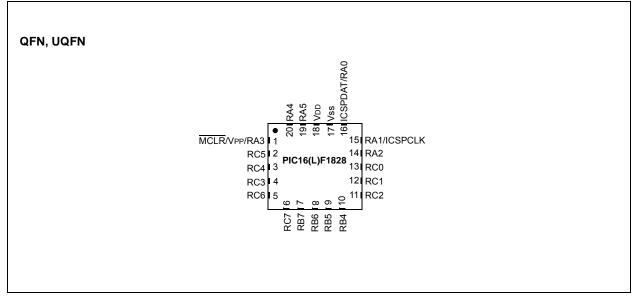

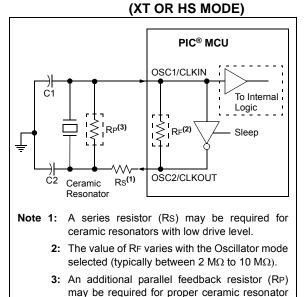

#### FIGURE 5-3:

#### QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- manufacturer data sheets for specifications and recommended application.2: Always verify oscillator performance over the VDD and temperature range that is

- expected for the application.

- For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

## FIGURE 5-4: CERAMIC RESONATOR OPERATION

## 5.2.1.3 Oscillator Start-up Timer (OST)

operation.

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended unless either FSCM or Two-Speed Start-up are enabled. In this case, the code will continue to execute at the selected INTOSC frequency while the OST is counting. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 5.4 "Two-Speed Clock Start-up Mode"**).

| U-0             | U-0                                 | R/W-0/0                                                       | R/W-1/1                            | R/W-0/0         | R/W-1/1          | R/W-1/1         | R/W-0/0      |

|-----------------|-------------------------------------|---------------------------------------------------------------|------------------------------------|-----------------|------------------|-----------------|--------------|

| _               |                                     | WDTPS4                                                        | WDTPS3                             | WDTPS2          | WDTPS1           | WDTPS0          | SWDTEN       |

| bit 7           |                                     |                                                               | 1                                  | •               | •                | •               | bit 0        |

|                 |                                     |                                                               |                                    |                 |                  |                 | ,            |

| Legend:         |                                     |                                                               |                                    |                 |                  |                 |              |

| R = Readab      | le bit                              | W = Writable                                                  | bit                                | U = Unimpler    | mented bit, read | d as '0'        |              |

| u = Bit is un   | changed                             | x = Bit is unk                                                | nown                               | -m/n = Value    | at POR and BO    | DR/Value at all | other Resets |

| '1' = Bit is se | et                                  | '0' = Bit is cle                                              | ared                               |                 |                  |                 |              |

|                 |                                     |                                                               |                                    |                 |                  |                 |              |

| bit 7-6         | Unimpleme                           | nted: Read as '                                               | 0'                                 |                 |                  |                 |              |

| bit 5-1         | WDTPS<4:0                           | )>: Watchdog Ti                                               | imer Period Se                     | elect bits      |                  |                 |              |

|                 | Bit Value =                         | Prescale Rate                                                 |                                    |                 |                  |                 |              |

|                 |                                     | 32 (Interval 1 m                                              |                                    |                 |                  |                 |              |

|                 |                                     | 64 (Interval 2 m<br>128 (Interval 4                           |                                    |                 |                  |                 |              |

|                 |                                     | 256 (Interval 8                                               | 21 /                               |                 |                  |                 |              |

|                 | 00100 = <b>1</b> :                  | 512 (Interval 16                                              | 6 ms typ)                          |                 |                  |                 |              |

|                 |                                     | 1024 (Interval 3                                              |                                    |                 |                  |                 |              |

|                 |                                     | 2048 (Interval 6<br>4096 (Interval 1                          |                                    |                 |                  |                 |              |

|                 |                                     | 8192 (Interval 2                                              | <b>21</b>                          |                 |                  |                 |              |

|                 |                                     | 16384 (Interval                                               |                                    |                 |                  |                 |              |

|                 |                                     | 32768 (Interval 65536 (Interva                                |                                    | at value)       |                  |                 |              |

|                 | 01100 = <b>1</b> :                  | $131072(2^{17})$ (h                                           | nterval 4s tvp)                    |                 |                  |                 |              |

|                 | 01101 = <b>1</b> :                  | 262144 (2 <sup>18</sup> ) (li                                 | nterval 8s tvp)                    |                 |                  |                 |              |

|                 | 01110 = 1:                          | 524288 (2 <sup>19</sup> ) (li<br>1048576 (2 <sup>20</sup> ) ( | nterval 16s typ                    | ))<br>)         |                  |                 |              |

|                 | 10000 = 1                           | 2097152 (2 <sup>21</sup> ) (                                  | Interval 32s ty<br>Interval 64s ty | (p)             |                  |                 |              |

|                 | 10001 = 1:                          | 4194304 (2 <sup>22</sup> ) (                                  | Interval 128s                      | typ)            |                  |                 |              |

|                 | 10010 = <b>1</b> :                  | 8388608 (2 <sup>23</sup> ) (                                  | Interval 256s                      | typ)            |                  |                 |              |

|                 | 10011 = R                           | eserved. Result                                               | s in minimum                       | interval (1·32) |                  |                 |              |

|                 | •                                   |                                                               |                                    |                 |                  |                 |              |

|                 | •                                   |                                                               |                                    |                 |                  |                 |              |

|                 | •<br>11111 - D                      | eserved. Result                                               | e in minimum                       | interval (1.32) |                  |                 |              |

| bit 0           |                                     | Software Enable                                               |                                    | ( )             | bit              |                 |              |

| bit 0           | If WDTE<1:                          |                                                               |                                    | atchoog miner   | bit              |                 |              |

|                 | This bit is ig                      |                                                               |                                    |                 |                  |                 |              |

|                 | If WDTE<1:0                         |                                                               |                                    |                 |                  |                 |              |

|                 | 1 = WDT is<br>0 = WDT is            |                                                               |                                    |                 |                  |                 |              |

|                 | 0 = WDT IS<br><u>If WDTE&lt;1:(</u> |                                                               |                                    |                 |                  |                 |              |

|                 | This bit is ig                      |                                                               |                                    |                 |                  |                 |              |

|                 |                                     |                                                               |                                    |                 |                  |                 |              |

## REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| TABLE 12-1: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name                   | Bit 7   | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------------------|---------|--------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA                 | —       |        | —       | ANSA4   |         | ANSA2   | ANSA1   | ANSA0   | 122                 |

| APFCON0 <sup>(1)</sup> | RXDTSEL | SDOSEL | SSSEL   | _       | T1GSEL  | TXCKSEL | _       | —       | 117                 |

| APFCON1                | —       | _      | —       | _       | P1DSEL  | P1CSEL  | P2BSEL  | CCP2SEL | 118                 |

| INLVLA                 | —       | _      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 123                 |

| LATA                   | —       | _      | LATA5   | LATA4   | _       | LATA2   | LATA1   | LATA0   | 122                 |

| OPTION_REG             | WPUEN   | INTEDG | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         | 176                 |

| PORTA                  | —       | _      | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 121                 |

| TRISA                  | —       | —      | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 121                 |

| WPUA                   | _       | _      | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 123                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations, read as '0'. Shaded cells are not used by PORTA.

Note 1: Unshaded cells apply to PIC16(L)F1824 only.

#### TABLE 12-2: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |  |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|--|

|         | 13:8 |         | —       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | CPD     | 40                  |  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   |            | 48      |         |                     |  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

#### 16.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of                                        |

|---------|---------------------------------------------------------------------------------|

|         | every conversion, regardless of whether<br>or not the ADC interrupt is enabled. |

|         |                                                                                 |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 16.1.5** "Interrupts" for more information.

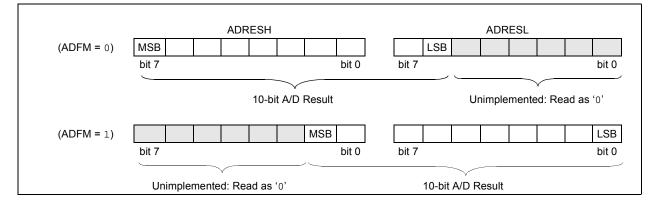

### FIGURE 16-3: 10-BIT A/D CONVERSION RESULT FORMAT

#### 16.1.6 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 16-3 shows the two output formats.

## 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR Buffer2

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACOUT pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

## 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

## EQUATION 17-1: DAC OUTPUT VOLTAGE

$$\label{eq:Vout} \begin{split} \text{Vout} &= \left((\text{Vsource+} - \text{Vsource-}) \times \frac{\text{DACR}{25}}{2^5}\right) + \text{Vsrc-} \\ \text{Note:} \quad \text{Vsource+ can equal FVR Buffer 2, VDD or} \\ \text{Vref+}. \text{Vsource- can equal Vss or Vref-}. \end{split}$$

## 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 30.0** "**Electrical Specifications**".

## 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

| Name    | Bit 7        | Bit 6                  | Bit 5          | Bit 4          | Bit 3          | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |  |

|---------|--------------|------------------------|----------------|----------------|----------------|----------|---------|---------|---------------------|--|

| ANSELA  | —            | _                      |                | ANSA4          | _              | ANSA2    | ANSA1   | ANSA0   | 122                 |  |

| CCP1CON | P1M•         | <1:0>                  | DC1B           | <1:0>          | :0> CCP1M<3:0> |          |         |         |                     |  |

| CCP2CON | P2M          | <:0>1                  | DC2B           | <1:0>          |                | 225      |         |         |                     |  |

| INLVLA  | _            | _                      | INLVLA5        | INLVLA4        | INLVLA3        | INLVLA2  | INLVLA1 | INLVLA0 | 123                 |  |

| INTCON  | GIE          | PEIE                   | TMR0IE         | INTE           | IOCIE          | TMR0IF   | INTF    | IOCIF   | 89                  |  |

| PIE1    | TMR1GIE      | ADIE                   | RCIE           | TXIE           | SSP1IE         | CCP1IE   | TMR2IE  | TMR1IE  | 90                  |  |

| PIR1    | TMR1GIF      | ADIF                   | RCIF           | TXIF           | SSP1IF         | CCP1IF   | TMR2IF  | TMR1IF  | 93                  |  |

| TMR1H   | Holding Regi | ster for the M         | ost Significan | t Byte of the  | 16-bit TMR1 F  | Register |         |         | 182*                |  |

| TMR1L   | Holding Regi | ster for the Le        | ast Significar | nt Byte of the | 16-bit TMR1    | Register |         |         | 182*                |  |

| TRISA   | _            | _                      | TRISA5         | TRISA4         | TRISA3         | TRISA2   | TRISA1  | TRISA0  | 121                 |  |

| T1CON   | TMR1CS1      | S1 TMR1CS0 T1CKPS<1:0> |                | T10SCEN        | T1SYNC         | _        | TMR10N  | 186     |                     |  |

| T1GCON  | TMR1GE       | T1GPOL                 | T1GTM          | T1GSPM         | T1GGO/<br>DONE | T1GVAL   | T1GSS1  | T1GSS0  | 187                 |  |

#### TABLE 21-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

Note 1: PIC16(L)F1828 only.

| R/W-x/u          | R/W-x/u                                                                                                       | R/W-x/u                                                                                                                                                                   | U-0                                              | R/W-x/u                          | R/W-x/u          | R/W-x/u  | R/W-x/u          |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------|------------------|----------|------------------|--|--|--|--|--|

| MDCLODIS         | MDCLPOL                                                                                                       | MDCLSYNC                                                                                                                                                                  | _                                                |                                  | MDCI             | _<3:0>   |                  |  |  |  |  |  |

| bit 7            |                                                                                                               |                                                                                                                                                                           |                                                  |                                  |                  |          | bit 0            |  |  |  |  |  |

| Legend:          |                                                                                                               |                                                                                                                                                                           |                                                  |                                  |                  |          |                  |  |  |  |  |  |

| R = Readable     | bit                                                                                                           | W = Writable bi                                                                                                                                                           | t                                                | U = Unimpler                     | nented bit, read | 1 as '0' |                  |  |  |  |  |  |

| u = Bit is unch  | anged                                                                                                         | x = Bit is unkno                                                                                                                                                          | wn                                               | -                                | at POR and BO    |          | other Resets     |  |  |  |  |  |

| '1' = Bit is set | 0                                                                                                             | '0' = Bit is clear                                                                                                                                                        | ed                                               |                                  |                  |          |                  |  |  |  |  |  |

| bit 7            | 1 = Output s<br>is disable<br>0 = Output s                                                                    | ignal driving the p                                                                                                                                                       | peripheral                                       | output pin (selec                | -                |          | <b>.</b> ,       |  |  |  |  |  |

| bit 6            | MDCLPOL: I<br>1 = Selected                                                                                    | is enabled<br><b>MDCLPOL:</b> Modulator Low Carrier Polarity Select bit<br>1 = Selected low carrier signal is inverted<br>0 = Selected low carrier signal is not inverted |                                                  |                                  |                  |          |                  |  |  |  |  |  |

| bit 5            | 1 = Modulato<br>time carr                                                                                     | : Modulator Low (<br>or waits for a fallin<br>rier<br>or output is not sy                                                                                                 | g edge on                                        | the low time carr                | ier signal befor | -        | itch to the high |  |  |  |  |  |

| bit 4            |                                                                                                               | nted: Read as '0'                                                                                                                                                         |                                                  |                                  | -                |          |                  |  |  |  |  |  |

| bit 3-0          | MDCL<3:0> Modulator Data High Carrier Selection bits <sup>(1)</sup><br>1111 = Reserved. No channel connected. |                                                                                                                                                                           |                                                  |                                  |                  |          |                  |  |  |  |  |  |

|                  | 0111 = CCF<br>0110 = CCF<br>0101 = CCF<br>0100 = CCF                                                          | CIN1 port pin                                                                                                                                                             | Output mo<br>Output mo<br>Output mo<br>Output mo | de only)<br>de only)<br>de only) |                  |          |                  |  |  |  |  |  |

### REGISTER 23-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3       | Bit 2     | Bit 1 | Bit 0 | Register<br>on Page |  |  |

|--------|----------|---------|----------|--------|-------------|-----------|-------|-------|---------------------|--|--|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC | —      |             | MDCH<3:0> |       |       |                     |  |  |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      |             | MDCL<3:0> |       |       |                     |  |  |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDOUT MDBIT |           |       |       | 198                 |  |  |

| MDSRC  | MDMSODIS | _       | —        | —      |             | 199       |       |       |                     |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

<sup>© 2010-2015</sup> Microchip Technology Inc.

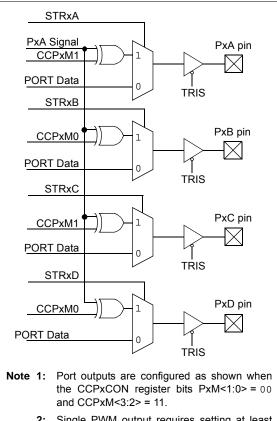

#### 24.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCPxM<3:2> = 11 and PxM<1:0> = 00 of the CCPxCON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STRx<D:A> bits of the PSTRxCON register, as shown in Table 24-9.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCPxM<1:0> bits of the CCPxCON register select the PWM output polarity for the Px<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 24.4.3 "Enhanced PWM Auto-shutdown mode"**. An autoshutdown event will only affect pins that have PWM outputs enabled.

FIGURE 24-18: SIMPLIFIED STEERING BLOCK DIAGRAM

**2:** Single PWM output requires setting at least one of the STRx bits.

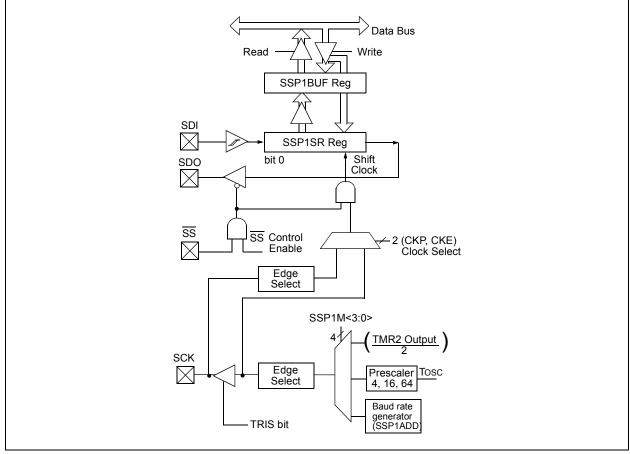

## 25.0 MASTER SYNCHRONOUS SERIAL PORT MODULE

### 25.1 Master SSP (MSSP1) Module Overview

The Master Synchronous Serial Port (MSSP1) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP1 module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy chain connection of slave devices

Figure 25-1 is a block diagram of the SPI interface module.

## FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-o<br>13  | priented file                                    | regi<br>8 | ster o     | ope<br>6 | erat       | ions    |           | 0 |

|---------------|--------------------------------------------------|-----------|------------|----------|------------|---------|-----------|---|

| (             | OPCODE                                           | -         | d          |          |            | f (FII  | E #)      |   |

| C             | l = 0 for des<br>l = 1 for des<br>= 7-bit file r | tinati    | on f       |          | ss         |         |           |   |

| Bit-ori<br>13 | iented file r                                    | -         | er op<br>9 | era<br>7 |            |         |           | 0 |

|               | OPCODE                                           |           | b (Bl      | T #      | <b>#</b> ) | f (F    | ILE #)    |   |

|               | o = 3-bit bit a<br>= 7-bit file r                |           |            | dre      | SS         |         |           |   |

| Litera        | and contro                                       | ol op     | eratio     | ons      | 5          |         |           |   |

| Gener         | al                                               |           |            |          |            |         |           |   |

| 13            |                                                  |           | 8          | 7        |            |         |           | 0 |

|               | OPCODE                                           |           |            |          |            | k (lit  | eral)     |   |

| ŀ             | x = 8-bit imm                                    | edia      | te val     | ue       |            |         |           |   |

| CALL a        | and Goto in:                                     | struc     | tions      | onl      | у          |         |           |   |

| 13            | 11                                               | 10        |            |          |            |         |           | 0 |

| (             | OPCODE                                           |           |            | k        | c (lit     | eral)   |           |   |

| MOVLE<br>13   | o instruction                                    | only      |            | 7        | 6          |         |           | 0 |

|               | OPCODE                                           |           |            |          |            | k (lite | eral)     |   |

| MOVLE         | a = 7-bit imm                                    |           | te val     | ue       |            |         |           |   |

| 13            | OPCODE                                           |           |            |          | 5          | 4       | (literal) | 0 |

| k             | = 5-bit imm                                      | edia      | e val      | ue       |            | ĸ       | (iiterai) |   |

|               | struction on                                     | ly        |            |          |            |         |           | _ |

| 13            | OPCODE                                           |           | <u>9</u> 8 | 3        |            | k (lit  | orol)     | 0 |

|               | c = 9-bit imm                                    | edia      | te val     |          |            | K (III  | eral)     |   |

|               | Offset instruc                                   |           |            |          |            |         |           |   |

| 13            |                                                  | JUOIN     | ,<br>7     | 6        | 5          |         |           | 0 |

|               | OPCODE                                           |           |            | n        |            | k       | (literal) | ) |

|               | n = appropri<br>k = 6-bit imn                    |           |            | ue       |            |         |           |   |

| FSR In<br>13  | crement ins                                      | truct     | ons        |          |            | 32      | 1         | 0 |

|               | OPCODE                                           |           |            |          |            | n       | m (m      |   |

|               | n = appropri<br>m = 2-bit mo                     |           |            |          |            |         |           |   |

|               | DE only                                          |           |            |          |            |         |           | 0 |

| 13            |                                                  |           | PCO        |          | -          |         |           | 0 |

|               |                                                  | C         |            | יטכ      | -          |         |           |   |

#### TABLE 30-6: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|              | ng Temperatur | re -40°C ≤ IA∶<br>I               | ≤ +125°C                                                   |                                           | Γ                                         |        |        | l                                  |                                    |

|--------------|---------------|-----------------------------------|------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------|--------|------------------------------------|------------------------------------|

| Param<br>No. | Sym.          |                                   | Characteristic                                             |                                           | Min.                                      | Тур†   | Max.   | Units                              | Conditions                         |

| 40*          | T⊤0H          | T0CKI High F                      | Pulse Width                                                | No Prescaler                              | 0.5 Tcy + 20                              | _      |        | ns                                 |                                    |

|              |               |                                   |                                                            | With Prescaler                            | 10                                        |        |        | ns                                 |                                    |

| 41*          | T⊤0L          | T0CKI Low P                       | ulse Width                                                 | No Prescaler                              | 0.5 Tcy + 20                              | —      | _      | ns                                 |                                    |

|              |               |                                   |                                                            | With Prescaler                            | 10                                        | —      | _      | ns                                 |                                    |

| 42*          | Тт0Р          | T0CKI Period                      | ł                                                          |                                           | Greater of:<br>20 or <u>Tcy + 40</u><br>N |        | —      | ns                                 | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H          | T1H T1CKI High<br>Time            | Synchronous, No Prescaler                                  |                                           | 0.5 Tcy + 20                              |        |        | ns                                 |                                    |

|              |               |                                   | Synchronous,<br>with Prescaler                             |                                           | 15                                        | —      | _      | ns                                 |                                    |

|              |               |                                   | Asynchronous                                               |                                           | 30                                        | _      |        | ns                                 |                                    |

| 46*          | T⊤1L          | T1CKI Low                         | Synchronous, No Prescaler                                  |                                           | 0.5 Tcy + 20                              |        |        | ns                                 |                                    |

|              |               | Time                              | Synchronous, v                                             | with Prescaler                            | 15                                        | —      | _      | ns                                 |                                    |

|              |               |                                   | Asynchronous                                               |                                           | 30                                        | _      |        | ns                                 |                                    |

| 47*          | TT1P          | T1CKI Input Synchronous<br>Period |                                                            | Greater of:<br>30 or <u>Tcy + 40</u><br>N |                                           | _      | ns     | N = prescale value<br>(1, 2, 4, 8) |                                    |

|              |               |                                   | Asynchronous                                               |                                           | 60                                        | _      |        | ns                                 |                                    |

| 48           | FT1           |                                   | lator Input Frequency Range nabled by setting bit T1OSCEN) |                                           | 32.4                                      | 32.768 | 33.1   | kHz                                |                                    |

| 49*          | TCKEZTMR1     | Delay from E<br>Increment         | xternal Clock Edge to Timer                                |                                           | 2 Tosc                                    | —      | 7 Tosc | —                                  | Timers in Sync<br>mode             |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwi

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

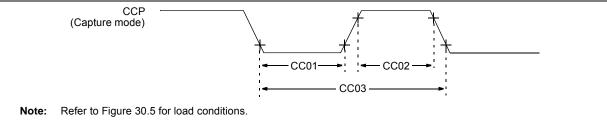

#### FIGURE 30-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

### TABLE 30-7: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                     |                |                       |      |      |       |                    |

|--------------------------------------------------------------------------------------------------------------------------|------|---------------------|----------------|-----------------------|------|------|-------|--------------------|

| Param<br>No.                                                                                                             | Sym. | Characteris         | stic           | Min.                  | Тур† | Max. | Units | Conditions         |

| CC01*                                                                                                                    | TccL | CCP Input Low Time  | No Prescaler   | 0.5Tcy + 20           |      |      | ns    |                    |

|                                                                                                                          |      |                     | With Prescaler | 20                    |      |      | ns    |                    |

| CC02*                                                                                                                    | TccH | CCP Input High Time | No Prescaler   | 0.5Tcy + 20           |      |      | ns    |                    |

|                                                                                                                          |      |                     | With Prescaler | 20                    |      |      | ns    |                    |

| CC03*                                                                                                                    | TccP | CCP Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale value |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 30-22: MEMORY PROGRAMMING REQUIREMENTS FOR PIC16F1824/8-H (High Temp.)

| PIC16F1824/8Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |       |                        |      |      | 9    |       |                                                               |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|------|------|------|-------|---------------------------------------------------------------|--|--|

| Param<br>No.                                                                                                                                                | Sym.  | Characteristic         | Min. | Тур. | Max. | Units | Conditions                                                    |  |  |

|                                                                                                                                                             |       | Data EEPROM Memory     |      |      |      |       |                                                               |  |  |

| D116                                                                                                                                                        | ED    | Byte Endurance         | 50K  |      | _    | E/W   | -40°C to +150°C                                               |  |  |

| D118                                                                                                                                                        | TDEW  | Erase/Write Cycle Time |      | _    | 6.0  | ms    | -40°C to +150°C                                               |  |  |

| D119                                                                                                                                                        | TRETD | Data Retention         |      | 20   | _    | Years | ≤ 50K Programming cycles                                      |  |  |

|                                                                                                                                                             |       | Program Flash Memory   |      |      |      |       |                                                               |  |  |

| D121                                                                                                                                                        | Ер    | Cell Endurance         | _    | _    | _    | _     | Programming the Flash memory<br>above +125°C is not permitted |  |  |

| D124                                                                                                                                                        | TRETD | Data Retention         | —    | 20   | _    | Years |                                                               |  |  |

#### TABLE 30-23: OSCILLATOR PARAMETERS FOR PIC16F1824/8-H (High Temp.)

|              |       |                                                  | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: -40°C $\leq$ TA $\leq$ +150°C for High Temperature |      |      |      |       |                                                                                               |  |

|--------------|-------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------|--|

| Param<br>No. | Sym.  | Characteristic                                   | Frequency<br>Tolerance                                                                                                                | Min. | Тур. | Max. | Units | Conditions                                                                                    |  |

| OS08         | HFosc | Int. Calibrated HFINTOSC<br>Freq. <sup>(1)</sup> | ±5%                                                                                                                                   | 1    | 16.0 | _    | MHz   | $\begin{array}{l} -40^{\circ}C \leq TA \leq 125^{\circ}C \\ V\text{DD} \geq 2.5V \end{array}$ |  |

|              |       |                                                  | ±10%                                                                                                                                  |      | 16.0 | _    | MHz   | $\begin{array}{l} -40^{\circ}C \leq TA \leq 150^{\circ}C \\ V\text{DD} \geq 2.5V \end{array}$ |  |

| OS08A        | MFosc | Int. Calibrated MFINTOSC<br>Freq. <sup>(1)</sup> | ±5%                                                                                                                                   | _    | 500  | —    | kHz   | $\begin{array}{l} -40^{\circ}C \leq TA \leq 125^{\circ}C \\ VDD \geq 2.5V \end{array}$        |  |

|              |       |                                                  | ±10%                                                                                                                                  |      | 500  | —    | kHz   | $\begin{array}{l} -40^{\circ}C \leq TA \leq 150^{\circ}C \\ V\text{DD} \geq 2.5V \end{array}$ |  |

| OS09         | LFosc | Internal LFINTOSC Freq.                          | ±35%                                                                                                                                  | _    | 31   | _    | kHz   | $\begin{array}{l} -40^{\circ}C \leq TA \leq 150^{\circ}C \\ V\text{DD} \geq 2.5V \end{array}$ |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

#### TABLE 30-24: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS FOR PIC16F1824/8-H (High Temp.)

|              |        |                                                            |           | Standard Operating Conditions: (unless otherwise stated)<br>Operating Temperature: $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |           |       |                                                  |  |  |

|--------------|--------|------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|--------------------------------------------------|--|--|

| Param<br>No. | Sym.   | Characteristic                                             | Min.      | Тур.                                                                                                                                            | Max.      | Units | Conditions                                       |  |  |

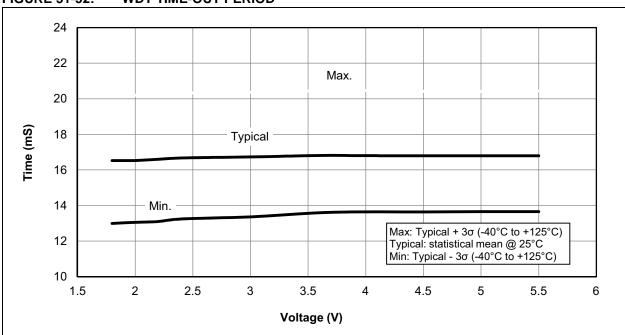

| 31           | TWDTLP | Low-Power Watchdog Timer<br>Time-out Period (No Prescaler) | 10        | 16                                                                                                                                              | 24        | ms    | V <sub>DD</sub> = 3.3V-5V<br>1:16 Prescaler used |  |  |

| 35           | VBOR   | Brown-out Reset Voltage <sup>(1)</sup>                     | 2.50<br>— | 2.70                                                                                                                                            | 2.90<br>— | V     | BORV = 0<br>BORV = 1                             |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

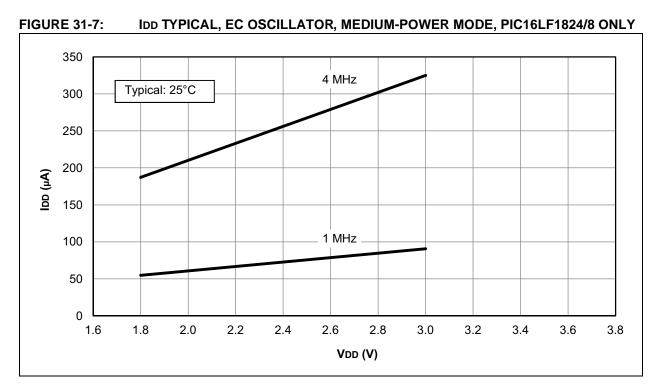

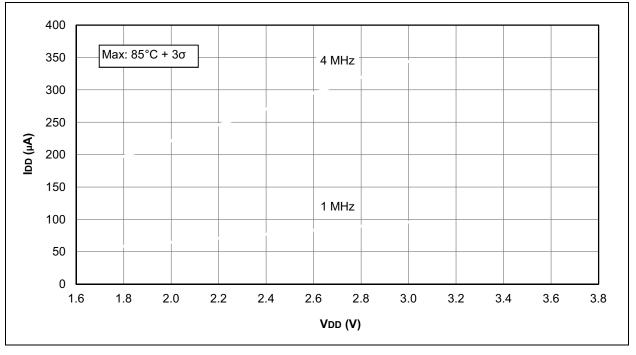

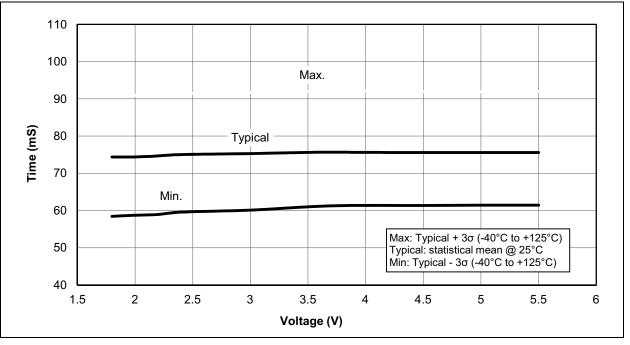

FIGURE 31-8: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1824/8 ONLY

## 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-255A Sheet 1 of 2

## APPENDIX A: DATA SHEET REVISION HISTORY

### Revision A (06/2010)

Original release.

### Revision B (12/2010)

Updated the data sheet to new format; Updated the Electrical Specifications section; Revised Sections 24.2 and 24.3.1; Updated Figure 8-2; Revised the Product Identification System section; Added the Temperature Indicator section.

### Revision C (09/2011)

Updated Table 3-3 and Register 20-1.

### Revision D (07/2012)

Updated the Family Types Table; Updated Figures 1, 2, 3 and 4; Removed CCPTMRS1; Updated Table 3-9; Updated Register 4-2; Updated Sections 5.2.1.3 and 5.5.3; Added Note below Section 5.4.1; Updated Note 1 in Table 7-1; Updated Register 14-1, Figure 16-1, Register 16-1, Equation 16-1, Register 12-20, Register 24-1 and Register 24-3; Updated the Capacitive Sensing (CPS) Module section; Updated the Electrical Specifications section; Added charts to the DC and AC Characteristics Graphs and Charts section; Updated the Product Identification System section; Updated the Packaging Information section; Other minor corrections.

### **Revision E (05/2014)**

Added new UQFN packages: 16-Lead, UQFN, 4x4x0.5, (JQ) and 20-Lead, UQFN, 4x4x0.5, (GZ) packages. Minor edits.

#### **Revision F (4/2015)**

Added Section 30.9: High Temperature Operation in the Electrical Specifications section.

## APPENDIX B: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This section provides comparisons when migrating from other similar PIC<sup>®</sup> devices to the PIC16(L)F1824/8 family of devices.

#### B.1 PIC16F648A to PIC16(L)F1828

| Feature                               | PIC16F648A         | PIC16(L)F1828                                         |  |  |  |  |  |

|---------------------------------------|--------------------|-------------------------------------------------------|--|--|--|--|--|

| Max. Operating<br>Speed               | 20 MHz             | 32 MHz                                                |  |  |  |  |  |

| Max. Program<br>Memory (Words)        | 4K                 | 4K                                                    |  |  |  |  |  |

| Max. SRAM (Bytes)                     | 256                | 256                                                   |  |  |  |  |  |

| Max. EEPROM<br>(Bytes)                | 256                | 256                                                   |  |  |  |  |  |

| A/D Resolution                        | 10-bit             | 10-bit                                                |  |  |  |  |  |

| Timers (8/16-bit)                     | 2/1                | 4/1                                                   |  |  |  |  |  |

| Brown-out Reset                       | Y                  | Y                                                     |  |  |  |  |  |

| Internal Pull-ups                     | RB<7:0>            | RA<7:0><br>RB<7:4> <sup>(1)</sup>                     |  |  |  |  |  |

| Interrupt-on-change                   | RB<7:4>            | RA<5:0>, Edge<br>Selectable<br>RB<7:4> <sup>(1)</sup> |  |  |  |  |  |

| Comparator                            | 2                  | 2                                                     |  |  |  |  |  |

| AUSART/EUSART                         | 1/0                | 0/1                                                   |  |  |  |  |  |

| Extended WDT                          | N                  | Y                                                     |  |  |  |  |  |

| Software Control<br>Option of WDT/BOR | N                  | Y                                                     |  |  |  |  |  |

| INTOSC<br>Frequencies                 | 48 kHz or<br>4 MHz | 31 kHz -<br>32 MHz                                    |  |  |  |  |  |

| Clock Switching                       | Y                  | Y                                                     |  |  |  |  |  |

| Capacitive Sensing                    | N                  | Y                                                     |  |  |  |  |  |

| CCP/ECCP                              | 2/0                | 2/2                                                   |  |  |  |  |  |

| Enhanced PIC16<br>CPU                 | N                  | Y                                                     |  |  |  |  |  |

| MSSPx/SSPx                            | 0                  | 1/0                                                   |  |  |  |  |  |

| Reference Clock                       | N                  | Y                                                     |  |  |  |  |  |

| Data Signal<br>Modulator              | N                  | Y                                                     |  |  |  |  |  |

| SR Latch                              | N                  | Y                                                     |  |  |  |  |  |

| Voltage Reference                     | N                  | Y                                                     |  |  |  |  |  |

| DAC                                   | Y                  | Y                                                     |  |  |  |  |  |

| Note 1: PIC16(L)F1828 only.           |                    |                                                       |  |  |  |  |  |

Note 1: PIC16(L)F1828 only.