## Microchip Technology - PIC16LF1828-E/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

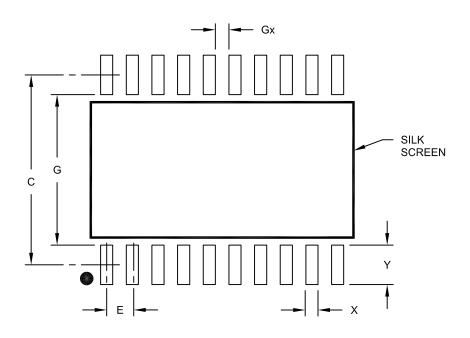

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1828-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-3:** PIC16(L)F1828 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                | Function | Input<br>Type | Output<br>Type | Description                         |

|---------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------|

| RC3/AN7/CPS7/C12IN3-/                                               | RC3      | TTL           | CMOS           | General purpose I/O.                |

| P2A <sup>(1,2)</sup> /CCP2 <sup>(1,2)</sup> /P1C <sup>(1,2)</sup> / | AN7      | AN            |                | A/D Channel 7 input.                |

| MDMIN                                                               | CPS7     | AN            | _              | Capacitive sensing input 7.         |

|                                                                     | C12IN3-  | AN            |                | Comparator C1 or C2 negative input. |

|                                                                     | P2A      | _             | CMOS           | PWM output.                         |

|                                                                     | CCP2     | AN            |                | Capture/Compare/PWM2.               |

|                                                                     | P1C      | _             | CMOS           | PWM output.                         |

|                                                                     | MDMIN    | _             | CMOS           | Modulator source input.             |

| RC4/C2OUT/SRNQ/P1B/TX <sup>(1)</sup> /                              | RC4      | TTL           | CMOS           | General purpose I/O.                |

| CK <sup>(1)</sup> /MDOUT                                            | C2OUT    | _             | CMOS           | Comparator C2 output.               |

|                                                                     | SRNQ     | _             | CMOS           | SR latch inverting output.          |

|                                                                     | P1B      | _             | CMOS           | PWM output.                         |

|                                                                     | TX       | —             | CMOS           | USART asynchronous transmit.        |

|                                                                     | СК       | ST            | CMOS           | USART synchronous clock.            |

|                                                                     | MDOUT    | _             | CMOS           | Modulator output.                   |

| RC5/P1A/CCP1/RX <sup>(1)</sup> /DT <sup>(1)</sup> /                 | RC5      | TTL           | CMOS           | General purpose I/O.                |

| MDCIN2                                                              | P1A      | —             | CMOS           | PWM output.                         |

|                                                                     | CCP1     | ST            | CMOS           | Capture/Compare/PWM1.               |

|                                                                     | RX       | ST            | _              | USART asynchronous input.           |

|                                                                     | DT       | ST            | CMOS           | USART synchronous data.             |

|                                                                     | MDCIN2   | ST            | _              | Modulator Carrier Input 2.          |

| RC6/AN8/CPS8/CCP4/SS                                                | RC6      | TTL           | CMOS           | General purpose I/O.                |

|                                                                     | AN8      | AN            | _              | A/D Channel 8 input.                |

|                                                                     | CPS8     | AN            | _              | Capacitive sensing input 8.         |

|                                                                     | CCP4     | AN            | _              | Capture/Compare/PWM4.               |

|                                                                     | SS       | ST            | _              | Slave Select input.                 |

| RC7/AN9/CPS9/SDO                                                    | RC7      | TTL           | CMOS           | General purpose I/O.                |

|                                                                     | AN9      | AN            | —              | A/D Channel 9 input.                |

|                                                                     | CPS9     | AN            | —              | Capacitive sensing input 9.         |

|                                                                     | SDO      | —             | CMOS           | SPI data output.                    |

| VDD                                                                 | Vdd      | Power         | —              | Positive supply.                    |

| Vss                                                                 | Vss      | Power         | —              | Ground reference.                   |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C<sup>™</sup> = Schmitt Trigger input with I<sup>2</sup>C levels

HV = High Voltage XTAL = Crystal

Note 1: Pin functions can be moved using the APFCONO and APFCON1 registers (Register 12-1 and Register 12-2). 2: Default function location.

## 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The High directive will set bit<7> if a label points to a location in program memory.

## EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants                   |  |

|-----------------------------|--|

| RETLW DATA0 ;Index0 data    |  |

| RETLW DATA1 ;Index1 data    |  |

| RETLW DATA2                 |  |

| RETLW DATA3                 |  |

| my_function                 |  |

| ; LOTS OF CODE              |  |

| MOVLW LOW constants         |  |

| MOVWF FSR1L                 |  |

| MOVLW HIGH constants        |  |

| MOVWF FSR1H                 |  |

| MOVIW 0[FSR1]               |  |

| ;THE PROGRAM MEMORY IS IN W |  |

## 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

## 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed in Table 3-2 below. For detailed information, see Table 3-3.

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| 0Bh or x8Bh  | INTCON |

| Bank 6              |         | Bit 7                           | Bit 6                                                    | Bit 5            | Bit 4      | Bit 3         | Bit 2       | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|---------------------|---------|---------------------------------|----------------------------------------------------------|------------------|------------|---------------|-------------|--------|-------|----------------------|---------------------------------|

|                     |         |                                 |                                                          |                  |            |               |             |        |       |                      |                                 |

| 300h <sup>(1)</sup> | INDF0   | Addressing th<br>(not a physica |                                                          | es contents of   | FSR0H/FSR0 | )L to address | data memory | ,      |       | XXXX XXXX            | XXXX XXXX                       |

|                     | INDF1   | Addressing th<br>(not a physica |                                                          | es contents of   | FSR1H/FSR1 | L to address  | data memory | ,      |       | XXXX XXXX            | XXXX XXXX                       |

| 302h <sup>(1)</sup> | PCL     | Program Cou                     | inter (PC) Lea                                           | st Significant E | 3yte       |               |             |        |       | 0000 0000            | 0000 0000                       |

| 303h <sup>(1)</sup> | STATUS  | —                               | _                                                        | _                | TO         | PD            | Z           | DC     | С     | 1 1000               | q quuu                          |

| 304h <sup>(1)</sup> | FSR0L   | Indirect Data                   | Memory Addr                                              | ess 0 Low Poi    | nter       | •             | •           |        |       | 0000 0000            | uuuu uuuu                       |

| 305h <sup>(1)</sup> | FSR0H   | Indirect Data                   | Memory Addr                                              | ess 0 High Poi   | inter      |               |             |        |       | 0000 0000            | 0000 0000                       |

| 306h <sup>(1)</sup> | FSR1L   | Indirect Data                   | Memory Addr                                              | ess 1 Low Poi    | nter       |               |             |        |       | 0000 0000            | uuuu uuuu                       |

| 307h <sup>(1)</sup> | FSR1H   | Indirect Data                   | Memory Addr                                              | ess 1 High Poi   | inter      |               |             |        |       | 0000 0000            | 0000 0000                       |

| 308h <sup>(1)</sup> | BSR     | —                               | —                                                        | —                |            |               | BSR<4:0>    |        |       | 0 0000               | 0 0000                          |

| 309h <sup>(1)</sup> | WREG    | Working Regi                    | ister                                                    |                  |            |               |             |        |       | 0000 0000            | uuuu uuuu                       |

| 30Ah <sup>(1)</sup> | PCLATH  | _                               | Write Buffer for the upper 7 bits of the Program Counter |                  |            |               |             |        |       | -000 0000            | -000 0000                       |

| 30Bh <sup>(1)</sup> | INTCON  | GIE                             | PEIE                                                     | TMR0IE           | INTE       | IOCIE         | TMR0IF      | INTF   | IOCIF | 0000 000x            | 0000 000u                       |

| 30Ch                | _       | Unimplement                     | ed                                                       |                  |            | •             |             |        |       | _                    | _                               |

| 30Dh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | _                               |

| 30Eh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | _                               |

| 30Fh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | _                               |

| 310h                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | _                               |

| 311h                | CCPR3L  | Capture/Com                     | pare/PWM Re                                              | gister 3 (LSB)   | )          |               |             |        |       | xxxx xxxx            | uuuu uuuu                       |

| 312h                | CCPR3H  | Capture/Com                     | pare/PWM Re                                              | gister 3 (MSB    | )          |               |             |        |       | xxxx xxxx            | uuuu uuuu                       |

| 313h                | CCP3CON | —                               | —                                                        | DC3B             | <1:0>      |               | CCP3N       | 1<3:0> |       | 00 0000              | 00 0000                         |

| 314h                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | —                               |

| 315h                | _       | Unimplement                     | Jnimplemented —                                          |                  |            |               |             |        | _     |                      |                                 |

| 316h                | _       | Unimplement                     | Unimplemented —                                          |                  |            |               |             |        | _     | _                    |                                 |

| 317h                | _       | Unimplement                     | Unimplemented                                            |                  |            |               |             |        | _     | _                    |                                 |

| 318h                | CCPR4L  | Capture/Com                     | pare/PWM Re                                              | gister 4 (LSB)   | )          |               |             |        |       | xxxx xxxx            | uuuu uuuu                       |

| 319h                | CCPR4H  | Capture/Com                     | pare/PWM Re                                              | gister 4 (MSB    | )          |               |             |        |       | xxxx xxxx            | uuuu uuuu                       |

| 31Ah                | CCP4CON | —                               | —                                                        | DC4B             | <1:0>      |               | CCP4N       | 1<3:0> |       | 00 0000              | 00 0000                         |

| 31Bh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | —                    | —                               |

| 31Ch                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | —                    | —                               |

| 31Dh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | —                               |

| 31Eh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | —                               |

| 31Fh                | _       | Unimplement                     | ed                                                       |                  |            |               |             |        |       | _                    | —                               |

### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note** 1: These registers can be addressed from any bank.

2: PIC16(L)F1828 only.

**3:** PIC16(L)F1824 only.

4: Unimplemented, read as '1'.

© 2010-2015 Microchip Technology Inc.

### **REGISTER 4-1: CONFIGURATION WORD 1 (CONTINUED)**

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-32 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire data EEPROM will be erased when the code protection is turned off during an erase.

- 3: The entire program memory will be erased when the code protection is turned off.

## 9.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 7.10 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

## REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0                | U-0 | R/W-1/1            | R/W-1/1 | U-0             | U-0                | U-0                | U-0    |

|--------------------|-----|--------------------|---------|-----------------|--------------------|--------------------|--------|

| —                  | _   | ANSB5              | ANSB4   |                 | —                  | —                  | —      |

| bit 7              |     | -                  |         |                 |                    |                    | bit 0  |

|                    |     |                    |         |                 |                    |                    |        |

| Legend:            |     |                    |         |                 |                    |                    |        |

| R = Readable bit   |     | W = Writable bi    | t       | U = Unimpleme   | ented bit, read as | s 'O'              |        |

| u = Bit is unchang | ged | x = Bit is unkno   | wn      | -n/n = Value at | POR and BOR/       | Value at all other | Resets |

| '1' = Bit is set   |     | '0' = Bit is clear | ed      |                 |                    |                    |        |

| DIT 7-6 | Unimplemented: Read as 0                                                                                                                                                                                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <ul> <li>ANSB&lt;5:4&gt;: Analog Select between Analog or Digital Function on pins RB&lt;5:4&gt;, respectively</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### **REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER**

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 WPUB<7:4>: Weak Pull-up Register bits<sup>(1,2)</sup> 1 = Pull-up enabled 0 = Pull-up disabled bit 3-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

### REGISTER 12-14: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | INLVLB<7:4>: PORTB Input Level Select bits                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | For RB<7:4> pins, respectively                                                                                                               |

|         | <ul><li>1 = ST input used for PORT reads and interrupt-on-change</li><li>0 = TTL input used for PORT reads and interrupt-on-change</li></ul> |

| bit 3-0 | Unimplemented: Read as '0                                                                                                                    |

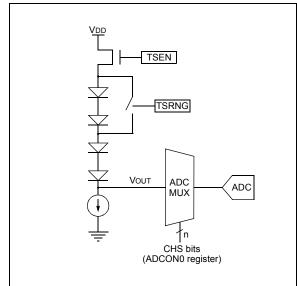

## 15.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between of  $-40^{\circ}$ C and  $+85^{\circ}$ C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

## 15.1 Circuit Operation

Figure 15-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 15-1 describes the output characteristics of the temperature indicator.

## EQUATION 15-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register (Register 14-1). When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

## FIGURE 15-1: TEMPERATURE CIRCUIT DIAGRAM

## 15.2 Minimum Operating VDD vs. Minimum Sensing Temperature

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 15-1 shows the recommended minimum VDD vs. range setting.

TABLE 15-1: RECOMMENDED VDD VS. RANGE

| Min. Vdd, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## **15.3 Temperature Output**

The output of the circuit is measured using the internal analog-to-digital converter. A channel is reserved for the temperature circuit output. Refer to **Section 16.0** "**Analog-to-Digital Converter (ADC) Module**" for detailed information.

## 15.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

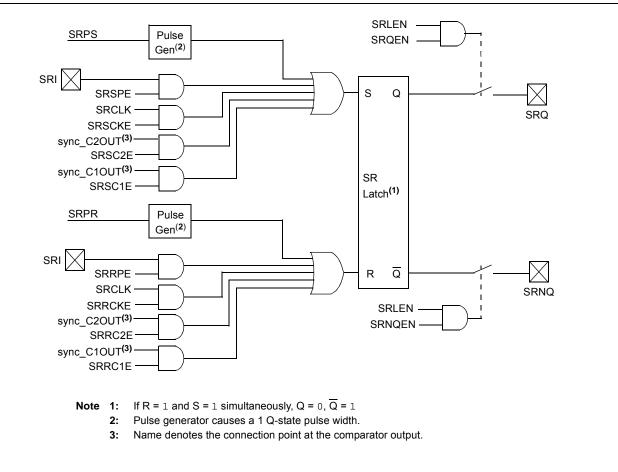

### FIGURE 18-1: SR LATCH SIMPLIFIED BLOCK DIAGRAM

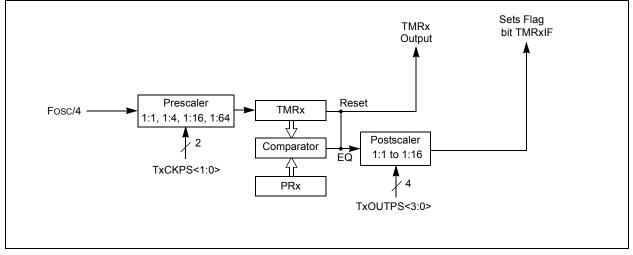

## 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is<br>used to designate Timer2, Timer4, or<br>Timer6. For example, TxCON references |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | T2CON, T4CON, or T6CON. PRx references PR2, PR4, or PR6.                                                                  |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSPx modules (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

## 24.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

## 24.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function registers, APFCON0 and APFCON1. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name    | Bit 7                                                                             | Bit 6                 | Bit 5         | Bit 4        | Bit 3      | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|-----------------------------------------------------------------------------------|-----------------------|---------------|--------------|------------|---------|---------|---------|---------------------|

| APFCON1 | —                                                                                 | —                     | -             | —            | P1DSEL     | P1CSEL  | P2BSEL  | CCP2SEL | 118                 |

| CCPxCON | PxM<                                                                              | 1:0> <b>(1)</b>       | DCxB          | <1:0>        |            | CCPxM<  | <3:0>   |         | 225                 |

| CCPRxL  | Capture/Cor                                                                       | mpare/PWM             | Register x Lo | ow Byte (LSE | 3)         |         |         |         | 203*                |

| CCPRxH  | Capture/Cor                                                                       | mpare/PWM             | Register x H  | igh Byte (MS | B)         |         |         |         | 203*                |

| CMxCON0 | CxON                                                                              | CxOUT                 | CxOE          | CxPOL        | —          | CxSP    | CxHYS   | CxSYNC  | 171                 |

| CMxCON1 | CxINTP                                                                            | CxINTN                | CxPCI         | H<1:0>       | —          |         | CxNCI   | H<1:0>  | 172                 |

| INLVLA  | _                                                                                 | _                     | INLVLA5       | INLVLA4      | INLVLA3    | INLVLA2 | INLVLA1 | INLVLA0 | 123                 |

| INLVLC  | INLVLC7(2)                                                                        | INLVLC6(2)            | INLVLC5       | INLVLC4      | INLVLC3    | INLVLC2 | INLVLC1 | INLVLC0 | 134                 |

| INTCON  | GIE                                                                               | PEIE                  | TMR0IE        | INTE         | IOCIE      | TMR0IF  | INTF    | IOCIF   | 89                  |

| PIE1    | TMR1GIE                                                                           | ADIE                  | RCIE          | TXIE         | SSP1IE     | CCP1IE  | TMR2IE  | TMR1IE  | 90                  |

| PIE2    | OSFIE                                                                             | C2IE                  | C1IE          | EEIE         | BCL1IE     | _       | —       | CCP2IE  | 91                  |

| PIE3    | _                                                                                 | _                     | CCP4IE        | CCP3IE       | TMR6IE     | _       | TMR4IE  | _       | 92                  |

| PIR1    | TMR1GIF                                                                           | ADIF                  | RCIF          | TXIF         | SSP1IF     | CCP1IF  | TMR2IF  | TMR1IF  | 93                  |

| PIR2    | OSFIF                                                                             | C2IF                  | C1IF          | EEIF         | BCL1IF     | _       | —       | CCP2IF  | 94                  |

| PIR3    | _                                                                                 | _                     | CCP4IF        | CCP3IF       | TMR6IF     | _       | TMR4IF  | _       | 95                  |

| T1CON   | TMR1CS1                                                                           | TMR1CS0               | T1CKPS1       | T1CKPS0      | T1OSCEN    | T1SYNC  | —       | TMR10N  | 186                 |

| T1GCON  | TMR1GE                                                                            | T1GPOL                | T1GTM         | T1GSPM       | T1GGO/DONE | T1GVAL  | T1GSS1  | T1GSS0  | 187                 |

| TMR1L   | TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                       |               |              |            |         |         |         | 182*                |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register        |                       |               |              |            |         |         |         | 182*                |

| TRISA   | —                                                                                 | —                     | TRISA5        | TRISA4       | TRISA3     | TRISA2  | TRISA1  | TRISA0  | 121                 |

| TRISC   | TRISC7 <sup>(2)</sup>                                                             | TRISC6 <sup>(2)</sup> | TRISC5        | TRISC4       | TRISC3     | TRISC2  | TRISC1  | TRISC0  | 132                 |

## TABLE 24-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

**Legend:** — = unimplemented locations, read as '0'. Shaded cells are not used by the Capture.

\* Page provides register information.

**Note 1:** Applies to ECCP modules only.

2: PIC16(L)F1828 only.

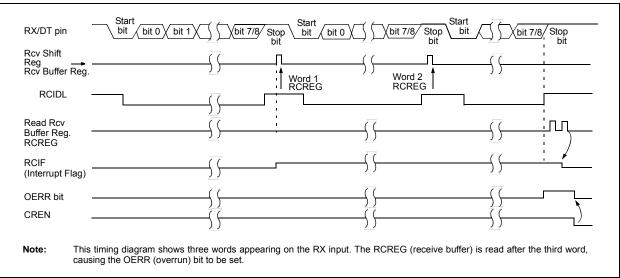

### 26.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 26.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 26.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

## FIGURE 26-5: ASYNCHRONOUS RECEPTION

|        |                | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                   |            |                             |                |            |                             |                    |            |                             |

|--------|----------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc           | ; = 32.00                     | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc           | = 18.43    | 2 MHz                       | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _                             | _                           | _                 |            | _                           | _              |            | _                           | _                  | _          | _                           |

| 1200   | —              | —                             | —                           | 1221              | 1.73       | 255                         | 1200           | 0.00       | 239                         | 1200               | 0.00       | 143                         |

| 2400   | 2404           | 0.16                          | 207                         | 2404              | 0.16       | 129                         | 2400           | 0.00       | 119                         | 2400               | 0.00       | 71                          |

| 9600   | 9615           | 0.16                          | 51                          | 9470              | -1.36      | 32                          | 9600           | 0.00       | 29                          | 9600               | 0.00       | 17                          |

| 10417  | 10417          | 0.00                          | 47                          | 10417             | 0.00       | 29                          | 10286          | -1.26      | 27                          | 10165              | -2.42      | 16                          |

| 19.2k  | 19.23k         | 0.16                          | 25                          | 19.53k            | 1.73       | 15                          | 19.20k         | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |

| 57.6k  | 55.55k         | -3.55                         | 3                           | —                 | —          | _                           | 57.60k         | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |

| 115.2k | —              | _                             | —                           | _                 | _          | —                           | _              | _          | _                           | —                  | _          | _                           |

#### TABLE 26-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|----------------|----------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                                          | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    |                | _                                                  | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202           | 0.16                                               | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404           | 0.16                                               | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | _                | _          | _                           |

| 9600   | 9615           | 0.16                                               | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           |

| 10417  | 10417          | 0.00                                               | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | _                | _          | _                           |

| 19.2k  | —              | _                                                  | _                           | _                | _          | _                           | 19.20k            | 0.00       | 2                           | _                | _          | _                           |

| 57.6k  | —              | _                                                  | —                           | —                | _          | —                           | 57.60k            | 0.00       | 0                           | _                | _          | —                           |

| 115.2k | —              | _                                                  | _                           | —                | _          | _                           | _                 | _          | _                           | _                | _          | —                           |

|        |                | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                |            |                             |                |            |                             |                    |            |                             |

|--------|----------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Foso           | = 32.00                       | 0 MHz                       | Fosc           | = 20.00    | 0 MHz                       | Fosc           | : = 18.43  | 2 MHz                       | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —              | _                             | _                           |                | _          | _                           |                | _          | _                           |                    | _          | _                           |

| 1200   | _              | _                             | _                           | —              | _          | _                           | _              | _          | _                           | _                  | _          | —                           |

| 2400   |                | _                             | _                           | —              | _          | _                           | _              | _          | _                           | _                  | _          | _                           |

| 9600   | 9615           | 0.16                          | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417  | 10417          | 0.00                          | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.82k         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 117.64k        | 2.12                          | 16                          | 113.64k        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                           |

| Operands:        | None                                                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                   |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT<br>Status bits TO and PD are set.                          |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                            |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |

| Status Affected: | Z                                                                                                                                                             |

| Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |  |  |

|------------------|-----------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |

| Status Affected: | Z                                                                     |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| DECF             | Decrement f                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                        |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                      |

| Status Affected: | Z                                                                                                                                        |

| Description:     | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

## **30.6 Thermal Considerations**

| Param<br>No. | Sym.      | Characteristic                         | Тур.  | Units                       | Conditions                                               |

|--------------|-----------|----------------------------------------|-------|-----------------------------|----------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance Junction to Ambient | 70.0  | °C/W                        | 14-pin PDIP package                                      |

|              |           |                                        | 95.3  | °C/W                        | 14-pin SOIC package                                      |

|              |           |                                        | 100.0 | °C/W                        | 14-pin TSSOP package                                     |

|              |           |                                        | 45.7  | °C/W                        | 16-pin QFN (4x4mm) package                               |

|              |           |                                        | 31.8  | °C/W                        | 16-pin UQFN (4x4mm) package                              |

|              |           |                                        | 62.2  | °C/W                        | 20-pin PDIP package                                      |

|              |           |                                        | 77.7  | °C/W                        | 20-pin SOIC package                                      |

|              |           |                                        | 87.3  | °C/W                        | 20-pin SSOP package                                      |

|              |           |                                        | 43.0  | °C/W                        | 20-pin QFN (4x4mm) package                               |

|              |           |                                        | 32.8  | °C/W                        | 20-pin UQFN (4x4mm) package                              |

| TH02 θJC     | θJC       | Thermal Resistance Junction to Case    | 32.8  | °C/W                        | 14-pin PDIP package                                      |

|              |           | 31.0                                   | °C/W  | 14-pin SOIC package         |                                                          |

|              |           |                                        | 24.4  | °C/W                        | 14-pin TSSOP package                                     |

|              |           | 6.3                                    | °C/W  | 16-pin QFN (4x4mm) package  |                                                          |

|              |           | 24.4                                   | °C/W  | 16-pin UQFN (4x4mm) package |                                                          |

|              |           |                                        | 27.5  | °C/W                        | 20-pin PDIP package                                      |

|              |           |                                        | 23.1  | °C/W                        | 20-pin SOIC package                                      |

|              |           |                                        | 31.1  | °C/W                        | 20-pin SSOP package                                      |

|              |           |                                        | 5.3   | °C/W                        | 20-pin QFN (4x4mm) package                               |

|              |           |                                        | 27.4  | °C/W                        | 20-pin UQFN (4x4mm) package                              |

| FH03         | TJMAX     | Maximum Junction Temperature           | 150   | °C                          |                                                          |

| ГН04         | PD        | Power Dissipation                      | _     | W                           | PD = PINTERNAL + PI/O                                    |

| FH05         | PINTERNAL | Internal Power Dissipation             |       | W                           | PINTERNAL = IDD x VDD (Note 1)                           |

| ГН06         | Pı/o      | I/O Power Dissipation                  |       | W                           | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | PDER      | Derated Power                          |       | W                           | PDER = PDMAX (TJ - TA)/θJA (Note 2)                      |

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature, TJ = Junction Temperature

#### **TABLE 30-5**: **RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER** AND BROWN-OUT RESET PARAMETERS

| Param<br>No. | Sym.   | Characteristic                                           | Min.         | Тур†        | Max.         | Units  | Conditions           |

|--------------|--------|----------------------------------------------------------|--------------|-------------|--------------|--------|----------------------|

| 30           | TMCL   | MCLR Pulse Width (low)                                   | 2            |             |              | μS     |                      |

| 31           | TWDTLP | Watchdog Timer<br>Time-out Period (No Prescaler)         | 12           | 16          | 20           | ms     | VDD = 3.3V-5V        |

| 32           | Tost   | Oscillator Start-up Timer Period <sup>(1)</sup>          | _            | 1024        |              | Tosc   |                      |

| 33*          | TPWRT  | Power-up Timer Period, $\overline{PWRTE} = 0$            | 40           | 65          | 140          | ms     |                      |

| 34*          | Tioz   | I/O high-impedance from MCLR Low or Watchdog Timer Reset | —            | —           | 2.0          | μS     |                      |

| 35           | VBOR   | Brown-out Reset Voltage <sup>(2)</sup>                   | 2.55<br>1.80 | 2.70<br>1.9 | 2.85<br>2.05 | V<br>V | BORV = 0<br>BORV = 1 |

| 36*          | VHYST  | Brown-out Reset Hysteresis                               | 20           | 35          | 75           | mV     | -40°C to +85°C       |

| 37*          | TBORDC | Brown-out Reset DC Response Time                         | 0            | 1           | 35           | μs     | $VDD \le VBOR$       |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: By design, the Oscillator Start-up (OST) counts the first 1.024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

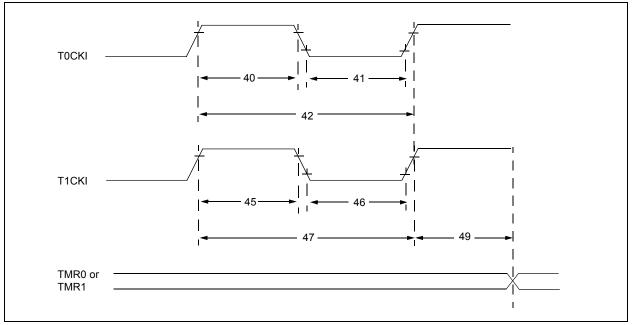

#### FIGURE 30-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

## TABLE 30-6: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|              | ng Temperatur                          | re -40°C ≤ IA∶<br>I             | ≤ +125°C                                                  |                | Γ                                         |        |                                    | l     |                                    |

|--------------|----------------------------------------|---------------------------------|-----------------------------------------------------------|----------------|-------------------------------------------|--------|------------------------------------|-------|------------------------------------|

| Param<br>No. | Sym.                                   |                                 | Characteristic                                            |                | Min.                                      | Тур†   | Max.                               | Units | Conditions                         |

| 40*          | T⊤0H                                   | T0CKI High F                    | Pulse Width No Prescaler                                  |                | 0.5 Tcy + 20                              | _      |                                    | ns    |                                    |

|              |                                        | With Prescaler                  |                                                           | 10             |                                           |        | ns                                 |       |                                    |

| 41*          | T⊤0L                                   | TT0L T0CKI Low Pulse Width No P |                                                           |                | 0.5 Tcy + 20                              | —      | _                                  | ns    |                                    |

|              |                                        |                                 |                                                           | With Prescaler | 10                                        | —      | _                                  | ns    |                                    |

| 42*          | TT0P                                   | T0CKI Period                    | l                                                         |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N |        | —                                  | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Тт1Н                                   | T1CKI High                      | Synchronous, No Prescaler                                 |                | 0.5 Tcy + 20                              |        |                                    | ns    |                                    |

|              |                                        | Time                            | Synchronous,<br>with Prescaler                            |                | 15                                        | —      | _                                  | ns    |                                    |

|              |                                        |                                 | Asynchronous                                              |                | 30                                        | _      |                                    | ns    |                                    |

| 46*          | T⊤1L                                   | T1CKI Low<br>Time               | Synchronous, No Prescaler                                 |                | 0.5 Tcy + 20                              |        |                                    | ns    |                                    |

|              |                                        |                                 | Synchronous, with Prescaler                               |                | 15                                        | —      | _                                  | ns    |                                    |

|              |                                        |                                 | Asynchronous                                              |                | 30                                        | _      |                                    | ns    |                                    |

| 47*          | TT1P T1CKI Input Synchronous<br>Period |                                 | Greater of:<br>30 or <u>Tcy + 40</u><br>N                 |                | _                                         | ns     | N = prescale value<br>(1, 2, 4, 8) |       |                                    |

|              |                                        |                                 | Asynchronous                                              |                | 60                                        | _      |                                    | ns    |                                    |

| 48           | FT1                                    |                                 | lator Input Frequency Range abled by setting bit T1OSCEN) |                | 32.4                                      | 32.768 | 33.1                               | kHz   |                                    |

| 49*          | TCKEZTMR1                              | Delay from E<br>Increment       | xternal Clock E                                           | dge to Timer   | 2 Tosc                                    | _      | 7 Tosc                             | —     | Timers in Sync<br>mode             |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwi

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

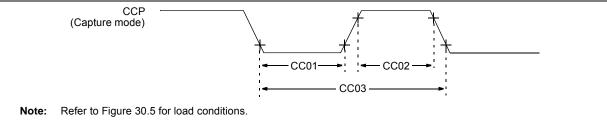

## FIGURE 30-11: CAPTURE/COMPARE/PWM TIMINGS (CCP)

## TABLE 30-7: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                     |                |                       |      |      |       |                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------|---------------------|----------------|-----------------------|------|------|-------|--------------------|--|--|

| Param<br>No.                                                                                                             | Sym. | Characteris         | stic           | Min.                  | Тур† | Max. | Units | Conditions         |  |  |

| CC01*                                                                                                                    | TccL | CCP Input Low Time  | No Prescaler   | 0.5Tcy + 20           |      |      | ns    |                    |  |  |