Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1828-i-gz |

TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| IADEL               | <del>5 5.</del> Oi  | LOIALI                         |                      | INLOIDIL         | I COIVIIVI      | /1111 (00    | 1111100    | , כ    |       |                   |                                 |

|---------------------|---------------------|--------------------------------|----------------------|------------------|-----------------|--------------|------------|--------|-------|-------------------|---------------------------------|

| Address             | Name                | Bit 7                          | Bit 6                | Bit 5            | Bit 4           | Bit 3        | Bit 2      | Bit 1  | Bit 0 | Value on POR, BOR | Value on all<br>other<br>Resets |

| Bank 4              |                     |                                |                      |                  |                 |              |            |        |       |                   |                                 |

| 200h <sup>(1)</sup> | INDF0               | Addressing the (not a physical |                      | es contents of   | FSR0H/FSR0      | L to address | data memor | /      |       | xxxx xxxx x       | XX XXXX                         |

| 201h <sup>(1)</sup> | INDF1               | Addressing the (not a physical |                      | es contents of   | FSR1H/FSR1      | L to address | data memor | /      |       | xxxx xxxx x       | xx xxxx                         |

| 202h <sup>(1)</sup> | PCL                 | Program Cou                    | nter (PC) Lea        | st Significant E | yte             |              |            |        |       | 0000 0000         | 000 0000                        |

| 203h <sup>(1)</sup> | STATUS              | _                              | _                    | _                | TO              | PD           | Z          | DC     | С     | 1 1000            | q quuu                          |

| 204h <sup>(1)</sup> | FSR0L               | Indirect Data                  | Memory Addr          | ess 0 Low Poir   | nter            |              |            | •      |       | 0000 0000 t       | uuu uuuu                        |

| 205h <sup>(1)</sup> | FSR0H               | Indirect Data                  | Memory Addr          | ess 0 High Poi   | nter            |              |            |        |       | 0000 0000         | 000 0000                        |

| 206h <sup>(1)</sup> | FSR1L               | Indirect Data                  | Memory Addr          | ess 1 Low Poir   | nter            |              |            |        |       | 0000 0000 t       | uuu uuuu                        |

| 207h <sup>(1)</sup> | FSR1H               | Indirect Data                  | Memory Addr          | ess 1 High Poi   | nter            |              |            |        |       | 0000 0000         | 000 0000                        |

| 208h <sup>(1)</sup> | BSR                 | _                              | _                    | _                |                 |              | BSR<4:0>   |        |       | 0 0000            | 0 0000                          |

| 209h <sup>(1)</sup> | WREG                | Working Reg                    | ister                |                  |                 |              |            |        |       | 0000 0000 t       | uuu uuuu                        |

| 20Ah <sup>(1)</sup> | PCLATH              | _                              | Write Buffer f       | or the upper 7   | bits of the Pro | gram Counte  | r          |        |       | -000 0000 -       | 000 0000                        |

| 20Bh <sup>(1)</sup> | INTCON              | GIE                            | PEIE                 | TMR0IE           | INTE            | IOCIE        | TMR0IF     | INTF   | IOCIF | 0000 000x (       | 000 000u                        |

| 20Ch                | WPUA                | _                              | _                    | WPUA5            | WPUA4           | WPUA3        | WPUA2      | WPUA1  | WPUA0 | 11 1111           | 11 1111                         |

| 20Dh                | WPUB <sup>(2)</sup> | WPUB7                          | WPUB6                | WPUB5            | WPUB4           | _            | _          | _      | _     | 1111 11           | 11                              |

| 20Eh                | WPUC                | WPUC7 <sup>(2)</sup>           | WPUC6 <sup>(2)</sup> | WPUC5            | WPUC4           | WPUC3        | WPUC2      | WPUC1  | WPUC0 | 1111 1111         | 111 1111                        |

| 20Fh                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 210h                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 211h                | SSP1BUF             | Synchronous                    | Serial Port Re       | eceive Buffer/T  | ransmit Regis   | ster         |            |        |       | xxxx xxxx u       | uuu uuuu                        |

| 212h                | SSP1ADD             |                                |                      |                  | ADD<7           | :0>          |            |        |       | 0000 0000         | 000 0000                        |

| 213h                | SSP1MSK             |                                |                      |                  | MSK<7           | :0>          |            |        |       | 1111 1111         | 111 1111                        |

| 214h                | SSP1STAT            | SMP                            | CKE                  | D/A              | Р               | S            | R/W        | UA     | BF    | 0000 0000         | 000 0000                        |

| 215h                | SSP1CON1            | WCOL                           | SSPOV                | SSPEN            | CKP             |              | SSPM       | 1<3:0> |       | 0000 0000         | 000 0000                        |

| 216h                | SSP1CON2            | GCEN                           | ACKSTAT              | ACKDT            | ACKEN           | RCEN         | PEN        | RSEN   | SEN   | 0000 0000         | 000 0000                        |

| 217h                | SSP1CON3            | ACKTIM                         | PCIE                 | SCIE             | BOEN            | SDAHT        | SBCDE      | AHEN   | DHEN  | 0000 0000         | 000 0000                        |

| 218h                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 219h                | _                   | — Unimplemented                |                      |                  |                 |              |            | _      | _     |                   |                                 |

| 21Ah                | _                   | Unimplemented                  |                      |                  |                 |              | _          | _      |       |                   |                                 |

| 21Bh                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 21Ch                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 21Dh                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 21Eh                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

| 21Fh                | _                   | Unimplement                    | ed                   |                  |                 |              |            |        |       | _                 | _                               |

|                     |                     |                                |                      |                  |                 |              |            |        |       |                   |                                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from any bank.

- 2: PIC16(L)F1828 only.

- 3: PIC16(L)F1824 only.

- 4: Unimplemented, read as '1'.

### REGISTER 6-1: CLKRCON: REFERE NCE CLOCK CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-1/1 | R/W-0/0 | R/W-0/0 | R/W-0/0      | R/W-0/0 |

|---------|---------|---------|---------|---------|---------|--------------|---------|

| CLKREN  | CLKROE  | CLKRSLR | CLKRD   | C<1:0>  | (       | CLKRDIV<2:0> | •       |

| bit 7   |         |         |         |         |         |              | bit 0   |

Legend:  $R = \text{Readable bit} \qquad W = \text{Writable bit} \qquad U = \text{Unimplemented bit, read as '0'} \\ u = \text{Bit is unchanged} \qquad x = \text{Bit is unknown} \qquad -\text{n/n} = \text{Value at POR and BOR/Value at all other Resets}$

'1' = Bit is set '0' = Bit is cleared

bit 7 CLKREN: Reference Clock Module Enable bit

1 = Reference Clock module is enabled

0 = Reference Clock module is disabled

bit 6 CLKROE: Reference Clock Output Enable bit (3)

1 = Reference Clock output is enabled on CLKR pin0 = Reference Clock output disabled on CLKR pin

bit 5 CLKRSLR: Reference Clock Slew Rate Control Limiting Enable bit

1 = Slew Rate limiting is enabled0 = Slew Rate limiting is disabled

bit 4-3 CLKRDC<1:0>: Reference Clock Duty Cycle bits

11 = Clock outputs duty cycle of 75% 10 = Clock outputs duty cycle of 50% 01 = Clock outputs duty cycle of 25% 00 = Clock outputs duty cycle of 0%

bit 2-0 CLKRDIV<2:0> Reference Clock Divider bits

111 = Base clock value divided by 128 110 = Base clock value divided by 64 101 = Base clock value divided by 32 100 = Base clock value divided by 16 011 = Base clock value divided by 8 010 = Base clock value divided by 4 001 = Base clock value divided by 2<sup>(1)</sup>

$000 = Base clock value^{(2)}$

Note 1: In this mode, the 25% and 75% duty cycle accuracy will be dependent on the source clock duty cycle.

- 2: In this mode, the duty cycle will always be equal to the source clock duty cycle, unless a duty cycle of 0% is selected.

- 3: To route CLKR to pin, CLKOUTEN of Configuration Word 1 = 1 is required. CLKOUTEN of Configuration Word 1 = 0 will result in Fosc/4. See Section 6.3 "Conflicts with the CLKR pin" for details.

# PIC16(L)F1824/8

TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|------------|---------|--------|--------|--------|--------|--------|--------|--------|------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 89               |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS2    | PS1    | PS0    | 176              |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 90               |

| PIE2       | OSFIE   | C2IE   | C1IE   | EEIE   | BCL1IE | _      | ı      | CCP2IE | 91               |

| PIE3       | _       | _      | CCP4IE | CCP3IE | TMR6IE | _      | TMR4IE | _      | 92               |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 93               |

| PIR2       | OSFIF   | C2IF   | C1IF   | EEIF   | BCL1IF | _      | _      | CCP2IF | 94               |

| PIR3       | _       | _      | CCP4IF | CCP3IF | TMR6IF | _      | TMR4IF | _      | 95               |

Legend: — = unimplemented locations, read as '0'. Shaded cells are not used by interrupts.

### 12.2 PORTA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-4). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize PORTA.

Reading the PORTA register (Register 12-3) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-4) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The INLVLA register (Register 12-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an Interrupt-on-Change occurs, if that feature is enabled. See Section 30.4 "DC Characteristics: PIC16(L)F1824/8-I/E" for more information on threshold levels.

Note: Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 12.2.1 WEAK PULL-UPS

Each of the PORTA pins has an individually configurable internal weak pull-up. Control bits WPUA<5:0> enable or disable each pull-up (see Register 12-7). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION\_REG register.

#### 12.2.2 ANSELA REGISTER

The ANSELA register (Register 12-6) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

### EXAMPLE 12-1: INITIALIZING PORTA

BANKSEL PORTA **CLRF** PORTA :Init PORTA BANKSEL LATA ;Data Latch CLRF LATA BANKSEL ANSELA **CLRF ANSELA** ;digital I/O BANKSEL TRISA **MOVLW** B'00111000' ;Set RA<5:3> as inputs **MOVWF TRISA** ;and set RA<2:0> as

;outputs

TABLE 16-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

| Name                  | Bit 7                  | Bit 6                  | Bit 5     | Bit 4   | Bit 3   | Bit 2     | Bit 1   | Bit 0   | Register on<br>Page |

|-----------------------|------------------------|------------------------|-----------|---------|---------|-----------|---------|---------|---------------------|

| ADCON0                | _                      | CHS4                   | CHS3      | CHS2    | CHS1    | CHS0      | GO/DONE | ADON    | 149                 |

| ADCON1                | ADFM                   |                        | ADCS<2:0> | •       | _       | ADNREF    | ADPRE   | F<1:0>  | 150                 |

| ADRESH                | A/D Result Re          | egister High           |           |         |         | •         | •       |         | 151, 154            |

| ADRESL                | A/D Result Re          | egister Low            |           |         |         |           |         |         | 151, 154            |

| ANSELA                | _                      | _                      | _         | ANSA4   | _       | ANSA2     | ANSA1   | ANSA0   | 122                 |

| ANSELB <sup>(1)</sup> | _                      | _                      | ANSB5     | ANSB4   | _       | _         | _       | _       | 128                 |

| ANSELC                | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | _         | _       | ANSC3   | ANSC2     | ANSC1   | ANSC0   | 133                 |

| INLVLA                | _                      | _                      | INLVLA5   | INLVLA4 | INLVLA3 | INLVLA2   | INLVLA1 | INLVLA0 | 123                 |

| INLVLB <sup>(1)</sup> | INLVLA7                | INLVLA6                | INLVLA5   | INLVLA4 | _       | _         | _       | _       | 128                 |

| INLVLC                | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5   | INLVLC4 | INLVLC3 | INLVLC2   | INLVLC1 | INLVLC0 | 134                 |

| INTCON                | GIE                    | PEIE                   | TMR0IE    | INTE    | IOCIE   | TMR0IF    | INTF    | IOCIF   | 89                  |

| PIE1                  | TMR1GIE                | ADIE                   | RCIE      | TXIE    | SSP1IE  | CCP1IE    | TMR2IE  | TMR1IE  | 90                  |

| PIR1                  | TMR1GIF                | ADIF                   | RCIF      | TXIF    | SSP1IF  | CCP1IF    | TMR2IF  | TMR1IF  | 93                  |

| TRISA                 | _                      | _                      | TRISA5    | TRISA4  | TRISA3  | TRISA2    | TRISA1  | TRISA0  | 121                 |

| TRISB <sup>(1)</sup>  | TRISB7                 | TRISB6                 | TRISB5    | TRISB4  | _       | _         | _       | _       | 127                 |

| TRISC                 | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5    | TRISC4  | TRISC3  | TRISC2    | TRISC1  | TRISC0  | 132                 |

| FVRCON                | FVREN                  | FVRRDY                 | TSEN      | TSRNG   | CDAFV   | /R<1:0>   | ADFV    | R<1:0>  | 141                 |

| DACCON0               | DACEN                  | DACLPS                 | DACOE     | _       | DACPS   | SS<1:0>   | _       | DACNSS  | 159                 |

| DACCON1               | _                      | _                      | _         |         |         | DACR<4:0> |         |         | 159                 |

Legend: x = unknown, u = unchanged, —= unimplemented, read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

Note 1: PIC16(L)F1828 only.

# PIC16(L)F1824/8

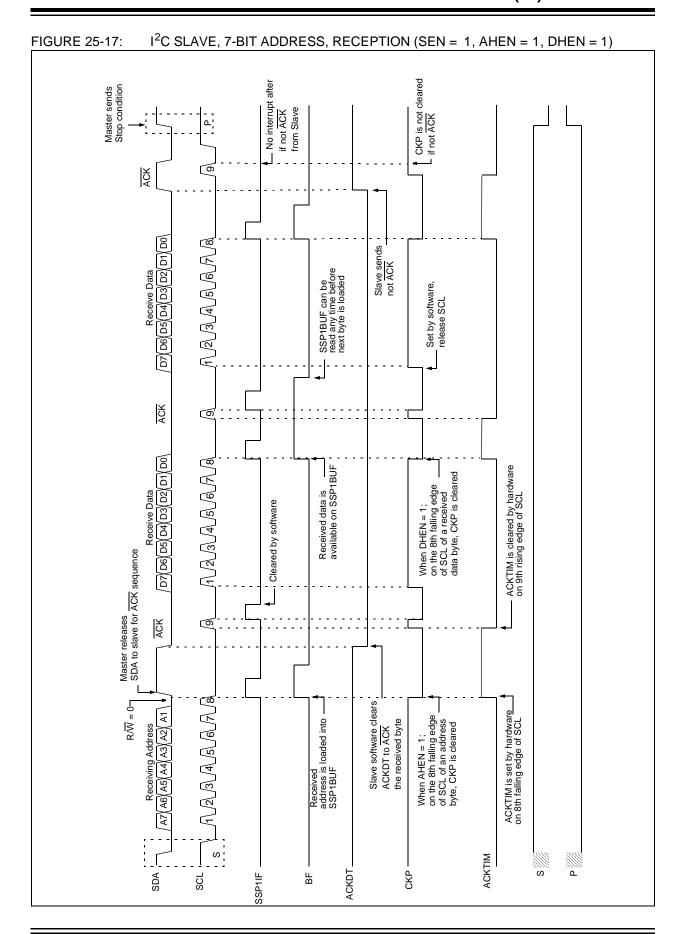

# 25.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP1 module configured as an I<sup>2</sup>C Slave in 10-bit Addressing mode.

Figure 25-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- Bus starts Idle.

- Master sends Start condition; S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSP1STAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- Software reads received address from SSP1BUF clearing the BF flag.

- Slave loads low address into SSP1ADD, releasing SCL.

- Master sends matching low address byte to the Slave; UA bit is set.

Note: Updates to the SSP1ADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSP1IF is set.

Note: If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSP1ADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- Slave reads the received matching address from SSP1BUF clearing BF.

- 12. Slave loads high address into SSP1ADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSP1CON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- Slave reads the received byte from SSP1BUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

# 25.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSP1ADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 25-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 25-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

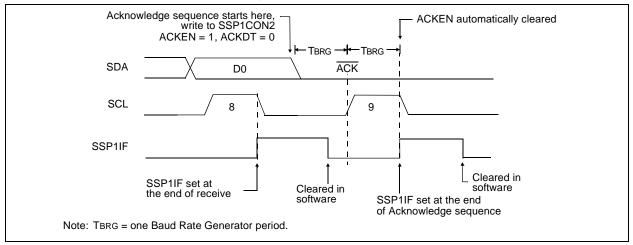

# 25.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSP1CON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP1 module then goes into Idle mode (Figure 25-30).

### 25.6.8.1 WCOL Status Flag

If the user writes the SSP1BUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 25.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSP1CON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSP1STAT register is set. A TBRG later, the PEN bit is cleared and the SSP1IF bit is set (Figure 25-31).

### 25.6.9.1 WCOL Status Flag

If the user writes the SSP1BUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

FIGURE 25-30: ACKNOWLEDGE SEQUEN CE WAVEFORM

# PIC16(L)F1824/8

## 26.4 EUSART Synchronous Mode

Synchronous serial communications are typically used

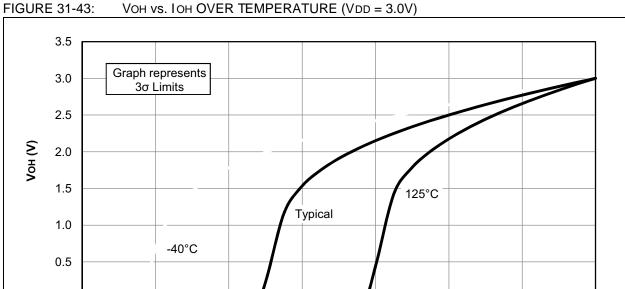

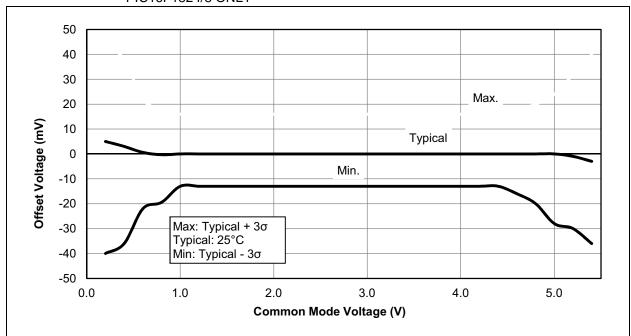

FIGURE 31-58: COMPARATOR INPUT OFFSET AT 25°C, NORMAL-POWER MODE (CxSP = 1), PIC16F1824/8 ONLY

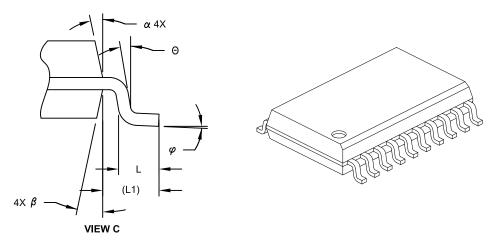

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |      | MILLIMETERS |     |      |  |

|--------------------------|------|-------------|-----|------|--|

| Dimension Li             | mits | MIN         | NOM | MAX  |  |

| Number of Pins           | N    | 20          |     |      |  |

| Pitch                    | е    | 1.27 BSC    |     |      |  |

| Overall Height           | Α    | -           | -   | 2.65 |  |

| Molded Package Thickness | A2   | 2.05        | -   | -    |  |

| Standoff §               | A1   | 0.10        | -   | 0.30 |  |

| Overall Width            | Е    | 10.30 BSC   |     |      |  |

| Molded Package Width     | E1   | 7.50 BSC    |     |      |  |

| Overall Length           | D    | 12.80 BSC   |     |      |  |

| Chamfer (Optional)       | h    | 0.25        | -   | 0.75 |  |

| Foot Length              | L    | 0.40        | -   | 1.27 |  |

| Footprint                | L1   | 1.40 REF    |     |      |  |

| Lead Angle               | Θ    | 0°          | -   | -    |  |

| Foot Angle               | φ    | 0°          | -   | 8°   |  |

| Lead Thickness           | С    | 0.20        | -   | 0.33 |  |

| Lead Width               | b    | 0.31        | -   | 0.51 |  |

| Mold Draft Angle Top     | α    | 5°          | -   | 15°  |  |

| Mold Draft Angle Bottom  | β    | 5°          | -   | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2