Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-QFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1828t-i-ml |

#### PIC12(L)F1822/1840/PIC16(L)F182x/1847 Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O's <sup>(2)</sup> | 10-bit ADC (ch) | CapSense (ch) | Comparators | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> CTM/SPI) | ECCP (Full-Bridge)<br>ECCP (Half-Bridge)<br>CCP | SR Latch | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|------------------------|----------------------|----------------------|-----------------|---------------|-------------|----------------------|--------|-------------------------------|-------------------------------------------------|----------|----------------------|-----|

| PIC12(L)F1822 | (1)              | 2K                              | 256                    | 128                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                             | 0/1/0                                           | Υ        | I/H                  | Υ   |

| PIC12(L)F1840 | (2)              | 4K                              | 256                    | 256                  | 6                    | 4               | 4             | 1           | 2/1                  | 1      | 1                             | 0/1/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1823 | (1)              | 2K                              | 256                    | 128                  | 12                   | 8               | 8             | 2           | 2/1                  | 1      | 1                             | 1/0/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1824 | (3)              | 4K                              | 256                    | 256                  | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1825 | (4)              | 8K                              | 256                    | 1024                 | 12                   | 8               | 8             | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1826 | (5)              | 2K                              | 256                    | 256                  | 16                   | 12              | 12            | 2           | 2/1                  | 1      | 1                             | 1/0/0                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1827 | (5)              | 4K                              | 256                    | 384                  | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1828 | (3)              | 4K                              | 256                    | 256                  | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 1                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1829 | (4)              | 8K                              | 256                    | 1024                 | 18                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

| PIC16(L)F1847 | (6)              | 8K                              | 256                    | 1024                 | 16                   | 12              | 12            | 2           | 4/1                  | 1      | 2                             | 1/1/2                                           | Υ        | I/H                  | Υ   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS41413 PIC12(L)F1822/PIC16(L)F1823 Data Sheet, 8/14-Pin Flash Microcontrollers.

2: DS41441 PIC12(L)F1840 Data Sheet, 8-Pin Flash Microcontrollers.

3: DS41419 PIC16(L)F1824/1828 Data Sheet, 28/40/44-Pin Flash Microcontrollers.

4: DS41440 PIC16(L)F1825/1829 Data Sheet, 14/20-Pin Flash Microcontrollers.

5: DS41391 PIC16(L)F1826/1827 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**6:** DS41453 PIC16(L)F1847 Data Sheet, 18/20/28-Pin Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit www.microchip.com/packaging or contact your local sales office.

DS40001419F-page 27

| <b>TABLE 3-7:</b> | PIC16(L | )F1824/8 | <b>MEMORY</b> | MAP, | <b>BANKS 24-31</b> |

|-------------------|---------|----------|---------------|------|--------------------|

|                   |         |          |               |      |                    |

|      | BANK 24               |      | BANK 25               |         | BANK 26               |      | BANK 27               |      | BANK 28               |      | BANK 29               |      | BANK 30               |      | BANK 31               |

|------|-----------------------|------|-----------------------|---------|-----------------------|------|-----------------------|------|-----------------------|------|-----------------------|------|-----------------------|------|-----------------------|

| C00h | INDF0                 | C80h | INDF0                 | D00h    | INDF0                 | D80h | INDF0                 | E00h | INDF0                 | E80h | INDF0                 | F00h | INDF0                 | F80h | INDF0                 |

| C01h | INDF1                 | C81h | INDF1                 | D01h    | INDF1                 | D81h | INDF1                 | E01h | INDF1                 | E81h | INDF1                 | F01h | INDF1                 | F81h | INDF1                 |

| C02h | PCL                   | C82h | PCL                   | D02h    | PCL                   | D82h | PCL                   | E02h | PCL                   | E82h | PCL                   | F02h | PCL                   | F82h | PCL                   |

| C03h | STATUS                | C83h | STATUS                | D03h    | STATUS                | D83h | STATUS                | E03h | STATUS                | E83h | STATUS                | F03h | STATUS                | F83h | STATUS                |

| C04h | FSR0L                 | C84h | FSR0L                 | D04h    | FSR0L                 | D84h | FSR0L                 | E04h | FSR0L                 | E84h | FSR0L                 | F04h | FSR0L                 | F84h | FSR0L                 |

| C05h | FSR0H                 | C85h | FSR0H                 | D05h    | FSR0H                 | D85h | FSR0H                 | E05h | FSR0H                 | E85h | FSR0H                 | F05h | FSR0H                 | F85h | FSR0H                 |

| C06h | FSR1L                 | C86h | FSR1L                 | D06h    | FSR1L                 | D86h | FSR1L                 | E06h | FSR1L                 | E86h | FSR1L                 | F06h | FSR1L                 | F86h | FSR1L                 |

| C07h | FSR1H                 | C87h | FSR1H                 | D07h    | FSR1H                 | D87h | FSR1H                 | E07h | FSR1H                 | E87h | FSR1H                 | F07h | FSR1H                 | F87h | FSR1H                 |

| C08h | BSR                   | C88h | BSR                   | D08h    | BSR                   | D88h | BSR                   | E08h | BSR                   | E88h | BSR                   | F08h | BSR                   | F88h | BSR                   |

| C09h | WREG                  | C89h | WREG                  | D09h    | WREG                  | D89h | WREG                  | E09h | WREG                  | E89h | WREG                  | F09h | WREG                  | F89h | WREG                  |

| C0Ah | PCLATH                | C8Ah | PCLATH                | D0Ah    | PCLATH                | D8Ah | PCLATH                | E0Ah | PCLATH                | E8Ah | PCLATH                | F0Ah | PCLATH                | F8Ah | PCLATH                |

| C0Bh | INTCON                | C8Bh | INTCON                | D0Bh    | INTCON                | D8Bh | INTCON                | E0Bh | INTCON                | E8Bh | INTCON                | F0Bh | INTCON                | F8Bh | INTCON                |

| C0Ch | _                     | C8Ch | _                     | D0Ch    | _                     | D8Ch |                       | E0Ch |                       | E8Ch | _                     | F0Ch | _                     | F8Ch |                       |

| C0Dh | _                     | C8Dh |                       | D0Dh    | _                     | D8Dh | _                     | E0Dh | _                     | E8Dh | _                     | F0Dh | _                     | F8Dh |                       |

| C0Eh | _                     | C8Eh | _                     | D0Eh    | _                     | D8Eh |                       | E0Eh | _                     | E8Eh | _                     | F0Eh | _                     | F8Eh |                       |

| C0Fh | _                     | C8Fh |                       | D0Fh    | _                     | D8Fh | _                     | E0Fh | _                     | E8Fh | _                     | F0Fh | _                     | F8Fh |                       |

| C10h | _                     | C90h |                       | D10h    | _                     | D90h | _                     | E10h | _                     | E90h | _                     | F10h | _                     | F90h |                       |

| C11h | _                     | C91h |                       | D11h    | _                     | D91h | _                     | E11h | _                     | E91h | _                     | F11h | _                     | F91h |                       |

| C12h | _                     | C92h |                       | D12h    | _                     | D92h | _                     | E12h | _                     | E92h | _                     | F12h | _                     | F92h |                       |

| C13h | _                     | C93h |                       | D13h    | _                     | D93h | _                     | E13h | _                     | E93h | _                     | F13h | _                     | F93h |                       |

| C14h | _                     | C94h | _                     | D14h    | _                     | D94h | _                     | E14h | _                     | E94h | _                     | F14h | _                     | F94h |                       |

| C15h | _                     | C95h | _                     | D15h    | _                     | D95h | _                     | E15h | _                     | E95h | _                     | F15h | _                     | F95h |                       |

| C16h | _                     | C96h | _                     | D16h    | _                     | D96h | _                     | E16h | _                     | E96h | _                     | F16h | _                     | F96h |                       |

| C17h | _                     | C97h | _                     | D17h    | _                     | D97h | _                     | E17h | _                     | E97h | _                     | F17h | _                     | F97h | See Table 3-8 for     |

| C18h | _                     | C98h |                       | D18h    | _                     | D98h | _                     | E18h | _                     | E98h | _                     | F18h | _                     | F98h | register mapping      |

| C19h | _                     | C99h | _                     | D19h    | _                     | D99h | _                     | E19h | _                     | E99h | _                     | F19h | _                     | F99h | details               |

| C1Ah | _                     | C9Ah |                       | D1Ah    |                       | D9Ah |                       | E1Ah |                       | E9Ah | _                     | F1Ah | _                     | F9Ah |                       |

| C1Bh | _                     | C9Bh |                       | D1Bh    |                       | D9Bh |                       | E1Bh |                       | E9Bh | _                     | F1Bh | _                     | F9Bh |                       |

| C1Ch | _                     | C9Ch |                       | D1Ch    | _                     | D9Ch | _                     | E1Ch | _                     | E9Ch | _                     | F1Ch | _                     | F9Ch |                       |

| C1Dh | _                     | C9Dh |                       | D1Dh    | _                     | D9Dh | _                     | E1Dh | _                     | E9Dh | _                     | F1Dh | _                     | F9Dh |                       |

| C1Eh | _                     | C9Eh |                       | D1Eh    |                       | D9Eh |                       | E1Eh |                       | E9Eh | _                     | F1Eh | _                     | F9Eh |                       |

| C1Fh | _                     | C9Fh |                       | D1Fh    |                       | D9Fh |                       | E1Fh |                       | E9Fh | _                     | F1Fh | _                     | F9Fh |                       |

| C20h |                       | CA0h |                       | D20h    |                       | DA0h |                       | E20h |                       | EA0h |                       | F20h |                       | FA0h |                       |

|      | Unimplemented         |      | Unimplemented         |         | Unimplemented         |      | Unimplemented         |      | Unimplemented         |      | Unimplemented         |      | Unimplemented         |      |                       |

|      | Read as '0'           |      | Read as '0'           |         | Read as '0'           |      | Read as '0'           |      | Read as '0'           |      | Read as '0'           |      | Read as '0'           |      |                       |

| 0.05 |                       |      |                       | D. 0.E. |                       |      |                       |      |                       |      |                       | E05: |                       |      |                       |

| C6Fh |                       | CEFh |                       | D6Fh    |                       | DEFh |                       | E6Fh |                       | EEFh |                       | F6Fh |                       | FEFh |                       |

| C70h | A                     | CF0h | A                     | D70h    | A                     | DF0h | A                     | E70h | A                     | EF0h | A                     | F70h | A                     | FF0h | A                     |

|      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |         | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |      | Accesses<br>70h – 7Fh |

| 055  | 7011 - 7111           | OFF: | 7011 - 7111           | DZEL    | 7011 - 7111           | חררי | -                     | C7C- | 7011 – 71 11          | CCC- | 7011 - 71 11          | C7C- | 7011 - 7111           | гггь | 7011 - 7111           |

| CFFh |                       | CFFh |                       | D7Fh    |                       | DFFh |                       | E7Fh |                       | EFFh |                       | F7Fh |                       | FFFh |                       |

= Unimplemented data memory locations, read as '0'. Legend:

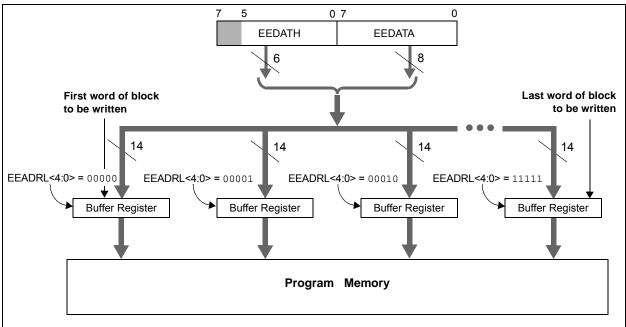

#### 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

#### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when the write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the write operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2ms, only during the cycle in which the write takes place (i.e., the last word of the block write). This is not Sleep mode, as the clocks and peripherals will

continue to run. The processor does not stall when LWLO = 1, loading the write latches. After the write cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

FIGURE 11-2: BLOCK WRITES TO FLASH PROGRAM MEMORY WITH 32 WRITE LATCHES

### REGISTER 13-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER (PIC16(L)F1828 ONLY)

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 IOCBP<7:4>: Interrupt-on-Change PORTB Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 **Unimplemented:** Read as '0'

## REGISTER 13-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER (PIC16(L)F1828 ONLY)

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 IOCAN<7:4>: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 **Unimplemented:** Read as '0'

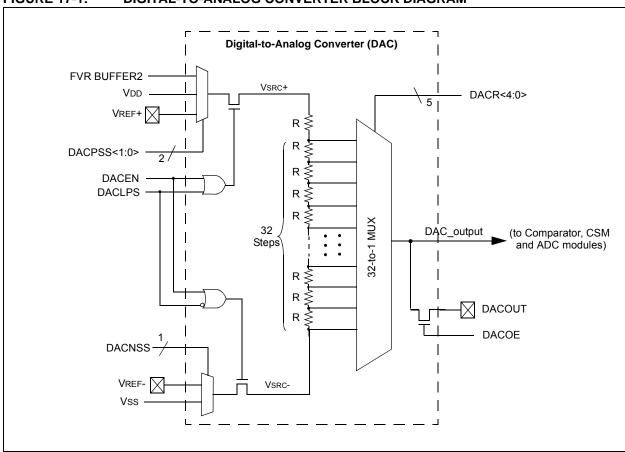

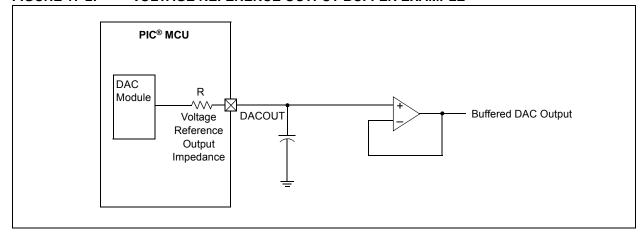

FIGURE 17-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

FIGURE 17-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

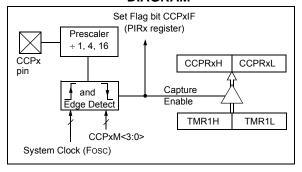

#### 24.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, CCP3 and CCP4.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 24-1 shows a simplified diagram of the Capture operation.

#### 24.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON1 register. Refer to **Section 12.1 "Alternate Pin Function"** for more details.

**Note:** If the CCPx pin is configured as an output,

a write to the port can cause a capture condition.

# FIGURE 24-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 24.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 24.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 24.1.4 CCP PRESCALER

Note:

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 24-1 demonstrates the code to perform this function.

### EXAMPLE 24-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | L CCPxCON   | ;Set Bank bits to point ;to CCPxCON |

|---------|-------------|-------------------------------------|

| CLRF    | CCPxCON     | ;Turn CCP module off                |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with                |

|         |             | ;the new prescaler                  |

|         |             | ; move value and CCP ON             |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this             |

|         |             | ;value                              |

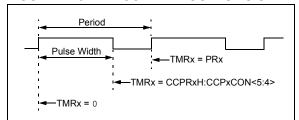

#### 24.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 24-3 shows a typical waveform of the PWM signal.

#### 24.3.1 STANDARD PWM OPERATION

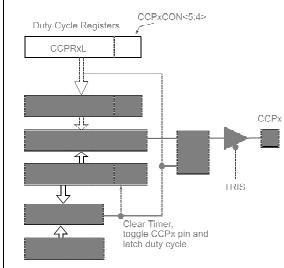

The standard PWM function described in this section is available and identical for CCP modules ECCP1, ECCP2, CCP3 and CCP4.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- · CCPRxL registers

- · CCPxCON registers

Figure 24-4 shows a simplified block diagram of PWM operation.

- **Note 1:** The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- **2:** Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 24-3: CCP PWM OUTPUT SIGNAL

### FIGURE 24-4: SIMPLIFIED PWM BLOCK DIAGRAM

- Note 1: The 8 bit timer TMRx register is concatenated with the 2-bit internal system clock (FOSC), or 2 bits of the prescaler, to create the 10-bit time

- 2: In PWM mode, CCPRxH is a read-only register.

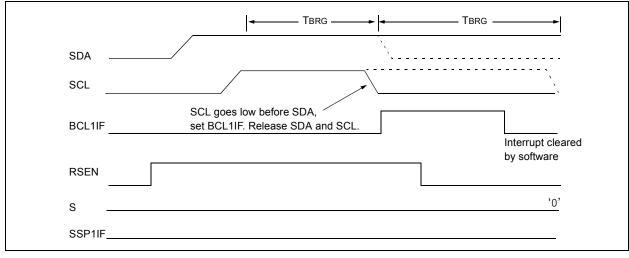

#### FIGURE 25-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### REGISTER 25-3: SSP1CON2: SSP1 CONTROL REGISTER 2

| R/W-0/0 | R-0/0   | R/W-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/S/HS-0/0 | R/W/HS-0/0 |

|---------|---------|---------|------------|------------|------------|------------|------------|

| GCEN    | ACKSTAT | ACKDT   | ACKEN      | RCEN       | PEN        | RSEN       | SEN        |

| bit 7   |         |         |            |            |            |            | bit 0      |

Legend:

bit 2

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HC = Cleared by hardware S = User set

bit 7 **GCEN:** General Call Enable bit (in I<sup>2</sup>C Slave mode only)

1 = Enable interrupt when a general call address (0x00 or 00h) is received in the SSP1SR

0 = General call address disabled

bit 6 ACKSTAT: Acknowledge Status bit (in I<sup>2</sup>C mode only)

1 = Acknowledge was not received0 = Acknowledge was received

bit 5 **ACKDT:** Acknowledge Data bit (in I<sup>2</sup>C mode only)

In Receive mode:

Value transmitted when the user initiates an Acknowledge sequence at the end of a receive

1 = Not Acknowledge0 = Acknowledge

bit 4 **ACKEN:** Acknowledge Sequence Enable bit (in I<sup>2</sup>C Master mode only)

In Master Receive mode:

1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit. Automatically cleared by hardware.

0 = Acknowledge sequence idle

bit 3 **RCEN:** Receive Enable bit (in I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for I<sup>2</sup>C

0 = Receive idle

**PEN:** Stop Condition Enable bit (in I<sup>2</sup>C Master mode only)

SCK Release Control:

1 = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Stop condition Idle

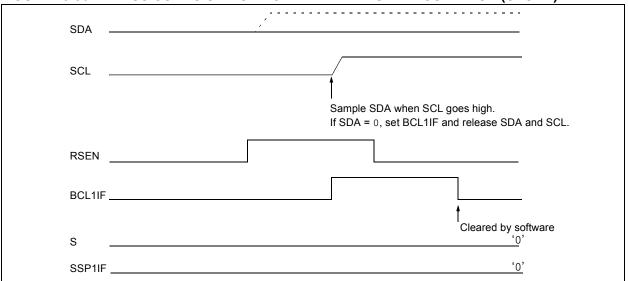

bit 1 **RSEN:** Repeated Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)

1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Repeated Start condition Idle

bit 0 **SEN:** Start Condition Enabled bit (in I<sup>2</sup>C Master mode only)

In Master mode:

1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Start condition Idle

In Slave mode:

1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)

0 = Clock stretching is disabled

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSP1BUF may not be written (or writes to the SSP1BUF are disabled).

TABLE 26-3: BAUD RATE FORMULAS

| C    | onfiguration B | its  | DDC/FUCADT Made     | Baud Rate Formula |

|------|----------------|------|---------------------|-------------------|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Baud Rate Formula |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0              | 1    | 8-bit/Asynchronous  | F000//40 (n.14)]  |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |

| 1    | 0              | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1              | х    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair

TABLE 26-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on Page |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|------------------|

| BAUDCON | ABDOVF | RCIDL | _     | SCKP  | BRG16 | _     | WUE   | ABDEN | 296              |

| RCSTA   | SPEN   | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 295              |

| SPBRGL  | BRG7   | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 297*             |

| SPBRGH  | BRG15  | BRG14 | BRG13 | BRG12 | BRG11 | BRG10 | BRG9  | BRG8  | 297*             |

| TXSTA   | CSRC   | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 294              |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

<sup>\*</sup> Page provides register information.

#### 26.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 26.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

Note: If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

#### 26.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 26.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 26.4.1.9 Synchronous Master Reception Setup:

- Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

Note 1: Module Enable and Current mode selections are not shown.

2: Comparators remain active in Noise Detection mode.

TABLE 29-3: PIC16F/LF1824/1828 ENHANCED INSTRUCTION SET

| Mnem    | nonic,       | Description                                          | 01         |         | 14-Bit   | Opcode   | )        | Status     | Nete     |

|---------|--------------|------------------------------------------------------|------------|---------|----------|----------|----------|------------|----------|

| Oper    | ands         | Description                                          | Cycles     | MSb     |          |          | LSb      | Affected   | Notes    |

|         |              | BYTE-ORIENTED FILE REGIS                             | TER OPE    | RATIO   | NS       |          |          |            |          |

| ADDWF   | f, d         | Add W and f                                          | 1          | 00      | 0111     | dfff     | ffff     | C, DC, Z   | 2        |

| ADDWFC  | f, d         | Add with Carry W and f                               | 1          | 11      | 1101     | dfff     | ffff     | C, DC, Z   | 2        |

| ANDWF   | f, d         | AND W with f                                         | 1          | 00      | 0101     | dfff     | ffff     | Z          | 2        |

| ASRF    | f, d         | Arithmetic Right Shift                               | 1          | 11      | 0111     | dfff     | ffff     | C, Z       | 2        |

| LSLF    | f, d         | Logical Left Shift                                   | 1          | 11      | 0101     | dfff     | ffff     | C, Z       | 2        |

| LSRF    | f, d         | Logical Right Shift                                  | 1          | 11      | 0110     | dfff     | ffff     | C, Z       | 2        |

| CLRF    | f            | Clear f                                              | 1          | 00      | 0001     | lfff     | ffff     | Z          | 2        |

| CLRW    | _            | Clear W                                              | 1          | 00      | 0001     | 0000     | 00xx     | Z          |          |

| COMF    | f, d         | Complement f                                         | 1          | 00      | 1001     | dfff     | ffff     | Z          | 2        |

| DECF    | f, d         | Decrement f                                          | 1          | 00      | 0011     | dfff     | ffff     | Z          | 2        |

| INCF    | f, d         | Increment f                                          | 1          | 0.0     | 1010     | dfff     | ffff     | Z          | 2        |

| IORWF   | f, d         | Inclusive OR W with f                                | 1          | 0.0     | 0100     | dfff     | ffff     | Z          | 2        |

| MOVF    | f, d         | Move f                                               | 1          | 00      | 1000     | dfff     | ffff     | Z          | 2        |

| MOVWF   | f            | Move W to f                                          | 1          | 00      | 0000     | 1fff     | ffff     |            | 2        |

| RLF     | f, d         | Rotate Left f through Carry                          | 1          | 00      |          | dfff     |          | С          | 2        |

| RRF     | f, d         | Rotate Right f through Carry                         | 1          | 00      | 1100     | dfff     | ffff     | С          | 2        |

| SUBWF   | f, d         | Subtract W from f                                    | 1          | 00      | 0010     | dfff     | ffff     | C, DC, Z   | 2        |

| SUBWFB  | f, d         | Subtract with Borrow W from f                        | 1          | 11      |          | dfff     |          | C, DC, Z   | 2        |

| SWAPF   | f, d         | Swap nibbles in f                                    | 1          | 00      | 1110     | dfff     | ffff     | , ,        | 2        |

| XORWF   | f, d         | Exclusive OR W with f                                | 1          | 00      | 0110     | dfff     | ffff     | Z          | 2        |

|         |              | BYTE ORIENTED SKIP (                                 | PERATION   | ONS     |          |          |          |            |          |

| DECFSZ  | f, d         | Decrement f, Skip if 0                               | 1(2)       | 00      | 1011     | dfff     | ffff     |            | 1, 2     |

| INCFSZ  | f, d         | Increment f, Skip if 0                               | 1(2)       | 00      | 1111     | dfff     | ffff     |            | 1, 2     |

|         |              | BIT-ORIENTED FILE REGIST                             | ER OPER    | RATION  | IS       |          | I        |            | I.       |

| BCF     | f, b         | Bit Clear f                                          | 1          | 01      | 00bb     | bfff     | ffff     |            | 2        |

| BSF     | f, b         | Bit Set f                                            | 1          | 01      | 01bb     | bfff     | ffff     |            | 2        |

|         | •            | BIT-ORIENTED SKIP O                                  | PERATIO    | NS      |          | •        |          |            |          |

| BTFSC   | f, b         | Bit Test f, Skip if Clear                            | 1 (2)      | 01      | 10bb     | bfff     | ffff     |            | 1, 2     |

| BTFSS   | f, b         | Bit Test f, Skip if Set                              | 1 (2)      | 01      |          | bfff     |          |            | 1, 2     |

|         |              | LITERAL OPERA                                        | TIONS      |         |          |          |          |            |          |

| ADDLW   | k            | Add literal and W                                    | 1          | 11      | 1110     | kkkk     | kkkk     | C, DC, Z   |          |

| ANDLW   | k            | AND literal with W                                   | 1          | 11      | 1001     | kkkk     | kkkk     | Z          |          |

| IORLW   | k            | Inclusive OR literal with W                          | 1          | 11      | 1000     | kkkk     | kkkk     | Z          |          |

| MOVLB   | k            | Move literal to BSR                                  | 1          | 00      | 0000     | 001k     | kkkk     |            |          |

| MOVLP   | k            | Move literal to PCLATH                               | 1          | 11      | 0001     | 1kkk     | kkkk     |            |          |

| MOVLW   | k            | Move literal to W                                    | 1          | 11      | 0000     | kkkk     | kkkk     |            |          |

| SUBLW   | k            | Subtract W from literal                              | 1          | 11      | 1100     | kkkk     | kkkk     | C, DC, Z   |          |

| XORLW   | k            | Exclusive OR literal with W                          | 1          | 11      | 1010     | kkkk     | kkkk     | Z          |          |

| Note 1: | f the Progra | m Counter (PC) is modified, or a conditional test is | e true the | inetruc | tion roc | uiroc tu | ıo evele | c The seco | nd cyclo |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

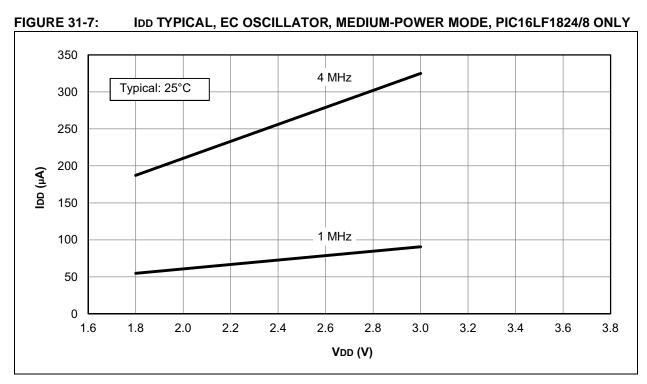

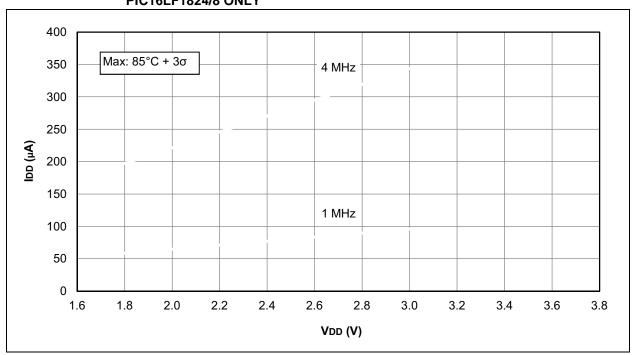

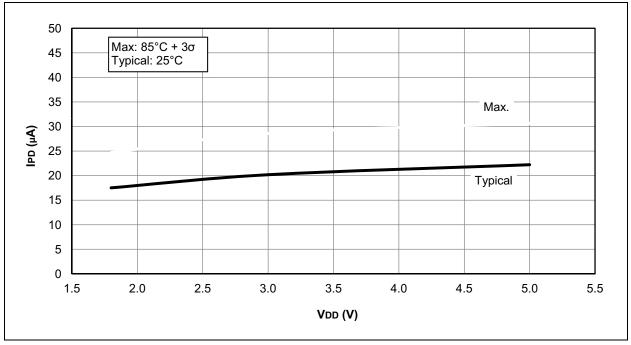

FIGURE 31-8: IDD MAXIMUM, EC OSCILLATOR, MEDIUM-POWER MODE, PIC16LF1824/8 ONLY

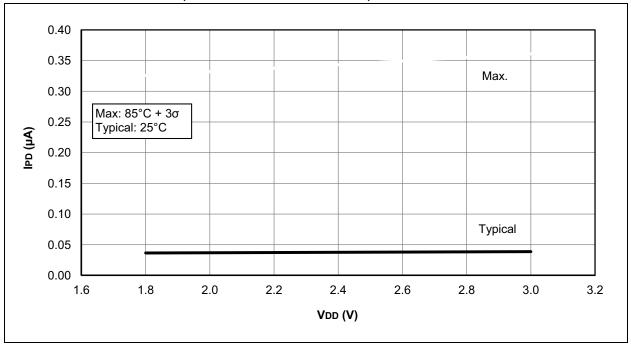

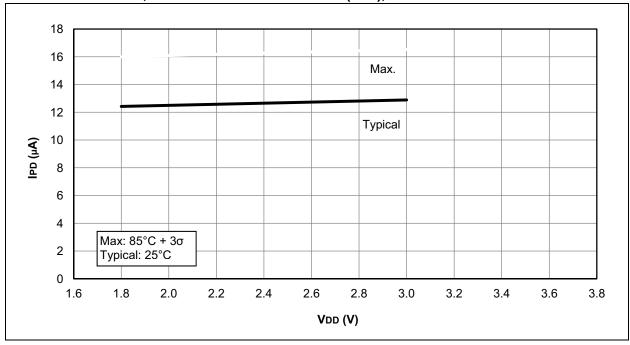

FIGURE 31-21: IPD BASE, LOW-POWER SLEEP MODE, PIC16LF1824/8 ONLY

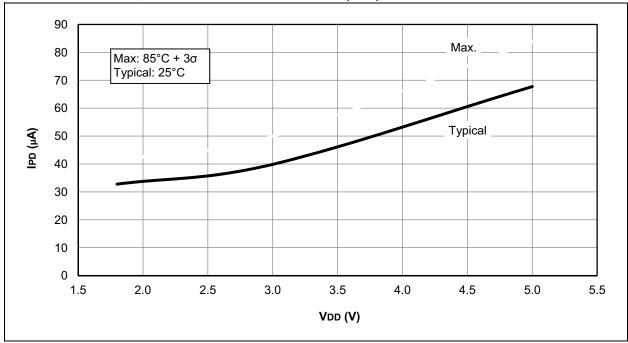

FIGURE 31-22: IPD BASE, LOW-POWER SLEEP MODE, PIC16F1824/8 ONLY

FIGURE 31-25: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC16LF1824/8 ONLY

FIGURE 31-26: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC16F1824/8 ONLY

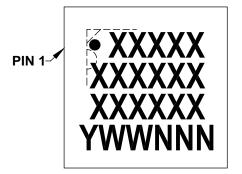

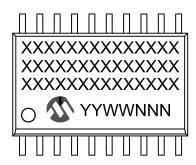

#### 33.2 Package Marking Information (Continued)

16-Lead QFN (4x4x0.9 mm) 16-Lead UQFN (4x4x0.5mm)

PIC16 LF1824 E/ML<sup>®</sup> 110017

Example

1220123

Example

20-Lead PDIP (300 mil)

<u>௴௴௴௴௴௴௴</u> PIC16LF1828 -E/P⊛3

20-Lead SOIC (7.50 mm)

Example