Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3930 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66j11t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                        | Pin Number | Pin B                    | Buffer                       | Description                                                                                                                                                                                              |  |

|---------------------------------------------------------------------------------|------------|--------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fin Name                                                                        | 80-TQFP    | Туре                     | Туре                         | Description                                                                                                                                                                                              |  |

|                                                                                 |            |                          |                              | PORTD is a bidirectional I/O port.                                                                                                                                                                       |  |

| RD0/AD0/PMD0<br>RD0<br>AD0<br>PMD0 <sup>(6)</sup>                               | 72         | 1/0<br>1/0<br>1/0        | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 0.<br>Parallel Master Port data.                                                                                                                            |  |

| RD1/AD1/PMD1<br>RD1<br>AD1<br>PMD1 <sup>(6)</sup>                               | 69         | I/O<br>I/O<br>I/O        | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 1.<br>Parallel Master Port data.                                                                                                                            |  |

| RD2/AD2/PMD2<br>RD2<br>AD2<br>PMD2 <sup>(6)</sup>                               | 68         | 1/0<br>1/0<br>1/0        | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 2.<br>Parallel Master Port data.                                                                                                                            |  |

| RD3/AD3/PMD3<br>RD3<br>AD3<br>PMD3 <sup>(6)</sup>                               | 67         | I/O<br>I/O<br>I/O        | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 3.<br>Parallel Master Port data.                                                                                                                            |  |

| RD4/AD4/PMD4/SDO2<br>RD4<br>AD4<br>PMD4 <sup>(6)</sup><br>SDO2                  | 66         | I/O<br>I/O<br>I/O<br>O   | ST<br>TTL<br>TTL<br>—        | Digital I/O.<br>External Memory Address/Data 4.<br>Parallel Master Port data.<br>SPI data out.                                                                                                           |  |

| RD5/AD5/PMD5/<br>SDI2/SDA2<br>RD5<br>AD5<br>PMD5 <sup>(6)</sup><br>SDI2<br>SDA2 | 65         | I/O<br>I/O<br>I/O<br>I   | ST<br>TTL<br>TTL<br>ST<br>ST | Digital I/O.<br>External Memory Address/Data 5.<br>Parallel Master Port data.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                              |  |

| RD6/AD6/PMD6/<br>SCK2/SCL2<br>RD6<br>AD6<br>PMD6 <sup>(6)</sup><br>SCK2<br>SCL2 | 64         | I/O<br>I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL<br>ST<br>ST | Digital I/O.<br>External Memory Address/Data 6.<br>Parallel Master Port data.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |

| RD7/AD7/PMD7/ <del>SS2</del><br>RD7<br>AD7<br>PMD7 <sup>(6)</sup><br>SS2        | 63         | 1/0<br>1/0<br>1/0<br>1   | ST<br>TTL<br>TTL<br>TTL      | Digital I/O.<br>External Memory Address/Data 7.<br>Parallel Master Port data.<br>SPI slave select input.                                                                                                 |  |

0

Note 1: Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared (Extended Microcontroller mode).

7: Alternate assignment for PMP data and control pins when PMPMX Configuration bit is cleared (programmed).

2: Default assignment for ECCP2/P2A for all devices in all operating modes (CCP2MX is set).

Befault assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

Alternate assignment for ECCP2/P2A when CCP2MX is cleared (Microcontroller mode).

Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

Default assignment for PMP data and control pins when PMPMX Configuration bit is set.

OD

= Output

= Open-Drain (no P diode to VDD)

### TABLE 1-4: PIC18F8XJ1X PINOUT I/O DESCRIPTIONS (CONTINUED)

= Input

= Power

$I^2C = ST$  with  $I^2C^{TM}$  or SMB levels

Т

Р

| Pin Name                                                                              | Pin Number | Pin                       | Buffer                                  | Description                                                                                                                        |

|---------------------------------------------------------------------------------------|------------|---------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                              | 80-TQFP    | Туре                      | Туре                                    | Description                                                                                                                        |

|                                                                                       |            |                           |                                         | PORTF is a bidirectional I/O port.                                                                                                 |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT                                                  | 23         | I/O<br>I<br>O             | ST<br>Analog<br>—                       | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.                                                                            |

| RF2/PMA5/AN7/C1OUT<br>RF2<br>PMA5<br>AN7<br>C1OUT                                     | 18         | I/O<br>O<br>I<br>O        | ST<br>—<br>Analog<br>—                  | Digital I/O.<br>Parallel Master Port address.<br>Analog Input 7.<br>Comparator 1 output.                                           |

| RF3/AN8/C2INB<br>RF3<br>AN8<br>C2INB                                                  | 17         | I/O<br>I<br>I             | ST<br>Analog<br>Analog                  | Digital input.<br>Analog Input 8.<br>Comparator 2 Input B.                                                                         |

| RF4/AN9/C2INA<br>RF4<br>AN9<br>C2INA                                                  | 16         | I/O<br>I<br>I             | ST<br>Analog<br>Analog                  | Digital input.<br>Analog Input 8.<br>Comparator 2 Input A.                                                                         |

| RF5/PMD2/AN10/<br>C1INB/CVREF<br>RF5<br>PMD2 <sup>(7)</sup><br>AN10<br>C1INB<br>CVREF | 15         | I/O<br>I/O<br>I<br>I<br>O | ST<br>TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Parallel Master Port address.<br>Analog Input 10.<br>Comparator 1 Input B.<br>Comparator reference voltage output. |

| RF6/PMD1/AN11/C1INA<br>RF6<br>PMD1 <sup>(7)</sup><br>AN11<br>C1INA                    | 14         | I/O<br>I/O<br>I           | ST<br>TTL<br>Analog<br>Analog           | Digital I/O.<br>Parallel Master Port address.<br>Analog Input 11.<br>Comparator 1 Input A.                                         |

| RF7/PMD0/ <u>SS1</u><br>RF7<br>PMD0 <sup>(7)</sup><br>SS1                             | 13         | I/O<br>I/O<br>I           | ST<br>TTL<br>TTL                        | Digital I/O.<br>Parallel Master Port address.<br>SPI slave select input.                                                           |

| Legend: TTL = TTL compa<br>ST = Schmitt Trig                                          |            | /IOS leve                 | els                                     | CMOS = CMOS compatible input or output<br>Analog = Analog input                                                                    |

#### **TABLE 1-4:** PIC18F8XJ1X PINOUT I/O DESCRIPTIONS (CONTINUED)

Т

= Input = Power Р

$I^2C = ST$  with  $I^2C^{TM}$  or SMB levels

Note 1: Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared (Extended Microcontroller mode).

0

OD

= Output

= Open-Drain (no P diode to VDD)

2: Default assignment for ECCP2/P2A for all devices in all operating modes (CCP2MX is set).

3: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

4: Alternate assignment for ECCP2/P2A when CCP2MX is cleared (Microcontroller mode).

5: Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

6: Default assignment for PMP data and control pins when PMPMX Configuration bit is set.

7: Alternate assignment for PMP data and control pins when PMPMX Configuration bit is cleared (programmed).

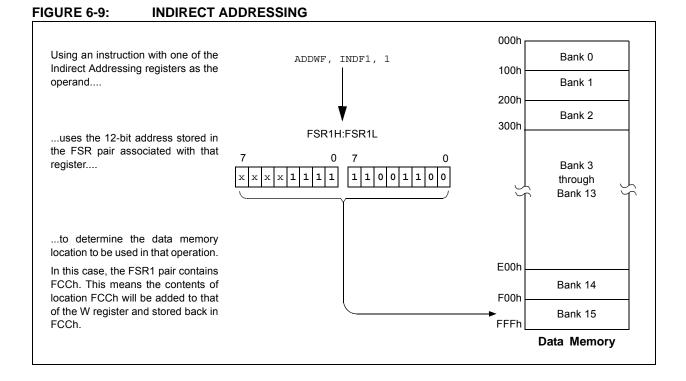

### 6.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1                   | R/W-1                          | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0            |

|-------------------------|--------------------------------|------------------------------------|------------------|------------------|------------------|-----------------|------------------|

| INT2IP                  | INT1IP                         | INT3IE                             | INT2IE           | INT1IE           | INT3IF           | INT2IF          | INT1IF           |

| bit 7                   |                                |                                    |                  |                  |                  |                 | bit 0            |

|                         |                                |                                    |                  |                  |                  |                 |                  |

| Legend:                 | abla bit                       | \\/ = \\/ritable                   | h it             | II – Unimplor    | monted bit rea   | d oo 'O'        |                  |

| R = Reada<br>-n = Value |                                | W = Writable<br>'1' = Bit is set   |                  | '0' = Bit is cle | nented bit, read | x = Bit is unkr |                  |

|                         | arron                          |                                    |                  |                  | aleu             |                 |                  |

| bit 7                   | INT2IP: INT2                   | External Interr                    | upt Priority bit |                  |                  |                 |                  |

|                         | 1 = High prio                  |                                    |                  |                  |                  |                 |                  |

|                         | 0 = Low prior                  | -                                  |                  |                  |                  |                 |                  |

| bit 6                   |                                | External Interr                    | upt Priority bit |                  |                  |                 |                  |

|                         | 1 = High prio<br>0 = Low prior |                                    |                  |                  |                  |                 |                  |

| bit 5                   | •                              | External Interr                    | upt Enable bit   |                  |                  |                 |                  |

|                         |                                | the INT3 extern                    | •                |                  |                  |                 |                  |

|                         | 0 = Disables                   | the INT3 exter                     | nal interrupt    |                  |                  |                 |                  |

| bit 4                   |                                | External Interr                    | -                |                  |                  |                 |                  |

|                         |                                | the INT2 extern<br>the INT2 extern |                  |                  |                  |                 |                  |

| bit 3                   |                                | External Interr                    | •                |                  |                  |                 |                  |

| Sit 0                   |                                | the INT1 exteri                    | -                |                  |                  |                 |                  |

|                         |                                | the INT1 exter                     |                  |                  |                  |                 |                  |

| bit 2                   | INT3IF: INT3                   | External Interr                    | upt Flag bit     |                  |                  |                 |                  |

|                         |                                |                                    |                  | must be cleare   | d in software)   |                 |                  |

| <b>L:1</b>              |                                |                                    | rupt did not occ | cur              |                  |                 |                  |

| bit 1                   |                                | External Interr                    |                  | must be cleare   | d in softwara)   |                 |                  |

|                         |                                |                                    | rupt did not occ |                  | u ili soltwale)  |                 |                  |

| bit 0                   |                                | External Interr                    | •                |                  |                  |                 |                  |

|                         |                                |                                    |                  | must be cleare   | d in software)   |                 |                  |

|                         | 0 = The INT1                   | l external inter                   | rupt did not occ | cur              |                  |                 |                  |

| Note:                   | Interrupt flag bits            |                                    |                  |                  |                  |                 |                  |

|                         | enable bit or the (            |                                    |                  |                  |                  |                 | errupt flag bits |

|                         | are clear prior to             | enabling an int                    | errupt. This fea | ature allows for | sonware pollin   | ıg.             |                  |

#### REGISTER 11-1: ODCON1: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|-----|--------|--------|---------|---------|---------|

| _     |     |     | CCP5OD | CCP4OD | ECCP3OD | ECCP2OD | ECCP10D |

| bit 7 |     |     |        |        |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 4-3 | CCP5OD:CCP4OD: CCPx Open-Drain Output Enable bits                                                                                      |

|         | <ul> <li>1 = Open-drain output is on the CCPx pin (Capture/PWM modes) is enabled</li> <li>0 = Open-drain output is disabled</li> </ul> |

| bit 2-0 | ECCP3OD: ECCP1OD: ECCPx Open-Drain Output Enable bits                                                                                  |

|         | <ul> <li>1 = Open-drain output is on the ECCPx pin (Capture mode) is enabled</li> <li>0 = Open-drain output is disabled</li> </ul>     |

### REGISTER 11-2: ODCON2: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 2

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------------|-----|-----|-----|-----|-----|-------|-------|

| —           | —   | —   | —   | —   | _   | U2OD  | U10D  |

| bit 7 bit 0 |     |     |     |     |     |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 U2OD:U1OD: EUSARTx Open-Drain Output Enable bits

1 = Open-drain output is on the TXx pin is enabled

0 = Open-drain output is disabled

#### REGISTER 11-3: ODCON3: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 3

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|---------|-----|-----|-----|-----|-----|--------|--------|

| —       | _   | —   | —   | _   | —   | SPI2OD | SPI10D |

| bit 7   |     |     |     |     |     |        | bit 0  |

| Legend: |     |     |     |     |     |        |        |

| Logona.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 SPI2OD:SPI1OD: SPI Open-Drain Output Enable bits

1 = Open-drain output is on the SDOx pin is enabled

0 = Open-drain output is disabled

### 11.2 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. It may function as a 6-bit or 7-bit port, depending on the oscillator mode selected. The corresponding Data Direction and Output Latch registers are TRISA and LATA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin; it is also multiplexed as the Parallel Master Port data pin (in 80-pin devices). The other PORTA pins are multiplexed with the analog VREF+ and VREF- inputs. The operation of pins, RA<5,3:0>, as A/D Converter inputs is selected by clearing or setting the appropriate PCFGx control bits in the ANCON0 register.

- Note 1: RA5 (RA5/PMD4/AN4) is multiplexed as an analog input in all devices and Parallel Master Port data in 80-pin devices.

- RA5 and RA<3:0> are configured as analog inputs on any Reset and are read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

OSC2/CLKO/RA6 and OSC1/CLKI/RA7 normally serve as the external circuit connections for the external (primary) oscillator circuit (HS and HSPLL Oscillator modes), or the external clock input (EC and ECPLL Oscillator modes). In these cases, RA6 and RA7 are not available as digital I/O, and their corresponding TRIS and LAT bits are read as '0'. For INTIO and INTPLL Oscillator modes (FOSC2 Configuration bit is '0'), either RA7 or both RA6 and RA7 automatically become available as digital I/O, depending on the oscillator mode selected. When RA6 is not configured as a digital I/O, in these cases, it provides a clock output at FOSC/4. A list of the possible configurations for RA6 and RA7, based on oscillator mode, is provided in Table 11-3. For these pins, the corresponding PORTA, TRISA and LATA bits are only defined when the pins are configured as I/O.

| TABLE 11-3: | FUNCTION OF RA<7:6> IN |

|-------------|------------------------|

|             | INTIO AND INTPLL MODES |

| Oscillator Mode<br>(FOSC<2:0> Configuration) | RA6  | RA7 |

|----------------------------------------------|------|-----|

| INTPLL1 (011)                                | CLKO | I/O |

| INTPLL2 (010)                                | I/O  | I/O |

| INTIO1 (001)                                 | CLKO | I/O |

| INTIO2 (000)                                 | I/O  | I/O |

**Legend:** CLKO = Fosc/4 clock output; I/O = digital port.

| CLRF  | PORTA         | ; | Initialize PORTA by    |

|-------|---------------|---|------------------------|

|       |               | ; | clearing output        |

|       |               | ; | data latches           |

| CLRF  | LATA          | ; | Alternate method to    |

|       |               | ; | clear data latches     |

| BSF   | WDTCON, ADSHR | ; | Enable write/read to   |

|       |               | ; | the shared SFR         |

| MOVLW | 1Fh           | ; | Configure A/D          |

| MOVWF | ANCON0        | ; | for digital inputs     |

| BCF   | WDTCON, ADSHR | ; | Disable write/read     |

|       |               | ; | to the shared SFR      |

| MOVLW | H'CF'         | ; | Value used to          |

|       |               | ; | initialize             |

|       |               | ; | data direction         |

| MOVWF | TRISA         | ; | Set RA<3:0> as inputs, |

|       |               | ; | RA<5:4> as outputs     |

|       |               |   |                        |

| Pin Name                 | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                        |

|--------------------------|---------------------|-----------------|-----|-------------|--------------------------------------------------------------------------------------------------------------------|

| RF1/AN6/                 | RF1                 | 0               | 0   | DIG         | LATF<1> data output; not affected by analog input.                                                                 |

| C2OUT                    |                     | 1               | I   | ST          | PORTF<1> data input; disabled when analog input is enabled.                                                        |

|                          | AN6                 | 1               | I   | ANA         | A/D Input Channel 6. Default configuration on POR.                                                                 |

|                          | C2OUT               | х               | 0   | DIG         | Comparator 2 output.                                                                                               |

| RF2/PMA5/                | RF2                 | 0               | 0   | DIG         | LATF<2> data output; not affected by analog input.                                                                 |

| AN7//C1OUT               |                     | 1               | Ι   | ST          | PORTF<2> data input; disabled when analog input is enabled.                                                        |

|                          | PMA5                | х               | 0   | DIG         | Parallel Master Port address.                                                                                      |

|                          | AN7                 | 1               | Ι   | ANA         | A/D Input Channel 7. Default configuration on POR.                                                                 |

|                          | C10UT               | х               | 0   | DIG         | Comparator 1 output.                                                                                               |

| RF3/AN8/                 | RF3                 | 0               | 0   | DIG         | LATF<3> data output; not affected by analog input.                                                                 |

| C2INB                    |                     | 1               | Ι   | ST          | PORTF<3> data input; disabled when analog input is enabled.                                                        |

|                          | AN8                 | 1               |     | ANA         | A/D Input Channel 8. Default configuration on POR.                                                                 |

|                          | C2INB               | х               | Ι   | ANA         | Comparator 2 Input B.                                                                                              |

| RF4/AN9/                 | RF4                 | 0               | 0   | DIG         | LATF<4> data output; not affected by analog input.                                                                 |

| C2INA                    |                     | 1               |     | ST          | PORTF<4> data input; disabled when analog input is enabled.                                                        |

|                          | AN9                 | 1               | Ι   | ANA         | A/D Input Channel 9. Default configuration on POR.                                                                 |

|                          | C2INA               | х               | Ι   | ANA         | Comparator 2 Input A.                                                                                              |

| RF5/PMD2/<br>AN10/C1INB/ | RF5                 | 0               | 0   | DIG         | LATF<5> data output; not affected by analog input. Disabled when CVREF output is enabled.                          |

| CVREF                    |                     | 1               | I   | ST          | PORTF<5> data input; disabled when analog input is enabled.<br>Disabled when CVREF output is enabled.              |

|                          | PMD2 <sup>(1)</sup> | х               | 0   | DIG         | Parallel Master Port data out.                                                                                     |

|                          |                     | х               | Ι   | TTL         | Parallel Master Port data input.                                                                                   |

|                          | AN10                | 1               | I   | ANA         | A/D Input Channel 10 and Comparator C1+ input. Default input configuration on POR.                                 |

|                          | C1INB               | х               | I   | ANA         | Comparator 1 Input B.                                                                                              |

|                          | CVREF               | х               | 0   | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                   |

| RF6/PMD1/                | RF6                 | 0               | 0   | DIG         | LATF<6> data output; not affected by analog input.                                                                 |

| AN11/C1INA               |                     | 1               | I   | ST          | PORTF<6> data input; disabled when analog input is enabled.                                                        |

|                          | PMD1 <sup>(1)</sup> | x               | 0   | DIG         | Parallel Master Port data out.                                                                                     |

|                          |                     | х               | I   | TTL         | Parallel Master Port data input.                                                                                   |

|                          | AN11                | 1               | I   | ANA         | A/D Input Channel 11 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |

|                          | C1INA               | x               | I   | ANA         | Comparator 1 Input A.                                                                                              |

| RF7/PMD0/                | RF7                 | 0               | 0   | DIG         | LATF<7> data output.                                                                                               |

| SS1                      |                     | 1               | I   | ST          | PORTF<7> data input.                                                                                               |

|                          | PMD0 <sup>(1)</sup> | x               | 0   | DIG         | Parallel Master Port data out.                                                                                     |

|                          |                     | x               | I   | TTL         | Parallel Master Port data input.                                                                                   |

|                          | SS1                 | 1               | 1   | TTL         | Slave select input for MSSP1 module.                                                                               |

### TABLE 11-14: PORTF FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input,

TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate PMP configuration when the PMPMX Configuration bit = 0; available on 80-pin devices only.

### REGISTER 12-2: PMCONL: PARALLEL PORT CONTROL LOW BYTE REGISTER

| R/W-0        | R/W-0                                    | R/W-0 <sup>(1)</sup>                                    | R/W-0 <sup>(1)</sup>                        | R/W-0 <sup>(1)</sup>      | R/W-0                 | R/W-0           | R/W-0         |

|--------------|------------------------------------------|---------------------------------------------------------|---------------------------------------------|---------------------------|-----------------------|-----------------|---------------|

| CSF1         | CSF0                                     | ALP                                                     | CS2P                                        | CS1P                      | BEP                   | WRSP            | RDSP          |

| oit 7        |                                          |                                                         |                                             |                           |                       |                 | bit           |

|              |                                          |                                                         |                                             |                           |                       |                 |               |

| Legend:      |                                          |                                                         |                                             |                           |                       |                 |               |

| R = Readab   |                                          | W = Writable                                            |                                             | U = Unimplen              |                       |                 |               |

| -n = Value a | IT POR                                   | '1' = Bit is set                                        |                                             | '0' = Bit is clea         | ared                  | x = Bit is unkn | iown          |

| bit 7-6      | 11 <b>= Reserv</b><br>10 <b>= PMCS</b> 1 | and PMCS2 fu                                            | nction as chip                              |                           | Address Bit 14        | 4 (PMADDRH A    | ddress Bit 6) |

| bit 5        | ALP: Addres                              | s Latch Polarity                                        | <sup>,</sup> bit <sup>(1)</sup><br>d PMALH) | lress Bits 15 an          | d 14 (PMADD           | RH Address Bit  | s 7 and 6)    |

| oit 4        | CS2P: Chip                               | ow (PMALL and<br>Select 2 Polarity<br>igh (PMCS2)       | ,                                           |                           |                       |                 |               |

| bit 3        |                                          | ow (PMCS2)<br>Select 1 Polarity<br>igh (PMCS1/PM        |                                             |                           |                       |                 |               |

|              |                                          | w (PMCS1/PM                                             |                                             |                           |                       |                 |               |

| bit 2        | -                                        | nable Polarity b                                        |                                             |                           |                       |                 |               |

|              |                                          | able active-high<br>able active-low (                   |                                             |                           |                       |                 |               |

| bit 1        | WRSP: Write                              | e Strobe Polarity                                       | / bit                                       |                           |                       |                 |               |

|              | 1 = Write str                            | odes and Maste<br>obe active-high<br>obe active-low     | (PMWR)                                      | <u>MODEH&lt;1:0&gt; =</u> | <u>: 00, 01, 10):</u> |                 |               |

|              | 1 = Enable                               | node 1 (PMMOE<br>strobe active-hig<br>strobe active-lov | gh (PMENB)                                  | <u>L):</u>                |                       |                 |               |

| oit 0        | RDSP: Read                               | I Strobe Polarity                                       | bit                                         |                           |                       |                 |               |

|              | 1 = Read st                              | odes and Maste<br>robe active-high<br>robe active-low   | (PMRD)                                      | <u>MODEH&lt;1:0&gt; =</u> | <u>: 00, 01, 10):</u> |                 |               |

|              |                                          | node 1 (PMMOE<br>ite strobe active                      | e-high (PMRD/                               | PMWR)                     |                       |                 |               |

### 14.7 Considerations in Asynchronous Counter Mode

Following a Timer1 interrupt and an update to the TMR1 registers, the Timer1 module uses a falling edge on its clock source to trigger the next register update on the rising edge. If the update is completed after the clock input has fallen, the next rising edge will not be counted.

If the application can reliably update TMR1 before the timer input goes low, no additional action is needed. Otherwise, an adjusted update can be performed fol-

lowing a later Timer1 increment. This can be done by monitoring TMR1L within the interrupt routine until it increments, and then updating the TMR1H:TMR1L register pair while the clock is low, or one-half of the period of the clock source. Assuming that Timer1 is being used as a Real-Time Clock, the clock source is a 32.768 kHz crystal oscillator. In this case, one-half period of the clock is 15.25  $\mu$ s.

The Real-Time Clock application code in Example 14-1 shows a typical ISR for Timer1, as well as the optional code required if the update cannot be done reliably within the required interval.

### EXAMPLE 14-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                                               |

|---------|--------|--------------|---------------------------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                                       |

|         | CLRF   | TMR1L        |                                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator                 |

|         | CLRF   | secs         | ; Initialize timekeeping registers                            |

|         | CLRF   | mins         | ;                                                             |

|         | MOVLW  | .12          |                                                               |

|         | MOVWF  | hours        |                                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                                     |

|         | RETURN |              |                                                               |

| RTCisr  |        |              |                                                               |

|         |        |              | ; Insert the next 4 lines of code when TMR1                   |

|         |        |              | ; can not be reliably updated before clock pulse goes low     |

|         | BTFSC  | TMR1L,0      | ; wait for TMR1L to become clear                              |

|         | BRA    | \$-2         | ; (may already be clear)                                      |

|         | BTFSS  | TMR1L,0      | ; wait for TMR1L to become set                                |

|         | BRA    | \$-2         | ; TMR1 has just incremented                                   |

|         |        |              | ; If TMR1 update can be completed before clock pulse goes low |

|         |        |              | ; Start ISR here                                              |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                                        |

|         | INCF   | secs, F      | ; Increment seconds                                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                         |

|         | CPFSGT | secs         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | secs         | ; Clear seconds                                               |

|         | INCF   | mins, F      | ; Increment minutes                                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                         |

|         | CPFSGT | mins         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | mins         | ; clear minutes                                               |

|         | INCF   | hours, F     | ; Increment hours                                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                           |

|         | CPFSGT | hours        |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | hours        | ; Reset hours                                                 |

|         | RETURN |              | ; Done                                                        |

|         |        |              |                                                               |

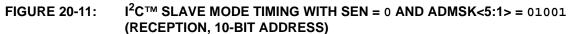

### REGISTER 20-3: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0        | R/W-0                                                                                                                   | R-0                                  |          | R-0              |          | R-0          | R-0                       | R-0               | R-0      |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|------------------|----------|--------------|---------------------------|-------------------|----------|--|--|

| SMP          | CKE                                                                                                                     | D/A                                  |          | P <sup>(1)</sup> |          | S(1)         | R/W <sup>(2,3)</sup>      | UA                | BF       |  |  |

| bit 7        | •                                                                                                                       |                                      |          |                  |          |              | •                         | •                 | bit C    |  |  |

|              |                                                                                                                         |                                      |          |                  |          |              |                           |                   |          |  |  |

| Legend:      |                                                                                                                         |                                      |          |                  |          |              |                           |                   |          |  |  |

| R = Readab   |                                                                                                                         | W = Writab                           |          |                  |          | -            | mented bit, rea           |                   |          |  |  |

| -n = Value a | t POR                                                                                                                   | '1' = Bit is :                       | set      |                  | .0,      | = Bit is cle | eared                     | x = Bit is unkn   | iown     |  |  |

| bit 7        | SMP: Slew                                                                                                               | Rate Control                         | bit      |                  |          |              |                           |                   |          |  |  |

|              | In Master or Slave mode:                                                                                                |                                      |          |                  |          |              |                           |                   |          |  |  |

|              |                                                                                                                         | ate control is d<br>ate control is e |          |                  |          |              | de (100 kHz ar<br>00 kHz) | nd 1 MHz)         |          |  |  |

| bit 6        | CKE: SMBL                                                                                                               |                                      |          | a lot tilgt      |          | a mede (1    | 100 Hi 12)                |                   |          |  |  |

|              | In Master or                                                                                                            | Slave mode:                          |          |                  |          |              |                           |                   |          |  |  |

|              |                                                                                                                         | s SMBus-spec<br>s SMBus-spec         |          |                  |          |              |                           |                   |          |  |  |

| bit 5        | D/A: Data/A                                                                                                             | -                                    |          | puto             |          |              |                           |                   |          |  |  |

|              | In Master m                                                                                                             | iode:                                |          |                  |          |              |                           |                   |          |  |  |

|              | Reserved.                                                                                                               |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | In Slave mo                                                                                                             |                                      |          |                  |          |              |                           |                   |          |  |  |

|              |                                                                                                                         | s that the last<br>s that the last   |          |                  |          |              |                           |                   |          |  |  |

| bit 4        | <ul> <li>Indicates that the last byte received or transmitted was address</li> <li>P: Stop bit<sup>(1)</sup></li> </ul> |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | 1 = Indicates that a Stop bit has been detected last                                                                    |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | 0 = Stop bit was not detected last                                                                                      |                                      |          |                  |          |              |                           |                   |          |  |  |

| bit 3        | <b>S:</b> Start bit <sup>(1)</sup><br>1 = Indicates that a Start bit has been detected last                             |                                      |          |                  |          |              |                           |                   |          |  |  |

|              |                                                                                                                         | was not deteo                        |          |                  | etected  | last         |                           |                   |          |  |  |

| bit 2        |                                                                                                                         | Write Informa                        |          |                  |          |              |                           |                   |          |  |  |

|              | In Slave mo                                                                                                             |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | 1 = Read                                                                                                                |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | 0 = Write                                                                                                               |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | <u>In Master m</u><br>1 = Transmi                                                                                       | i <u>ode:</u><br>it is in progres    | \$       |                  |          |              |                           |                   |          |  |  |

|              |                                                                                                                         | it is not in prog                    |          |                  |          |              |                           |                   |          |  |  |

| bit 1        | UA: Update                                                                                                              | Address bit (                        | 10-Bit   | t Slave m        | ode on   | ly)          |                           |                   |          |  |  |

|              |                                                                                                                         | s that the use<br>does not nee       |          |                  |          | address i    | n the SSPxAD              | D register        |          |  |  |

| bit 0        |                                                                                                                         | Full Status bit                      |          |                  | ,u       |              |                           |                   |          |  |  |

|              | In Transmit                                                                                                             |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | 1 = SSPxBl                                                                                                              | JF is full                           |          |                  |          |              |                           |                   |          |  |  |

|              | 0 = SSPxBl                                                                                                              |                                      |          |                  |          |              |                           |                   |          |  |  |

|              | In Receive r                                                                                                            | <u>mode:</u><br>JF is full (doe:     | a not i  | noludo th        |          | and Stor     | hite)                     |                   |          |  |  |

|              |                                                                                                                         | JF is empty (c                       |          |                  |          |              |                           |                   |          |  |  |

| Note 1: ⊺    | his bit is cleare                                                                                                       | ed on Reset a                        | nd wh    | en SSPE          | N is cl  | eared.       |                           |                   |          |  |  |

|              |                                                                                                                         |                                      |          |                  |          |              | ess match. This           | bit is only valid | from the |  |  |

| а            | ddress match                                                                                                            | to the next Sta                      | art bit, | Stop bit         | or not 7 | ACK bit.     |                           |                   |          |  |  |

| • •          |                                                                                                                         | HL OFN DOF                           | NI DE    |                  | 1 1      |              | and a star of the star    |                   |          |  |  |

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

ADD W to f

f {,d {,a}}

01da

Add W to register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the

result is stored back in register 'f'.

If 'a' is '0', the Access Bank is selected.

If 'a' is '1', the BSR is used to select the

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \leq 95$  (5Fh). See

Section 26.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details.

Q3

Process

Data

REG, 0, 0

ffff

ffff

Q4

Write to

destination

ADDWF

a ∈ [0,1]

$0 \leq f \leq 255$  $d \in [0,1]$

$(W) + (f) \rightarrow dest$

N, OV, C, DC, Z

0010

GPR bank.

> Q2 Read

register 'f

ADDWF

17h

0C2h

0D9h

0C2h

#### 26.1.1 STANDARD INSTRUCTION SET

| ADDLW                             | ADD Litera              | l to W                         |                                  | ADDWF                                                       | AI               |

|-----------------------------------|-------------------------|--------------------------------|----------------------------------|-------------------------------------------------------------|------------------|

| Syntax:                           | ADDLW                   | k                              |                                  | Syntax:                                                     | A                |

| Operands:                         | $0 \leq k \leq 255$     |                                |                                  | Operands:                                                   | 0                |

| Operation:                        | $(W) + k \rightarrow V$ | N                              |                                  |                                                             | d<br>a           |

| Status Affected:                  | N, OV, C, D             | С, Z                           |                                  | Operation:                                                  | (W               |

| Encoding:                         | 0000                    | 1111 kł                        | kk kkkk                          | Status Affected:                                            | (V)<br>N,        |

| Description:                      |                         | ts of W are a<br>k' and the re | dded to the<br>sult is placed in | Encoding:<br>Description:                                   | Ac               |

| Words:                            | 1                       |                                |                                  |                                                             | re               |

| Cycles:                           | 1                       |                                |                                  |                                                             | re:<br>If '      |

| Q Cycle Activity:                 |                         |                                |                                  |                                                             | If '             |

| Q1                                | Q2                      | Q3                             | Q4                               |                                                             | Gl               |

| Decode                            | Read<br>literal 'k'     | Process<br>Data                | Write to<br>W                    |                                                             | lf '<br>se<br>in |

| <u>Example:</u><br>Before Instruc |                         | .5h                            |                                  |                                                             | m<br>Se<br>Bi    |

| W =                               | 10h                     |                                |                                  |                                                             | Li               |

| After Instructio<br>W =           | on<br>25h               |                                |                                  | Words:                                                      | 1                |

|                                   |                         |                                |                                  | Cycles:                                                     | 1                |

|                                   |                         |                                |                                  | Q Cycle Activity:                                           |                  |

|                                   |                         |                                |                                  | Q1                                                          |                  |

|                                   |                         |                                |                                  | Decode                                                      | F<br>reg         |

|                                   |                         |                                |                                  | Example:                                                    | AI               |

|                                   |                         |                                |                                  | Before Instruct<br>W<br>REG<br>After Instructio<br>W<br>REG | =<br>=           |

|                                   |                         |                                |                                  |                                                             |                  |

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| BTFS        | C                                                                             | Bit Test File                                                                 | , Skip if Clear                                                                                                               |                                                                  | BTFS          | S                                                                        | Bit Test File                                                                 | , Skip if Set                                                                                                                   |                                                                 |

|-------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Synta       | x:                                                                            | BTFSC f, b                                                                    | {,a}                                                                                                                          |                                                                  | Syntax        | (:                                                                       | BTFSS f, b {                                                                  | ,a}                                                                                                                             |                                                                 |

| Opera       | ands:                                                                         | $0 \leq f \leq 255$                                                           |                                                                                                                               |                                                                  | Opera         | nds:                                                                     | $0 \leq f \leq 255$                                                           |                                                                                                                                 |                                                                 |

|             |                                                                               | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                        |                                                                                                                               |                                                                  |               |                                                                          | 0 ≤ b < 7<br>a ∈ [0,1]                                                        |                                                                                                                                 |                                                                 |

| Opera       | ation:                                                                        | skip if (f <b>)</b>                                                           | = 0                                                                                                                           |                                                                  | Opera         | tion:                                                                    | skip if (f <b>)</b>                                                           | = 1                                                                                                                             |                                                                 |

| •           | s Affected:                                                                   | None                                                                          |                                                                                                                               |                                                                  | •             | Affected:                                                                | None                                                                          |                                                                                                                                 |                                                                 |

| Enco        |                                                                               | 1011                                                                          | bbba ff                                                                                                                       | ff ffff                                                          | Encod         | ina:                                                                     | 1010                                                                          | bbba ff:                                                                                                                        | ff ffff                                                         |

| Desci       | iption:                                                                       | instruction is<br>the next inst<br>current instru<br>and a NOP is             | gister 'f' is '0', '<br>skipped. If bit<br>ruction fetched<br>uction execution<br>executed inst<br>rcle instruction.          | 'b' is '0', then<br>during the<br>in is discarded<br>ead, making | Descri        | ption:                                                                   | instruction is<br>the next inst<br>current instru<br>and a NOP is             | gister 'f' is '1', t<br>skipped. If bit<br>ruction fetched<br>uction executio<br>executed instruction.                          | 'b' is '1', then<br>during the<br>n is discarded<br>ead, making |

|             |                                                                               |                                                                               | e Access Banl<br>BSR is used to                                                                                               | is selected. If select the                                       |               |                                                                          |                                                                               | e Access Bank<br>BSR is used to                                                                                                 | is selected. If select the                                      |

|             |                                                                               | is enabled, t<br>Indexed Lite<br>whenever f ≤<br>Section 26.2<br>Bit-Oriented | d the extended<br>his instruction<br>ral Offset Addr<br>≤ 95 (5Fh). See<br>2.3 "Byte-Orie<br>d Instructions<br>et Mode" for d | essing mode<br>ented and<br>in Indexed                           |               |                                                                          | set is enable<br>Indexed Lite<br>whenever f ≤<br>Section 26.2<br>Bit-Oriented | d the extended<br>d, this instructi<br>ral Offset Addr<br>g 95 (5Fh). See<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | on operates in<br>essing mode<br>nted and<br>in Indexed         |

| Word        | s:                                                                            | 1                                                                             |                                                                                                                               |                                                                  | Words         | :                                                                        | 1                                                                             |                                                                                                                                 |                                                                 |

| Cycle       | s:                                                                            |                                                                               | cles if skip and<br>2-word instruc                                                                                            |                                                                  | Cycles        | :                                                                        |                                                                               | vcles if skip an<br>a 2-word instru                                                                                             |                                                                 |

| Q C\        | cle Activity:                                                                 | - , -                                                                         |                                                                                                                               |                                                                  | Q Cv          | cle Activity:                                                            | - )                                                                           |                                                                                                                                 |                                                                 |

| ر د د ا     | Q1                                                                            | Q2                                                                            | Q3                                                                                                                            | Q4                                                               |               | Q1                                                                       | Q2                                                                            | Q3                                                                                                                              | Q4                                                              |

|             | Decode                                                                        | Read                                                                          | Process                                                                                                                       | No                                                               | Γ             | Decode                                                                   | Read                                                                          | Process                                                                                                                         | No                                                              |

|             |                                                                               | register 'f'                                                                  | Data                                                                                                                          | operation                                                        |               |                                                                          | register 'f'                                                                  | Data                                                                                                                            | operation                                                       |