Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3930 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

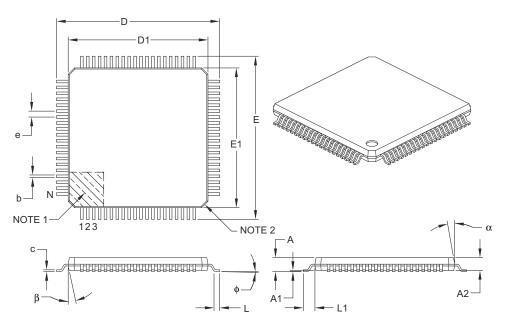

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67j11-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.3 Data Memory Organization

| Note: | The operation of some aspects of data    |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | memory are changed when the PIC18        |  |  |  |  |  |  |  |

|       | extended instruction set is enabled. See |  |  |  |  |  |  |  |

|       | Section 6.6 "Data Memory and the         |  |  |  |  |  |  |  |

|       | Extended Instruction Set" for more       |  |  |  |  |  |  |  |

|       | information.                             |  |  |  |  |  |  |  |

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. The PIC18F87J11 family implements all available banks and provide 3936 bytes of data memory available to the user. Figure 6-7 shows the data memory organization for the devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this section.

To ensure that commonly used registers (select SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to select SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 6.3.2 "Access Bank"** provides a detailed description of the Access RAM.

#### 6.3.1 BANK SELECT REGISTER

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer. Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits of a location's address. The instruction itself includes the 8 Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 6-8.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh, will end up resetting the Program Counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-7 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

### 6.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy more than the top half of Bank 15 (F5Ah to FFFh). A list of these registers is given inTable 6-3, Table 6-4 and Table 6-5.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's

**Note:** Addresses, F5Ah through F5Fh, are not part of the Access Bank. These registers must always be accessed using the Bank Select Register. Addresses, F40h to F59h, are not implemented and are not accessible to the user.

### TABLE 6-3: SPECIAL FUNCTION REGISTER MAP FOR PIC18F87J11 FAMILY DEVICES

| Address | Name                    | Address | Name                   | Address | Name     | Address | Name                 | Address | Name                   | Address | Name    |

|---------|-------------------------|---------|------------------------|---------|----------|---------|----------------------|---------|------------------------|---------|---------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>   | FBFh    | ECCP1AS  | F9Fh    | IPR1                 | F7Fh    | SPBRGH1                | F5Fh    | PMDIN2H |

| FFEh    | TOSH                    | FDEh    | POSTINC2(1)            | FBEh    | ECCP1DEL | F9Eh    | PIR1                 | F7Eh    | BAUDCON1               | F5Eh    | PMDIN2L |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(1)            | FBDh    | CCPR1H   | F9Dh    | PIE1                 | F7Dh    | SPBRGH2                | F5Dh    | PMEH    |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup> | FBCh    | CCPR1L   | F9Ch    | RCSTA2               | F7Ch    | BAUDCON2               | F5Ch    | PMEL    |

| FFBh    | PCLATU                  | FDBh    | PLUSW2(1)              | FBBh    | CCP1CON  | F9Bh    | OSCTUNE              | F7Bh    | TMR3H                  | F5Bh    | PMSTATH |

| FFAh    | PCLATH                  | FDAh    | FSR2H                  | FBAh    | ECCP2AS  | F9Ah    | TRISJ <sup>(2)</sup> | F7Ah    | TMR3L                  | F5Ah    | PMSTATL |

| FF9h    | PCL                     | FD9h    | FSR2L                  | FB9h    | ECCP2DEL | F99h    | TRISH <sup>(2)</sup> | F79h    | T3CON                  | F59h    | _       |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                 | FB8h    | CCPR2H   | F98h    | TRISG                | F78h    | TMR4                   | F58h    | —       |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                  | FB7h    | CCPR2L   | F97h    | TRISF                | F77h    | PR4 <sup>(3)</sup>     | F57h    | —       |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                  | FB6h    | CCP2CON  | F96h    | TRISE                | F76h    | T4CON                  | F56h    | —       |

| FF5h    | TABLAT                  | FD5h    | T0CON                  | FB5h    | ECCP3AS  | F95h    | TRISD                | F75h    | CCPR4H                 | F55h    | —       |

| FF4h    | PRODH                   | FD4h    | _                      | FB4h    | ECCP3DEL | F94h    | TRISC                | F74h    | CCPR4L                 | F54h    | _       |

| FF3h    | PRODL                   | FD3h    | OSCCON <sup>(3)</sup>  | FB3h    | CCPR3H   | F93h    | TRISB                | F73h    | CCP4CON                | F53h    | —       |

| FF2h    | INTCON                  | FD2h    | CM1CON                 | FB2h    | CCPR3L   | F92h    | TRISA                | F72h    | CCPR5H                 | F52h    | —       |

| FF1h    | INTCON2                 | FD1h    | CM2CON                 | FB1h    | CCP3CON  | F91h    | LATJ <sup>(2)</sup>  | F71h    | CCPR5L                 | F51h    | —       |

| FF0h    | INTCON3                 | FD0h    | RCON                   | FB0h    | SPBRG1   | F90h    | LATH <sup>(2)</sup>  | F70h    | CCP5CON                | F50h    | —       |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H <sup>(3)</sup>   | FAFh    | RCREG1   | F8Fh    | LATG                 | F6Fh    | SSP2BUF                | F4Fh    | —       |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L <sup>(3)</sup>   | FAEh    | TXREG1   | F8Eh    | LATF                 | F6Eh    | SSP2ADD                | F4Eh    | —       |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON <sup>(3)</sup>   | FADh    | TXSTA1   | F8Dh    | LATE                 | F6Dh    | SSP2STAT               | F4Dh    | —       |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2 <sup>(3)</sup>    | FACh    | RCSTA1   | F8Ch    | LATD                 | F6Ch    | SSP2CON1               | F4Ch    | —       |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2 <sup>(3)</sup>     | FABh    | SPBRG2   | F8Bh    | LATC                 | F6Bh    | SSP2CON2               | F4Bh    | —       |

| FEAh    | FSR0H                   | FCAh    | T2CON                  | FAAh    | RCREG2   | F8Ah    | LATB                 | F6Ah    | CMSTAT                 | F4Ah    | —       |

| FE9h    | FSR0L                   | FC9h    | SSP1BUF                | FA9h    | TXREG2   | F89h    | LATA                 | F69h    | PMADDRH <sup>(4)</sup> | F49h    | —       |

| FE8h    | WREG                    | FC8h    | SSP1ADD                | FA8h    | TXSTA2   | F88h    | PORTJ <sup>(2)</sup> | F68h    | PMADDRL <sup>(4)</sup> | F48h    | —       |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSP1STAT               | FA7h    | EECON2   | F87h    | Porth <sup>(2)</sup> | F67h    | PMDIN1H                | F47h    | _       |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSP1CON1               | FA6h    | EECON1   | F86h    | PORTG                | F66h    | PMDIN1L                | F46h    | —       |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSP1CON2               | FA5h    | IPR3     | F85h    | PORTF                | F65h    | PMCONH                 | F45h    | —       |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                 | FA4h    | PIR3     | F84h    | PORTE                | F64h    | PMCONL                 | F44h    | —       |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                 | FA3h    | PIE3     | F83h    | PORTD                | F63h    | PMMODEH                | F43h    | —       |

| FE2h    | FSR1H                   | FC2h    | ADCON0 <sup>(3)</sup>  | FA2h    | IPR2     | F82h    | PORTC                | F62h    | PMMODEL                | F42h    | _       |

| FE1h    | FSR1L                   | FC1h    | ADCON1 <sup>(3)</sup>  | FA1h    | PIR2     | F81h    | PORTB                | F61h    | PMDOUT2H               | F41h    | _       |

| FE0h    | BSR                     | FC0h    | WDTCON                 | FA0h    | PIE2     | F80h    | PORTA                | F60h    | PMDOUT2L               | F40h    | _       |

Note 1: This is not a physical register.

2: This register is not available on 64-pin devices.

3: This register shares the same address with another register (see Table 6-4 for alternate register).

4: The PMADDRH/L and PMDOUT1H/L register pairs share the same address. PMADDR is used in Master modes and PMDOUT1 is used in Slave modes.

5: Addresses, F40 to F59, are not implemented and are not accessible to the user.

## REGISTER 6-3: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| R/W-0          | R-x                                                                                                           | U-0              | R/W-0 | U-0               | U-0              | U-0             | U-0    |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|------------------|-----------------|--------|--|--|--|

| REGSLP         | LVDSTAT                                                                                                       | —                | ADSHR | —                 | —                | —               | SWDTEN |  |  |  |

| bit 7          |                                                                                                               |                  |       |                   |                  |                 | bit 0  |  |  |  |

|                |                                                                                                               |                  |       |                   |                  |                 |        |  |  |  |

| Legend:        |                                                                                                               |                  |       |                   |                  |                 |        |  |  |  |

| R = Readable   | bit                                                                                                           | W = Writable b   | oit   | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |

| -n = Value at  | POR                                                                                                           | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |  |  |  |

| bit 7<br>bit 6 | For details of bit operation, see Register 25-9.                                                              |                  |       |                   |                  |                 |        |  |  |  |

| bit 5          | Unimplemen                                                                                                    | ted: Read as '0  | 3     |                   |                  |                 |        |  |  |  |

| bit 4          | ADSHR: Shared Address SFR Select bit<br>1 = Alternate SFR is selected<br>0 = Default (Legacy) SFR is selected |                  |       |                   |                  |                 |        |  |  |  |

| bit 3-1        | Unimplemen                                                                                                    | ted: Read as '0  | ,     |                   |                  |                 |        |  |  |  |

| bit 0          | SWDTEN: Software Controlled Watchdog Timer Enable bit<br>For details of bit operation, see Register 25-9.     |                  |       |                   |                  |                 |        |  |  |  |

## 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 64 bytes at a time or two bytes at a time. Program memory is erased in blocks of 1024 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

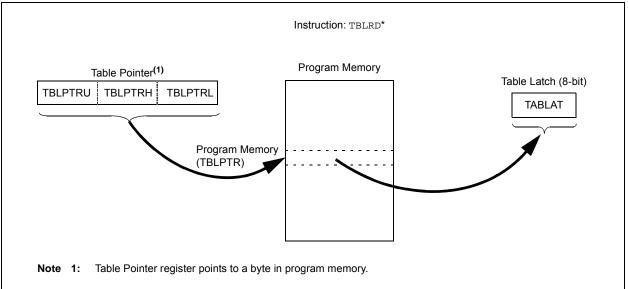

## 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "Writing **to Flash Program Memory**". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1: TABLE READ OPERATION

## 7.4 Erasing Flash Program Memory

The minimum erase block is 512 words or 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 12 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write H'55' to EECON2.

- 5. Write H'AA' to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- The CPU will stall for duration of the erase for Tiw (see Parameter D133A).

- 8. Re-enable interrupts.

### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY ROW

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE ADDR LOW | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|

|           |                                           |                                                                          |                                                              |

| ERASE_ROW | MOVWF                                     | TBLPTRL                                                                  |                                                              |

|           | BSF                                       | EECON1, WREN                                                             | ; enable write to memory                                     |

|           | BSF                                       | EECON1, FREE                                                             | ; enable Row Erase operation                                 |

|           | BCF                                       | INTCON, GIE                                                              | ; disable interrupts                                         |

| Required  | MOVLW                                     | Н'55'                                                                    |                                                              |

| Sequence  | MOVWF                                     | EECON2                                                                   | ; write H'55'                                                |

|           | MOVLW                                     | H'AA'                                                                    |                                                              |

|           | MOVWF                                     | EECON2                                                                   | ; write H'AA'                                                |

|           | BSF                                       | EECON1, WR                                                               | ; start erase (CPU stall)                                    |

|           | BSF                                       | INTCON, GIE                                                              | ; re-enable interrupts                                       |

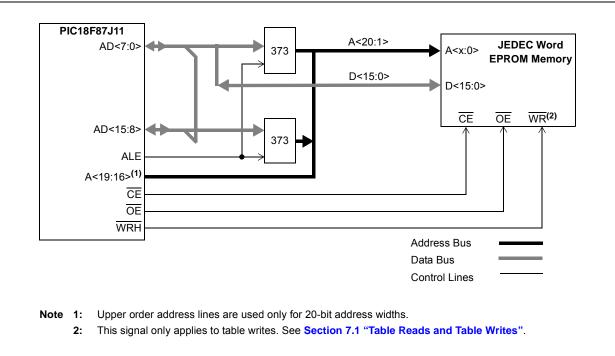

## 8.6.2 16-BIT WORD WRITE MODE

Figure 8-2 shows an example of 16-Bit Word Write mode for PIC18F87J11 family devices. This mode is used for word-wide memories which include some of the EPROM and Flash type memories. This mode allows opcode fetches and table reads from all forms of 16-bit memory and table writes to any type of word-wide external memories. This method makes a distinction between TBLWT cycles to even or odd addresses.

During a TBLWT cycle to an even address (TBLPTR<0> = 0), the TABLAT data is transferred to a holding latch and the external address data bus is tri-stated for the data portion of the bus cycle. No write signals are activated.

During a TBLWT cycle to an odd address (TBLPTR<0> = 1), the TABLAT data is presented on the upper byte of the AD<15:0> bus. The contents of the holding latch are presented on the lower byte of the AD<15:0> bus.

<u>The WRH</u> signal is strobed for each write cycle; the WRL pin is unused. The signal on the BA0 pin indicates the LSb of the TBLPTR, but it is left unconnected. Instead, the UB and LB signals are active to select both bytes. The obvious limitation to this method is that the table write must be done in pairs on a specific word boundary to correctly write a word location.

#### FIGURE 8-2: 16-BIT WORD WRITE MODE EXAMPLE

#### 10.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the bit that enables interrupt priorities (IPEN).

## REGISTER 10-13: RCON: RESET CONTROL REGISTER

| R/W-0 | U-0 | R/W-1 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-----|-------|-------|

| IPEN  | —   | CM    | RI    |     |     | POR   | BOR   |

| bit 7 |     |       |       |     |     |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 7 | IPEN: Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                  |

| bit 5 | CM: Configuration Mismatch Flag bit                                                                                                                         |

|       | For details of bit operation, see Register 5-1.                                                                                                             |

| bit 4 | RI: RESET Instruction Flag bit                                                                                                                              |

|       | For details of bit operation, see Register 5-1.                                                                                                             |

| bit 3 | TO: Watchdog Timer Time-out Flag bit                                                                                                                        |

|       | For details of bit operation, see Register 5-1.                                                                                                             |

| bit 2 | PD: Power-Down Detection Flag bit                                                                                                                           |

|       | For details of bit operation, see Register 5-1.                                                                                                             |

| bit 1 | POR: Power-on Reset Status bit                                                                                                                              |

|       | For details of bit operation, see Register 5-1.                                                                                                             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                                                                             |

|       | For details of bit operation, see Register 5-1.                                                                                                             |

| Pin Name | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                     |

|----------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------|

| RJ0/ALE  | RJ0      | 0               | 0   | DIG         | LATJ<0> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<0> data input.                                                                            |

|          | ALE      | x               | 0   | DIG         | External Memory Interface address latch enable control output; takes priority over digital I/O. |

| RJ1/OE   | RJ1      | 0               | 0   | DIG         | LATJ<1> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<1> data input.                                                                            |

|          | ŌE       | х               | 0   | DIG         | External Memory Interface output enable control output; takes priority over digital I/O.        |

| RJ2/WRL  | RJ2      | 0               | 0   | DIG         | LATJ<2> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<2> data input.                                                                            |

|          | WRL      | х               | 0   | DIG         | External Memory Bus write low byte control; takes priority over digital I/O.                    |

| RJ3/WRH  | RJ3      | 0               | 0   | DIG         | LATJ<3> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<3> data input.                                                                            |

|          | WRH      | х               | 0   | DIG         | External Memory Interface write high byte control output; takes priority over digital I/O.      |

| RJ4/BA0  | RJ4      | 0               | 0   | DIG         | LATJ<4> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<4> data input.                                                                            |

|          | BA0      | х               | 0   | DIG         | External Memory Interface Byte Address 0 control output; takes priority over digital I/O.       |

| RJ5/CE   | RJ5      | 0               | 0   | DIG         | LATJ<5> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<5> data input.                                                                            |

|          | CE       | x               | 0   | DIG         | External Memory Interface chip enable control output; takes priority over digital I/O.          |

| RJ6/LB   | RJ6      | 0               | 0   | DIG         | LATJ<6> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<6> data input.                                                                            |

|          | LB       | x               | 0   | DIG         | External Memory Interface lower byte enable control output; takes priority over digital I/O.    |

| RJ7/UB   | RJ7      | 0               | 0   | DIG         | LATJ<7> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<7> data input.                                                                            |

|          | UB       | х               | 0   | DIG         | External Memory Interface upper byte enable control output; takes priority over digital I/O.    |

TABLE 11-20: PORTJ FUNCTIONS

Legend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 11-21. | SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ |

|--------------|--------------------------------------------|

| IADLE II-ZI. | SUMMART OF REGISTERS ASSOCIATED WITH FORTS |

| Name                 | Bit 7  | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------|--------|--------|---------------------|--------|--------|--------|--------|--------|-----------------------------|

| PORTJ <sup>(1)</sup> | RJ7    | RJ6    | RJ5                 | RJ4    | RJ3    | RJ2    | RJ1    | RJ0    | 65                          |

| LATJ <sup>(1)</sup>  | LATJ7  | LATJ6  | LATJ5               | LATJ4  | LATJ3  | LATJ2  | LATJ1  | LATJ0  | 64                          |

| TRISJ <sup>(1)</sup> | TRISJ7 | TRISJ6 | TRISJ5              | TRISJ4 | TRISJ3 | TRISJ2 | TRISJ1 | TRISJ0 | 64                          |

| PORTG                | RDPU   | REPU   | RJPU <sup>(1)</sup> | RG4    | RG3    | RG2    | RG1    | RG0    | 65                          |

**Legend:** Shaded cells are not used by PORTJ.

Note 1: Unimplemented on 64-pin devices, read as '0'.

NOTES:

#### REGISTER 12-6: PMEL: PARALLEL PORT ENABLE LOW BYTE REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PTEN7 | PTEN6 | PTEN5 | PTEN4 | PTEN3 | PTEN2 | PTEN1 | PTEN0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-2 | PTEN<7:2>: PMP Address Port Enable bits                          |

|---------|------------------------------------------------------------------|

|         | 1 = PMA<7:2> function as PMP address lines                       |

|         | 0 = PMA<7:2> function as port I/O                                |

| bit 1-0 | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                        |

|         | 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL |

|         | 0 = PMA1 and PMA0 pads function as port I/O                      |

### REGISTER 12-7: PMSTATH: PARALLEL PORT STATUS HIGH BYTE REGISTER

| R-0     | R/W-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|---------|-------|-----|-----|------|------|------|-------|

| IBF     | IBOV  |     | _   | IB3F | IB2F | IB1F | IB0F  |

| bit 7   |       |     |     |      |      |      | bit 0 |

|         |       |     |     |      |      |      |       |

| Legend: |       |     |     |      |      |      |       |

| Legena:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | IBF: Input Buffer Full Status bit                                                                                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = All writable input buffer registers are full                                                                                                                          |

|         | 0 = Some or all of the writable input buffer registers are empty                                                                                                          |

| bit 6   | IBOV: Input Buffer Overflow Status bit                                                                                                                                    |

|         | <ul> <li>1 = A write attempt to a full input byte register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul>                            |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                |

| bit 3-0 | IB3F:IB0F: Input Buffer Status Full bits                                                                                                                                  |

|         | <ul> <li>1 = Input buffer contains data that has not been read (reading buffer will clear this bit)</li> <li>0 = Input buffer does not contain any unread data</li> </ul> |

NOTES:

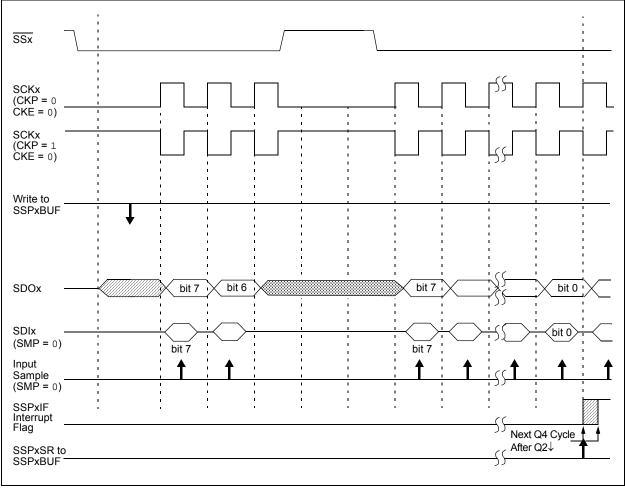

## 20.3.7 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

#### 20.3.8 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 04h). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a

transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode, with                     |

|---------|---------------------------------------------------------|

|         | the SSx pin control enabled,                            |

|         | (SSPxCON1<3:0> = 0100), the SPI                         |

|         | module will reset if the $\overline{SSx}$ pin is set to |

|         | Vdd.                                                    |

|         |                                                         |

2: If the SPI is used in Slave mode, with CKE set, then the SSx pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDOx pin can be connected to the SDIx pin. When the SPI needs to operate as a receiver, the SDOx pin can be configured as an input; this disables transmissions from the SDOx. The SDIx can always be left as an input (SDI function) since it cannot create a bus conflict.

## 20.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 20.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 20.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPxSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

#### 20.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

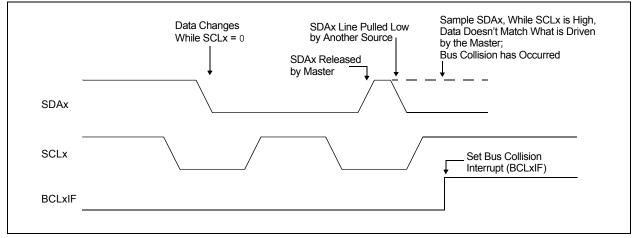

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high, and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF, and reset the  $I^2C$  port to its Idle state (Figure 20-27).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the I<sup>2</sup>C bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

### FIGURE 20-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

| CLRF                                                | Clear f                                                               |                                         |                                    | CLR        | WDT                         | Clear Wate                            | hdog Timer      |                                        |

|-----------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------|------------------------------------|------------|-----------------------------|---------------------------------------|-----------------|----------------------------------------|

| Syntax:                                             | CLRF f{,;                                                             | a}                                      |                                    | Synt       | ax:                         | CLRWDT                                |                 |                                        |

| Operands:                                           | $0 \leq f \leq 255$                                                   |                                         |                                    | Ope        | rands:                      | None                                  |                 |                                        |

|                                                     | a ∈ [0,1]                                                             |                                         |                                    | Ope        | ration:                     | $000h \rightarrow Wl$                 | ЭT,             |                                        |

| Operation:                                          | $\begin{array}{l} 000h \rightarrow f, \\ 1 \rightarrow Z \end{array}$ |                                         |                                    |            |                             | $1 \rightarrow \overline{\text{TO}},$ | OT postscaler,  |                                        |

| Status Affected:                                    | Z                                                                     |                                         |                                    |            |                             | $1 \rightarrow PD$                    |                 |                                        |

| Encoding:                                           | 0110                                                                  | 101a ff:                                | ff ffff                            |            | us Affected:                | TO, PD                                |                 |                                        |

| Description:                                        | Clears the oregister.                                                 | contents of the                         | especified                         |            | oding:<br>cription:         | 0000<br>CLRWDT ins                    | 0000 00         |                                        |

|                                                     | ,                                                                     |                                         | nk is selected.<br>d to select the |            |                             | 0                                     | e WDT. Status   | esets <u>the</u> post-<br>bits, TO and |

|                                                     | lf 'a' is '0' a                                                       | nd the extend                           | ed instruction                     | Wor        | ds:                         | 1                                     |                 |                                        |

|                                                     |                                                                       |                                         | ction operates                     | Cycl       | es:                         | 1                                     |                 |                                        |

|                                                     |                                                                       | Literal Offset A                        |                                    | QC         | cycle Activity:             |                                       |                 |                                        |

|                                                     |                                                                       | ever f ≤ 95 (5<br>. <b>2.3 "Byte-Or</b> | ,                                  |            | Q1                          | Q2                                    | Q3              | Q4                                     |

|                                                     | Bit-Oriente                                                           | ed Instruction<br>set Mode" for         | s in Indexed                       |            | Decode                      | No<br>operation                       | Process<br>Data | No<br>operation                        |

| Words:                                              | 1                                                                     |                                         |                                    |            |                             |                                       |                 |                                        |

| Cycles:                                             | 1                                                                     |                                         |                                    | <u>Exa</u> | <u>mple:</u>                | CLRWDT                                |                 |                                        |

| Q Cycle Activity:                                   |                                                                       |                                         |                                    |            | Before Instruc              |                                       |                 |                                        |

| Q1                                                  | Q2                                                                    | Q3                                      | Q4                                 |            | WDT Co<br>After Instruction |                                       | ?               |                                        |

| Decode                                              | Read<br>register 'f'                                                  | Process<br>Data                         | Write<br>register 'f'              |            | WDT Co<br><u>WD</u> T Po    | unter =<br>stscaler =                 | 00h<br>0        |                                        |

| Example:                                            | CLRF                                                                  | FLAG_REG,                               | 1                                  |            | TO<br>PD                    | =                                     | 1<br>1          |                                        |

| Before Instru<br>FLAG_I<br>After Instruct<br>FLAG_I | REG = 5A                                                              |                                         |                                    |            |                             |                                       |                 |                                        |

| DAW               | Decimal Ac            | djust W Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | er         | DECF                  | Decremen                 | tf                                   |                              |

|-------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|--------------------------|--------------------------------------|------------------------------|

| Syntax:           | DAW                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | Syntax:               | DECF f{,                 | d {,a}}                              |                              |

| Operands:         | None                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | Operands:             | $0 \leq f \leq 255$      |                                      |                              |

| Operation:        | lf [W<3:0> >          | > 9] or [DC = 1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | then,      |                       | $d \in [0,1]$            |                                      |                              |

|                   | · · ·                 | $6 \rightarrow W < 3:0>;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | Onenting              | a ∈ [0,1]                | 1                                    |                              |

|                   | else,<br>(W<3:0>) →   | → W<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | Operation:            | $(f) - 1 \rightarrow de$ |                                      |                              |

|                   | ,                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | Status Affected:      | C, DC, N, (              |                                      |                              |

|                   | •                     | > 9] or [C = 1] the formatte of the format | hen,       | Encoding:             | 0000                     |                                      | ff ffff                      |

|                   | (VV < 7.4 >) + C = 1; | $0 \rightarrow VV < 7.4^{\circ},$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | Description:          |                          | register 'f'. If<br>ored in W. If 'c |                              |

|                   | else,                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                       |                          | ored back in r                       | ,                            |

|                   | (W<7:4>) →            | → W<7:4>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                       | lf 'a' is '0', t         | he Access Ba                         | ank is selected.             |