Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 3930 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67j11t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then clear the SCSx bits and execute SLEEP. When the clock source is switched to the INTOSC block, the primary oscillator is shut down and the OSTS bit is cleared.

When a wake event occurs, the peripherals continue to be clocked from the internal oscillator block. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTRC. The IDLEN and SCSx bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

## 4.5 Exiting Idle and Sleep Modes

An exit from Sleep mode, or any of the Idle modes, is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes sections (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

### 4.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode, or the Sleep mode, to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 10.0 "Interrupts").

A fixed delay of interval, TCSD, following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 4.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 25.2 "Watchdog Timer (WDT)").

The Watchdog Timer and postscaler are cleared by one of the following events:

- Executing a SLEEP or CLRWDT instruction

- The loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled)

## 4.5.3 EXIT BY RESET

Exiting an Idle or Sleep mode by Reset automatically forces the device to run from the INTRC.

#### 4.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped

- The primary clock source is either the EC or ECPLL mode

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (EC). However, a fixed delay of interval, TCSD, following the wake event, is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

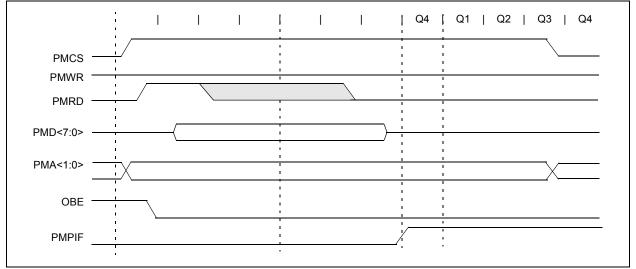

#### 12.2.3.1 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCS = 1 and PMRD = 1), the data from one of the four output bytes is presented onto PMD<7:0>. Which byte is read depends on the 2-bit address placed on ADDR<1:0>. Table 12-2 shows the corresponding output registers and their associated address.

When an output buffer is read, the corresponding OBxE bit is set. The OBE flag bit is set when all the buffers are empty. If any buffer is already empty (OBxE = 1), the next read to that buffer will generate an OBUF event.

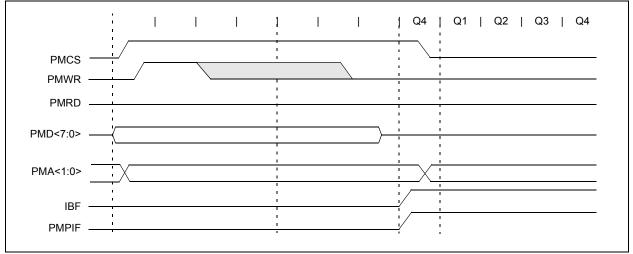

#### 12.2.3.2 WRITE TO SLAVE PORT

When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into one of the four input buffer bytes. Which byte is written depends on the 2-bit address placed on ADDRL<1:0>. Table 12-2 shows the corresponding input registers and their associated address.

When an input buffer is written, the corresponding IBxF bit is set. The IBF flag bit is set when all the buffers are written. If any buffer is already written (IBxF = 1), the next write strobe to that buffer will generate an OBUF event and the byte will be discarded.

### FIGURE 12-8: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### 12.3.11 MASTER MODE TIMING

This section contains a number of timing examples that represent the common Master mode configuration options. These options vary from 8-bit to 16-bit data, fully demultiplexed to fully multiplexed address, as well as Wait states.

#### FIGURE 12-12: READ AND WRITE TIMING, 8-BIT DATA, DEMULTIPLEXED ADDRESS

| Q1 Q2             | 2 03 04 01 02 03 04 01 02 03 04 | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 | Q3 Q4 Q1 Q2 Q3 Q4 |

|-------------------|---------------------------------|-------------------------------|-------------------|

| PMCS2             |                                 |                               |                   |

| PMCS1<br>PMD<7:0> | ; ; <u>}</u>                    |                               |                   |

| PMA<13:0>         |                                 |                               |                   |

| PMWR<br>PMRD      |                                 |                               |                   |

| PMPIF             |                                 |                               |                   |

| BUSY              |                                 |                               |                   |

## FIGURE 12-13: READ TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS

|           | Q1 Q2 Q3 Q4 | Q1 Q2                        | Q3 Q4   | Q1         | Q2          | Q3          | Q4  | Q1 Q2 Q3 Q4                           | Q1   Q2   Q3   Q4   Q1   Q2   Q3   Q4 |

|-----------|-------------|------------------------------|---------|------------|-------------|-------------|-----|---------------------------------------|---------------------------------------|

| PMCS2     |             |                              | 1       | i          | 1           | 1           |     |                                       |                                       |

| PMCS1     |             |                              | <br>    |            | 1<br>1<br>1 | 1<br>1<br>1 |     | · · · · · · · · · · · · · · · · · · · |                                       |

| PMD<7:0>  |             | Addres                       | ss<7:0> | <u>)</u> — | 1<br>1<br>1 | ( D         | ata | <u></u>                               |                                       |

| PMA<13:8> |             | <br>1 .<br>1 .               | 1       | i          | 1           | i           |     |                                       |                                       |

| PMWR      |             | 1 1<br>1 1                   |         | -          | 1<br>1      | 1           |     |                                       |                                       |

| PMRD      |             |                              |         |            |             | I<br>I      |     | <u> </u>                              |                                       |

| PMALL     |             | <u> </u>                     |         | 1          | 1           | 1           |     |                                       |                                       |

| PMPIF     |             | 1 1<br>1 1<br><del>1 1</del> |         |            | 1<br>1<br>1 |             |     |                                       |                                       |

| BUSY      |             |                              | +       | <u>'</u>   | 1           | 1           | l   |                                       |                                       |

## 16.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- · Module Reset on ECCPx Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 16-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 16-2.

The Timer3 module is controlled through the T3CON register (Register 16-1). It also selects the clock source options for the CCP and ECCP modules; see Section 18.1.1 "CCP Modules and Timer Resources" for more information.

## REGISTER 16-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| I a superior of the |                                    |                                                                                                                                                                                                   |                                                                                                         |                                     |

|---------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------|

| Legend:             |                                    |                                                                                                                                                                                                   |                                                                                                         | (O)                                 |

| R = Readat          |                                    | W = Writable bit                                                                                                                                                                                  | U = Unimplemented bit                                                                                   |                                     |

| -n = Value a        | at POR                             | '1' = Bit is set                                                                                                                                                                                  | '0' = Bit is cleared                                                                                    | x = Bit is unknown                  |

|                     |                                    |                                                                                                                                                                                                   |                                                                                                         |                                     |

| bit 7               | -                                  | 6-Bit Read/Write Mode Enable                                                                                                                                                                      |                                                                                                         |                                     |

|                     |                                    | les register read/write of Time<br>les register read/write of Time                                                                                                                                | •                                                                                                       |                                     |

| bit 6,3             | T3CCP<                             | 2:1>: Timer3 and Timer1 to E                                                                                                                                                                      | CCPx/CCPx Enable bits                                                                                   |                                     |

|                     | 10 = Tim<br>Tim<br>01 = Tim<br>Tim | er3 and Timer4 are the clock<br>ler3 and Timer4 are the clock<br>ler1 and Timer2 are the clock<br>ler3 and Timer4 are the clock<br>ler1 and Timer2 are the clock<br>ler1 and Timer2 are the clock | sources for ECCP3, CCP4 a<br>sources for ECCP1 and ECC<br>sources for ECCP2, ECCP3<br>sources for ECCP1 | nd CCP5;<br>CP2<br>, CCP4 and CCP5; |

| bit 5-4             | <b>T3CKPS</b>                      | <1:0>: Timer3 Input Clock Pre                                                                                                                                                                     | escale Select bits                                                                                      |                                     |

|                     | 10 = 1:4<br>01 = 1:2               | Prescale value<br>Prescale value<br>Prescale value<br>Prescale value                                                                                                                              |                                                                                                         |                                     |

| bit 2               | (Not usal                          | : Timer3 External Clock Input<br>ole if the device clock comes f<br>/IR3CS = 1:                                                                                                                   | -                                                                                                       |                                     |

|                     | 1 = Does<br>0 = Sync               | not synchronize external cloc<br>hronizes external clock input                                                                                                                                    | ck input                                                                                                |                                     |

|                     |                                    | <u>IR3CS = 0:</u><br>s ignored. Timer3 uses the inte                                                                                                                                              | ernal clock when TMR3CS =                                                                               | 0.                                  |

| bit 1               | TMR3CS                             | : Timer3 Clock Source Select                                                                                                                                                                      | t bit                                                                                                   |                                     |

|                     |                                    | rnal clock input from Timer1 c<br>g edge)                                                                                                                                                         | oscillator or T13CKI (on the ri                                                                         | sing edge after the first           |

|                     | 0 = Inter                          | nal clock (Fosc/4)                                                                                                                                                                                |                                                                                                         |                                     |

| bit 0               | TMR3ON                             | I: Timer3 On bit                                                                                                                                                                                  |                                                                                                         |                                     |

|                     | 1 = Enab<br>0 = Stops              | les Timer3<br>s Timer3                                                                                                                                                                            |                                                                                                         |                                     |

| ECCP Mode      | CCP2CON<br>Configuration                        | RB3           | RC1          | RE7          | RE2            | RE1    | RE0    |  |  |  |

|----------------|-------------------------------------------------|---------------|--------------|--------------|----------------|--------|--------|--|--|--|

|                | All Devices, CCP2MX = 1, Either Operating mode: |               |              |              |                |        |        |  |  |  |

| Compatible CCP | 00xx 11xx                                       | RB3/INT3      | ECCP2        | RE7          | RE2            | RE1    | RE0    |  |  |  |

| Dual PWM       | 10xx 11xx                                       | RB3/INT3      | P2A          | RE7          | P2B            | RE1    | RE0    |  |  |  |

| Quad PWM       | x1xx 11xx                                       | RB3/INT3      | P2A          | RE7          | P2B            | P2C    | P2D    |  |  |  |

|                | All Devices, CCP2MX = 0, Microcontroller mode:  |               |              |              |                |        |        |  |  |  |

| Compatible CCP | 00xx 11xx                                       | RB3/INT3      | RC1/T1OS1    | ECCP2        | RE2            | RE1    | RE0    |  |  |  |

| Dual PWM       | 10xx 11xx                                       | RB3/INT3      | RC1/T1OS1    | P2A          | P2B            | RE1    | RE0    |  |  |  |

| Quad PWM       | x1xx 11xx                                       | RB3/INT3      | RC1/T10S1    | P2A          | P2B            | P2C    | P2D    |  |  |  |

|                | PIC18F8XJ1                                      | IX Devices, C | CP2MX = 0, E | Extended Mic | rocontroller r | node:  |        |  |  |  |

| Compatible CCP | 00xx 11xx                                       | ECCP2         | RC1/T1OS1    | RE7/AD15     | RE2/CS         | RE1/WR | RE0/RD |  |  |  |

| Dual PWM       | 10xx 11xx                                       | P2A           | RC1/T1OS1    | RE7/AD15     | P2B            | RE1/WR | RE0/RD |  |  |  |

| Quad PWM       | x1xx 11xx                                       | P2A           | RC1/T1OS1    | RE7/AD15     | P2B            | P2C    | P2D    |  |  |  |

## TABLE 19-2: PIN CONFIGURATIONS FOR ECCP2

Legend: x = Don't care. Shaded cells indicate pin assignments not used by ECCP2 in a given mode.

### TABLE 19-3: PIN CONFIGURATIONS FOR ECCP3

| CCP3CON<br>Configuration                               | RG0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RE4                                                                                                                                                                                                                                                | RE3                                                                                                                                                                                                                                                                                                                                                                         | RG3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RH5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RH4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC18F6XJ1X Devices:                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 00xx 11xx                                              | ECCP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RE4                                                                                                                                                                                                                                                | RE3                                                                                                                                                                                                                                                                                                                                                                         | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 10xx 11xx                                              | P3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P3B                                                                                                                                                                                                                                                | RE3                                                                                                                                                                                                                                                                                                                                                                         | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| x1xx 11xx                                              | P3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P3B                                                                                                                                                                                                                                                | P3C                                                                                                                                                                                                                                                                                                                                                                         | P3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PIC18F8XJ1X Devices, ECCPMX = 0, Microcontroller mode: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 00xx 11xx                                              | ECCP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RE6/AD14                                                                                                                                                                                                                                           | RE5/AD13                                                                                                                                                                                                                                                                                                                                                                    | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RH7/AN15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RH6/AN14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 10xx 11xx                                              | P3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RE6/AD14                                                                                                                                                                                                                                           | RE5/AD13                                                                                                                                                                                                                                                                                                                                                                    | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P3B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RH6/AN14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| x1xx 11xx                                              | P3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RE6/AD14                                                                                                                                                                                                                                           | RE5/AD13                                                                                                                                                                                                                                                                                                                                                                    | P3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P3B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P3C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| X Devices, ECC                                         | PMX = 1, Ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ended Micro                                                                                                                                                                                                                                        | controller mo                                                                                                                                                                                                                                                                                                                                                               | de, 16-Bit or 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20-Bit Addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | s Width:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 00xx 11xx                                              | ECCP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RE6/AD14                                                                                                                                                                                                                                           | RE5/AD13                                                                                                                                                                                                                                                                                                                                                                    | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RH7/AN15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RH6/AN14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| licrocontroller r                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                             | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ess Width:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 00xx 11xx                                              | ECCP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RE4/AD12                                                                                                                                                                                                                                           | RE3/AD11                                                                                                                                                                                                                                                                                                                                                                    | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RH5/AN13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RH4/AN12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 10xx 11xx                                              | P3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P3B                                                                                                                                                                                                                                                | RE3/AD11                                                                                                                                                                                                                                                                                                                                                                    | RG3/CCP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RH5/AN13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RH4/AN12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| x1xx 11xx                                              | P3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P3B                                                                                                                                                                                                                                                | P3C                                                                                                                                                                                                                                                                                                                                                                         | P3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RH5/AN13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RH4/AN12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                        | CCP3CON           Configuration           00xx         11xx           10xx         11xx           10xx         11xx           x1xx         11xx           00xx         11xx           00xx         11xx           10xx         11xx           00xx         11xx           10xx         11xx           00xx         11xx           X         Devices, ECC           00xx         11xx           licrocontroller         0           00xx         11xx           10xx         11xx | CCP3CON<br>ConfigurationRG000xx11xxECCP310xx11xxP3Ax1xx11xxP3Ax1xx11xxP3APIC18F8XJ1X Device00xx11xxECCP310xx11xxP3Ax1xx11xxP3Ax1xx11xxP3Ax1xx11xxECCP300xx11xxECCP3PIC18F8Icrocontroller worde or Externation00xx11xxECCP300xx11xxECCP310xx11xxP3A | CCP3CON<br>ConfigurationRG0RE4ConfigurationRG0RE400xx11xxECCP3RE410xx11xxP3AP3Bx1xx11xxP3AP3Bv1xx11xxP3AP3BPIC18F8XJ1X Devices, ECCPMX00xx11xxECCP3RE6/AD1410xx11xxP3ARE6/AD14x1xx11xxP3ARE6/AD14x1xx11xxP3ARE6/AD14VDEvices, ECCPMX = 1, Extended Microor00xx11xxECCP3RE6/AD14VDC18F8XJ1X DeviceIcrocontroller mode or Extended Microor00xx11xxECCP3RE4/AD1210xx11xxP3AP3B | CCP3CON<br>ConfigurationRG0RE4RE3PIC18F6XJ1X Devices:00xx 11xxECCP3RE4RE310xx 11xxP3AP3BRE3x1xx 11xxP3AP3BP3CPIC18F8XJ1X Devices, ECCPMX = 0, Microcol00xx 11xxECCP3RE6/AD14RE5/AD1310xx 11xxP3ARE6/AD14RE5/AD1310xx 11xxP3ARE6/AD14RE5/AD1310xx 11xxP3ARE6/AD14RE5/AD13x1xx 11xxP3ARE6/AD14RE5/AD13X Devices, ECCPMX = 1, Extended Microcontroller mod00xx 11xxECCP300xx 11xxECCP3RE6/AD14RE5/AD13PIC18F8XJ1X Devices, ECCPMX =Icrocontroller mode or Extended Microcontroller mod00xx 11xxECCP3RE4/AD1200xx 11xxP3AP3BRE3/AD1110xx 11xxP3A | CCP3CON<br>ConfigurationRG0RE4RE3RG3PIC18F6XJ1X Devices:00xx 11xxECCP3RE4RE3RG3/CCP410xx 11xxP3AP3BRE3RG3/CCP410xx 11xxP3AP3BP3CP3DPIC18F8XJ1X Devices, ECCPMX = 0, Microcontroller mode00xx 11xxECCP3RE6/AD14RE5/AD13RG3/CCP410xx 11xxP3ARE6/AD14RE5/AD13RG3/CCP410xx 11xxP3ARE6/AD14RE5/AD13P3DX Devices, ECCPMX = 1, Extended Microcontroller mode, 16-Bit or 200xx 11xxECCP3RE6/AD14RE5/AD13RG3/CCP4IIcrocontroller mode or Extended Microcontroller mode, 12-Bit Addr00xx 11xxECCP3RE4/AD12RE3/AD11RG3/CCP400xx 11xxP3AP3BRE3/AD11RG3/CCP4 | CCP3CON<br>ConfigurationRG0RE4RE3RG3RH5PIC18F6XJ1X Devices:00xx 11xxECCP3RE4RE3RG3/CCP4N/A10xx 11xxP3AP3BRE3RG3/CCP4N/Ax1xx 11xxP3AP3BP3CP3DN/APIC18F8XJ1X Devices, ECCPMX = 0, Microcontroller mode:00xx 11xxECCP3RE6/AD14RE5/AD13RG3/CCP4RH7/AN1510xx 11xxP3ARE6/AD14RE5/AD13RG3/CCP4P3Bx1xx 11xxP3ARE6/AD14RE5/AD13P3DP3BX1xx 11xxP3ARE6/AD14RE5/AD13P3DP3BX Devices, ECCPMX = 1, Extended Microcontroller mode, 16-Bit or 20-Bit Address00xx 11xxECCP3RE6/AD14RE5/AD13RG3/CCP4RH7/AN15Incrocontroller mode or Extended Microcontroller mode, 12-Bit Address Width:00xx 11xxECCP3RE4/AD12RE3/AD11RG3/CCP4RH5/AN1310xx 11xxP3AP3BRE3/AD11RG3/CCP4RH5/AN1310xx 11xxP3AP3BRE3/AD11RG3/CCP4RH5/AN13 |  |  |  |

**Legend:** x = Don't care, N/A = Not Available. Shaded cells indicate pin assignments not used by ECCP3 in a given mode.

**Note 1:** With ECCP3 in Quad PWM mode, the CCP4 module's output is overridden by P1D; otherwise, CCP4 is fully operational.

| R/W-0        | R/W-0                             | R/W-0                               | R/W-0                | R/W-0                       | R/W-0              | R/W-0               | R/W-0              |

|--------------|-----------------------------------|-------------------------------------|----------------------|-----------------------------|--------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                           | ACKDT <sup>(1)</sup>                | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7        | -                                 |                                     | 1                    |                             | 1                  | 11                  | bit                |

|              |                                   |                                     |                      |                             |                    |                     |                    |

| Legend:      |                                   |                                     |                      |                             |                    |                     |                    |

| R = Readab   |                                   | W = Writable                        |                      | U = Unimplem                |                    |                     |                    |

| -n = Value a | It POR                            | '1' = Bit is set                    |                      | '0' = Bit is clea           | ared               | x = Bit is unkn     | own                |

| bit 7        | GCEN: Gene                        | eral Call Enable                    | bit                  |                             |                    |                     |                    |

|              | Unused in Ma                      |                                     |                      |                             |                    |                     |                    |

| bit 6        | ACKSTAT: A                        | cknowledge Sta                      | atus bit (Master     | Transmit mode               | e only)            |                     |                    |

|              |                                   | edge was not re                     |                      |                             |                    |                     |                    |

|              |                                   | edge was receiv                     |                      |                             |                    |                     |                    |

| bit 5        |                                   |                                     | bit (Master Re       | ceive mode onl              | y) <sup>(1)</sup>  |                     |                    |

|              | 1 = Not Ackn                      | Ų                                   |                      |                             |                    |                     |                    |

| L:1 4        | 0 = Acknowle                      | •                                   |                      | :(2)                        |                    |                     |                    |

| bit 4        |                                   | nowledge Sequ                       |                      |                             | oine and trans     | mits ACKDT dat      | a hit:             |

|              |                                   | cally cleared by                    |                      |                             | uns and trans      |                     | a bit,             |

|              |                                   | edge sequence                       |                      |                             |                    |                     |                    |

| bit 3        | RCEN: Rece                        | ive Enable bit (                    | Master Receive       | e mode only) <sup>(2)</sup> |                    |                     |                    |

|              | 1 = Enables I<br>0 = Receive i    | Receive mode f                      | or I <sup>2</sup> C  |                             |                    |                     |                    |

| bit 2        |                                   | ondition Enable                     | bit(2)               |                             |                    |                     |                    |

|              | -                                 |                                     |                      | and SCI x pins:             | automatically      | cleared by hard     | ware               |

|              | 0 = Stop cond                     |                                     | 0.1 0.0 027 0.0      |                             | aatomaticany       |                     |                    |

| bit 1        | RSEN: Repe                        | ated Start Cond                     | lition Enable bi     | t <mark>(2)</mark>          |                    |                     |                    |

|              |                                   | Repeated Start<br>d Start condition |                      | e SDAx and S                | CLx pins; auto     | matically cleared   | d by hardwar       |

| bit 0        | SEN: Start Co                     | ondition Enable                     | bit <sup>(2)</sup>   |                             |                    |                     |                    |

|              | 1 = Initiates S<br>0 = Start cond |                                     | n the SDAx an        | d SCLx pins; a              | utomatically cl    | eared by hardw      | are                |

| Note 1: T    | he value that wil                 | I be transmitted                    | when the user        | initiates an Ack            | knowledge seq      | uence at the end    | d of a receive     |

| 2: 1         | f the I <sup>2</sup> C module     | is active, these                    | bits may not b       | e set (no spool             | ling) and the S    | SPxBUF may n        | ot he writter      |

2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

## 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has 11 inputs for the 64-pin devices and 15 for the 80-pin devices. This module allows conversion of an analog input signal to a corresponding 10-bit digital number.

The module has six registers:

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Port Configuration Register 2 (ANCON0)