Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 68                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3930 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 15x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j11t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

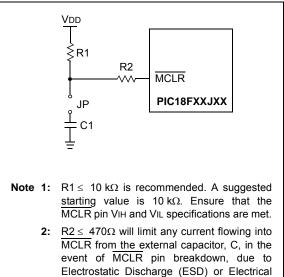

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

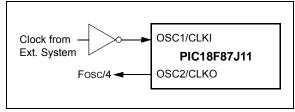

#### 3.4.2 EXTERNAL CLOCK INPUT (EC MODES)

The EC and ECPLL Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency, divided by 4, is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-3 shows the pin connections for the EC Oscillator mode.

#### FIGURE 3-3: EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

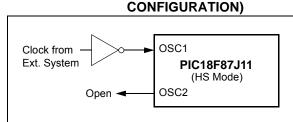

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 3-4. In this configuration, the divide-by-4 output on OSC2 is not available. Current consumption in this configuration will be somewhat higher than EC mode, as the internal oscillator's feedback circuitry will be enabled (in EC mode, the feedback circuit is disabled).

## FIGURE 3-4: EXTERNAL CLOCK INPUT OPERATION (HS OSC

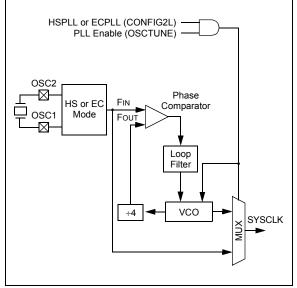

## 3.4.3 PLL FREQUENCY MULTIPLIER

A Phase Locked Loop (PLL) circuit is provided as an option for users who want to use a lower frequency oscillator circuit, or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with the External Memory Interface (EMI) due to high-frequency crystals, or users who require higher clock speeds from an internal oscillator.

## 3.4.3.1 HSPLL and ECPLL Modes

The HSPLL and ECPLL modes provide the ability to selectively run the device at 4 times the external oscillating source to produce frequencies up to 40 MHz.

The PLL is enabled by programming the FOSC<2:0> Configuration bits to either '111' (for ECPLL) or '101' (for HSPLL). In addition, the PLLEN bit (OSCTUNE<6>) must also be set. Clearing PLLEN disables the PLL, regardless of the chosen oscillator configuration. It also allows additional flexibility for controlling the application's clock speed in software.

## 3.4.3.2 PLL and INTOSC

The PLL is also available to the internal oscillator block when the internal oscillator block is configured as the primary clock source. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.5.2 "INTPLL Modes**".

# PIC18F87J11 FAMILY

| TABLE 5-3: | INITIALIZATION CONDITIONS FOR ALL REGISTERS <sup>(4)</sup> (CONTINUED) |                                    |                                                                                |                                 |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|

| Register   | Applicable Devices                                                     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |  |

| IPR3       | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| PIR3       | PIC18F6XJ1X PIC18F8XJ1X                                                | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <b>(3)</b>            |  |  |  |  |  |  |

| PIE3       | PIC18F6XJ1X PIC18F8XJ1X                                                | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| IPR2       | PIC18F6XJ1X PIC18F8XJ1X                                                | 111- 1111                          | 111- 1111                                                                      | uuu- uuuu                       |  |  |  |  |  |  |

| PIR2       | PIC18F6XJ1X PIC18F8XJ1X                                                | 000- 0000                          | 000- 0000                                                                      | uuu- uuuu <b>(<sup>3)</sup></b> |  |  |  |  |  |  |

| PIE2       | PIC18F6XJ1X PIC18F8XJ1X                                                | 000- 0000                          | 000- 0000                                                                      | uuu- uuuu                       |  |  |  |  |  |  |

| IPR1       | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| PIR1       | PIC18F6XJ1X PIC18F8XJ1X                                                | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <b>(<sup>3)</sup></b> |  |  |  |  |  |  |

| PIE1       | PIC18F6XJ1X PIC18F8XJ1X                                                | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| RCSTA2     | PIC18F6XJ1X PIC18F8XJ1X                                                | 0000 000x                          | 0000 000x                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| OSCTUNE    | PIC18F6XJ1X PIC18F8XJ1X                                                | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| TRISJ      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| TRISH      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| TRISG      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1 1111                             | 1 1111                                                                         | u uuuu                          |  |  |  |  |  |  |

| TRISF      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 111-                          | 1111 111-                                                                      | uuuu uuu-                       |  |  |  |  |  |  |

| TRISE      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| TRISD      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| TRISC      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| TRISB      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| TRISA      | PIC18F6XJ1X PIC18F8XJ1X                                                | 1111 1111                          | 1111 1111                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| LATJ       | PIC18F6XJ1X PIC18F8XJ1X                                                | XXXX XXXX                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| LATH       | PIC18F6XJ1X PIC18F8XJ1X                                                | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| LATG       | PIC18F6XJ1X PIC18F8XJ1X                                                | x xxxx                             | u uuuu                                                                         | u uuuu                          |  |  |  |  |  |  |

| LATF       | PIC18F6XJ1X PIC18F8XJ1X                                                | xxxx xxx-                          | uuuu uuu-                                                                      | uuuu uuu-                       |  |  |  |  |  |  |

| LATE       | PIC18F6XJ1X PIC18F8XJ1X                                                | XXXX XXXX                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| LATD       | PIC18F6XJ1X PIC18F8XJ1X                                                | xxxx xxxx                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| LATC       | PIC18F6XJ1X PIC18F8XJ1X                                                | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

| LATB       | PIC18F6XJ1X PIC18F8XJ1X                                                | xxxx xxxx                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |  |

| LATA       | PIC18F6XJ1X PIC18F8XJ1X                                                | xxxx xxxx                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |  |  |  |

|            |                                                                        |                                    |                                                                                |                                 |  |  |  |  |  |  |

## TABLE 5-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS<sup>(4)</sup> (CONTINUED)

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be effected (to cause wake-up).

4: See Table 5-2 for Reset value for specific conditions.

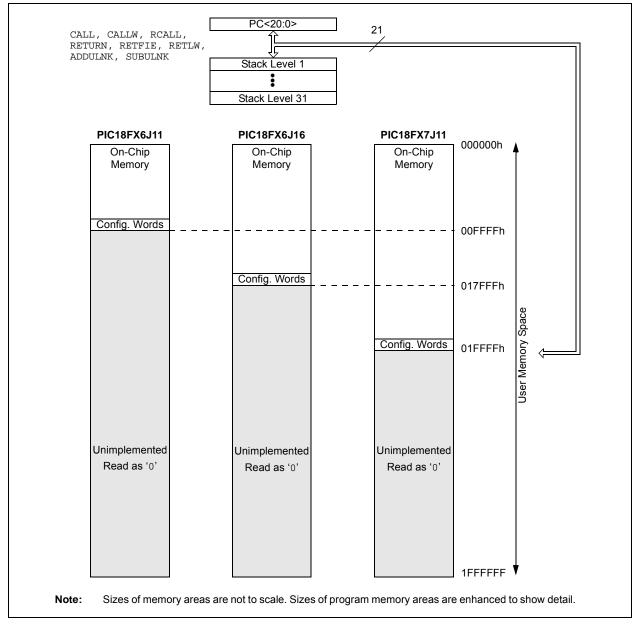

## 6.0 MEMORY ORGANIZATION

There are two types of memory in PIC18 Flash microcontroller devices:

- Program Memory

- Data RAM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**.

## 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit Program Counter (PC) which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The entire PIC18F87J11 family of devices offers three different on-chip Flash program memory sizes, from 64 Kbytes (up to 16,384 single-word instructions) to 128 Kbytes (65,536 single-word instructions). The program memory maps for individual family members are shown in Figure 6-3.

#### FIGURE 6-1: MEMORY MAPS FOR PIC18F87J11 FAMILY DEVICES

## 6.1.6.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-2) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 25.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | underflow has the effect of vectoring the |  |  |  |  |  |  |  |  |

|       | program to the Reset vector, where the    |  |  |  |  |  |  |  |  |

|       | stack conditions can be verified and      |  |  |  |  |  |  |  |  |

|       | appropriate actions can be taken. This is |  |  |  |  |  |  |  |  |

|       | not the same as a Reset, as the contents  |  |  |  |  |  |  |  |  |

|       | of the SFRs are not affected.             |  |  |  |  |  |  |  |  |

#### 6.1.6.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack, without disturbing normal program execution, is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

## REGISTER 6-2: STKPTR: STACK POINTER REGISTER

| R/C-0                          | R/C-0                 | U-0              | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |

|--------------------------------|-----------------------|------------------|-------|-------------------|-----------------|--------------------|-------|

| STKFUL <sup>(1)</sup>          | STKUNF <sup>(1)</sup> |                  | SP4   | SP3               | SP2             | SP1                | SP0   |

| bit 7                          | •                     |                  |       |                   | •               |                    | bit 0 |

|                                |                       |                  |       |                   |                 |                    |       |

| Legend: C = Clearable Only bit |                       |                  |       |                   |                 |                    |       |

| R = Readable                   | bit                   | W = Writable     | bit   | U = Unimplem      | nented bit, rea | d as '0'           |       |

| -n = Value at I                | POR                   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unknown |       |

|                                |                       |                  |       |                   |                 |                    |       |

|                                |                       |                  | (1)   |                   |                 |                    |       |

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>      |

|---------|-------------------------------------------------|

|         | 1 = Stack became full or overflowed             |

|         | 0 = Stack has not become full or overflowed     |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup> |

|         | <ol> <li>Stack underflow occurred</li> </ol>    |

|         | 0 = Stack underflow did not occur               |

| bit 5   | Unimplemented: Read as '0'                      |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits            |

|         |                                                 |

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

#### 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |

|-------|--------------------------------------------|

|       | core PIC18 instruction set are changed     |

|       | when the PIC18 extended instruction set is |

|       | enabled. See Section 6.6 "Data Memory      |

|       | and the Extended Instruction Set" for      |

|       | more information.                          |

While the program memory can be addressed in only one way, through the Program Counter, information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 6.6.1 "Indexed Addressing with Literal Offset**".

## 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device, or they operate implicitly on one register. This addressing mode is known as Inherent Addressing; examples include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This is known as Literal Addressing mode, because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit Literal Address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General

**Purpose Register File**"), or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

#### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|        | LFSR  | FSR0, 100h | ; |                |

|--------|-------|------------|---|----------------|

| NEXT   | CLRF  | POSTINC0   | ; | Clear INDF     |

|        |       |            | ; | register then  |

|        |       |            | ; | inc pointer    |

|        | BTFSS | FSROH, 1   | ; | All done with  |

|        |       |            | ; | Bank1?         |

|        | BRA   | NEXT       | ; | NO, clear next |

| CONTIN | UE    |            | ; | YES, continue  |

|        |       |            |   |                |

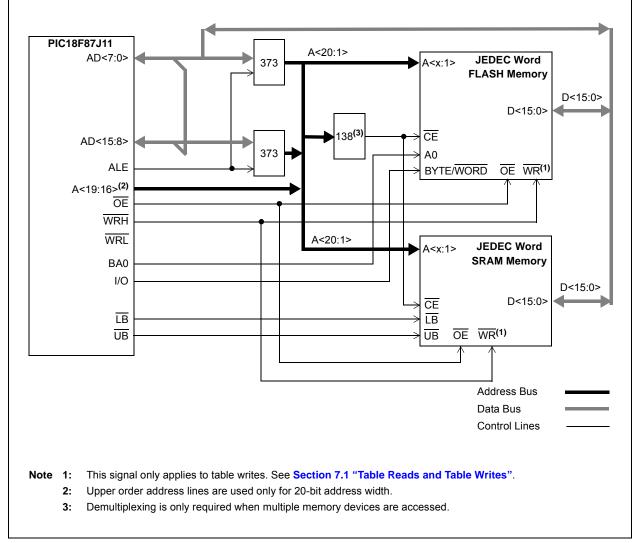

#### 8.6.3 16-BIT BYTE SELECT MODE

Figure 8-3 shows an example of 16-Bit Byte Select mode. This mode allows table write operations to word-wide external memories with byte selection capability. This generally includes both word-wide Flash and SRAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH signal is strobed for each write cycle; the WRL pin is not used. The BA0 or UB/LB signals are used to select the byte to be written, based on the Least Significant bit of the TBLPTR register. Flash and SRAM devices use different control signal combinations to implement Byte Select mode. JEDEC standard Flash memories require that a controller I/O port pin be connected to the memory's BYTE/WORD pin to provide the select signal. They also use the BA0 signal from the controller as a byte address. JEDEC standard static RAM memories, on the other hand, use the UB or LB signals to select the byte.

| Pin Name      | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                               |  |  |  |  |

|---------------|----------------------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RB0/INT0/FLT0 | RB0                  | 0               | 0   | DIG         | LATB<0> data output.                                                                                                                      |  |  |  |  |

|               |                      | 1               | I   | TTL         | PORTB<0> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | INT0                 | 1               | I   | ST          | External Interrupt 0 input.                                                                                                               |  |  |  |  |

|               | FLT0                 | 1               | I   | ST          | Enhanced PWM Fault input (ECCP1 module); enabled in software.                                                                             |  |  |  |  |

| RB1/INT1/     | RB1                  | 0               | 0   | DIG         | LATB<1> data output.                                                                                                                      |  |  |  |  |

| PMA4          |                      | 1               | I   | TTL         | PORTB<1> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | INT1                 | 1               | Ι   | ST          | External Interrupt 1 input.                                                                                                               |  |  |  |  |

|               | PMA4                 | х               | 0   | —           | Parallel Master Port address out.                                                                                                         |  |  |  |  |

| RB2/INT2/     | RB2                  | 0               | 0   | DIG         | IG LATB<2> data output.                                                                                                                   |  |  |  |  |

| PMA3          |                      | 1               | I   | TTL         | PORTB<2> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | INT2                 | 1               | I   | ST          | External Interrupt 2 input.                                                                                                               |  |  |  |  |

|               | PMA3                 | х               | 0   |             | Parallel Master Port address out.                                                                                                         |  |  |  |  |

| RB3/INT3/     | RB3                  | 0               | 0   | DIG         | IG LATB<3> data output.                                                                                                                   |  |  |  |  |

| PMA2/ECCP2/   |                      | 1               | I   | TTL         | PORTB<3> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

| P2A           | INT3                 | 1               | I   | ST          | External Interrupt 3 input.                                                                                                               |  |  |  |  |

|               | PMA2                 | x               | 0   |             | Parallel Master Port address out.                                                                                                         |  |  |  |  |

|               | ECCP2 <sup>(1)</sup> | 0               | 0   | DIG         | ECCP2 compare output and CCP2 PWM output; takes priority over port data.                                                                  |  |  |  |  |

|               |                      | 1               | I   | ST          | ECCP2 capture input.                                                                                                                      |  |  |  |  |

|               | P2A <sup>(1)</sup>   | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, Channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |  |  |  |  |

| RB4/KBI0/     | RB4                  | 0               | 0   | DIG         | LATB<4> data output.                                                                                                                      |  |  |  |  |

| PMA1          |                      | 1               | I   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | KBI0                 |                 | Ι   | TTL         | Interrupt-on-pin change.                                                                                                                  |  |  |  |  |

|               | PMA1                 | х               | 0   | —           | Parallel Master Port address out.                                                                                                         |  |  |  |  |

| RB5/KBI1/     | RB5                  | 0               | 0   | DIG         | LATB<5> data output.                                                                                                                      |  |  |  |  |

| PMA0          |                      | 1               | I   | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | KBI1                 |                 | Ι   | TTL         | Interrupt-on-pin change.                                                                                                                  |  |  |  |  |

|               | PMA0                 | х               | 0   | _           | Parallel Master Port address out.                                                                                                         |  |  |  |  |

| RB6/KBI2/PGC  | RB6                  | 0               | 0   | DIG         | LATB<6> data output.                                                                                                                      |  |  |  |  |

|               |                      | 1               | I   | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | KBI2                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                  |  |  |  |  |

|               | PGC                  | x               | I   | ST          | Serial execution (ICSP™) clock input for ICSP and ICD operation. <sup>(2)</sup>                                                           |  |  |  |  |

| RB7/KBI3/PGD  | RB7                  | 0               | 0   | DIG         | LATB<7> data output.                                                                                                                      |  |  |  |  |

|               |                      | 1               | I   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                                               |  |  |  |  |

|               | KBI3                 | 1               | Ι   | TTL         | Interrupt-on-pin change.                                                                                                                  |  |  |  |  |

|               | PGD                  | x               | 0   | DIG         | Serial execution data output for ICSP and ICD operation. <sup>(2)</sup>                                                                   |  |  |  |  |

|               |                      | х               | I   | ST          | Serial execution data input for ICSP and ICD operation. <sup>(2)</sup>                                                                    |  |  |  |  |

## TABLE 11-6: PORTB FUNCTIONS

Legend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Alternate assignment for ECCP2/P2A when the CCP2MX Configuration bit is cleared (Extended Microcontroller mode, 80-pin devices only); the default assignment is RC1.

2: All other pin functions are disabled when ICSP™ or ICD is enabled.

## **19.2 Capture and Compare Modes**

Except for the operation of the Special Event Trigger discussed below, the Capture and Compare modes of the ECCP module are identical in operation to that of CCP4. These are discussed in detail in Section 18.2 "Capture Mode" and Section 18.3 "Compare Mode".

#### 19.2.1 SPECIAL EVENT TRIGGER

ECCP1 and ECCP2 incorporate an internal hardware trigger that is generated in Compare mode on a match between the CCPRx register pair and the selected timer. This can be used in turn to initiate an action. This mode is selected by setting CCPxCON<3:0> to '1011'.

The Special Event Trigger output of either ECCP1 or ECCP2 resets the TMR1 or TMR3 register pair, depending on which timer resource is currently selected. This allows the CCPRx register pair to effectively be a 16-bit programmable period register for Timer1 or Timer3. In addition, the ECCP2 Special Event Trigger will also start an A/D conversion if the A/D module is enabled.

Special Event Triggers are not implemented for ECCP3, CCP4 or CCP5. Selecting the Special Event Trigger mode for these modules has the same effect as selecting the Compare with Software Interrupt mode (CCPxM<3:0> = 1010).

Note: The Special Event Trigger from ECCP2 will not set the Timer1 or Timer3 interrupt flag bits.

#### 19.3 Standard PWM Mode

When configured in Single Output mode, the ECCP module functions identically to the standard CCP module in PWM mode, as described in **Section 18.4** "**PWM Mode**". This is also sometimes referred to as "Compatible CCP" mode as in Tables 19-1 through 19-3.

Note: When setting up single output PWM operations, users are free to use either of the processes described in Section 18.4.3 "Setup for PWM Operation" or Section 19.4.9 "Setup for PWM Operation". The latter is more generic but will work for either single or multi-output PWM.

## EXAMPLE 21-1: CALCULATING BAUD RATE ERROR

| For a device with FOSC of 16 | For a device with FOSC of 16 MHz, desired baud rate of 9600, Asynchronous mode, and 8-bit BRG: |                                                              |  |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| Desired Baud Rate            | =                                                                                              | Fosc/(64 ([SPBRGHx:SPBRGx] + 1))                             |  |  |  |  |  |

| Solving for SPBRGHx:         | SPB                                                                                            | RGx:                                                         |  |  |  |  |  |

| Х                            | =                                                                                              | ((FOSC/Desired Baud Rate)/64) – 1                            |  |  |  |  |  |

|                              | =                                                                                              | ((16000000/9600)/64) – 1                                     |  |  |  |  |  |

|                              | =                                                                                              | [25.042] = 25                                                |  |  |  |  |  |

| Calculated Baud Rate         | =                                                                                              | 16000000/(64 (25 + 1))                                       |  |  |  |  |  |

|                              | =                                                                                              | 9615                                                         |  |  |  |  |  |

| Error                        | =                                                                                              | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate |  |  |  |  |  |

|                              | =                                                                                              | (9615 - 9600)/9600 = 0.16%                                   |  |  |  |  |  |

|                              |                                                                                                |                                                              |  |  |  |  |  |

#### TABLE 21-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name                                                   | Bit 7                                      | Bit 6     | Bit 5       | Bit 4       | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on Page: |

|--------------------------------------------------------|--------------------------------------------|-----------|-------------|-------------|--------|-------|-------|-------|--------------------------|

| TXSTAx                                                 | CSRC                                       | TX9       | TXEN        | SYNC        | SENDB  | BRGH  | TRMT  | TX9D  | 63                       |

| RCSTAx                                                 | SPEN                                       | RX9       | SREN        | CREN        | ADDEN  | FERR  | OERR  | RX9D  | 63                       |

| BAUDCONx                                               | ABDOVF RCIDL RXDTP TXCKP BRG16 — WUE ABDEN |           |             |             |        |       |       |       |                          |

| SPBRGHx EUSARTx Baud Rate Generator Register High Byte |                                            |           |             |             |        |       |       |       | 65                       |

| SPBRGx                                                 | EUSARTx                                    | Baud Rate | Generator I | Register Lo | w Byte |       |       |       | 65                       |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

| R/WO-1        | R/WO-1                                                    | R/WO-1           | U-0             | U-0               | U-0              | U-0             | R/WO-1   |  |  |  |  |

|---------------|-----------------------------------------------------------|------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|--|

| DEBUG         | XINST                                                     | STVREN           | _               | _                 | _                | _               | WDTEN    |  |  |  |  |

| bit 7         | bi                                                        |                  |                 |                   |                  |                 |          |  |  |  |  |

|               |                                                           |                  |                 |                   |                  |                 |          |  |  |  |  |

| Legend:       |                                                           |                  |                 |                   |                  |                 |          |  |  |  |  |

| R = Readable  | e bit                                                     | WO = Write-C     | nce bit         | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                       | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own      |  |  |  |  |

|               |                                                           |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 7         | DEBUG: Bac                                                | kground Debug    | lger Enable bit |                   |                  |                 |          |  |  |  |  |

|               | •                                                         |                  |                 | and RB7 are c     | • •              |                 | I/O pins |  |  |  |  |

|               | •                                                         |                  |                 | and RB7 are d     | edicated to In-0 | Circuit Debug   |          |  |  |  |  |

| bit 6         | XINST: Exten                                              | ded Instruction  | Set Enable bit  | t                 |                  |                 |          |  |  |  |  |

|               |                                                           |                  |                 | Addressing mod    |                  | 4               | ,        |  |  |  |  |

|               |                                                           |                  |                 | Addressing mod    | le are disabled  | (Legacy mode    | )        |  |  |  |  |

| bit 5         | STVREN: Sta                                               | ck Overflow/Ur   | derflow Reset   | Enable bit        |                  |                 |          |  |  |  |  |

|               |                                                           | stack overflow/  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = Reset on stack overflow/underflow is disabled         |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 4-1       | Unimplemented: Read as '0'                                |                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 0         | WDTEN: Wat                                                | chdog Timer E    | nable bit       |                   |                  |                 |          |  |  |  |  |

|               | 1 = WDT is er                                             | nabled           |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = WDT is disabled (control is placed on the SWDTEN bit) |                  |                 |                   |                  |                 |          |  |  |  |  |

## REGISTER 25-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

#### REGISTER 25-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-1     | U-1 | U-1 | U-1 | U-0 | R/WO-1 | U-1 | U-1   |

|---------|-----|-----|-----|-----|--------|-----|-------|

|         | —   | —   | —   | —   | CP0    | —   | —     |

| bit 7   |     |     |     |     |        |     | bit 0 |

|         |     |     |     |     |        |     |       |

| Legend: |     |     |     |     |        |     |       |

| R = Readable bit  | WO = Write-Once bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|---------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-3 Unimplemented: Maintain as '11110'

bit 2 **CP0:** Code Protection bit

- 1 = Program memory is not code-protected

- 0 = Program memory is code-protected

- bit 1-0 Unimplemented: Read as '0'

## 25.3.2 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC18F87J11 family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<0>).

The operation of the Brown-out Reset is described in more detail in Section 5.4 "Brown-out Reset (BOR)" and Section 5.4.1 "Detecting BOR". The brown-out voltage levels are specific in Section 28.1 "DC Characteristics: Supply Voltage PIC18F87J11 Family (Industrial)".

#### 25.3.3 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VDDCORE must never exceed VDD by 0.3 volts.

#### 25.3.4 OPERATION IN SLEEP MODE

When enabled, the on-chip regulator always consumes a small incremental amount of current over IDD. This includes when the device is in Sleep mode, even though the core digital logic does not require power. To provide additional savings in applications where power resources are critical, the regulator can be configured to automatically disable itself whenever the device goes into Sleep mode. This feature is controlled by the REGSLP bit (WDTCON<7>, Register 25-9). Setting this bit disables the regulator in Sleep mode and reduces its current consumption to a minimum. Substantial Sleep mode power savings can be obtained by setting the REGSLP bit, but device wake-up time will increase in order to insure the regulator has enough time to stabilize. The REGSLP bit is automatically cleared by hardware when a Low-Voltage Detect condition occurs.

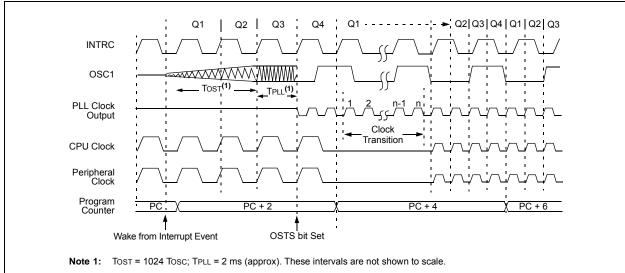

## 25.4 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is HS or HSPLL (Crystal-Based) modes. Since the EC and ECPLL modes do not require an Oscillator Start-up Timer delay, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

FIGURE 25-3: TIMING TRANSITION FOR TWO-SPEED START-UP (INTRC TO HSPLL)

# PIC18F87J11 FAMILY

| NEGF              | Negate f                                                                                                                                                                                                                                                                   |           |      |      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|

| Syntax:           | NEGF f                                                                                                                                                                                                                                                                     | {,a}      |      |      |

| Operands:         | $0 \le f \le 255$<br>$a \in [0,1]$                                                                                                                                                                                                                                         | 5         |      |      |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                         |           |      |      |

| Status Affected:  | N, OV, C,                                                                                                                                                                                                                                                                  | DC, Z     |      |      |

| Encoding:         | 0110                                                                                                                                                                                                                                                                       | 110a      | ffff | ffff |

| Description:      | Location 'f' is negated using two's complement. The result is placed in the data memory location 'f'.                                                                                                                                                                      |           |      |      |

|                   | lf 'a' is '0',<br>If 'a' is '1',<br>GPR bank                                                                                                                                                                                                                               | the BSR i |      |      |

|                   | If 'a' is '0' and the extended instruct<br>set is enabled, this instruction oper<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented an<br>Bit-Oriented Instructions in Inder<br>Literal Offset Mode" for details. |           |      |      |

| Words:            | 1                                                                                                                                                                                                                                                                          |           |      |      |

| Cycles:           | 1                                                                                                                                                                                                                                                                          |           |      |      |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                            |           |      |      |

| Q1                | Q2                                                                                                                                                                                                                                                                         | Q3        | 3    | Q4   |

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

| Example: | NEGF | REG, | 1 |

|----------|------|------|---|

|----------|------|------|---|

| Before Instru   | ction |      |      |       |

|-----------------|-------|------|------|-------|

| REG             | =     | 0011 | 1010 | [3Ah] |

| After Instructi | on    |      |      |       |

| REG             | =     | 1100 | 0110 | [C6h] |

| NOP       |                | No Operation  |                     |       |   |      |  |  |  |

|-----------|----------------|---------------|---------------------|-------|---|------|--|--|--|

| Synta     | ax:            | NOP           | NOP                 |       |   |      |  |  |  |

| Oper      | ands:          | None          |                     |       |   |      |  |  |  |

| Oper      | ation:         | No operati    | on                  |       |   |      |  |  |  |

| Statu     | s Affected:    | None          |                     |       |   |      |  |  |  |

| Encoding: |                | 0000          | 0000                | 000   | 0 | 0000 |  |  |  |

|           |                | 1111          | XXXX                | XXX   | x | xxxx |  |  |  |

| Desc      | ription:       | No operation. |                     |       |   |      |  |  |  |

| Word      | ls:            | 1             |                     |       |   |      |  |  |  |

| Cycle     | es:            | 1             |                     |       |   |      |  |  |  |

| QC        | ycle Activity: |               |                     |       |   |      |  |  |  |

|           | Q1             | Q2            | Q3 Q4               |       |   | Q4   |  |  |  |

|           | Decode         | No            | No                  | No No |   | No   |  |  |  |

|           |                | operation     | operation operation |       |   |      |  |  |  |

Example:

None.

#### 28.2 DC Characteristics: Power-Down and Supply Current PIC18F87J11 Family (Industrial) (Continued)

| PIC18F87J11 Family<br>(Industrial) |                                             | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |            |                                              |                                            |  |  |

|------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|----------------------------------------------|--------------------------------------------|--|--|

| Param<br>No.                       | Device                                      | Тур                                                                                                                                | Max  | Units | Conditions |                                              |                                            |  |  |

|                                    | Supply Current (IDD) Cont. <sup>(2,3)</sup> |                                                                                                                                    |      |       |            |                                              |                                            |  |  |

|                                    | All devices                                 | 18                                                                                                                                 | 35   | μA    | -40°C      |                                              |                                            |  |  |

|                                    |                                             | 19                                                                                                                                 | 35   | μA    | +25°C      | $VDD = 2.0V,$ $VDDCORE = 2.0V^{(4)}$         |                                            |  |  |

|                                    |                                             | 28                                                                                                                                 | 49   | μA    | +85°C      | VDDOORE 2.0V                                 |                                            |  |  |

|                                    | All devices                                 | 20                                                                                                                                 | 45   | μA    | -40°C      |                                              | Fosc = 32 kHz <sup>(3)</sup>               |  |  |

|                                    |                                             | 21                                                                                                                                 | 45   | μA    | +25°C      | VDD = 2.5V,<br>VDDCORE = 2.5V <sup>(4)</sup> | ( <b>SEC_RUN</b> mode,<br>Timer1 as clock) |  |  |

|                                    |                                             | 32                                                                                                                                 | 61   | μA    | +85°C      |                                              |                                            |  |  |

|                                    | All devices                                 | 0.06                                                                                                                               | 0.11 | mA    | -40°C      |                                              |                                            |  |  |

|                                    |                                             | 0.07                                                                                                                               | 0.11 | mA    | +25°C      | VDD = 3.3V <sup>(5)</sup>                    |                                            |  |  |

|                                    |                                             | 0.09                                                                                                                               | 0.15 | mA    | +85°C      |                                              |                                            |  |  |

|                                    | All devices                                 | 14                                                                                                                                 | 28   | μA    | -40°C      |                                              |                                            |  |  |

|                                    |                                             | 15                                                                                                                                 | 28   | μA    | +25°C      | VDD = 2.0V,<br>$VDDCORE = 2.0V^{(4)}$        |                                            |  |  |

|                                    |                                             | 24                                                                                                                                 | 43   | μA    | +85°C      | VDDOORE 2.0V                                 |                                            |  |  |

|                                    | All devices                                 | 15                                                                                                                                 | 31   | μA    | -40°C      |                                              | Fosc = 32 kHz <sup>(3)</sup>               |  |  |

|                                    |                                             | 16                                                                                                                                 | 31   | μA    | +25°C      | VDD = 2.5V,<br>$VDDCORE = 2.5V^{(4)}$        | (SEC_IDLE mode,                            |  |  |

|                                    |                                             | 27                                                                                                                                 | 50   | μA    | +85°C      |                                              | Timer1 as clock)                           |  |  |

|                                    | All devices                                 | 0.05                                                                                                                               | 0.10 | mA    | -40°C      |                                              |                                            |  |  |

|                                    |                                             | 0.06                                                                                                                               | 0.10 | mA    | +25°C      | VDD = 3.3V <sup>(5)</sup>                    |                                            |  |  |

|                                    |                                             | 0.08                                                                                                                               | 0.14 | mA    | +85°C      |                                              |                                            |  |  |

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in a high-impedance state and tied to VDD or Vss, and all features that add delta current are disabled (such as WDT, Timer1 oscillator, BOR, etc.).

2: The supply current is mainly a function of the operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT is enabled/disabled as specified.

3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

4: Voltage regulator is disabled (ENVREG = 0, tied to Vss).

5: Voltage regulator is enabled (ENVREG = 1, tied to VDD, REGSLP = 1).

# PIC18F87J11 FAMILY

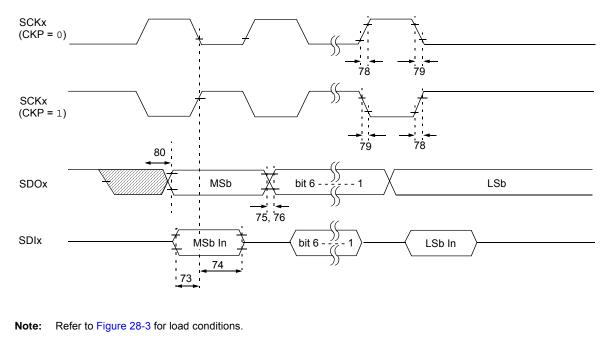

| TABLE 28-20: | EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0) |

|--------------|------------------------------------------------------|

|--------------|------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|-----|-----|-------|------------|

| 73           | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 100 |     | ns    |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                 | —   | 25  | ns    |            |

| 76           | TdoF                  | SDOx Data Output Fall Time                 | —   | 25  | ns    |            |

| 78           | TscR                  | SCKx Output Rise Time                      | —   | 25  | ns    |            |

| 79           | TscF                  | SCKx Output Fall Time                      | —   | 25  | ns    |            |

| 80           | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge     | —   | 50  | ns    |            |

| Param.<br>No. | Symbol  | Charac                           | teristic                  | Min              | Max  | Units | Conditions                   |  |

|---------------|---------|----------------------------------|---------------------------|------------------|------|-------|------------------------------|--|

| 100           | Тнідн   | HIGH Clock High Time 100 kHz mod |                           | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

|               |         |                                  | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

| 101           | TLOW    | Clock Low Time                   | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |  |

|               |         |                                  | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | ms    |                              |  |

| 102           | TR      | SDAx and SCLx                    | 100 kHz mode              |                  | 1000 | ns    | CB is specified to be from   |  |

|               |         | Rise Time                        | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | 10 to 400 pF                 |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | —                | 300  | ns    | Ī                            |  |

| 103           | TF      | SDAx and SCLx                    | 100 kHz mode              | —                | 300  | ns    | CB is specified to be from   |  |

|               |         | Fall Time                        | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | 10 to 400 pF                 |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | _                | 100  | ns    |                              |  |

| 90            | TSU:STA | Start Condition                  | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | Only relevant for Repeated   |  |

|               |         | Setup Time                       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | Start condition              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

| 91            | THD:STA | Start Condition                  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | After this period, the first |  |

|               |         | Hold Time                        | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | clock pulse is generated     |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

| 106           | THD:DAT | Data Input                       | 100 kHz mode              | 0                | _    | ns    |                              |  |

|               |         | Hold Time                        | 400 kHz mode              | 0                | 0.9  | ms    |                              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | _                |      | ns    |                              |  |

| 107           | TSU:DAT | Data Input                       | 100 kHz mode              | 250              | _    | ns    | (Note 2)                     |  |

|               |         | Setup Time                       | 400 kHz mode              | 100              |      | ns    |                              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> |                  | _    | ns    |                              |  |

| 92            | Tsu:sto | Stop Condition                   | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

|               |         | Setup Time                       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | ms    |                              |  |

| 109           | ΤΑΑ     | Output Valid                     | 100 kHz mode              |                  | 3500 | ns    |                              |  |

|               |         | from Clock                       | 400 kHz mode              | _                | 1000 | ns    |                              |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | _                |      | ns    |                              |  |

| 110           | TBUF    | Bus Free Time                    | 100 kHz mode              | 4.7              | —    | ms    | Time the bus must be free    |  |

|               |         |                                  | 400 kHz mode              | 1.3              | —    | ms    | before a new transmission    |  |

|               |         |                                  | 1 MHz mode <sup>(1)</sup> | —                | —    | ms    | can start                    |  |

| D102          | Св      | Bus Capacitive Lo                | bading                    | _                | 400  | pF    |                              |  |

TABLE 28-27: MSSPx I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins.

2: A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but Parameter #107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, Parameter #102 + Parameter #107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCLx line is released.

| Param<br>No. | Symbol        | Characteristic                                    | Min                 | Тур      | Мах        | Units    | Conditions                                                  |