Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | EBI/EMI, I²C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                         |

| Program Memory Size        | 96KB (48K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3930 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 15x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j16-i-pt |

TABLE 1-3: PIC18F6XJ1X PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                             | Pin Number | Pin          | Buffer                  | Description                                                      |

|--------------------------------------|------------|--------------|-------------------------|------------------------------------------------------------------|

| Pin Name                             | 64-TQFP    | Туре         | Туре                    | Description                                                      |

|                                      |            |              |                         | PORTA is a bidirectional I/O port.                               |

| RA0/AN0<br>RA0<br>AN0                | 24         | I/O<br>I     | TTL<br>Analog           | Digital I/O.<br>Analog Input 0.                                  |

| RA1/AN1<br>RA1<br>AN1                | 23         | I/O<br>I     | TTL<br>Analog           | Digital I/O.<br>Analog Input 1.                                  |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF- | 22         | I/O<br> <br> | TTL<br>Analog<br>Analog | Digital I/O. Analog Input 2. A/D reference voltage (low) input.  |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+ | 21         | I/O<br> <br> | TTL<br>Analog<br>Analog | Digital I/O. Analog Input 3. A/D reference voltage (high) input. |

| RA4/T0CKI<br>RA4<br>T0CKI            | 28         | I/O<br>I     | ST<br>ST                | Digital I/O.<br>Timer0 external clock input.                     |

| RA5/AN4<br>RA5<br>AN4                | 27         | I/O<br>I     | TTL<br>Analog           | Digital I/O.<br>Analog Input 4.                                  |

| RA6                                  | _          | _            | _                       | See the OSC2/CLKO/RA6 pin.                                       |

| RA7                                  | _          | _            | _                       | See the OSC1/CLKI/RA7 pin.                                       |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

$I^2C$  = ST with  $I^2C^{TM}$  or SMB levels

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

OD = Open-Drain (no P diode to VDD)

Note 1: Default assignment for ECCP2/P2A when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2/P2A when Configuration bit, CCP2MX, is cleared.

# 2.4 Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)

The on-chip voltage regulator enable pin, ENVREG, must always be connected directly to either a supply voltage or to ground. Tying ENVREG to VDD enables the regulator, while tying it to ground disables the regulator. Refer to **Section 25.3 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

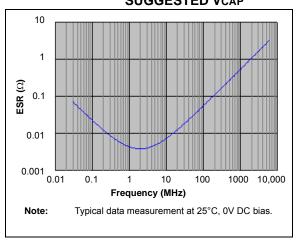

When the regulator is enabled, a low-ESR ( $< 5\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 28.0 "Electrical Characteristics"** for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 28.0** "Electrical Characteristics" for information on VDD and VDDCORE.

Note that the "LF" versions of some low pin count PIC18FJ parts (e.g., the PIC18LF45J10) do not have the ENVREG pin. These devices are provided with the voltage regulator permanently disabled; they must always be provided with a supply voltage on the VDDCORE pin.

FIGURE 2-3: FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |

|-----------|--------------------|------------------------|----------------|---------------|--------------|

| TDK       | C3216X7R1C106K     | 10 μF                  | ±10%           | 16V           | -55 to 125°C |

| TDK       | C3216X5R1C106K     | 10 μF                  | ±10%           | 16V           | -55 to 85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 μF                  | ±10%           | 16V           | -55 to 125°C |

| Panasonic | ECJ-4YB1C106K      | 10 μF                  | ±10%           | 16V           | -55 to 85°C  |

| Murata    | GRM32DR71C106KA01L | 10 μF                  | ±10%           | 16V           | -55 to 125°C |

| Murata    | GRM31CR61C106KC31L | 10 μF                  | ±10%           | 16V           | -55 to 85°C  |

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| R/W-0  | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| INTSRC | PLLEN       | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |  |  |  |  |

| bit 7  | bit 7 bit C |       |       |       |       |       |       |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 INTSRC: Internal Oscillator Low-Frequency Source Select bit

1 = 31.25 kHz device clock derived from 8 MHz INTOSC source (divide-by-256 enabled)

0 = 31 kHz device clock derived from INTRC 31 kHz oscillator

bit 6 PLLEN: Frequency Multiplier PLL Enable bit

1 = PLL is enabled0 = PLL is disabled

bit 5-0 TUN<5:0>: Fast RC Oscillator (INTOSC) Frequency Tuning bits

011111 = Maximum frequency

.

000001

000000 = Center frequency. Fast RC Oscillator is running at the calibrated frequency.

111111

•

100000 = Minimum frequency

# 3.3 Clock Sources and Oscillator Switching

Essentially, PIC18F87J11 family devices have three independent clock sources:

- · Primary oscillators

- · Secondary oscillators

- Internal oscillator

The **primary oscillators** can be thought of as the main device oscillators. These are any external oscillators connected to the OSC1 and OSC2 pins, and include the External Crystal and Resonator modes, and the External Clock modes. If selected by the FOSC<2:0> Configuration bits, the internal oscillator block (either the 31 kHz INTRC or the 8 MHz INTOSC source) may be considered a primary oscillator. The particular mode is defined by the FOSCx Configuration bits. The details of these modes are covered in **Section 3.4** "External **Oscillator Modes**".

The **secondary oscillators** are external clock sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode. PIC18F87J11 family devices offer the Timer1 oscillator

as a secondary oscillator source. This oscillator, in all power-managed modes, is often the time base for functions, such as a Real-Time Clock (RTC). The Timer1 oscillator is discussed in greater detail in Section 14.0 "Timer1 Module".

In addition to being a primary clock source in some circumstances, the **internal oscillator** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor. The internal oscillator block is discussed in more detail in **Section 3.5** "Internal Oscillator Block".

The PIC18F87J11 family includes features that allow the device clock source to be switched from the main oscillator, chosen by device configuration, to one of the alternate clock sources. When an alternate clock source is enabled, various power-managed operating modes are available.

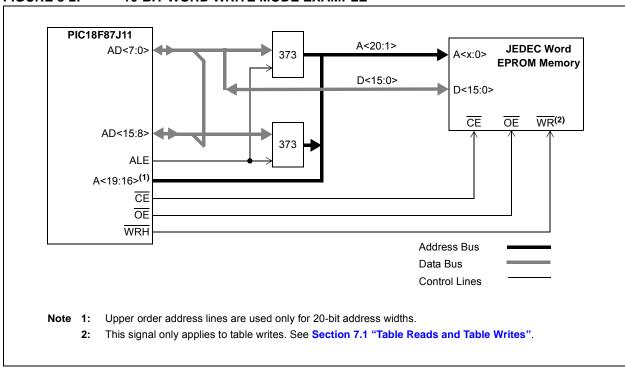

#### 8.6.2 16-BIT WORD WRITE MODE

Figure 8-2 shows an example of 16-Bit Word Write mode for PIC18F87J11 family devices. This mode is used for word-wide memories which include some of the EPROM and Flash type memories. This mode allows opcode fetches and table reads from all forms of 16-bit memory and table writes to any type of word-wide external memories. This method makes a distinction between TBLWT cycles to even or odd addresses.

During a TBLWT cycle to an even address (TBLPTR<0> = 0), the TABLAT data is transferred to a holding latch and the external address data bus is tri-stated for the data portion of the bus cycle. No write signals are activated.

During a TBLWT cycle to an odd address (TBLPTR<0> = 1), the TABLAT data is presented on the upper byte of the AD<15:0> bus. The contents of the holding latch are presented on the lower byte of the AD<15:0> bus.

The WRH signal is strobed for each write cycle; the WRL pin is unused. The signal on the BA0 pin indicates the LSb of the TBLPTR, but it is left unconnected. Instead, the UB and LB signals are active to select both bytes. The obvious limitation to this method is that the table write must be done in pairs on a specific word boundary to correctly write a word location.

FIGURE 8-2: 16-BIT WORD WRITE MODE EXAMPLE

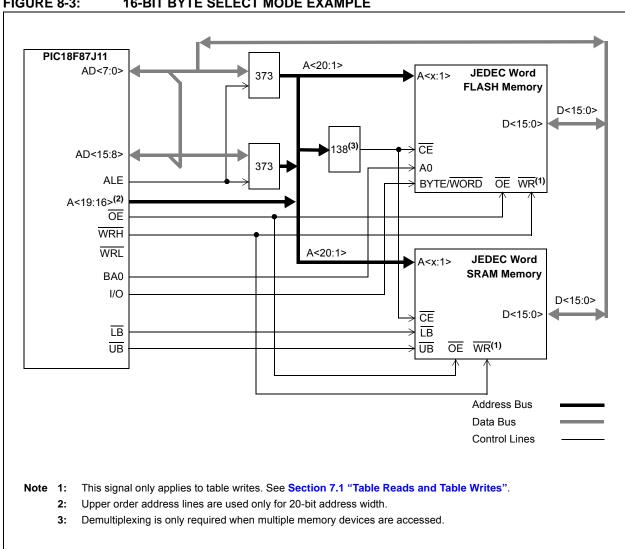

#### 8.6.3 16-BIT BYTE SELECT MODE

Figure 8-3 shows an example of 16-Bit Byte Select mode. This mode allows table write operations to word-wide external memories with byte selection capability. This generally includes both word-wide Flash and SRAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH signal is strobed for each write cycle; the WRL pin is not used. The BA0 or UB/LB signals are used to select the byte to be written, based on the Least Significant bit of the TBLPTR register.

Flash and SRAM devices use different control signal combinations to implement Byte Select mode. JEDEC standard Flash memories require that a controller I/O port pin be connected to the memory's BYTE/WORD pin to provide the select signal. They also use the BA0 signal from the controller as a byte address. JEDEC standard static RAM memories, on the other hand, use the UB or LB signals to select the byte.

FIGURE 8-3: 16-BIT BYTE SELECT MODE EXAMPLE

**NOTES:**

# 11.2 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. It may function as a 6-bit or 7-bit port, depending on the oscillator mode selected. The corresponding Data Direction and Output Latch registers are TRISA and LATA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin; it is also multiplexed as the Parallel Master Port data pin (in 80-pin devices). The other PORTA pins are multiplexed with the analog VREF+ and VREF- inputs. The operation of pins, RA<5,3:0>, as A/D Converter inputs is selected by clearing or setting the appropriate PCFGx control bits in the ANCON0 register.

- **Note 1:** RA5 (RA5/PMD4/AN4) is multiplexed as an analog input in all devices and Parallel Master Port data in 80-pin devices.

- 2: RA5 and RA<3:0> are configured as analog inputs on any Reset and are read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

OSC2/CLKO/RA6 and OSC1/CLKI/RA7 normally serve as the external circuit connections for the external (primary) oscillator circuit (HS and HSPLL Oscillator modes), or the external clock input (EC and ECPLL Oscillator modes). In these cases, RA6 and RA7 are not available as digital I/O, and their corresponding TRIS and LAT bits are read as '0'.

For INTIO and INTPLL Oscillator modes (FOSC2 Configuration bit is '0'), either RA7 or both RA6 and RA7 automatically become available as digital I/O, depending on the oscillator mode selected. When RA6 is not configured as a digital I/O, in these cases, it provides a clock output at Fosc/4. A list of the possible configurations for RA6 and RA7, based on oscillator mode, is provided in Table 11-3. For these pins, the corresponding PORTA, TRISA and LATA bits are only defined when the pins are configured as I/O.

TABLE 11-3: FUNCTION OF RA<7:6> IN INTIO AND INTPLL MODES

| Oscillator Mode (FOSC<2:0> Configuration) | RA6  | RA7 |

|-------------------------------------------|------|-----|

| INTPLL1 (011)                             | CLKO | I/O |

| INTPLL2 (010)                             | I/O  | I/O |

| INTIO1 (001)                              | CLKO | I/O |

| INTIO2 (000)                              | I/O  | I/O |

**Legend:** CLKO = Fosc/4 clock output; I/O = digital port.

#### **EXAMPLE 11-2: INITIALIZING PORTA**

|       |               | ••• |                        |

|-------|---------------|-----|------------------------|

| CLRF  | PORTA         | ;   | Initialize PORTA by    |

|       |               | ;   | clearing output        |

|       |               | ;   | data latches           |

| CLRF  | LATA          | ;   | Alternate method to    |

|       |               | ;   | clear data latches     |

| BSF   | WDTCON, ADSHR | ;   | Enable write/read to   |

|       |               | ;   | the shared SFR         |

| MOVLW | 1Fh           | ;   | Configure A/D          |

| MOVWF | ANCON0        | ;   | for digital inputs     |

| BCF   | WDTCON, ADSHR | ;   | Disable write/read     |

|       |               | ;   | to the shared SFR      |

| MOVLW | H'CF'         | ;   | Value used to          |

|       |               | ;   | initialize             |

|       |               | ;   | data direction         |

| MOVWF | TRISA         | ;   | Set RA<3:0> as inputs, |

|       |               | ;   | RA<5:4> as outputs     |

|       |               |     |                        |

TABLE 11-10: PORTD FUNCTIONS (CONTINUED)

| Pin Name   | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                        |

|------------|---------------------|-----------------|-----|-------------|------------------------------------------------------------------------------------|

| RD6/AD6/   | RD6                 | 0               | 0   | DIG         | LATD<6> data output.                                                               |

| PMD6/SCK2/ |                     | 1               | I   | ST          | PORTD<6> data input.                                                               |

| SCL2       | AD6 <sup>(2)</sup>  | х               | 0   | DIG-3       | External Memory Interface, Address/Data Bit 6 output. (1)                          |

|            |                     | х               | I   | TTL         | External Memory Interface, Data Bit 6 input. <sup>(1)</sup>                        |

|            | PMD6 <sup>(3)</sup> | х               | 0   | DIG         | Parallel Master Port data out.                                                     |

|            |                     | х               | I   | TTL         | Parallel Master Port data input.                                                   |

|            | SCK2                | 0               | 0   | DIG         | SPI clock output (MSSP2 module); takes priority over port data.                    |

|            |                     | 1               | I   | ST          | SPI clock input (MSSP2 module).                                                    |

|            | SCL2                | 0               | 0   | DIG         | I <sup>2</sup> C™ clock output (MSSP2 module); takes priority over port data.      |

|            |                     | 1               | I   | ST          | I <sup>2</sup> C clock input (MSSP2 module); input type depends on module setting. |

| RD7/AD7/   | RD7                 | 0               | 0   | DIG         | LATD<7> data output.                                                               |

| PMD7/SS2   |                     | 1               | I   | ST          | PORTD<7> data input.                                                               |

|            | AD7 <sup>(2)</sup>  | х               | 0   | DIG         | External Memory Interface, Address/Data Bit 7 output. (1)                          |

|            |                     | х               | I   | TTL         | External Memory Interface, Data Bit 7 input. (1)                                   |

|            | PMD7 <sup>(3)</sup> | х               | 0   | DIG         | Parallel Master Port data out.                                                     |

|            |                     | х               | I   | TTL         | Parallel Master Port data input.                                                   |

|            | SS2                 | х               | I   | TTL         | Slave select input for MSSP2 module.                                               |

gend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: External Memory Interface I/O takes priority over all other digital and PMP I/O.

2: These bits are available on 80-pin devices only.

**3:** Default configuration for PMP (PMPMX Configuration bit = 1).

TABLE 11-11: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name  | Bit 7  | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|-------|--------|--------|---------------------|--------|--------|--------|--------|--------|-----------------------------|

| PORTD | RD7    | RD6    | RD5                 | RD4    | RD3    | RD2    | RD1    | RD0    | 65                          |

| LATD  | LATD7  | LATD6  | LATD5               | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 64                          |

| TRISD | TRISD7 | TRISD6 | TRISD5              | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 64                          |

| PORTG | RDPU   | REPU   | RJPU <sup>(1)</sup> | RG4    | RG3    | RG2    | RG1    | RG0    | 65                          |

**Legend:** Shaded cells are not used by PORTD.

Note 1: Unimplemented on 64-pin devices, read as '0'.

# 11.8 PORTG, TRISG and LATG Registers

PORTG is a 5-bit wide, bidirectional port. All pins on PORTG are digital only and tolerate voltages up to 5.5V.

PORTG is multiplexed with EUSART2 functions (Table 11-16). PORTG pins have Schmitt Trigger input buffers. PORTG is also multiplexed with address and control functions of the Parallel Master Port.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTG pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register without concern due to peripheral overrides.

Although the port itself is only five bits wide, PORTG<7:5> bits are still implemented. These are used to control the weak pull-ups on the I/O ports associated with the External Memory Bus (PORTD, PORTE and PORTJ). Setting these bits enables the pull-ups. Since these are control bits and are not associated with port I/O, the corresponding TRISG and LATG bits are not implemented.

#### **EXAMPLE 11-8: INITIALIZING PORTG**

| CLRF  | PORTG | ; Initialize PORTG by       |

|-------|-------|-----------------------------|

|       |       | ; clearing output           |

|       |       | ; data latches              |

| CLRF  | LATG  | ; Alternate method to clear |

|       |       | ; output data latches       |

| MOVLW | 04h   | ; Value used to initialize  |

|       |       | ; data direction            |

| MOVWF | TRISG | ; Set RG1:RG0 as outputs    |

|       |       | ; RG2 as input              |

|       |       | ; RG4:RG3 as outputs        |

|       |       |                             |

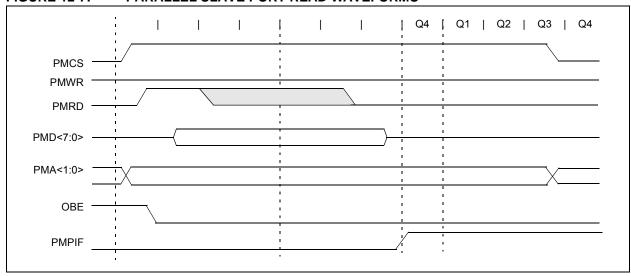

#### 12.2.3.1 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCS = 1 and PMRD = 1), the data from one of the four output bytes is presented onto PMD<7:0>. Which byte is read depends on the 2-bit address placed on ADDR<1:0>. Table 12-2 shows the corresponding output registers and their associated address.

When an output buffer is read, the corresponding OBxE bit is set. The OBE flag bit is set when all the buffers are empty. If any buffer is already empty (OBxE = 1), the next read to that buffer will generate an OBUF event.

FIGURE 12-7: PARALLEL SLAVE PORT READ WAVEFORMS

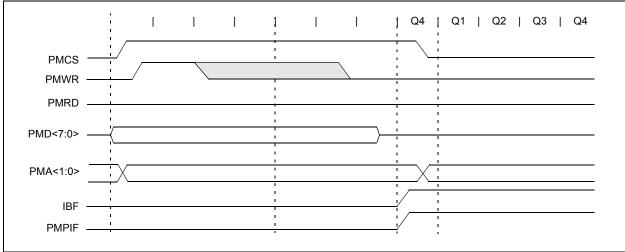

#### 12.2.3.2 WRITE TO SLAVE PORT

When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into one of the four input buffer bytes. Which byte is written depends on the 2-bit address placed on ADDRL<1:0>. Table 12-2 shows the corresponding input registers and their associated address.

When an input buffer is written, the corresponding IBxF bit is set. The IBF flag bit is set when all the buffers are written. If any buffer is already written (IBxF = 1), the next write strobe to that buffer will generate an OBUF event and the byte will be discarded.

FIGURE 12-8: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C™ MODE) **REGISTER 20-3:**

| R/W-0 | R/W-0     | R-0 | R-0  | R-0              | R-0      | R-0 | R-0 |  |  |  |  |

|-------|-----------|-----|------|------------------|----------|-----|-----|--|--|--|--|

| SMP   | CKE       | D/Ā | P(1) | S <sup>(1)</sup> | R/W(2,3) | UA  | BF  |  |  |  |  |

| bit 7 | bit 7 bit |     |      |                  |          |     |     |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SMP: Slew Rate Control bit

In Master or Slave mode:

1 = Slew rate control is disabled for Standard Speed mode (100 kHz and 1 MHz)

0 = Slew rate control is enabled for High-Speed mode (400 kHz)

bit 6 CKE: SMBus Select bit

In Master or Slave mode:

1 = Enables SMBus-specific inputs

0 = Disables SMBus-specific inputs

D/A: Data/Address bit bit 5

In Master mode:

Reserved.

In Slave mode:

1 = Indicates that the last byte received or transmitted was data

0 = Indicates that the last byte received or transmitted was address

bit 4

1 = Indicates that a Stop bit has been detected last

0 = Stop bit was not detected last

S: Start bit(1) bit 3

1 = Indicates that a Start bit has been detected last

0 = Start bit was not detected last

R/W: Read/Write Information bit (2,3) bit 2

In Slave mode:

1 = Read

0 = Write

In Master mode:

1 = Transmit is in progress

0 = Transmit is not in progress

bit 1 **UA:** Update Address bit (10-Bit Slave mode only)

1 = Indicates that the user needs to update the address in the SSPxADD register

0 = Address does not need to be updated

bit 0 BF: Buffer Full Status bit

In Transmit mode:

1 = SSPxBUF is full

0 = SSPxBUF is empty

In Receive mode:

1 = SSPxBUF is full (does not include the  $\overline{ACK}$  and Stop bits)

0 = SSPxBUF is empty (does not include the  $\overline{ACK}$  and Stop bits)

**Note 1:** This bit is cleared on Reset and when SSPEN is cleared.

2: This bit holds the  $R/\overline{W}$  bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit or not ACK bit.

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

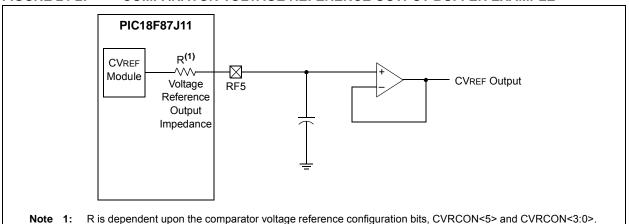

#### 24.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 24-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in Section 28.0 "Electrical Characteristics".

#### 24.3 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RF5 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RF5 as a digital output with CVRSS enabled will also increase current consumption.

The RF5 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 24-2 shows an example buffering technique.

#### 24.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 24.5 Effects of a Reset

A device Reset disables the voltage reference by clearing CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing CVROE, and selects the high-voltage range by clearing CVRR. The CVRx value select bits are also cleared.

FIGURE 24-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

TABLE 24-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|-----------------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|-----------------------------|

| CVRCON <sup>(2)</sup> | CVREN                 | CVROE                 | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 65                          |

| CM1CON                | CON                   | COE                   | CPOL   | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   | 62                          |

| CM2CON                | CON                   | COE                   | CPOL   | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   | 62                          |

| TRISA                 | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 64                          |

| TRISF                 | TRISF7                | TRISF6                | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | _      | 64                          |

| ANCON0 <sup>(2)</sup> | PCFG7                 | PCFG6                 | _      | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 63                          |

| ANCON1 <sup>(2)</sup> | PCFG15                | PCFG14                | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9  | PCFG8  | 63                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

**Note 1:** These bits are only available in select oscillator modes (FOSC2 Configuration bit = 0); otherwise, they are unimplemented.

2: Configuration SFR, overlaps with default SFR at this address; available only when WDTCON<4> = 1.

| BTFS     | SC                                | Bit Test File                                                            | , Skip if Clear                                                                                                               |                                                                  | BTFS        | SS                                                                            | Bit Test File                                                            | , Skip if Set                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synta    | ax:                               | BTFSC f, b                                                               | {,a}                                                                                                                          |                                                                  | Synta       | ax:                                                                           | BTFSS f, b {                                                             | ,a}                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Oper     | ands:                             | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                    |                                                                                                                               |                                                                  | Oper        | ands:                                                                         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                    |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Oper     | ation:                            | skip if (f <b>)</b>                                                      | = 0                                                                                                                           |                                                                  | Oper        | ation:                                                                        | skip if (f <b>)</b>                                                      | = 1                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Statu    | tatus Affected: None              |                                                                          |                                                                                                                               | Statu                                                            | s Affected: | None                                                                          |                                                                          |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Enco     | Encoding: 1011 bbba ffff ffff     |                                                                          |                                                                                                                               | Enco                                                             | ding:       | 1010                                                                          | bbba ff:                                                                 | ff ffff                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Desc     | ription:                          | instruction is<br>the next instruction<br>current instru<br>and a NOP is | gister 'f' is '0', to<br>skipped. If bit<br>ruction fetched<br>action execution<br>executed instruction.                      | 'b' is '0', then<br>during the<br>in is discarded<br>ead, making | Desc        | ription:                                                                      | instruction is<br>the next instruction<br>current instru<br>and a NOP is | gister 'f' is '1', t<br>skipped. If bit<br>ruction fetched<br>uction executio<br>executed instruction.         | 'b' is '1', then<br>during the<br>n is discarded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                                   | •                                                                        | e Access Bank<br>BSR is used to                                                                                               | is selected. If select the                                       |             |                                                                               |                                                                          | e Access Bank<br>BSR is used to                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                   | is enabled, the Indexed Lite whenever f ≤ Section 26.2 Bit-Oriented      | d the extended<br>his instruction<br>ral Offset Addr<br>§ 95 (5Fh). See<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | essing mode<br>ented and<br>in Indexed                           |             |                                                                               | set is enable<br>Indexed Lite<br>whenever f section 26.3<br>Bit-Oriented | d the extended d, this instructional Offset Address 95 (5Fh). See 2.3 "Byte-Oried Instructions et Mode" for de | on operates in<br>essing mode<br>the control of the control<br>the control of the control |

| Word     | s:                                | 1                                                                        |                                                                                                                               |                                                                  | Word        | s:                                                                            | 1                                                                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Cycle    | es:                               | •                                                                        | cles if skip and<br>2-word instruc                                                                                            |                                                                  | Cycle       | es:                                                                           |                                                                          | ycles if skip and<br>a 2-word instru                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Q C      | ycle Activity:                    | •                                                                        |                                                                                                                               |                                                                  | Q C         | ycle Activity:                                                                | ·                                                                        |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | Q1                                | Q2                                                                       | Q3                                                                                                                            | Q4                                                               |             | Q1                                                                            | Q2                                                                       | Q3                                                                                                             | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          | Decode                            | Read register 'f'                                                        | Process<br>Data                                                                                                               | No operation                                                     |             | Decode                                                                        | Read register 'f'                                                        | Process<br>Data                                                                                                | No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| If sk    | ip:                               | 1 oglotor 1                                                              | Duta                                                                                                                          | орогалоп                                                         | lf sk       | ip:                                                                           | rogiotor i                                                               | Duta                                                                                                           | ороганоп                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | Q1                                | Q2                                                                       | Q3                                                                                                                            | Q4                                                               |             | Q1                                                                            | Q2                                                                       | Q3                                                                                                             | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          | No                                | No                                                                       | No                                                                                                                            | No                                                               |             | No                                                                            | No                                                                       | No                                                                                                             | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |