# E·XFL

#### NXP USA Inc. - MKL02Z16VFG4R Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                            |

| Number of I/O              | 14                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 6x12b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 16-QFN (3x3)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl02z16vfg4r |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# KL04/KL05 Product Brief Supports all KL04 and KL05 devices

### 1 Kinetis L Series

The Kinetis L series is the most scalable portfolio of ultra lowpower, mixed-signal ARM Cortex-M0+ MCUs in the industry. The portfolio includes 5 MCU families that offer a broad range of memory, peripheral and package options. Kinetis L Series families share common peripherals and pincounts allowing developers to migrate easily within an MCU family or between MCU families to take advantage of more memory or feature integration. This scalability allows developers to standardize on the Kinetis L Series for their end product platforms, maximising hardware and software reuse and reducing time-to-market.

Features common to all Kinetis L series families include:

- 48 MHz ARM Cortex-M0+ core

- High-speed 12/16-bit analog-to-digital converters

- 12-bit digital-to-analog converters for all series except for KLx4/KLx2 family

- High-speed analog comparators

- Low-power touch sensing with wake-up on touch from reduced power states for all series except for KLx4 family

- Powerful timers for a broad range of applications including motor control

- Low power focused serial communication interfaces such as low power UART, SPI, I2C etc.

- Single power supply: 1.71V 3.6V with multiple lowpower modes support single operation temperature: -40

~ 105 °C (exclude CSP package)

© 2011–2012 Freescale Semiconductor, Inc.

#### Contents

| 1 | Kinetis L Series                  | 1  |

|---|-----------------------------------|----|

| 2 | KL04/KL05 Sub-Family Introduction | 3  |

| 3 | Block Diagram                     | 4  |

| 4 | Features                          | 6  |

| 5 | Power modes                       | 17 |

| 6 | Revision History                  | 19 |

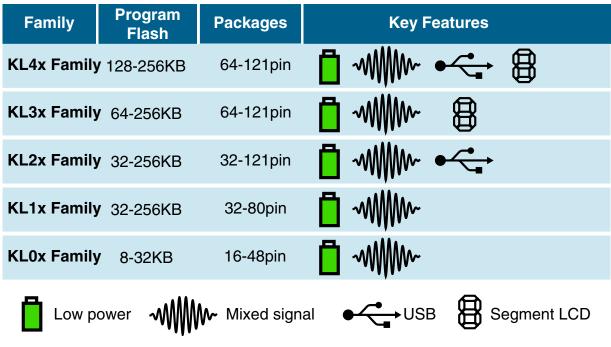

#### Kinetis L Series

Kinetis L series MCU families combine the latest low-power innovations with precision mixed-signal capability and a broad range of communication, connectivity, and human-machine interface peripherals. Each MCU family is supported by a market-leading enablement bundle from Freescale and numerous ARM 3rd party ecosystem partners. The KL0x family is the entry-point to the Kinetis L series and is pin compatible with the 8-bit S08PT family. The KL1x/2x/3x/4x families are compatible with each other and their equivalent ARM Cortex-M4 Kinetis K series families - K10/20/30/40.

#### Figure 1. Kinetis L series families of MCU portfolio

All Kinetis L series families include a powerful array of analog, communication and timing and control peripherals with the level of feature integration increasing with flash memory size and the pin count. Features within the Kinetis L series families include:

- Core and Architecture:

- ARM Cortex-M0+ Core running up to 48 MHz with zero wait state execution from memories

- Single-cycle access to I/O: Up to 50 percent faster than standard I/O, improves reaction time to external events allowing bit banging and software protocol emulation

- Two-stage pipeline: Reduced number of cycles per instruction (CPI), enabling faster branch instruction and ISR entry, and reducing power consumption

- Excellent code density vs. 8-bit and 16-bit MCUs reduces flash size, system cost and power consumption

- Optimized access to program memory: Accesses on alternate cycles reduces power consumption

- 100 percent compatible with ARM Cortex-M0 and a subset ARM Cortex-M3/M4: Reuse existing compilers and debug tools

- Simplified architecture: 56 instructions and 17 registers enables easy programming and efficient packaging of 8/16/32-bit data in memory

- Linear 4 GB address space removes the need for paging/banking, reducing software complexity

- ARM third-party ecosystem support: Software and tools to help minimize development time/cost

- · Micro Trace Buffer: Lightweight trace solution allows fast bug identification and correction

- BME: Bit manipulation engine reduces code size and cycles for bit oriented operations to peripheral registers eliminating traditional methods where the core would need to perform read-modify-write operations.

- Up to 4-channel DMA for peripheral and memory servicing with minimal CPU intervention (feature not available on KL02 family)

- Ultra low-power:

- Extreme dynamic efficiency: 32-bit ARM Cortex-M0+ core combined with Freescale 90 nm thin film storage flash technology delivers 50% energy savings per Coremark versus the closest 8/16-bit competitive solution

#### KL04/KL05 Sub-Family Introduction

- Multiple flexible low-power modes, including new operation clocking option which reduces dynamic power by shutting off bus and system clocks for lowest power core processing. Peripherals with an alternate asynchronous clock source can continue operation.

- UART, SPI, I2C, ADC, DAC, TPM, LPT, and DMA support low-power mode operation without waking up the core

- Memory:

- Scalable memory footprints from 8 KB flash / 1 KB SRAM to 256 KB flash / 32 KB SRAM

- Embedded 64 B cache memory for optimizing bus bandwidth and flash execution performance (32 B cache on KL02 family)

- Mixed-signal analog:

- Fast, high precision 16-, or 12-bit ADC with optional differential pairs, 12-bit DAC, high speed comparators. Powerful signal conditioning, conversion and analysis capability with reduced system cost (12-bit DAC not available on KL02 family)

- Human Machine Interface (HMI):

- Optional capacitive Touch Sensing Interface with full low-power support and minimal current adder when enabled

- Segment LCD controller

- Connectivity and Communications:

- Up to three UARTs, all UARTs support DMA transfers, and can trigger when data on bus is detected, UART0 supports 4x to 32x over sampling ratio. Asynchronous transmit and receive operation for operating in STOP/ VLPS modes.

- Up to two SPIs

- Up to two I<sup>2</sup>Cs

- Full-speed USB OTG controller with on-chip transceiver

- 5 V to 3.3 V USB on-chip regulator

- Up to one I<sup>2</sup>S

- Reliability, Safety and Security:

- Internal watchdog with independent clock source

- Timing and Control:

- Powerful timer modules which support general purpose, PWM, and motor control functions

- Periodic Interrupt Timer for RTOS task scheduler time base or trigger source for ADC conversion and timer modules

- System:

- GPIO with pin interrupt functionality

- Wide operating voltage range from 1.71 V to 3.6 V with flash programmable down to 1.71 V with fully functional flash and analog peripherals

- Ambient operating temperature ranges from -40 °C to 105 °C

### 2 KL04/KL05 Sub-Family Introduction

The device is highly-integrated, market leading ultra low power 32-bit microcontroller based on the enhanced Cortex-M0+ (CM0+) core platform. The family derivatives feature:

- Core platform clock up to 48 MHz, bus clock up to 24 MHz

- Memory option is up to 32 KB Flash and 4 KB RAM

- Wide operating voltage ranges from 1.71V to 3.6V with full functional Flash program/erase/read operations

- Multiple package options from 24-pin to 48-pin

- Ambient operating temperature ranges from –40  $^\circ$ C to 105  $^\circ$ C

The family acts as an ultra low power, cost effective microcontroller to provide developers an appropriate entry-level 32-bit solution. The family is next generation MCU solution for low cost, low power, high performance devices applications. It's valuable for cost-sensitive, portable applications requiring long battery life-time.

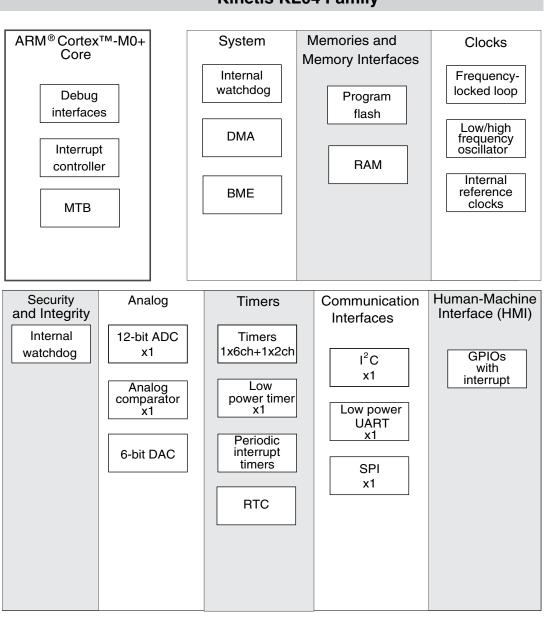

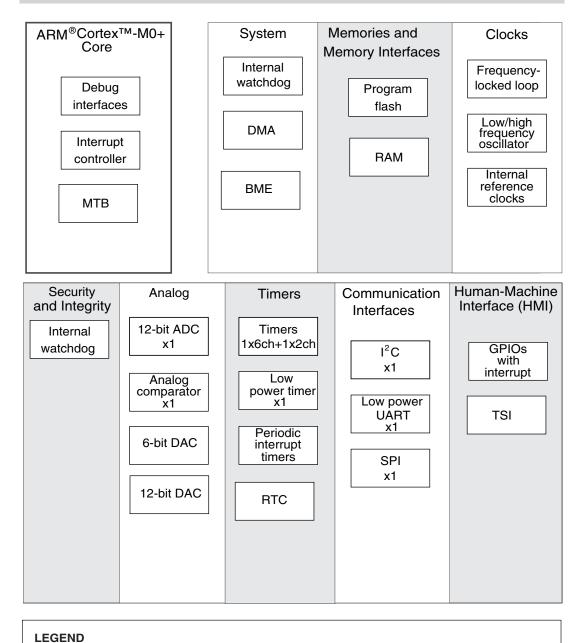

### 3 Block Diagram

The below figure shows a superset block diagram of the device. Other devices within the family have a subset of the features.

#### Kinetis KL04 Family

#### LEGEND

#### Figure 2. KL04 Family Block Diagram

### **Kinetis KL05 Family**

#### Figure 3. KL05 Family Block Diagram

## 4 Features

### 4.1 Feature Summary

All devices within the KL04 and KL05 family features the following at a minimum:

#### Table 1. Common features among all KL04 and KL05 devices

| Operating characteristics    | <ul> <li>1.71 V to 3.6 V</li> <li>Temperature range (T<sub>A</sub>) -40 °C to 85 °C for WLCSP package and -40 °C to 105 °C for all the others</li> <li>Flexible modes of operation</li> </ul>                                                                                                                                                                    |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core features                | <ul> <li>Next generation 32-bit ARM Cortex M0+ core</li> <li>Support up to 32 interrupt request sources</li> <li>Nested vectored interrupt controller (NVIC)</li> <li>Debug &amp; trace capability <ul> <li>2-pin serial wire debug (SWD)</li> <li>Micro trace buffer (MTB)</li> </ul> </li> </ul>                                                               |

| System and power management  | <ul> <li>Software watchdog</li> <li>Integrated bit manipulation engine (BME)</li> <li>DMA controller for KL04 and KL05</li> <li>Low-leakage wake-up unit (LLWU) for KL04 and KL05</li> <li>Power management controller with 10 different power modes</li> <li>Non-maskable interrupt (NMI)</li> <li>80-bit unique identification (ID) number per chip</li> </ul> |

| Clocks                       | <ul> <li>External crystal oscillator or resonator</li> <li>DC- 48 MHz external square wave input clock</li> <li>Internal clock references <ul> <li>31.25 to 39.063 kHz oscillator</li> <li>4 MHz oscillator</li> <li>1 kHz oscillator</li> </ul> </li> <li>Frequency-locked loop with the range of <ul> <li>20-25 MHz</li> <li>40-48 MHz</li> </ul> </li> </ul>  |

| Memory and memory interfaces | <ul><li>Up to 32 KB flash with 64 byte cache for KL04/KL05</li><li>Up to 4 KB random-access memory</li></ul>                                                                                                                                                                                                                                                     |

| Security and integrity       | COP watchdog                                                                                                                                                                                                                                                                                                                                                     |

| Analog                       | <ul> <li>12-bit analog-to-digital converter(ADC)</li> <li>High speed comparator (HSCMP)with internal 6-bit digital-to-analog converter (DAC)</li> <li>12-bit digital-to-analog converter (DAC) for KL05</li> </ul>                                                                                                                                               |

| Timers                       | <ul> <li>One 6-channel and one 2-channel 16-bit TPM modules<br/>for KL04 and KL05, and two 2-channel 16-bit TPM<br/>modules for KL02</li> <li>32-bit Programmable interrupt timer (PIT)</li> <li>Real-time clock (RTC)</li> <li>Low-power timer (LPTMR)</li> <li>System tick timer (SYSTIK)</li> </ul>                                                           |

Table continues on the next page ...

| Table 1. Common features among all KL04 and KL05 devices (co | ontinued) |

|--------------------------------------------------------------|-----------|

|--------------------------------------------------------------|-----------|

| Communications          | <ul> <li>SPI with DMA support</li> <li>I<sup>2</sup>C with DMA support</li> <li>Low-power UART with DMA support</li> </ul>                                       |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Human-machine interface | <ul> <li>GPIO with pin interrupt support, DMA request<br/>capability, and other pin control options</li> <li>Capacitive touch sensing inputs for KL05</li> </ul> |

### 4.2 Memory and package options

The following table summarizes the memory and package options for the KL0x family. All devices which share a common package are pin-for-pin compatible.

|            | <b>A</b>          | Mer        | nory         |                 |              | Package       |              |               |

|------------|-------------------|------------|--------------|-----------------|--------------|---------------|--------------|---------------|

| Sub-Family | Performance (MHz) | Flash (KB) | SRAM<br>(KB) | 16 QFN<br>(3x3) | 24 QFN (4x4) | 32 LQFP (7x7) | 32 QFN (5x5) | 48 LQFP (7x7) |

| KL04       | 48                | 8          | 1            | —               | +            | +             | +            | —             |

|            | 48                | 16         | 2            | —               | +            | +             | +            | +             |

|            | 48                | 32         | 4            | —               | +            | +             | +            | +             |

| KL05       | 48                | 8          | 1            | —               | +            | +             | +            | —             |

|            | 48                | 16         | 2            | _               | +            | +             | +            | +             |

|            | 48                | 32         | 4            | _               | +            | +             | +            | +             |

Table 2. KL0x family summary

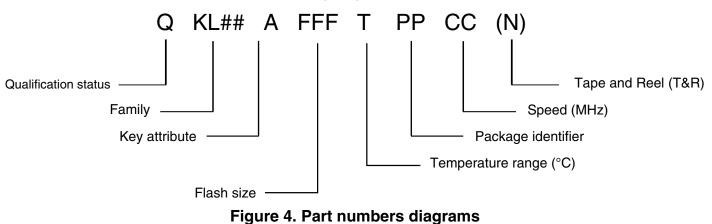

### 4.3 Part Numbers and Packaging

| Field | Description                 | Values                                                                                                                                                   |

|-------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                                                               |

| KL##  | Kinetis family              | • KL04<br>• KL05                                                                                                                                         |

| A     | Key attribute               | • Z = Cortex-M0+                                                                                                                                         |

| FFF   | Program flash memory size   | <ul> <li>8 = 8 KB</li> <li>16 = 16 KB</li> <li>32 = 32 KB</li> </ul>                                                                                     |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                      |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                                                         |

| PP    | Package identifier          | <ul> <li>FK = 24 QFN (4 mm x 4 mm)</li> <li>LC = 32 LQFP (7 mm x 7 mm)</li> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>LF = 48 LQFP (7 mm x 7 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                                                             |

| Ν     | Packaging type              | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                                                                           |

### 4.4 KL04/KL05 Family Features

The following sections list the differences among the various devices available within the KL04/KL05 family.

The features listed below each part number specify the maximum configuration available on that device. The signal multiplexing configuration determines which modules can be used simultaneously.

#### 4.4.1 KL04 family features (48MHz performance) Table 3. KL04 48MHz Performance Table

| MC Partnumber | MKL04Z8VFK4(R)                 | MKL04Z16VFK4(R) | MKL04Z32VFK4(R) | MKL04Z8VLC4(R) | MKL04Z16VLC4(R) | MKL04Z32VLC4(R) | MKL04Z8VFM4(R) | MKL04Z16VFM4(R) | MKL04Z32VFM4(R) | MKL04Z16VLF4(R) | MKL04Z32VLF4(R) |

|---------------|--------------------------------|-----------------|-----------------|----------------|-----------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|

|               |                                |                 |                 | Gene           | ral             |                 |                |                 |                 |                 |                 |

| CPU Frequency | 48<br>MHz                      | 48<br>MHz       | 48<br>MHz       | 48<br>MHz      | 48<br>MHz       | 48<br>MHz       | 48<br>MHz      | 48<br>MHz       | 48<br>MHz       | 48<br>MHz       | 48<br>MHz       |

| Pin Count     | 24                             | 24              | 24              | 32             | 32              | 32              | 32             | 32              | 32              | 48              | 48              |

| Package       | QFN                            | QFN             | QFN             | LQFP           | LQFP            | LQFP            | QFN            | QFN             | QFN             | LQFP            | LQFP            |

|               | Memories and Memory Interfaces |                 |                 |                |                 |                 |                |                 |                 |                 |                 |

| Flash         | 8KB                            | 16KB            | 32KB            | 8KB            | 16KB            | 32KB            | 8KB            | 16KB            | 32KB            | 16KB            | 32KB            |

Table continues on the next page...

#### Features

| Table 3. | KL04 48MHz | Performance | Table | (continued) |

|----------|------------|-------------|-------|-------------|

|----------|------------|-------------|-------|-------------|

|                                             | 1                | 1                | 1                | 1                | -                | i                | -                |                  |                  | i                |                  |

|---------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| MC Partnumber                               | MKL04Z8VFK4(R)   | MKL04Z16VFK4(R)  | MKL04Z32VFK4(R)  | MKL04Z8VLC4(R)   | MKL04Z16VLC4(R)  | MKL04Z32VLC4(R)  | MKL04Z8VFM4(R)   | MKL04Z16VFM4(R)  | MKL04Z32VFM4(R)  | MKL04Z16VLF4(R)  | MKL04Z32VLF4(R)  |

| SRAM                                        | 1KB              | 2KB              | 4KB              | 1KB              | 2KB              | 4KB              | 1KB              | 2KB              | 4KB              | 2KB              | 4KB              |

| Cache                                       | 64B              |

|                                             |                  | •                |                  | Core Mo          | dules            |                  |                  |                  |                  | •                |                  |

| Debug                                       | SWD              |

| Trace                                       | MTB              |

| NMI                                         | YES              |

|                                             |                  |                  | S                | ystem M          | odules           |                  |                  |                  |                  |                  |                  |

| Watchdog                                    | YES              |

| PMC                                         | YES              |

| DMA                                         | 4ch              |

| BME (Bit Manipulation<br>Engine)            | YES              |

|                                             | •                |                  | (                | Clock Mo         | odules           |                  |                  |                  |                  | •                |                  |

| MCG                                         | FLL              |

| OSC (32-40kHz/3-32MHz)                      | YES              |

| RTC                                         | YES              |

|                                             |                  |                  |                  | Anal             | og               |                  |                  |                  |                  |                  |                  |

| Total SE Channels SAR<br>ADC (w temp sense) | 12bit,<br>1x12ch | 12bit,<br>1x12ch | 12bit,<br>1x12ch | 12bit,<br>1x14ch |

| DP Channels                                 | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

| SE Channels                                 | 12ch             | 12ch             | 12ch             | 14ch             |

| 12-bit DAC                                  | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

| Analog Comparator                           | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| Analog Comparator Inputs                    | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                |

|                                             |                  |                  |                  | Time             | rs               |                  |                  |                  |                  |                  |                  |

| General purpose/PWM                         | 1x6ch<br>+1x2ch  |

| Low Power Timer                             | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| PIT (32bit)                                 | 1x2ch            |

|                                             |                  |                  | Comm             | unicatio         | n Interfa        | ces              |                  |                  |                  |                  |                  |

| Low Power UART                              | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| UART                                        | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

| SPI chip selects per module                 | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              |

| I2C                                         | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| I2S                                         | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

|                                             |                  |                  | abla aan         |                  |                  |                  |                  |                  |                  |                  |                  |

Table continues on the next page...

| Table 3. | KL04 48MHz Performance Table ( | (continued) | ) |

|----------|--------------------------------|-------------|---|

|----------|--------------------------------|-------------|---|

| MC Partnumber                    | MKL04Z8VFK4(R) | MKL04Z16VFK4(R) | MKL04Z32VFK4(R) | MKL04Z8VLC4(R) | MKL04Z16VLC4(R) | MKL04Z32VLC4(R) | MKL04Z8VFM4(R) | MKL04Z16VFM4(R) | MKL04Z32VFM4(R) | MKL04Z16VLF4(R) | MKL04Z32VLF4(R) |

|----------------------------------|----------------|-----------------|-----------------|----------------|-----------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| USB OTG LS/FS w/ on-chip<br>xcvr | -              | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

| USB 120mAReg                     | -              | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

|                                  |                |                 | Huma            | n-Machi        | ne Interf       | ace             |                |                 |                 |                 |                 |

| Segment LCD                      | -              | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

| TSI (Capacitive Touch)           | -              | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

| Total GPIOs                      | 22             | 22              | 22              | 28             | 28              | 28              | 28             | 28              | 28              | 41              | 41              |

| GPIOs w/ Interrupt               | 12             | 12              | 12              | 14             | 14              | 14              | 14             | 14              | 14              | 18              | 18              |

| High Current GPIOs (18mA)        | 2              | 2               | 2               | 4              | 4               | 4               | 4              | 4               | 4               | 4               | 4               |

|                                  |                |                 | Opera           | ting Cha       | racteris        | tics            |                |                 |                 |                 |                 |

| Voltage Range                    | 1.71-3.<br>6V  | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V  | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V  | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V   |

| Flash Write V                    | 1.71V          | 1.71V           | 1.71V           | 1.71V          | 1.71V           | 1.71V           | 1.71V          | 1.71V           | 1.71V           | 1.71V           | 1.71V           |

| Temp Range                       | -40 to<br>105C | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C  |

# 4.4.2 KL05 family features (48 MHz performance)

| MC Partnumber | MKL05Z8VFK4(R)                 | MKL05Z16VFK4(R) | MKL05Z32VFK4(R) | MKL05Z8VLC4(R) | MKL05Z16VLC4(R) | MKL05Z32VLC4(R) | MKL05Z8VFM4(R) | MKL05Z16VFM4(R) | MKL05Z32VFM4(R) | MKL05Z16VLF4(R) | MKL05Z32VLF4(R) |

|---------------|--------------------------------|-----------------|-----------------|----------------|-----------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|

|               |                                |                 |                 | Gene           | ral             |                 |                |                 |                 |                 |                 |

| CPU Frequency | 48<br>MHz                      | 48<br>MHz       | 48<br>MHz       | 48<br>MHz      | 48<br>MHz       | 48<br>MHz       | 48<br>MHz      | 48<br>MHz       | 48<br>MHz       | 48<br>MHz       | 48<br>MHz       |

| Pin Count     | 24                             | 24              | 24              | 32             | 32              | 32              | 32             | 32              | 32              | 48              | 48              |

| Package       | QFN                            | QFN             | QFN             | LQFP           | LQFP            | LQFP            | QFN            | QFN             | QFN             | LQFP            | LQFP            |

|               | Memories and Memory Interfaces |                 |                 |                |                 |                 |                |                 |                 |                 |                 |

| Flash         | 8KB                            | 16KB            | 32KB            | 8KB            | 16KB            | 32KB            | 8KB            | 16KB            | 32KB            | 16KB            | 32KB            |

| SRAM          | 1KB                            | 2KB             | 4KB             | 1KB            | 2KB             | 4KB             | 1KB            | 2KB             | 4KB             | 2KB             | 4KB             |

Table 4. KL05 48 MHz performance table

Table continues on the next page ...

#### Features

| Table 4. | KL05 48 MHz performance table (continued) |

|----------|-------------------------------------------|

|----------|-------------------------------------------|

|                                             |                  |                  |                  | -                |                  | 1                | -                | -                |                  | 1                |                  |

|---------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| MC Partnumber                               | MKL05Z8VFK4(R)   | MKL05Z16VFK4(R)  | MKL05Z32VFK4(R)  | MKL05Z8VLC4(R)   | MKL05Z16VLC4(R)  | MKL05Z32VLC4(R)  | MKL05Z8VFM4(R)   | MKL05Z16VFM4(R)  | MKL05Z32VFM4(R)  | MKL05Z16VLF4(R)  | MKL05Z32VLF4(R)  |

| Cache                                       | 64B              |

|                                             |                  |                  |                  | Core Mo          | dules            |                  |                  |                  |                  |                  |                  |

| Debug                                       | SWD              |

| Trace                                       | MTB              |

| NMI                                         | YES              |

|                                             | •                |                  | S                | ystem M          | odules           |                  |                  |                  | •                |                  |                  |

| Watchdog                                    | YES              |

| PMC                                         | YES              |

| DMA                                         | 4ch              |

| BME (Bit Manipulation<br>Engine)            | YES              |

|                                             |                  |                  | (                | Clock Mo         | odules           |                  |                  | <u>.</u>         | ļ                |                  |                  |

| MCG                                         | FLL              |

| OSC (32-40kHz/3-32MHz)                      | YES              |

| RTC                                         | YES              |

|                                             |                  |                  |                  | Anal             | og               |                  |                  |                  |                  |                  |                  |

| Total SE Channels SAR<br>ADC (w temp sense) | 12bit,<br>1x12ch | 12bit,<br>1x12ch | 12bit,<br>1x12ch | 12bit,<br>1x14ch |

| DP Channels                                 | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

| SE Channels                                 | 12ch             | 12ch             | 12ch             | 14ch             |

| 12-bit DAC                                  | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| Analog Comparator                           | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| Analog Comparator Inputs                    | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                | 4                |

|                                             |                  |                  |                  | Time             | rs               |                  |                  |                  |                  |                  |                  |

| General purpose/PWM                         | 1x6ch<br>+1x2ch  |

| Low Power Timer                             | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| PIT (32bit)                                 | 1x2ch            |

| Communication Interfaces                    |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| Low Power UART                              | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| UART                                        | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

| SPI chip selects per module                 | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              | 1/0              |

| I2C                                         | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | 1                |

| I2S                                         | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                | -                |

Table continues on the next page...

| MC Partnumber                    | MKL05Z8VFK4(R)            | MKL05Z16VFK4(R) | MKL05Z32VFK4(R) | MKL05Z8VLC4(R) | MKL05Z16VLC4(R) | MKL05Z32VLC4(R) | MKL05Z8VFM4(R) | MKL05Z16VFM4(R) | MKL05Z32VFM4(R) | MKL05Z16VLF4(R) | MKL05Z32VLF4(R) |

|----------------------------------|---------------------------|-----------------|-----------------|----------------|-----------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| USB OTG LS/FS w/ on-chip<br>xcvr | -                         | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

| USB 120mAReg                     | -                         | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

|                                  |                           |                 | Huma            | n-Machi        | ne Interf       | ace             |                |                 |                 |                 |                 |

| Segment LCD                      | -                         | -               | -               | -              | -               | -               | -              | -               | -               | -               | -               |

| TSI (Capacitive Touch)           | 8ch                       | 8ch             | 8ch             | 12ch           | 12ch            | 12ch            | 12ch           | 12ch            | 12ch            | 12ch            | 12ch            |

| Total GPIOs                      | 22                        | 22              | 22              | 28             | 28              | 28              | 28             | 28              | 28              | 41              | 41              |

| GPIOs w/ Interrupt               | 12                        | 12              | 12              | 14             | 14              | 14              | 14             | 14              | 14              | 18              | 18              |

| High Current GPIOs (18mA)        | 2                         | 2               | 2               | 4              | 4               | 4               | 4              | 4               | 4               | 4               | 4               |

|                                  | Operating Characteristics |                 |                 |                |                 |                 |                |                 |                 |                 |                 |

| Voltage Range                    | 1.71-3.<br>6V             | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V  | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V  | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V   | 1.71-3.<br>6V   |

| Flash Write V                    | 1.71V                     | 1.71V           | 1.71V           | 1.71V          | 1.71V           | 1.71V           | 1.71V          | 1.71V           | 1.71V           | 1.71V           | 1.71V           |

| Temp Range                       | -40 to<br>105C            | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C  | -40 to<br>105C  |

Table 4. KL05 48 MHz performance table (continued)

### 4.5 Module-by-module feature list

The following sections describe the high-level module features for the family's superset device. See the previous section for differences among the subset devices.

### 4.5.1 Core Modules

#### 4.5.1.1 ARM Cortex M0+ Core

- Up to 48 MHz core frequency from 1.71 V to 3.6 V across temperature range of -40 °C to 105 °C

- Support up to 32 interrupt request sources

- 2-stage pipeline microarchitecture for reduced power consumption and improved architectural performance (cycles per instruction)

- Binary compatible instruction set architecture with the CM0 core

- Thumb instruction set combines high code density with 32-bit performance

- Serial wire debug (SWD) reduces the number of pins required for debugging

- Micro trace buffer (MTB) provides lightweight program trace capabilities using system RAM as the destination memory

- Single cycle 32 bits by 32 bits multiply

### 4.5.1.2 Nested Vectored Interrupt Controller (NVIC)

- Up to 32 interrupt sources

- Includes a single non-maskable interrupt

### 4.5.1.3 Wake-up Interrupt Controller (WIC)

- · Supports interrupt handling when system clocking is disabled in low power modes

- Takes over and emulates the NVIC behavior when correctly primed by the NVIC on entry to very-deep-sleep

- A rudimentary interrupt masking system with no prioritization logic signals for wake-up as soon as a non-masked interrupt is detected

- Contains no programmer's model visible state and is therefore invisible to end users of the device other than through the benefits of reduced power consumption while sleeping

#### 4.5.1.4 Debug Controller

- 2-pin serial wire debug (SWD) provides external debugger interface

- Micro trace buffer (MTB) provides simple execution trace capability and operates as a simple AHB-Lite SRAM controller

### 4.5.2 System Modules

### 4.5.2.1 Power Management Control Unit (PMC)

- Separate digital (regulated) and analog (referenced to digital) supply outputs

- Programmable power saving modes

- No output supply decoupling capacitors required

- · Available wake-up from power saving modes via RTC and external inputs

- Integrated Power-on Reset (POR)

- Integrated Low Voltage Detect (LVD) with reset (brownout) capability

- Selectable LVD trip points

- Programmable Low Voltage Warning (LVW) interrupt capability

- Buffered bandgap reference voltage output

- Factory programmed trim for bandgap and LVD

- 1 kHz Low Power Oscillator (LPO)

### 4.5.2.2 DMA Channel Multiplexer (DMA MUX)

- 4 independently selectable DMA channel routers

- 2 periodic trigger sources available

- Each channel router can be assigned to 1 of 63 possible peripheral DMA sources

### 4.5.2.3 DMA Controller

Four independently programmable DMA controller channels provides the means to directly transfer data between system memory and I/O peripherals

- DMA controller is capable of functioning in run, wait and stop modes of operation

- Dual-address transfers via 32-bit master connection to the system bus

#### Memories and Memory Interfaces

- Data transfers in 8-, 16-, or 32-bit blocks

- Continuous-mode or cycle-steal transfers from software or peripheral initiation

#### 4.5.2.4 COP Watchdog Module

- Independent clock source input (independent from CPU/bus clock)

- Choice between two clock sources

- LPO oscillator

- Bus clock

#### 4.5.2.5 System Clocks

- System Oscillator (XOSC) Loop-control Pierce oscillator; Crystal or ceramic resonator range of 32 kHz to 40 kHz (low range mode) or 3-32 MHz (high range mode)

- Multipurpose Clock Generator (MCG)

- Frequency-locked loop (FLL) controlled by internal or external reference

- 20MHz~40MHz FLL output

- 40MHz~48MHz FLL output

- Internal reference clocks Can be used as a clock source for other on-chip peripherals

- On-chip RC oscillator range of 31.25 kHz to 39.0625 kHz with 0.2% trim step and 1% accuracy across temperature range of 0 °C to 70 °C and 2% accuracy across full temperature range

- Ultra low power 4 MHz IRC

### 4.5.3 Memories and Memory Interfaces

#### 4.5.3.1 On-Chip Memory

- 48 MHz performance devices

- Up to 32 KB program flash memory

- Up to 4 KB SRAM

- · Security circuitry to prevent unauthorized access to RAM and flash contents

### 4.5.4 Analog

### 4.5.4.1 Analog-to-Digital Converter (ADC)

- Linear successive approximation algorithm with up to 16-bit resolution

- Output modes:

- Single-ended 12-bit, 10-bit, and 8-bit modes, in right-justified unsigned format

- Single or continuous conversion

- Configurable sample time and conversion speed/power

- · Conversion complete and hardware average complete flag and interrupt

- Input clock selectable from up to four sources

- Operation in low power modes for lower noise operation

- Asynchronous clock source for lower noise operation with option to output the clock

- Selectable asynchronous hardware conversion trigger with hardware channel select

- Automatic compare with interrupt for various programmable values

- Temperature sensor

- Hardware average function

- Selectable voltage reference

- Self-calibration mode

### 4.5.4.2 High-Speed Analog Comparator (CMP)

- 6-bit DAC programmable reference generator output

- Up to five selectable comparator inputs; each input can be compared with any input by any polarity sequence

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output

- Comparator output supports:

- Sampled

- · Windowed (ideal for certain PWM zero-crossing-detection applications

- Digitally filtered using external sample signal or scaled peripheral clock

- Two performance modes:

- · Shorter propagation delay at the expense of higher power

- Low power, with longer propagation delay

- Operational in all MCU power modes except for VLLS0

#### 4.5.4.3 12-Bit Digital-to-Analog Converter (DAC)

- 12-bit resolution

- · Guaranteed 6-sigma monotonicity over input word

- · High- and low-speed conversions

- 1 µs conversion rate for high speed, 2 µs for low speed

- Power-down mode

- · Automatic mode allows the DAC to generate its own output waveforms including square, triangle, and sawtooth

- · Automatic mode allows programmable period, update rate, and range

- DMA support

#### 4.5.5 Timers

#### 4.5.5.1 Timer/PWM (TPM)

- Selectable source clock

- Programmable prescaler

- 16-bit counter supporting free-running or initial/final value, and counting is up or up-down

- · Input capture, output compare, and edge-aligned and center-aligned PWM modes

- Input capture and output compare modes

- · Generation of hardware triggers

- DMA support for TPM events

### 4.5.5.2 Periodic Interrupt Timers (PITs)

- 2 general purpose interrupt timers

- 2 interrupt timers for triggering ADC conversions

- 32-bit counter resolution

- Clocked by bus clock frequency

- DMA support

#### 4.5.5.3 Real-Time Clock (RTC)

- 32-bit seconds counter with 32-bit alarm

- 16-bit prescaler with compensation

#### **Communication Interfaces**

- Register write protection

- Hard Lock requires MCU POR to enable write access

### 4.5.6 Communication Interfaces

### 4.5.6.1 Inter-Integrated Circuit (I<sup>2</sup>C)

- Compatible with I<sup>2</sup>C bus standard and SMBus Specification Version 2 features

- •Up to 400 kbit/s with maximum bus loading

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Programmable slave address and glitch input filter

- Interrupt or DMA driven byte-by-byte data transfer

- · Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Bus busy detection broadcast and 10-bit address extension

- · Address matching causes wake-up when processor is in low power mode

### 4.5.6.2 UART0

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit baud rate selection with fractional divide of 32

- Programmable 8-bit or 9-bit data format

- Separately enabled transmitter and receiver

- Programmable transmitter output polarity

- Programmable receive input polarity

- 13-bit break character option

- 11-bit break character detection option

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- · Address match feature in receiver to reduce address mark wakeup ISR overhead

- Interrupt or DMA driven operation

- Receiver framing error detection

- Hardware parity generation and checking

- Configurable oversampling ratio to support from 1/4 to 1/32 bit-time noise detection

- Operation in low power modes

### 4.5.6.3 Serial Peripheral Interface (SPI)

- Master and slave mode

- Full-duplex, three-wire synchronous transfers

- Programmable transmit bit rate

- Double-buffered transmit and receive data registers

- Serial clock phase and polarity options

- · Slave select output

- Mode fault error flag with CPU interrupt capability

- Control of SPI operation during wait mode

- Selectable MSB-first or LSB-first shifting

- Support for both transmit and receive by DMA

### 4.5.7 Human Machine Interface

#### 4.5.7.1 General Purpose Input/Output (GPIO)

- Hysteresis and configurable pull up device on all input pins

- Configurable drive strength on some output pins

- Independent pin value register to read logic level on digital pin

### 4.5.7.2 Touch Sensor Input (TSI)

- Support up to 16 external electrodes

- · Automatic detection of electrode capacitance across all operational power modes

- Internal reference oscillator for high-accuracy measurement

- Configurable software or hardware scan trigger

- Fully support Freescale touch sensing software (TSS) library

- Capability to wake MCU from low power modes

- · Compensate for temperature and supply voltage variations

- High sensitivity change with 16-bit resolution register

- Configurable up to 4096 scan times.

- Support DMA data transfer

### 5 Power modes

The power management controller (PMC) provides multiple power options to allow the user to optimize power consumption for the level of functionality needed.

Depending on the stop requirements of the user application, a variety of stop modes are available that provide state retention, partial power down or full power down of certain logic and/or memory. I/O states are held in all modes of operation. The following table compares the various power modes available.

For each run mode there is a corresponding wait and stop mode. Wait modes are similar to ARM sleep modes. Stop modes (VLPS, STOP) are similar to ARM sleep deep mode. The very low power run (VLPR) operating mode can drastically reduce runtime power when the maximum bus frequency is not required to handle the application needs.

The three primary modes of operation are run, wait and stop. The WFI instruction invokes both wait and stop modes for the chip. The primary modes are augmented in a number of ways to provide lower power based on application needs.

| Chip mode                | Description                                                                                                                                                                                          | Core mode  | Normal<br>recovery<br>method |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------|

| Normal run               | Allows maximum performance of chip. Default mode out of reset; on-<br>chip voltage regulator is on.                                                                                                  | Run        | —                            |

| Normal Wait -<br>via WFI | Allows peripherals to function while the core is in sleep mode, reducing power. NVIC remains sensitive to interrupts; peripherals continue to be clocked.                                            | Sleep      | Interrupt                    |

| Normal Stop -<br>via WFI | Places chip in static state. Lowest power mode that retains all registers while maintaining LVD protection. NVIC is disabled; AWIC is used to wake up from interrupt; peripheral clocks are stopped. | Sleep Deep | Interrupt                    |

Table 5.

Chip power modes

Table continues on the next page ...

| Chip mode                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Core mode  | Normal                           |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | recovery<br>method               |

| VLPR (Very Low<br>Power Run)              | On-chip voltage regulator is in a low power mode that supplies only<br>enough power to run the chip at a reduced frequency. Reduced<br>frequency Flash access mode (1 MHz); LVD off; in BLPI clock mode,<br>the fast internal reference oscillator is available to provide a low power<br>nominal 4MHz source for the core with the nominal bus and flash clock<br>required to be <800kHz; alternatively, BLPE clock mode can be used<br>with an external clock or the crystal oscillator providing the clock<br>source.                            | Run        |                                  |

| VLPW (Very<br>Low Power<br>Wait) -via WFI | Same as VLPR but with the core in sleep mode to further reduce<br>power; NVIC remains sensitive to interrupts (FCLK = ON). On-chip<br>voltage regulator is in a low power mode that supplies only enough<br>power to run the chip at a reduced frequency.                                                                                                                                                                                                                                                                                           | Sleep      | Interrupt                        |

| VLPS (Very Low<br>Power Stop)-via<br>WFI  | Places chip in static state with LVD operation off. Lowest power mode<br>with ADC and pin interrupts functional. Peripheral clocks are stopped,<br>but OSC, LPTMR, RTC, CMP, TSI can be used. TPM and UART can<br>optionally be enabled if their clock source is enabled. NVIC is disabled<br>(FCLK = OFF); AWIC is used to wake up from interrupt. On-chip<br>voltage regulator is in a low power mode that supplies only enough<br>power to run the chip at a reduced frequency. All SRAM is operating<br>(content retained and I/O states held). | Sleep Deep | Interrupt                        |

| LLS (Low<br>Leakage Stop)                 | <ul> <li>State retention power mode. Most peripherals are in state retention mode (with clocks stopped), but OSC, LLWU, LPTMR, RTC, CMP,, TSI can be used. NVIC is disabled; LLWU is used to wake up.</li> <li>NOTE: The LLWU interrupt must not be masked by the interrupt controller to avoid a scenario where the system does not fully exit stop mode on an LLS recovery.</li> <li>All SRAM is operating (content retained and I/O states held).</li> </ul>                                                                                     | Sleep Deep | Wakeup<br>Interrupt <sup>1</sup> |

| VLLS3 (Very<br>Low Leakage<br>Stop3)      | Most peripherals are disabled (with clocks stopped), but OSC, LLWU,<br>LPTMR, RTC, CMP, TSI can be used. NVIC is disabled; LLWU is used<br>to wake up.<br>SRAM_U and SRAM_L remain powered on (content retained and I/O<br>states held).                                                                                                                                                                                                                                                                                                            | Sleep Deep | Wakeup Reset <sup>2</sup>        |

| VLLS1 (Very<br>Low Leakage<br>Stop1)      | Most peripherals are disabled (with clocks stopped), but OSC, LLWU,<br>LPTMR, RTC, CMP, TSI can be used. NVIC is disabled; LLWU is used<br>to wake up.<br>All of SRAM_U and SRAM_L are powered off.                                                                                                                                                                                                                                                                                                                                                 | Sleep Deep | Wakeup Reset <sup>2</sup>        |

| VLLS0 (Very<br>Low Leakage<br>Stop 0)     | Most peripherals are disabled (with clocks stopped), but LLWU,<br>LPTMR, RTC, TSI can be used. NVIC is disabled; LLWU is used to<br>wake up.                                                                                                                                                                                                                                                                                                                                                                                                        | Sleep Deep | Wakeup Reset <sup>2</sup>        |

|                                           | All of SRAM_U and SRAM_L are powered off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                  |

|                                           | LPO disabled, optional POR brown-out detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                  |

| Table 5. | Chip po | ower modes | (continued) |

|----------|---------|------------|-------------|

|----------|---------|------------|-------------|

- 1. Resumes normal run mode operation by executing the LLWU interrupt service routine.

- 2. Follows the reset flow with the LLWU interrupt flag set for the NVIC.

### 6 Revision History

The following table provides a revision history for this document.

| Rev. No. | Date       | Substantial Changes                                                                                                |  |

|----------|------------|--------------------------------------------------------------------------------------------------------------------|--|

| 1        | 3/16/2012  | Initial publish                                                                                                    |  |

| 2        | 6/4/2012   | Updated Kinetis KL series of MCU portfolio diagram.                                                                |  |

|          |            | Updated KL04 family block diagram.                                                                                 |  |

|          |            | Updated ADC feature for KL04.                                                                                      |  |

|          |            | Updated KL0x family summary table.                                                                                 |  |

| 2.1      | 10/22/2012 | Updated the feature in the section of Inter-Integrated Circuit (I2C) to "Up to 400 kbps with maximum bus loading". |  |

Table 6. Revision history

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

$\label{eq:FreescaleTM} Freescale TM and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.$

© 2011–2012 Freescale Semiconductor, Inc.

Document Number: KL0xPB Rev. 2.1, 10/2012