#### Welcome to E-XFL.COM

### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500v2                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.0GHz                                                                 |

| Co-Processors/DSP               | Security; SEC                                                          |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 90°C (TA)                                                        |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8533evjaqga |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                  | Characteristic                                                                         | Symbol                               | Max Value                                                            | Unit | Notes |

|--------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------|------|-------|

| DDR and DDR2                                     | DRAM I/O voltage                                                                       | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                         | V    | —     |

| Three-speed Ethernet I/O, MII management voltage |                                                                                        | LV <sub>DD</sub> (eTSEC1)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

|                                                  |                                                                                        | TV <sub>DD</sub> (eTSEC3)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

| PCI, DUART, sy<br>JTAG I/O voltage               | stem control and power management, I <sup>2</sup> C, and e                             | OV <sub>DD</sub>                     | -0.3 to 3.63                                                         | V    | —     |

| Local bus I/O vo                                 | Itage                                                                                  | BV <sub>DD</sub>                     | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | _     |

| Input voltage                                    | DDR/DDR2 DRAM signals                                                                  | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                                  | DDR/DDR2 DRAM reference                                                                | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                                  | Three-speed Ethernet signals                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub> | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 2     |

|                                                  | Local bus signals                                                                      | BV <sub>IN</sub>                     | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | V    | —     |

|                                                  | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                     | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                                  | PCI                                                                                    | OV <sub>IN</sub>                     | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

| Storage tempera                                  | ature range                                                                            | T <sub>STG</sub>                     | -55 to 150                                                           | °C   | -     |

### Table 1. Absolute Maximum Ratings<sup>1</sup> (continued)

### Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause.

2. (M,L,O)V<sub>IN</sub>, and MV<sub>RFF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Table 2. Recommended Operation | erating Conditions |

|--------------------------------|--------------------|

|--------------------------------|--------------------|

| Characteristic                            | Symbol           | Recommended<br>Value            | Unit | Notes |

|-------------------------------------------|------------------|---------------------------------|------|-------|

| Core supply voltage                       | V <sub>DD</sub>  | 1.0 ± 50 mV                     | V    | —     |

| PLL supply voltage                        | AV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | 1     |

| Core power supply for SerDes transceivers | SV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| Pad power supply for SerDes transceivers  | XV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| DDR and DDR2 DRAM I/O voltage             | GV <sub>DD</sub> | 2.5 V ± 125 mV<br>1.8 V ± 90 mV | V    | 2     |

Electrical Characteristics

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |

|                                       | 45 (default)<br>45 (default)<br>125     | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                                                         | 2     |

|                                       | 42 (default)                            |                                                                                  |       |

| DDR signal                            | 20                                      | GV <sub>DD</sub> = 2.5 V                                                         | —     |

| DDR2 signal                           | 16<br>32 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | —     |

| TSEC signals                          | 42                                      | LV <sub>DD</sub> = 2.5/3.3 V                                                     | —     |

| DUART, system control, JTAG           | 42                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |

| I <sup>2</sup> C                      | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |

### Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

# 2.2 Power Sequencing

The device requires its power rails to be applied in specific sequence in order to ensure proper device operation. These requirements are as follows for power up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, SV<sub>DD</sub>, OV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2. GV<sub>DD</sub>

Note that all supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power up, then the sequencing for  $GV_{DD}$  is not required.

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

### DDR and DDR2 SDRAM

### Table 16 provides the input AC timing specifications for the DDR SDRAM when $GV_{DD}(typ) = 2.5 V$ .

### Table 16. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | _     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _                        | V    | —     |

Table 17 provides the input AC timing specifications for the DDR SDRAM interface.

### Table 17. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions.

| Parameter                             | Symbol              | Min  | Мах | Unit | Notes |

|---------------------------------------|---------------------|------|-----|------|-------|

| Controller skew for MDQS—MDQ/MECC/MDM | t <sub>CISKEW</sub> |      |     | ps   | 1, 2  |

| 533 MHz                               |                     | -300 | 300 |      | 3     |

| 400 MHz                               |                     | -365 | 365 |      | —     |

| 333 MHz                               |                     | -390 | 390 |      | _     |

### Notes:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that will be captured with MDQS[n]. This should be subtracted from the total timing budget.

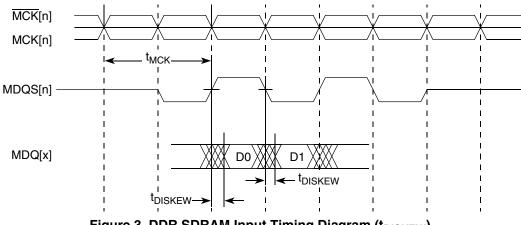

- 2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called  $t_{DISKEW}$ . This can be determined by the following equation:  $t_{DISKEW} = \pm (T/4 abs(t_{CISKEW}))$ , where T is the clock period and  $abs(t_{CISKEW})$  is the absolute value of  $t_{CISKEW}$ . See Figure 3.

- 3. Maximum DDR1 frequency is 400 MHz.

Figure 3 shows the DDR SDRAM input timing diagram.

Figure 3. DDR SDRAM Input Timing Diagram (t<sub>DISKEW</sub>)

DDR and DDR2 SDRAM

# 6.2.2 DDR SDRAM Output AC Timing Specifications

Table 18 provides the output AC timing specifications for the DDR SDRAM interface.

### Table 18. DDR SDRAM Output AC Timing Specifications

At recommended operating conditions.

| Parameter                                      | Symbol <sup>1</sup>                         | Min                  | Max  | Unit | Notes  |

|------------------------------------------------|---------------------------------------------|----------------------|------|------|--------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing      | t <sub>MCK</sub>                            | 3.75                 | 6    | ns   | 2      |

| ADDR/CMD output setup with respect to MCK      | t <sub>DDKHAS</sub>                         |                      |      | ns   | 3      |

| 533 MHz<br>400 MHz<br>333 MHz                  |                                             | 1.48<br>1.95<br>2.40 | <br> |      | 7      |

| ADDR/CMD output hold with respect to MCK       | t <sub>DDKHAX</sub>                         |                      |      | ns   | 3      |

| 533 MHz<br>400 MHz<br>333 MHz                  |                                             | 1.48<br>1.95<br>2.40 |      |      | 7<br>  |

| MCS[n] output setup with respect to MCK        | t <sub>DDKHCS</sub>                         |                      |      | ns   | 3      |

| 533 MHz<br>400 MHz<br>333 MHz                  |                                             | 1.48<br>1.95<br>2.40 |      |      | 7<br>  |

| MCS[n] output hold with respect to MCK         | t <sub>DDKHCX</sub>                         |                      |      | ns   | 3      |

| 533 MHz<br>400 MHz<br>333 MHz                  |                                             | 1.48<br>1.95<br>2.40 | <br> |      | 7<br>  |

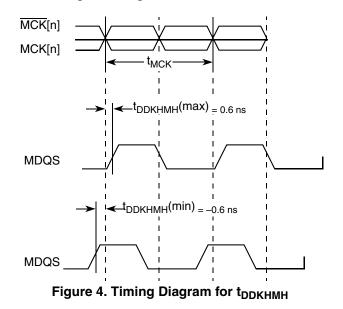

| MCK to MDQS Skew                               | t <sub>DDKHMH</sub>                         | -0.6                 | 0.6  | ns   | 4      |

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS,</sub><br>t <sub>DDKLDS</sub> |                      |      | ps   | 5      |

| 533 MHz<br>400 MHz<br>333 MHz                  |                                             | 538<br>700<br>900    |      |      | 7<br>  |

| MDQ/MECC/MDM output hold with respect to MDQS  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> |                      |      | ps   | 5      |

| 533 MHz<br>400 MHz<br>333 MHz                  |                                             | 538<br>700<br>900    | <br> |      | 7<br>— |

| MDQS preamble                                  | t <sub>DDKHMP</sub>                         | 0.75 x tMCK          | -    | ns   | 6      |

### Table 18. DDR SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions.

| Parameter      | Symbol <sup>1</sup> | Min        | Мах        | Unit | Notes |

|----------------|---------------------|------------|------------|------|-------|

| MDQS postamble | t <sub>DDKHME</sub> | 0.4 x tMCK | 0.6 x tMCK | ns   | 6     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/ $\overline{MCK}$  referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the MPC8533E PowerQUICC III Integrated Communications Processor Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- 5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

- 7. Maximum DDR1 frequency is 400 MHz.

### NOTE

For the ADDR/CMD setup and hold specifications in Table 18, it is assumed that the clock control register is set to adjust the memory clocks by  $\frac{1}{2}$  applied cycle.

Figure 4 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

### Table 40. Local Bus General Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled (continued)

| Parameter                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> | —   | 2.5 | ns   | 5     |

Notes:

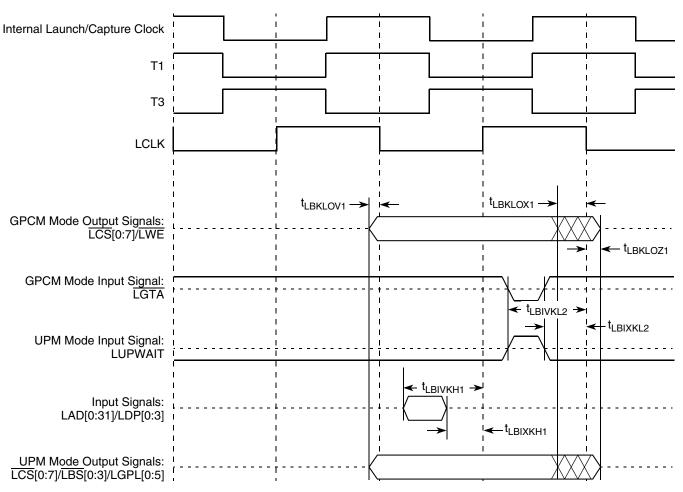

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

### Table 41 describes the general timing parameters of the local bus interface at $BV_{DD} = 2.5$ V.

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Мах | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | _     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | —   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.4 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.8 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>lbotot</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                | —   | 2.8 | ns   |       |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | —   | 2.8 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | —   | 2.8 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | —   | 2.8 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.8 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.8 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

### Table 41. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Bypass Mode)

# 12 JTAG

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8533E.

# 12.1 JTAG DC Electrical Characteristics

Table 44 provides the DC electrical characteristics for the JTAG interface.

### Table 44. JTAG DC Electrical Characteristics

| Parameter                                                                      | Symbol          | Min  | Мах                    | Unit | Notes |

|--------------------------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                                       | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage                                                        | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current (OV <sub>IN</sub> = 0 V or OV <sub>IN</sub> = OV <sub>DD</sub> ) | I <sub>IN</sub> | —    | ±5                     | μA   | 1     |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )                  | V <sub>OH</sub> | 2.4  | _                      | V    | —     |

| Low-level output voltage (OV <sub>DD</sub> = min, $I_{OL}$ = 2 mA)             | V <sub>OL</sub> | —    | 0.4                    | V    | —     |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$ .

# **12.2 JTAG AC Electrical Specifications**

Table 45 provides the JTAG AC timing specifications as defined in Figure 30 through Figure 33.

### Table 45. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 3).

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | —        | ns   | —     |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | —     |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | —        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 20<br>25 | _        | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO            | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 4<br>4   | 20<br>25 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2.5<br>4 |          | ns   | 5     |

### **High-Speed Serial Interfaces (HSSI)**

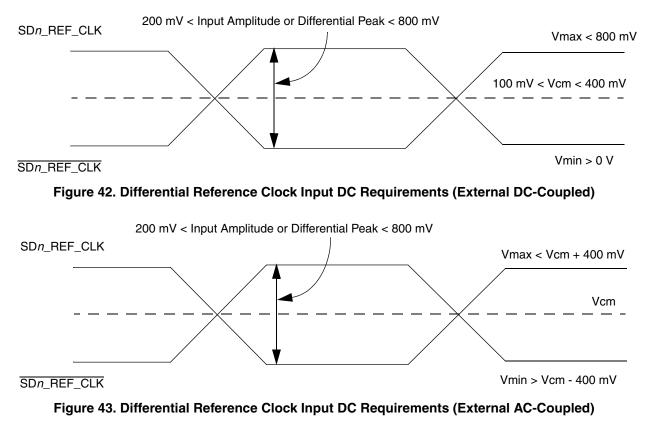

- For external DC-coupled connection, as described in Section 16.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV.

Figure 42 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 43 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended Mode

- The reference clock can also be single-ended. The SDn\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-peak (from Vmin to Vmax) with SDn\_REF\_CLK either left unconnected or tied to ground.

- The SDn\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 44 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

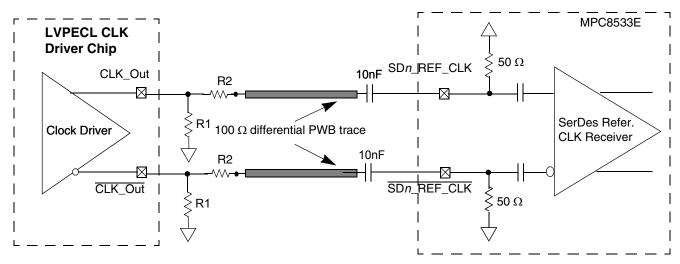

assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8533E SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock driver clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 47. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

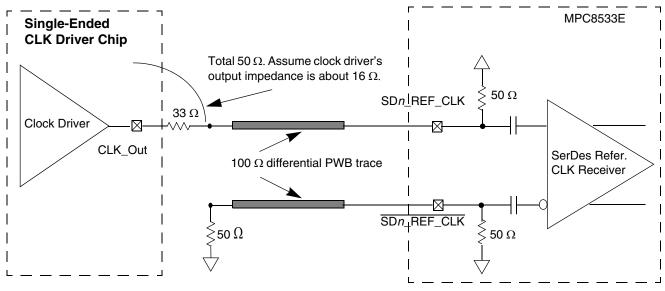

Figure 48 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8533E SerDes reference clock input's DC requirement.

Figure 48. Single-Ended Connection (Reference Only)

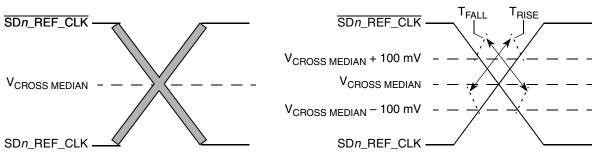

Figure 50. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. Refer to the following sections for detailed information:

• Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

### 16.2.4.1 Spread Spectrum Clock

SD1\_REF\_CLK/SD1\_REF\_CLK were designed to work with a spread spectrum clock (+0 to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation should be used.

SD2\_REF\_CLK/SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

# 16.3 SerDes Transmitter and Receiver Reference Circuits

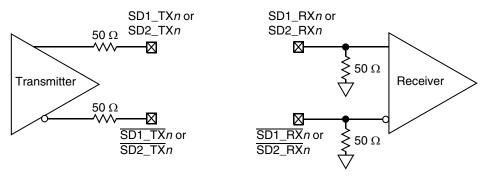

Figure 51 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 51. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in the section below (PCI Express) in this document based on the application usage:

• Section 17, "PCI Express"

Please note that external AC Coupling capacitor is required for the above serial transmission protocols with the capacitor value defined in specification of each protocol section.

PCI Express

# 17 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8533E.

# 17.1 DC Requirements for PCI Express SD\_REF\_CLK and SD\_REF\_CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

# **17.2 AC Requirements for PCI Express SerDes Clocks**

Table 53 provides the AC requirements for the PCI Express SerDes clocks.

| Symbol <sup>2</sup> | Parameter Description                                                                    | Min | Тур | Max | Units | Notes |

|---------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-------|-------|

| t <sub>REF</sub>    | REFCLK cycle time                                                                        | _   | 10  | —   | ns    | 1     |

| t <sub>REFCJ</sub>  | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _   | 100 | ps    |       |

| t <sub>REFPJ</sub>  | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _   | 50  | ps    | —     |

Table 53. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

Notes:

1. Typical based on PCI Express Specification 2.0.

2. Guaranteed by characterization.

# 17.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm$ 300 ppm tolerance.

# 17.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer please refer to the *PCI Express Base Specification. Rev. 1.0a.*

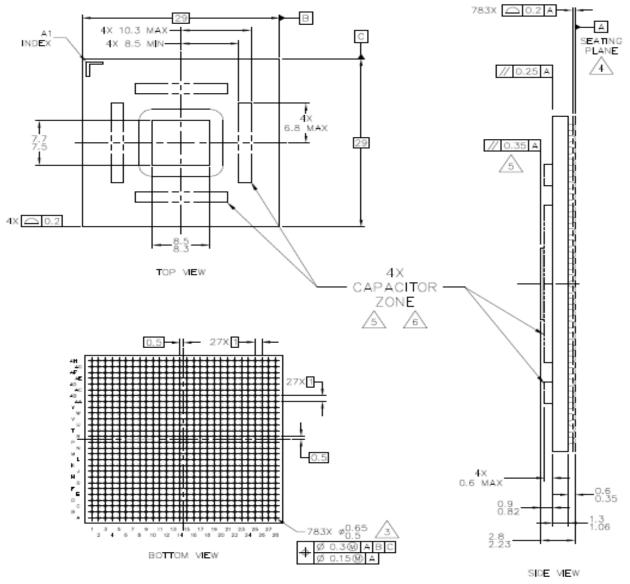

## 18.2 Mechanical Dimensions of the MPC8533E FC-PBGA

Figure 55 shows the mechanical dimensions and bottom surface nomenclature of the MPC8533E, 783 FC-PBGA package without a lid.

### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. Capacitors may not be present on all parts. Care must be taken not to short exposed metal capacitor pads.

- 7. All dimensions are symmetric across the package center lines, unless dimensioned otherwise.

### Figure 55. Mechanical Dimensions and Bottom Surface Nomenclature of the MPC8533E FC-PBGA without a Lid

Package Description

# 18.3 Pinout Listings

Table 57 provides the pinout listing for the MPC8533E 783 FC-PBGA package.

### NOTE

The naming convention of TSEC1 and TSEC3 is used to allow the splitting voltage rails for the eTSEC blocks and to ease the port of existing PowerQUICC III software.

### NOTE

The DMA\_DACK[0:1] and TEST\_SEL pins must be set to a proper state during POR configuration. Please refer to Table 57 for more details.

| Signal         | Package Pin Number                                                                                                                                                                                 | Pin Type | Power<br>Supply  | Notes    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                | PCI                                                                                                                                                                                                |          |                  |          |

| PCI1_AD[31:0]  | AE8, AD8, AF8, AH12, AG12, AB9, AC9, AE9,<br>AD10, AE10, AC11, AB11, AB12, AC12, AF12,<br>AE11, Y14, AE15, AC15, AB15, AA15, AD16,<br>Y15, AB16, AF18, AE18, AC17, AE19, AD19,<br>AB17, AB18, AA16 | I/O      | OV <sub>DD</sub> | -        |

| PCI1_C_BE[3:0] | AC10, AE12, AA14, AD17                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

| PCI1_GNT[4:1]  | AE7, AG11,AH11, AC8                                                                                                                                                                                | 0        | OV <sub>DD</sub> | 4, 8, 24 |

| PCI1_GNT0      | AE6                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | _        |

| PCI1_IRDY      | AF13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR       | AB14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | _        |

| PCI1_PERR      | AE14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR      | AC14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_STOP      | AA13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY      | AD13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]  | AF9, AG10, AH10, AD6                                                                                                                                                                               | ļ        | OV <sub>DD</sub> | —        |

| PCI1_REQ0      | AB8                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK       | AH26                                                                                                                                                                                               | I        | OV <sub>DD</sub> | —        |

| PCI1_DEVSEL    | AC13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME     | AD12                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL     | AG6                                                                                                                                                                                                | I        | OV <sub>DD</sub> | —        |

### Table 57. MPC8533E Pinout Listing

### Table 57. MPC8533E Pinout Listing (continued)

| Signal                     | Package Pin Number                             | Pin Type | Power<br>Supply  | Notes           |

|----------------------------|------------------------------------------------|----------|------------------|-----------------|

| SD2_REF_CLK                | AF2                                            | I        | XV <sub>DD</sub> | _               |

| SD2_TST_CLK                | AG4                                            | _        | _                | -               |

| SD2_TST_CLK                | AF4                                            | _        | —                | —               |

|                            | General-Purpose Output                         |          | •                | •               |

| GPOUT[0:7]                 | AF22, AH23, AG27, AH25, AF21, AF25, AG26, AF26 | 0        | OV <sub>DD</sub> | _               |

|                            | General-Purpose Input                          |          | 1                |                 |

| GPIN[0:7]                  | AH24, AG24, AD23, AE21, AD22, AF23, AG25, AE20 | I        | OV <sub>DD</sub> | _               |

|                            | System Control                                 |          |                  |                 |

| HRESET                     | AG16                                           | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ                 | AG15                                           | 0        | OV <sub>DD</sub> | 21              |

| SRESET                     | AG19                                           | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN                   | AH5                                            | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT                  | AA12                                           | 0        | OV <sub>DD</sub> | 2, 4            |

|                            | Debug                                          |          | •                | •               |

| TRIG_IN                    | AC5                                            | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/<br>QUIESCE | AB5                                            | 0        | OV <sub>DD</sub> | 5, 8, 15,<br>21 |

| MSRCID[0:1]                | Y7, W9                                         | 0        | OV <sub>DD</sub> | 4, 5, 8         |

| MSRCID[2:4]                | AA9, AB6, AD5                                  | 0        | OV <sub>DD</sub> | 5, 15, 21       |

| MDVAL                      | Y8                                             | 0        | OV <sub>DD</sub> | 5               |

| CLK_OUT                    | AE16                                           | 0        | OV <sub>DD</sub> | 10              |

|                            | Clock                                          |          | ·                | ·               |

| RTC                        | AF15                                           | I        | OV <sub>DD</sub> | —               |

| SYSCLK                     | AH16                                           | I        | OV <sub>DD</sub> | —               |

|                            | JTAG                                           |          |                  |                 |

| тск                        | AG28                                           | I        | OV <sub>DD</sub> | —               |

| TDI                        | AH28                                           | I        | OV <sub>DD</sub> | 11              |

| TDO                        | AF28                                           | 0        | OV <sub>DD</sub> | 10              |

| TMS                        | AH27                                           | I        | OV <sub>DD</sub> | 11              |

| TRST                       | AH22                                           | I        | OV <sub>DD</sub> | 11              |

Clocking

# 19 Clocking

This section describes the PLL configuration of the MPC8533E. Note that the platform clock is identical to the core complex bus (CCB) clock.

# 19.1 Clock Ranges

Table 58 provides the clocking specifications for the processor cores and Table 59 provides the clocking specifications for the memory bus.

|                               | Maximum Processor Core Frequency |     |     |     |      |      |      |      |      |       |

|-------------------------------|----------------------------------|-----|-----|-----|------|------|------|------|------|-------|

| Characteristic                | 667                              | MHz | 800 | MHz | 1000 | MHz  | 1067 | MHz  | Unit | Notes |

|                               | Min                              | Max | Min | Max | Min  | Max  | Min  | Max  |      |       |

| e500 core processor frequency | 667                              | 667 | 667 | 800 | 667  | 1000 | 667  | 1067 | MHz  | 1, 2  |

Table 58. Processor Core Clocking Specifications

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

2. The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

### Table 59. Memory Bus Clocking Specifications

| Characteristic         | Maximum Pro              | Unit | Notes |      |

|------------------------|--------------------------|------|-------|------|

|                        | 667, 800, 1000, 1067 MHz |      |       |      |

|                        | Min                      | Max  |       |      |

| Memory bus clock speed | 166                      | 266  | MHz   | 1, 2 |

Notes:

- 1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

# 19.2 CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency of the CCB is set using the following reset signals (see Table 60):

- SYSCLK input signal

- Binary value on LA[28:31] at power up

Note that there is no default for this PLL ratio; these signals must be pulled to the desired values. Also note that the DDR data rate is the determining factor in selecting the CCB bus frequency, since the CCB frequency must equal the DDR data rate.

| Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio | Binary Value of<br>LA[28:31] Signals | CCB:SYSCLK Ratio |

|-----------------------------------|------------------|--------------------------------------|------------------|

| 0000                              | 16:1             | 1000                                 | 8:1              |

| 0001                              | Reserved         | 1001                                 | 9:1              |

| 0010                              | Reserved         | 1010                                 | 10:1             |

| 0011                              | 3:1              | 1011                                 | Reserved         |

| 0100                              | 4:1              | 1100                                 | 12:1             |

| 0101                              | 5:1              | 1101                                 | Reserved         |

| 0110                              | 6:1              | 1110                                 | Reserved         |

| 0111                              | Reserved         | 1111                                 | Reserved         |

| Table | 60. | ССВ | Clock | Ratio |

|-------|-----|-----|-------|-------|

|       | ••• |     |       |       |

# 19.3 e500 Core PLL Ratio

Table 61 describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE, and LGPL2 at power up, as shown in Table 61.

| Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio | Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio |

|--------------------------------------------------|---------------------------|--------------------------------------------------|---------------------------|

| 000                                              | 4:1                       | 100                                              | 2:1                       |

| 001                                              | Reserved                  | 101                                              | 5:2                       |

| 010                                              | Reserved                  | 110                                              | 3:1                       |

| 011                                              | 3:2                       | 111                                              | 7:2                       |

# 19.4 PCI Clocks

For specifications on the PCI\_CLK, refer to the PCI 2.2 Local Bus Specifications.

The use of PCI\_CLK is optional if SYSCLK is in the range of 33–66 MHz. If SYSCLK is outside this range then use of PCI\_CLK is required as a separate PCI clock source, asynchronous with respect to SYSCLK.

## 19.6.2 Platform to FIFO Restrictions

Please note the following FIFO maximum speed restrictions based on platform speed. Refer to Section 4.4, "Platform to FIFO Restrictions," for additional information.

| Platform Speed (MHz) | Maximum FIFO Speed for Reference Clocks TSEC <i>n</i> _TX_CLK, TSEC <i>n</i> _RX_CLK (MHz) <sup>1</sup> |

|----------------------|---------------------------------------------------------------------------------------------------------|

| 533                  | 126                                                                                                     |

| 400                  | 94                                                                                                      |

### **Table 64. FIFO Maximum Speed Restrictions**

Note:

1. FIFO speed should be less than 24% of the platform speed.

# 20 Thermal

This section describes the thermal specifications of the MPC8533E.

# 20.1 Thermal Characteristics

Table 65 provides the package thermal characteristics.

Table 65. Package Thermal Characteristics

| Characteristic                         | JEDEC Board             | Symbol                | Value | Unit | Notes |

|----------------------------------------|-------------------------|-----------------------|-------|------|-------|

| Junction-to-ambient natural convection | Single layer board (1s) | $R_{	hetaJA}$         | 26    | °C/W | 1, 2  |

| Junction-to-ambient natural convection | Four layer board (2s2p) | $R_{\thetaJA}$        | 21    | °C/W | 1, 2  |

| Junction-to-ambient (@200 ft/min)      | Single layer board (1s) | $R_{\thetaJA}$        | 21    | °C/W | 1, 2  |

| Junction-to-ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{\thetaJA}$        | 17    | °C/W | 1, 2  |

| Junction-to-board thermal              | —                       | $R_{\theta JB}$       | 12    | °C/W | 3     |

| Junction-to-case thermal               |                         | $R_{	extsf{	heta}JC}$ | <0.1  | °C/W | 4     |

### Notes:

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

2. Per JEDEC JESD51-2 and JESD51-6 with the board (JESD51-9) horizontal.

3. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

4. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. Actual thermal resistance is less than 0.1°C/W.

### System Design Information

Note the following:

- AV<sub>DD</sub> SRDS should be a filtered version of SV<sub>DD</sub>.

- Signals on the SerDes interface are fed from the XV<sub>DD</sub> power plane.

# 21.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8533E system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$ ; and GND power planes in the PCB, utilizing short low impedance traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers should work directly with their power regulator vendor for best values and types and quantity of bulk capacitors.

# 21.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power ( $SV_{DD}$  and  $XV_{DD}$ ) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only surface mount technology (SMT) capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to further reduce inductance.

- First, the board should have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors should be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors should be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there should be a  $1-\mu F$  ceramic chip capacitor on each side of the device. This should be done for all SerDes supplies.

- Third, between the device and any SerDes voltage regulator there should be a 10-µF, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a 100-µF, low ESR SMT tantalum chip capacitor. This should be done for all SerDes supplies.

Device Nomenclature

# 22.2 Nomenclature of Parts Fully Addressed by this Document

Table 70 provides the Freescale part numbering nomenclature for the MPC8533E.

### Table 70. Device Nomenclature

| MPC             | nnnn               | E                                       | С                  | НХ                                                       | AA                                                             | X                                         | В                                         |

|-----------------|--------------------|-----------------------------------------|--------------------|----------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|-------------------------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature Range  | Package <sup>1</sup>                                     | Processor<br>Frequency <sup>2</sup>                            | Platform<br>Frequency                     | Revision<br>Level                         |

| MPC             | 8533               | Blank = not<br>included<br>E = included | Blank = 0° to 90°C | VT = FC-PBGA<br>(lead-free)<br>VJ = lead-free<br>FC-PBGA | AL = 667 MHz<br>AN = 800 MHz<br>AQ = 1000 MHz<br>AR = 1067 MHz | F = 333 MHz<br>G = 400 MHz<br>J = 533 MHz | Blank = Rev.<br>1.1 1.1.1<br>A = Rev. 2.1 |

Notes:

- 1. See Section 18, "Package Description," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 3. The VT part number is ROHS-compliant, with the permitted exception of the C4 die bumps.

- 4. The VJ part number is entirely lead-free. This includes the C4 die bumps.

# 22.3 Part Marking

Parts are marked as in the example shown in Figure 66.

Notes:

MMMMM is the 5-digit mask number.

ATWLYYWW is the traceability code.

CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States.

### Figure 66. Part Marking for FC-PBGA Device