# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500v2                                                        |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.067GHz                                                              |

| Co-Processors/DSP               | Security; SEC                                                         |

| RAM Controllers                 | DDR, DDR2                                                             |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 90°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8533evtarj |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MPC8533E Overview

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and remote masters

- Extended DMA functions (advanced chaining and striding capability)

- Support for scatter and gather transfers

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control each DMA channel from external 3-pin interface

- Ability to launch DMA from single write transaction

- PCI controller

- PCI 2.2 compatible

- One 32-bit PCI port with support for speeds from 16 to 66 MHz

- Host and agent mode support

- 64-bit dual address cycle (DAC) support

- Supports PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses

- Supports posting of processor-to-PCI and PCI-to-memory writes

- PCI 3.3-V compatible

- Selectable hardware-enforced coherency

| Characteristic                                                                          |                                                                                        | Symbol                               | Max Value                                                            | Unit | Notes |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------|------|-------|

| DDR and DDR2                                                                            | DDR and DDR2 DRAM I/O voltage                                                          |                                      | -0.3 to 2.75<br>-0.3 to 1.98                                         | V    | —     |

| Three-speed Ethernet I/O, MII management voltage                                        |                                                                                        | LV <sub>DD</sub> (eTSEC1)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

|                                                                                         |                                                                                        | TV <sub>DD</sub> (eTSEC3)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

| PCI, DUART, system control and power management, I <sup>2</sup> C, and JTAG I/O voltage |                                                                                        | OV <sub>DD</sub>                     | -0.3 to 3.63                                                         | V    | —     |

| Local bus I/O vo                                                                        | Itage                                                                                  | BV <sub>DD</sub>                     | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | —     |

| Input voltage                                                                           | DDR/DDR2 DRAM signals                                                                  | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                                                                         | DDR/DDR2 DRAM reference                                                                | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                                                                         | Three-speed Ethernet signals                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub> | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 2     |

|                                                                                         | Local bus signals                                                                      | BV <sub>IN</sub>                     | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | V    | —     |

|                                                                                         | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                     | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                                                                         | PCI                                                                                    | OV <sub>IN</sub>                     | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

| Storage tempera                                                                         | Storage temperature range                                                              |                                      | -55 to 150                                                           | °C   | -     |

### Table 1. Absolute Maximum Ratings<sup>1</sup> (continued)

#### Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause.

2. (M,L,O)V<sub>IN</sub>, and MV<sub>RFF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Table 2. Recommended Operation | erating Conditions |

|--------------------------------|--------------------|

|--------------------------------|--------------------|

| Characteristic                            | Symbol           | Recommended<br>Value            | Unit | Notes |

|-------------------------------------------|------------------|---------------------------------|------|-------|

| Core supply voltage                       | V <sub>DD</sub>  | 1.0 ± 50 mV                     | V    | —     |

| PLL supply voltage                        | AV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | 1     |

| Core power supply for SerDes transceivers | SV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| Pad power supply for SerDes transceivers  | XV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| DDR and DDR2 DRAM I/O voltage             | GV <sub>DD</sub> | 2.5 V ± 125 mV<br>1.8 V ± 90 mV | V    | 2     |

**Electrical Characteristics**

| Characteristic                                                                                 |                                                                                                        | Symbol                               | Recommended<br>Value                               | Unit | Notes |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Three-speed Ethernet I/O voltage                                                               |                                                                                                        | LV <sub>DD</sub><br>(eTSEC1)         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                                                                                |                                                                                                        | TV <sub>DD</sub><br>(eTSEC3)         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   |      |       |

| PCI, DUART, PCI Express, system control and power management, $\rm I^2C,$ and JTAG I/O voltage |                                                                                                        | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus I/O voltage                                                                          |                                                                                                        | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V    | 5     |

| Input voltage                                                                                  | DDR and DDR2 DRAM signals                                                                              | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                                                                                | DDR and DDR2 DRAM reference                                                                            | MV <sub>REF</sub>                    | GND to GV <sub>DD</sub> /2                         | V    | 2     |

|                                                                                                | Three-speed Ethernet signals                                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                                                                                | Local bus signals                                                                                      | BV <sub>IN</sub>                     | GND to BV <sub>DD</sub>                            | V    | 5     |

|                                                                                                | PCI, Local bus, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

| Junction temper                                                                                | ature range                                                                                            | Тj                                   | 0 to 90                                            | °C   | —     |

### Table 2. Recommended Operating Conditions (continued)

Notes:

1. This voltage is the input to the filter discussed in Section 21.2, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, which may be reduced from V<sub>DD</sub> by the filter.

2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

3. Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

4. **Caution:** T/LV<sub>IN</sub> must not exceed T/ LV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

5. Caution: BV<sub>IN</sub> must not exceed BV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

Electrical Characteristics

## 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |

|                                       | 45 (default)<br>45 (default)<br>125     | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                                                         | 2     |

|                                       | 42 (default)                            |                                                                                  |       |

| DDR signal                            | 20                                      | GV <sub>DD</sub> = 2.5 V                                                         | —     |

| DDR2 signal                           | 16<br>32 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | —     |

| TSEC signals                          | 42                                      | LV <sub>DD</sub> = 2.5/3.3 V                                                     | —     |

| DUART, system control, JTAG           | 42                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |

| I <sup>2</sup> C                      | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |

### Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

## 2.2 Power Sequencing

The device requires its power rails to be applied in specific sequence in order to ensure proper device operation. These requirements are as follows for power up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, SV<sub>DD</sub>, OV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2. GV<sub>DD</sub>

Note that all supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power up, then the sequencing for  $GV_{DD}$  is not required.

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

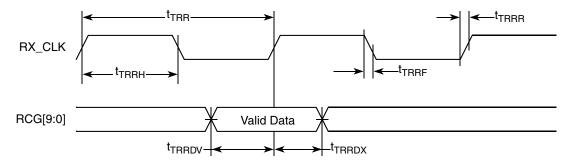

A summary of the single-clock TBI mode AC specifications for receive appears in Table 31.

### Table 31. TBI Single-Clock Mode Receive AC Timing Specification

| Parameter/Condition                       | Symbol             | Min | Тур | Max | Unit | Notes |

|-------------------------------------------|--------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                       | t <sub>TRR</sub>   | 7.5 | 8.0 | 8.5 | ns   | —     |

| RX_CLK duty cycle                         | t <sub>TRRH</sub>  | 40  | 50  | 60  | %    | —     |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>  | —   | —   | 250 | ps   |       |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>  | —   | —   | 1.0 | ns   |       |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>  | —   | —   | 1.0 | ns   |       |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDV</sub> | 2.0 | —   | —   | ns   |       |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDX</sub> | 1.0 | —   | —   | ns   | _     |

A timing diagram for TBI receive appears in Figure 17.

Figure 17. TBI Single-Clock Mode Receive AC Timing Diagram

## 8.5.4 RGMII and RTBI AC Timing Specifications

Table 32 presents the RGMII and RTBI AC timing specifications.

### Table 32. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit | Notes |

|--------------------------------------------|-------------------------------------|------|-----|------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGT_TX</sub>               | -500 | 0   | 500  | ps   | 5     |

| Data to clock input skew (at receiver)     | t <sub>SKRGT_RX</sub>               | 1.0  | —   | 2.8  | ns   | 2     |

| Clock period duration                      | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   | 3     |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    | 3, 4  |

| Rise time (20%–80%)                        | t <sub>RGTR</sub>                   | _    | —   | 0.75 | ns   | —     |

Enhanced Three-Speed Ethernet (eTSEC), MII Management

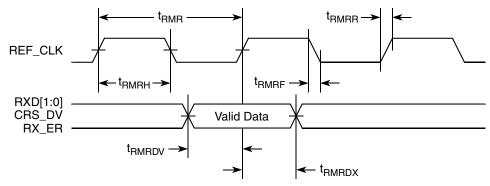

## 8.5.5.2 RMII Receive AC Timing Specifications

Table 34 shows the RMII receive AC timing specifications.

### Table 34. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.or 2.5 V  $\pm$  5%.

| Parameter/Condition                                          | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit | Notes |

|--------------------------------------------------------------|---------------------|------|------|------|------|-------|

| REF_CLK clock period                                         | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   | —     |

| REF_CLK duty cycle                                           | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    | _     |

| REF_CLK peak-to-peak jitter                                  | t <sub>RMRJ</sub>   | —    | —    | 250  | ps   | —     |

| Rise time REF_CLK (20%-80%)                                  | t <sub>RMRR</sub>   | 1.0  | —    | 2.0  | ns   | —     |

| Fall time REF_CLK (80%-20%)                                  | t <sub>RMRF</sub>   | 1.0  | —    | 2.0  | ns   | —     |

| RXD[1:0], CRS_DV, RX_ER setup time to<br>REF_CLK rising edge | t <sub>RMRDV</sub>  | 4.0  | _    | _    | ns   | —     |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge     | t <sub>RMRDX</sub>  | 2.0  | _    | _    | ns   | _     |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

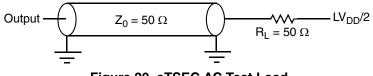

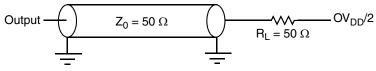

Figure 20 provides the AC test load for eTSEC.

Figure 20. eTSEC AC Test Load

Figure 21 shows the RMII receive AC timing diagram.

Figure 21. RMII Receive AC Timing Diagram

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 36. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V ± 5%.

| Parameter/Condition | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|---------------------|---------------------|-----|-----|-----|------|-------|

| MDC fall time       | t <sub>MDHF</sub>   | _   | —   | 10  | ns   | —     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- 2. This parameter is dependent on the platform clock frequency (MIIMCFG [MgmtClk] field determines the clock frequency of the MgmtClk Clock EC\_MDC).

- 3. This parameter is dependent on the platform clock frequency. The delay is equal to 16 platform clock periods ±3 ns. For example, with a platform clock of 333 MHz, the min/max delay is 48 ns ± 3 ns. Similarly, if the platform clock is 400 MHz, the min/max delay is 40 ns ± 3 ns).

- 4. t<sub>plb clk</sub> is the platform (CCB) clock.

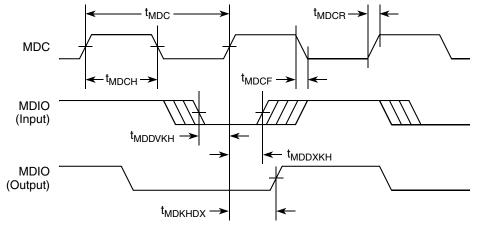

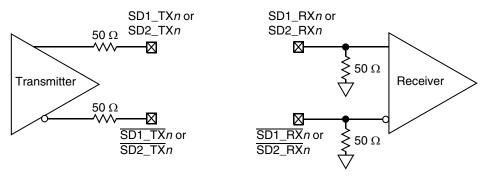

Figure 22 shows the MII management AC timing diagram.

Figure 22. MII Management Interface Timing Diagram

## 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8533E.

## **10.1 Local Bus DC Electrical Characteristics**

Table 37 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Table 37. Local Bus DC Electrical Characteristics (3.3 V DC) |  |  |  |  |  |

|--------------------------------------------------------------|--|--|--|--|--|

|                                                              |  |  |  |  |  |

| Parameter                                                                       | Symbol          | Min  | Мах                    | Unit | Notes |

|---------------------------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                                        | V <sub>IH</sub> | 2    | BV <sub>DD</sub> + 0.3 | V    | _     |

| Low-level input voltage                                                         | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current (BV <sub>IN</sub> = 0 V or BV <sub>IN</sub> = BOV <sub>DD</sub> ) | I <sub>IN</sub> | —    | ±5                     | μA   | 1     |

| High-level output voltage ( $BV_{DD} = min$ , $I_{OH} = -2 mA$ )                | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

| Low-level output voltage (BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)       | V <sub>OL</sub> | —    | 0.4                    | V    | _     |

### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

Table 38 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 38. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit | Notes |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                        | V <sub>IH</sub> | 1.70 | BV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.7                    | V    | —     |

| Input current ( $BV_{IN} = 0 V \text{ or } BV_{IN} = BV_{DD}$ ) | I <sub>IN</sub> | —    | ±15                    | μA   | 1     |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -1 mA$ )   | V <sub>OH</sub> | 2.0  | —                      | V    | —     |

| Low-level output voltage ( $BV_{DD} = min, I_{OL} = 1 mA$ )     | V <sub>OL</sub> | —    | 0.4                    | V    | —     |

### Note:

1. The symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

Table 39 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 1.8 \text{ V DC}$ .

### Table 39. Local Bus DC Electrical Characteristics (1.8 V DC)

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit | Notes |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                        | V <sub>IH</sub> | 1.3  | BV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.6                    | V    | _     |

| Input current ( $BV_{IN} = 0 V \text{ or } BV_{IN} = BV_{DD}$ ) | I <sub>IN</sub> | -    | ±15                    | μA   | 1     |

### Table 41. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled (continued)

| Parameter                                            | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to 0.4 ×  $BV_{DD}$  of the signal in question for 2.5-V signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

| Table 42 describes the general timing parameters of the local bus interface at $BV_{DD} = 1.8 \text{ V DC}$ . |

|---------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------|

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | —   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.6 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.9 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>LBOTOT</sub>                 | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                | _   | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.9 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

### Table 42. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)

#### Programmable Interrupt Controller

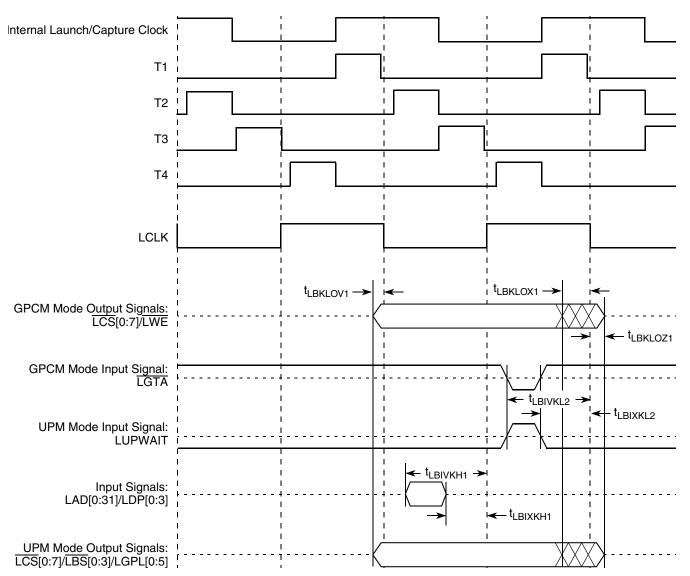

Figure 29. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

## **11 Programmable Interrupt Controller**

In IRQ edge trigger mode, when an external interrupt signal is asserted (according to the programmed polarity), it must remain the assertion for at least 3 system clocks (SYSCLK periods).

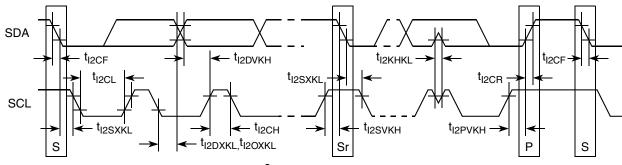

## Figure 34 provides the AC test load for the $I^2C$ .

Figure 34. I<sup>2</sup>C AC Test Load

Figure 35 shows the AC timing diagram for the  $I^2C$  bus.

Figure 35. I<sup>2</sup>C Bus AC Timing Diagram

## 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO interface of the MPC8533E.

## 14.1 GPIO DC Electrical Characteristics

Table 48 provides the DC electrical characteristics for the GPIO interface.

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit | Notes |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                        | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | _     |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.8                    | V    | _     |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = V_{DD}$ )    | I <sub>IN</sub> | —    | ±5                     | μA   | 1     |

| High-level output voltage ( $OV_{DD} = mn$ , $I_{OH} = -2 mA$ ) | V <sub>OH</sub> | 2.4  | —                      | V    | _     |

| Low-level output voltage ( $OV_{DD} = min$ , $I_{OL} = 2 mA$ )  | V <sub>OL</sub> | —    | 0.4                    | V    | _     |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

#### **High-Speed Serial Interfaces (HSSI)**

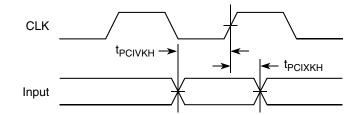

Figure 38 shows the PCI input AC timing conditions.

Figure 38. PCI Input AC Timing Measurement Conditions

Figure 39 shows the PCI output AC timing conditions.

Figure 39. PCI Output AC Timing Measurement Condition

## 16 High-Speed Serial Interfaces (HSSI)

The MPC8533E features two serializer/deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications.Both SerDes1 and SerDes2 can be used for PCI Express data transfers application.This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

## 16.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

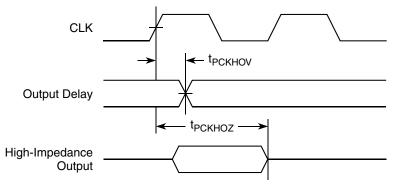

Figure 40 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD*n*\_TX and  $\overline{SDn}_T\overline{X}$ ) or a receiver input (SD*n*\_RX and  $\overline{SDn}_R\overline{X}$ ). Each signal swings between A Volts and B Volts where A > B.

Figure 50. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. Refer to the following sections for detailed information:

• Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

### 16.2.4.1 Spread Spectrum Clock

SD1\_REF\_CLK/SD1\_REF\_CLK were designed to work with a spread spectrum clock (+0 to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation should be used.

SD2\_REF\_CLK/SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

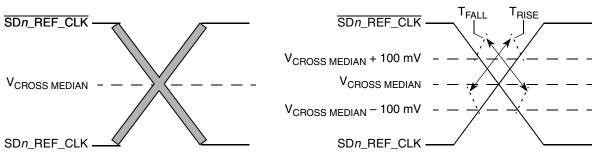

## 16.3 SerDes Transmitter and Receiver Reference Circuits

Figure 51 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 51. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in the section below (PCI Express) in this document based on the application usage:

• Section 17, "PCI Express"

Please note that external AC Coupling capacitor is required for the above serial transmission protocols with the capacitor value defined in specification of each protocol section.

Package Description

## 18.3 Pinout Listings

Table 57 provides the pinout listing for the MPC8533E 783 FC-PBGA package.

### NOTE

The naming convention of TSEC1 and TSEC3 is used to allow the splitting voltage rails for the eTSEC blocks and to ease the port of existing PowerQUICC III software.

### NOTE

The DMA\_DACK[0:1] and TEST\_SEL pins must be set to a proper state during POR configuration. Please refer to Table 57 for more details.

| Signal         | Package Pin Number                                                                                                                                                                                 | Pin Type | Power<br>Supply  | Notes    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                | PCI                                                                                                                                                                                                |          |                  |          |

| PCI1_AD[31:0]  | AE8, AD8, AF8, AH12, AG12, AB9, AC9, AE9,<br>AD10, AE10, AC11, AB11, AB12, AC12, AF12,<br>AE11, Y14, AE15, AC15, AB15, AA15, AD16,<br>Y15, AB16, AF18, AE18, AC17, AE19, AD19,<br>AB17, AB18, AA16 | I/O      | OV <sub>DD</sub> | -        |

| PCI1_C_BE[3:0] | AC10, AE12, AA14, AD17                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

| PCI1_GNT[4:1]  | AE7, AG11,AH11, AC8                                                                                                                                                                                | 0        | OV <sub>DD</sub> | 4, 8, 24 |

| PCI1_GNT0      | AE6                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | _        |

| PCI1_IRDY      | AF13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR       | AB14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | _        |

| PCI1_PERR      | AE14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR      | AC14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_STOP      | AA13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY      | AD13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]  | AF9, AG10, AH10, AD6                                                                                                                                                                               | ļ        | OV <sub>DD</sub> | —        |

| PCI1_REQ0      | AB8                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK       | AH26                                                                                                                                                                                               | I        | OV <sub>DD</sub> | —        |

| PCI1_DEVSEL    | AC13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME     | AD12                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL     | AG6                                                                                                                                                                                                | I        | OV <sub>DD</sub> | —        |

### Table 57. MPC8533E Pinout Listing

### Table 57. MPC8533E Pinout Listing (continued)

| Signal         | Package Pin Number                   | Pin Type         | Power<br>Supply  | Notes    |

|----------------|--------------------------------------|------------------|------------------|----------|

|                | Ethernet Management Inter            | rface            |                  |          |

| EC_MDC         | AC7                                  | 0                | OV <sub>DD</sub> | 4, 8, 14 |

| EC_MDIO        | Y9                                   | I/O              | OV <sub>DD</sub> | —        |

|                | Gigabit Reference Cloc               | k                |                  |          |

| EC_GTX_CLK125  | T2                                   | I                | LV <sub>DD</sub> | —        |

|                | Three-Speed Ethernet Controller (Gig | abit Ethernet 1) |                  |          |

| TSEC1_RXD[7:0] | U10, U9, T10, T9, U8, T8, T7, T6     | I                | LV <sub>DD</sub> | —        |

| TSEC1_TXD[7:0] | T5, U5, V5, V3, V2, V1, U2, U1       | 0                | LV <sub>DD</sub> | 4, 8, 14 |

| TSEC1_COL      | R5                                   | I                | LV <sub>DD</sub> | —        |

| TSEC1_CRS      | T4                                   | I/O              | LV <sub>DD</sub> | 16       |

| TSEC1_GTX_CLK  | T1                                   | 0                | LV <sub>DD</sub> | —        |

| TSEC1_RX_CLK   | V7                                   | I                | LV <sub>DD</sub> | —        |

| TSEC1_RX_DV    | U7                                   | I                | LV <sub>DD</sub> | _        |

| TSEC1_RX_ER    | R9                                   | I                | LV <sub>DD</sub> | 4, 8     |

| TSEC1_TX_CLK   | V6                                   | I                | LV <sub>DD</sub> | _        |

| TSEC1_TX_EN    | U4                                   | 0                | LV <sub>DD</sub> | 22       |

| TSEC1_TX_ER    | Т3                                   | 0                | LV <sub>DD</sub> | _        |

|                | Three-Speed Ethernet Controller (Gig | abit Ethernet 3) |                  |          |

| TSEC3_RXD[7:0] | P11, N11, M11, L11, R8, N10, N9, P10 | I                | LV <sub>DD</sub> | _        |

| TSEC3_TXD[7:0] | M7, N7, P7, M8, L7, R6, P6, M6       | 0                | LV <sub>DD</sub> | 4, 8, 14 |

| TSEC3_COL      | M9                                   | I                | LV <sub>DD</sub> | _        |

| TSEC3_CRS      | L9                                   | I/O              | LV <sub>DD</sub> | 16       |

| TSEC3_GTX_CLK  | R7                                   | 0                | LV <sub>DD</sub> | _        |

| TSEC3_RX_CLK   | P9                                   | I                | LV <sub>DD</sub> | _        |

| TSEC3_RX_DV    | P8                                   | I                | LV <sub>DD</sub> | _        |

| TSEC3_RX_ER    | R11                                  | I                | LV <sub>DD</sub> | _        |

| TSEC3_TX_CLK   | L10                                  | I                | LV <sub>DD</sub> | —        |

| TSEC3_TX_EN    | N6                                   | 0                | LV <sub>DD</sub> | 22       |

| TSEC3_TX_ER    | L8                                   | 0                | LV <sub>DD</sub> | 4, 8     |

|                | DUART                                |                  |                  | -        |

| UART_CTS[0:1]  | AH8, AF6                             | I                | OV <sub>DD</sub> | —        |

| UART_RTS[0:1]  | AG8, AG9                             | 0                | OV <sub>DD</sub> | —        |

Clocking

## 19 Clocking

This section describes the PLL configuration of the MPC8533E. Note that the platform clock is identical to the core complex bus (CCB) clock.

## 19.1 Clock Ranges

Table 58 provides the clocking specifications for the processor cores and Table 59 provides the clocking specifications for the memory bus.

|                               | Maximum Processor Core Frequency |     |     |     |      |      |          |      |      |       |

|-------------------------------|----------------------------------|-----|-----|-----|------|------|----------|------|------|-------|

| Characteristic                | 667                              | MHz | 800 | MHz | 1000 | MHz  | 1067 MHz |      | Unit | Notes |

|                               | Min                              | Max | Min | Max | Min  | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 667                              | 667 | 667 | 800 | 667  | 1000 | 667      | 1067 | MHz  | 1, 2  |

Table 58. Processor Core Clocking Specifications

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

2. The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

### Table 59. Memory Bus Clocking Specifications

| Characteristic         | -             | lency        | Unit | Notes |

|------------------------|---------------|--------------|------|-------|

|                        | 667, 800, 100 | 00, 1067 MHz |      |       |

|                        | Min           | Max          |      |       |

| Memory bus clock speed | 166           | 266          | MHz  | 1, 2  |

Notes:

- 1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

## 19.2 CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency of the CCB is set using the following reset signals (see Table 60):

- SYSCLK input signal

- Binary value on LA[28:31] at power up

NP

International Electronic Research Corporation (IERC)818-842-7277 413 North Moss St Burbank, CA 91502 Internet: www.ctscorp.com Millennium Electronics (MEI)408-436-8770 Loroco Sites 671 East Brokaw Road San Jose, CA 95112 Internet: www.mei-thermal.com Tvco Electronics800-522-6752 Chip Coolers<sup>™</sup> P.O. Box 3668 Harrisburg, PA 17105-3668 Internet: www.chipcoolers.com Wakefield Engineering603-635-2800 33 Bridge St. Pelham, NH 03076 Internet: www.wakefield.com

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost. Several heat sinks offered by Aavid Thermalloy, Advanced Thermal Solutions, Alpha Novatech, IERC, Chip Coolers, Millennium Electronics, and Wakefield Engineering offer different heat sink-to-ambient thermal resistances, that will allow the MPC8533E to function in various environments.

## 20.3.1 Internal Package Conduction Resistance

For the packaging technology, shown in Table 65, the intrinsic internal conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-board thermal resistance

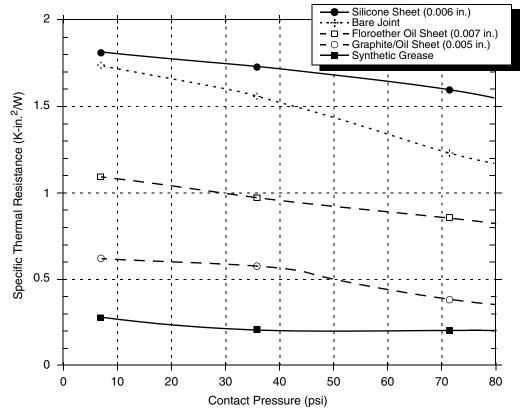

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 57). Therefore, the synthetic grease offers the best thermal performance, especially at the low interface pressure.

Figure 59. Thermal Performance of Select Thermal Interface Materials

The system board designer can choose between several types of thermal interface. There are several commercially-available thermal interfaces provided by the following vendors:

Chomerics, Inc. 781-935-4850 77 Dragon Ct. Woburn, MA 01801 Internet: www.chomerics.com Dow-Corning Corporation800-248-2481 Corporate Center P.O.Box 999 Midland, MI 48686-0997 Internet: www.dow.com Shin-Etsu MicroSi, Inc.888-642-7674 10028 S. 51st St. Phoenix, AZ 85044 Internet: www.microsi.com The Bergquist Company800-347-4572 18930 West 78<sup>th</sup> St.

System Design Information

## 21.9.1 Termination of Unused Signals

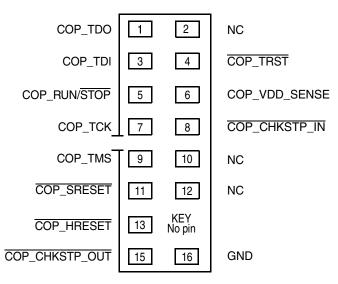

If the JTAG interface and COP header will not be used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0-k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 65. If this is not possible, the isolation resistor will allow future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- No pull-up/pull-down is required for TDI, TMS, or TDO.

Figure 64 shows the COP connector physical pinout.

Figure 64. COP Connector Physical Pinout

## 23 Document Revision History

This table provides a revision history for the MPC8533E hardware specification.

### Table 71. MPC8533E Document Revision History

| Revision | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8        | 09/2015 | • In Table 10 and Table 12, removed the output leakage current rows and removed table note 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7        | 06/2014 | <ul> <li>In Table 70, "Device Nomenclature," added full Pb-free part code.</li> <li>In Table 70, "Device Nomenclature," added footnotes 3 and 4.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6        | 05/2011 | Updated the value of t <sub>JTKLDX</sub> to 2.5 ns from 4ns in Table 45.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5        | 01/2011 | Updated Table 70.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4        | 09/2010 | <ul> <li>Modified local bus information in Section 1.1, "Key Features," to show max local bus frequency as 133 MHz.</li> <li>Added footnote 28 to Table 57.</li> <li>Updated solder-ball parameter in Table 56.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3        | 11/2009 | <ul> <li>Update Section 20.3.4, "Temperature Diode,"</li> <li>Update Table 56 Package Parameters from 95.5%sn to 96.5%sn</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2        | 01/2009 | <ul> <li>Update power number table to include 1067 MHz/533 MHz power numbers.</li> <li>Remove Part number tables from Hardware spec. The part numbers are available on Freescale web site product page.</li> <li>Removed I/O power numbers from the Hardware spec. and added the table to bring-up guide applacation note</li> <li>Updated RX_CLK duty cycle min, and max value to meet the industry standard GMII duty cycle.</li> <li>In Table 35, removed note 1 and renumbered remaining note.</li> <li>Update paragraph Section 21.3, "Decoupling Recommendations</li> <li>Update t<sub>DDKHMP</sub>, t<sub>DDKHME</sub> in Table 18</li> <li>Update Figure 5 DDR Output Timing Diagram</li> </ul> |

| 1        | 06/2008 | Update in Table 18 DDR SDRAM Output AC Timing Specifications tMCK Max value<br>Improvement to Section 16, "High-Speed Serial Interfaces (HSSI)<br>Update Figure 55 Mechanical Dimensions<br>Update in Table 43 Local Bus General Timing Parameters—PLL Bypassed                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0        | 04/2008 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |