#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| 2 0 0 0 0 0                     |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | PowerPC e500v2                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 1.067GHz                                                    |

| Co-Processors/DSP               | Security; SEC                                               |

| RAM Controllers                 | DDR, DDR2                                                   |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (2)                                         |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 90°C (TA)                                             |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 783-BBGA, FCBGA                                             |

| Supplier Device Package         | 783-FCPBGA (29x29)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8533evtarja |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with x8/x16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

- Up to 32 simultaneous open pages for DDR2

- Contiguous or discontiguous memory mapping

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL\_2 compatible I/O (1.8-V SSTL\_1.8 for DDR2)

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters that can generate interrupts

- Supports a variety of other internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, WTLS/WAP, SSL/TLS, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 2048 bits

- Elliptic curve cryptography with  $F_2m$  and F(p) modes and programmable field size up to 511 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Three PCI Express interfaces

- Two  $\times$ 4 link width interfaces and one  $\times$ 1 link width interface

- PCI Express 1.0a compatible

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Traffic class 0 only

- Full 64-bit decode with 32-bit wide windows

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, which automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the 8 counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- IEEE Std 1149.1<sup>™</sup>-compliant, JTAG boundary scan

- 783 FC-PBGA package

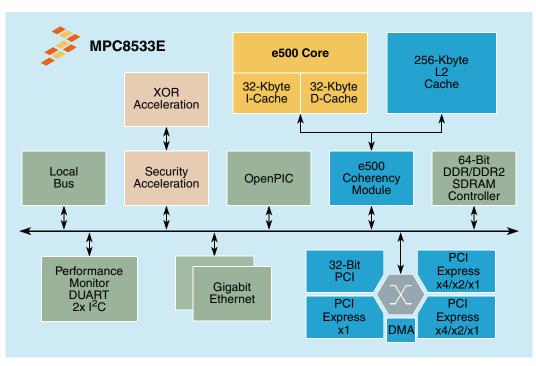

Figure 1 shows the MPC8533E block diagram.

Figure 1. MPC8533E Block Diagram

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8533E. This device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| aximum Ratings <sup>1</sup> |

|-----------------------------|

|                             |

| Characteristic                            | Symbol           | Max Value   | Unit | Notes |

|-------------------------------------------|------------------|-------------|------|-------|

| Core supply voltage                       | V <sub>DD</sub>  | -0.3 to 1.1 | V    | _     |

| PLL supply voltage                        | AV <sub>DD</sub> | -0.3 to 1.1 | V    | _     |

| Core power supply for SerDes transceivers | SV <sub>DD</sub> | -0.3 to 1.1 | V    | _     |

| Pad power supply for SerDes transceivers  | XV <sub>DD</sub> | -0.3 to 1.1 | V    | _     |

|                                    | Characteristic                                                                         | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Max Value                                                            | Unit | Notes |

|------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-------|

| DDR and DDR2                       | DRAM I/O voltage                                                                       | $ \begin{array}{ c c c c c c } & GV_{DD} & -0.3 \ to \ 2.75 & -0.3 \ to \ 1.98 & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & $ |                                                                      |      | —     |

| Three-speed Etl                    | nernet I/O, MII management voltage                                                     | LV <sub>DD</sub> (eTSEC1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      | V    | —     |

|                                    |                                                                                        | -0.3 to 1.           LV <sub>DD</sub> (eTSEC1)           TV <sub>DD</sub> (eTSEC3)           TV <sub>DD</sub> (eTSEC3)           -0.3 to 3.           -0.3 to 2.           TV <sub>DD</sub> (eTSEC3)           -0.3 to 3.           -0.3 to 1.           MV <sub>IN</sub> -0.3 to (GV <sub>DD</sub> )           MV <sub>REF</sub> -0.3 to (GV <sub>DD</sub> )           TV <sub>IN</sub> -0.3 to (TV <sub>DD</sub> )           BV <sub>IN</sub> -0.3 to (BV <sub>DD</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      | V    | —     |

| PCI, DUART, sy<br>JTAG I/O voltage | stem control and power management, I <sup>2</sup> C, and e                             | OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3 to 3.63                                                         | V    | —     |

| Local bus I/O vo                   | Itage                                                                                  | BV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3 to 2.75                                                         | V    | —     |

| Input voltage                      | DDR/DDR2 DRAM signals                                                                  | MV <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                    | DDR/DDR2 DRAM reference                                                                | MV <sub>REF</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                    | Three-speed Ethernet signals                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 2     |

|                                    | Local bus signals                                                                      | BV <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | V    | —     |

|                                    | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                    | PCI                                                                                    | OV <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

| Storage tempera                    | ature range                                                                            | T <sub>STG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -55 to 150                                                           | °C   | -     |

## Table 1. Absolute Maximum Ratings<sup>1</sup> (continued)

#### Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause.

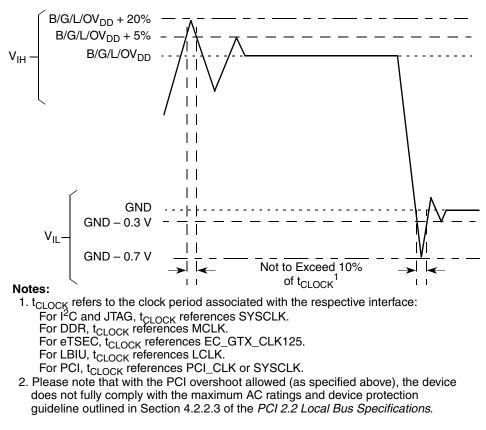

2. (M,L,O)V<sub>IN</sub>, and MV<sub>RFF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

# 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Table 2. Recommended Operation | erating Conditions |

|--------------------------------|--------------------|

|--------------------------------|--------------------|

| Characteristic                            | Symbol           | Recommended<br>Value            | Unit | Notes |

|-------------------------------------------|------------------|---------------------------------|------|-------|

| Core supply voltage                       | V <sub>DD</sub>  | 1.0 ± 50 mV                     | V    | —     |

| PLL supply voltage                        | AV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | 1     |

| Core power supply for SerDes transceivers | SV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| Pad power supply for SerDes transceivers  | XV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| DDR and DDR2 DRAM I/O voltage             | GV <sub>DD</sub> | 2.5 V ± 125 mV<br>1.8 V ± 90 mV | V    | 2     |

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8533E.

### Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>/BV<sub>DD</sub>/TV<sub>DD</sub>

The core voltage must always be provided at nominal 1.0 V (see Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 SDRAM interface uses a single-ended differential receiver referenced the externally supplied  $MV_{REF}$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL2 electrical signaling standard.

### Table 18. DDR SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions.

| Parameter      | Symbol <sup>1</sup> | Min        | Мах        | Unit | Notes |  |

|----------------|---------------------|------------|------------|------|-------|--|

| MDQS postamble | t <sub>DDKHME</sub> | 0.4 x tMCK | 0.6 x tMCK | ns   | 6     |  |

Notes:

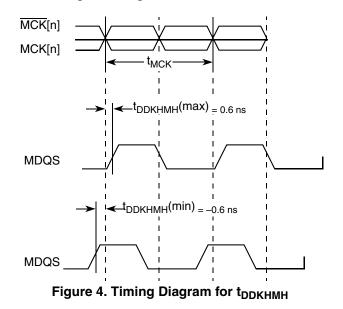

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/ $\overline{MCK}$  referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the MPC8533E PowerQUICC III Integrated Communications Processor Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- 5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

- 7. Maximum DDR1 frequency is 400 MHz.

# NOTE

For the ADDR/CMD setup and hold specifications in Table 18, it is assumed that the clock control register is set to adjust the memory clocks by  $\frac{1}{2}$  applied cycle.

Figure 4 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Enhanced Three-Speed Ethernet (eTSEC), MII Management

# 8.2 eTSEC DC Electrical Characteristics

All GMII, MII, TBI, RGMII, RTBI, RMII, and FIFO drivers and receivers comply with the DC parametric attributes specified in Table 21 and Table 22. The potential applied to the input of a GMII, MII, TBI, RTBI, RMII, and FIFO receiver may exceed the potential of the receiver's power supply (that is, a GMII driver powered from a 3.6-V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5-V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter                                                                  | Symbol                               | Min   | Мах   | Unit | Notes   |

|----------------------------------------------------------------------------|--------------------------------------|-------|-------|------|---------|

| Supply voltage 3.3 V                                                       | LV <sub>DD</sub><br>TV <sub>DD</sub> | 3.135 | 3.465 | V    | 1, 2    |

| Output high voltage ( $LV_{DD}/TV_{DD} = Min$ , $I_{OH} = -4.0 mA$ )       | V <sub>OH</sub>                      | 2.4   | —     | V    | —       |

| Output low voltage ( $LV_{DD}/TV_{DD} = Min$ , $I_{OL} = 4.0 \text{ mA}$ ) | V <sub>OL</sub>                      | —     | 0.5   | V    | —       |

| Input high voltage                                                         | V <sub>IH</sub>                      | 1.95  | —     | V    | —       |

| Input low voltage                                                          | V <sub>IL</sub>                      | —     | 0.90  | V    | —       |

| Input high current ( $V_{IN} = LV_{DD}$ , $V_{IN} = TV_{DD}$ )             | I <sub>IH</sub>                      | —     | 40    | μA   | 1, 2, 3 |

| Input low current (V <sub>IN</sub> = GND)                                  | IIL                                  | -600  | —     | μA   | 3       |

| Table 21. GMII, MII, TBI, RMII and FIFO | DC Electrical Characteristics |

|-----------------------------------------|-------------------------------|

|-----------------------------------------|-------------------------------|

Notes:

1. LV<sub>DD</sub> supports eTSEC1.

2. TV<sub>DD</sub> supports eTSEC3.

3. The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

\_\_\_\_\_

| Table 22. | GMII, | MII, | RMII, | RGMII, | , RTBI, | TBI, | and | FIFO | DC | Electric | al C | haracter | istics | 5 |

|-----------|-------|------|-------|--------|---------|------|-----|------|----|----------|------|----------|--------|---|

|           |       |      |       |        |         |      |     |      |    |          |      |          |        |   |

| Parameters                                                               | Symbol                             | Min   | Max   | Unit | Notes   |

|--------------------------------------------------------------------------|------------------------------------|-------|-------|------|---------|

| Supply voltage 2.5 V                                                     | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.375 | 2.625 | V    | 1, 2    |

| Output high voltage ( $LV_{DD}/TV_{DD} = Min$ , $I_{OH} = -1.0 mA$ )     | V <sub>OH</sub>                    | 2.0   | _     | V    | _       |

| Output low voltage ( $LV_{DD}/TV_{DD} = Min$ , $I_{OL} = 1.0 mA$ )       | V <sub>OL</sub>                    | _     | 0.4   | V    | —       |

| Input high voltage                                                       | V <sub>IH</sub>                    | 1.70  | _     | V    | —       |

| Input low voltage                                                        | V <sub>IL</sub>                    | _     | 0.7   | V    | —       |

| Input current ( $V_{IN} = 0$ , $V_{IN} = LV_{DD}$ , $V_{IN} = TV_{DD}$ ) | I <sub>IN</sub>                    | _     | ±15   | μA   | 1, 2, 3 |

Notes:

1. LV<sub>DD</sub> supports eTSEC1.

2. TV<sub>DD</sub> supports eTSEC3.

3. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

#### Table 25. GMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition                    | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|----------------------------------------|---------------------|-----|-----|-----|------|-------|

| GTX_CLK data clock fall time (80%-20%) | t <sub>GTXF</sub>   | _   | —   | 1.0 | ns   | —     |

Notes:

- The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub> (reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- Data valid t<sub>GTKHDV</sub> to GTX\_CLK Min setup time is a function of clock period and max hold time (Min setup = cycle time Max delay).

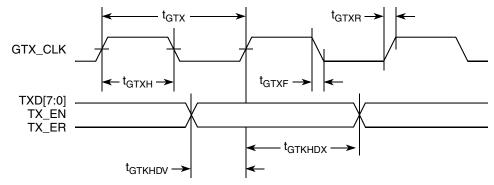

## Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

# 8.3.2.2 GMII Receive AC Timing Specifications

Table 26 provides the GMII receive AC timing specifications.

#### Table 26. GMII Receive AC Timing Specifications

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | —   | 8.0 | —   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 35  | —   | 65  | %    | —     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | —   | ns   | —     |

| RX_CLK to RXD[7:0], RX_DV, RX_ER hold time  | t <sub>GRDXKH</sub>                 | 0.5 | —   | —   | ns   | —     |

| RX_CLK clock rise (20%–80%)                 | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | —     |

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

#### Table 26. GMII Receive AC Timing Specifications (continued)

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition              | Symbol <sup>1</sup> | Min | Тур | Max | Unit | Notes |

|----------------------------------|---------------------|-----|-----|-----|------|-------|

| RX_CLK clock fall time (80%–20%) | t <sub>GRXF</sub>   |     | —   | 1.0 | ns   |       |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

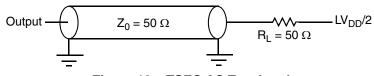

Figure 10 provides the AC test load for eTSEC.

Figure 10. eTSEC AC Test Load

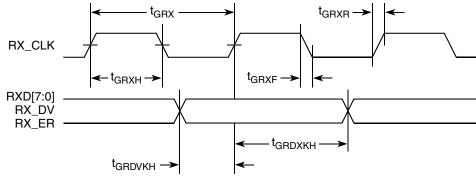

Figure 11 shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

# 8.4 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 31.

### Table 31. TBI Single-Clock Mode Receive AC Timing Specification

| Parameter/Condition                       | Symbol             | Min | Тур | Мах | Unit | Notes |

|-------------------------------------------|--------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                       | t <sub>TRR</sub>   | 7.5 | 8.0 | 8.5 | ns   | _     |

| RX_CLK duty cycle                         | t <sub>TRRH</sub>  | 40  | 50  | 60  | %    | _     |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>  | —   | —   | 250 | ps   |       |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>  | —   | —   | 1.0 | ns   |       |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>  | —   | —   | 1.0 | ns   |       |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDV</sub> | 2.0 | —   | —   | ns   |       |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDX</sub> | 1.0 | —   | —   | ns   | _     |

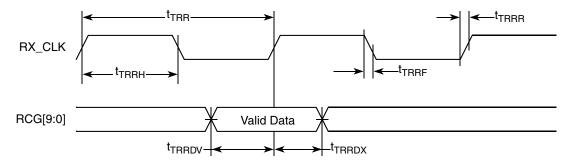

A timing diagram for TBI receive appears in Figure 17.

Figure 17. TBI Single-Clock Mode Receive AC Timing Diagram

# 8.5.4 RGMII and RTBI AC Timing Specifications

Table 32 presents the RGMII and RTBI AC timing specifications.

### Table 32. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit | Notes |

|--------------------------------------------|-------------------------------------|------|-----|------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGT_TX</sub>               | -500 | 0   | 500  | ps   | 5     |

| Data to clock input skew (at receiver)     | t <sub>SKRGT_RX</sub>               | 1.0  | —   | 2.8  | ns   | 2     |

| Clock period duration                      | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   | 3     |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    | 3, 4  |

| Rise time (20%-80%)                        | t <sub>RGTR</sub>                   | _    | —   | 0.75 | ns   | —     |

#### Table 40. Local Bus General Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled (continued)

| Parameter                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> | —   | 2.5 | ns   | 5     |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

## Table 41 describes the general timing parameters of the local bus interface at $BV_{DD} = 2.5$ V.

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Мах | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | _     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | —   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.4 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.8 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>lbotot</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                | —   | 2.8 | ns   |       |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | —   | 2.8 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | —   | 2.8 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | —   | 2.8 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.8 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.8 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | _   | 2.6 | ns   | 5     |

## Table 41. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

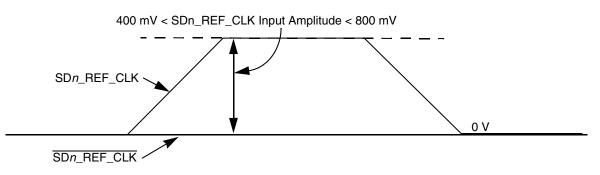

Figure 44. Single-Ended Reference Clock Input DC Requirements

# 16.2.3 Interfacing With Other Differential Signaling Levels

With on-chip termination to SGND\_SRDS*n* (xcorevss), the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC-coupled.

Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

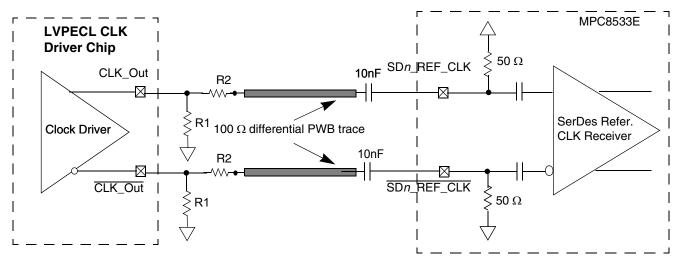

LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

# NOTE

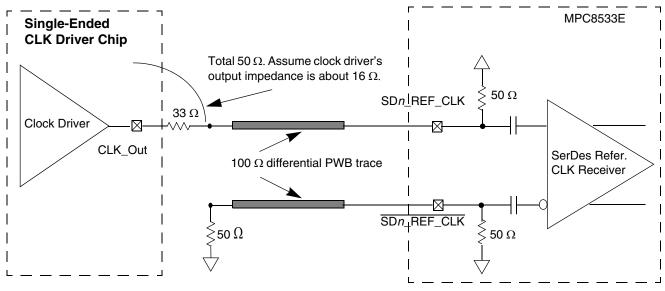

Figure 45 through Figure 48 are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8533E SerDes reference clock receiver requirement provided in this document.

assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8533E SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock driver clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 47. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

Figure 48 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8533E SerDes reference clock input's DC requirement.

Figure 48. Single-Ended Connection (Reference Only)

# Table 57. MPC8533E Pinout Listing (continued)

| Signal                     | Package Pin Number                             | Pin Type | Power<br>Supply  | Notes           |

|----------------------------|------------------------------------------------|----------|------------------|-----------------|

| SD2_REF_CLK                | AF2                                            | I        | XV <sub>DD</sub> | _               |

| SD2_TST_CLK                | AG4                                            | _        | _                | -               |

| SD2_TST_CLK                | AF4                                            | _        | —                | —               |

|                            | General-Purpose Output                         |          | •                | •               |

| GPOUT[0:7]                 | AF22, AH23, AG27, AH25, AF21, AF25, AG26, AF26 | 0        | OV <sub>DD</sub> | _               |

|                            | General-Purpose Input                          |          | •                | •               |

| GPIN[0:7]                  | AH24, AG24, AD23, AE21, AD22, AF23, AG25, AE20 | I        | OV <sub>DD</sub> | -               |

|                            | System Control                                 |          |                  |                 |

| HRESET                     | AG16                                           | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ                 | AG15                                           | 0        | OV <sub>DD</sub> | 21              |

| SRESET                     | AG19                                           | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN                   | AH5                                            | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT                  | AA12                                           | 0        | OV <sub>DD</sub> | 2, 4            |

|                            | Debug                                          |          | •                | •               |

| TRIG_IN                    | AC5                                            | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/<br>QUIESCE | AB5                                            | 0        | OV <sub>DD</sub> | 5, 8, 15,<br>21 |

| MSRCID[0:1]                | Y7, W9                                         | 0        | OV <sub>DD</sub> | 4, 5, 8         |

| MSRCID[2:4]                | AA9, AB6, AD5                                  | 0        | OV <sub>DD</sub> | 5, 15, 21       |

| MDVAL                      | Y8                                             | 0        | OV <sub>DD</sub> | 5               |

| CLK_OUT                    | AE16                                           | 0        | OV <sub>DD</sub> | 10              |

|                            | Clock                                          |          | ·                | ·               |

| RTC                        | AF15                                           | I        | OV <sub>DD</sub> | —               |

| SYSCLK                     | AH16                                           | I        | OV <sub>DD</sub> | —               |

|                            | JTAG                                           |          |                  |                 |

| тск                        | AG28                                           | I        | OV <sub>DD</sub> | —               |

| TDI                        | AH28                                           | I        | OV <sub>DD</sub> | 11              |

| TDO                        | AF28                                           | 0        | OV <sub>DD</sub> | 10              |

| TMS                        | AH27                                           | I        | OV <sub>DD</sub> | 11              |

| TRST                       | AH22                                           | I        | OV <sub>DD</sub> | 11              |

Package Description

| Signal          | Package Pin Number                                                                                                       | Pin Type                                              | Power<br>Supply  | Notes |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------|

| V <sub>DD</sub> | L16, L14, M13, M15, M17, N12, N14, N16, N18,<br>P13, P15, P17, R12, R14, R16, R18, T13, T15,<br>T17, U12, U14, U16, U18, | Power for core<br>(1.0 V)                             | V <sub>DD</sub>  | -     |

| SVDD_SRDS       | M27, N25, P28, R24, R26, T24, T27, U25, W24,<br>W26, Y24, Y27, AA25, AB28, AD27                                          | Core power for<br>SerDes 1<br>transceivers<br>(1.0 V) | SV <sub>DD</sub> | -     |

| SVDD_SRDS2      | AB1, AC26, AD2, AE26, AG2                                                                                                | Core power for<br>SerDes 2<br>transceivers<br>(1.0 V) | SV <sub>DD</sub> | -     |

| XVDD_SRDS       | M21, N23, P20, R22, T20, U23, V21, W22, Y20                                                                              | Pad power for<br>SerDes 1<br>transceivers<br>(1.0 V)  | XV <sub>DD</sub> | -     |

| XVDD_SRDS2      | Y6, AA6, AA23, AF5, AG5                                                                                                  | Pad power for<br>SerDes 2<br>transceivers<br>(1.0 V)  | XV <sub>DD</sub> | -     |

| XGND_SRDS       | M20, M24, N22, P21, R23, T21, U22, V20, W23,<br>Y21                                                                      | —                                                     | —                | —     |

| XGND_SRDS2      | Y4, AA4, AA22, AD4, AE4, AH4                                                                                             | —                                                     | _                | —     |

| SGND_SRDS       | M28, N26, P24, P27, R25, T28, U24, U26, V24,<br>W25, Y28, AA24, AA26, AB24, AB27, AC24,<br>AD28                          | —                                                     | _                | -     |

| AGND_SRDS       | V27                                                                                                                      | SerDes PLL<br>GND                                     | _                | —     |

| SGND_SRDS2      | Y2, AA1, AB3, AC2, AC3, AC25, AD3, AD24, AE3, AE1, AE25, AF3, AH2                                                        | —                                                     | _                | —     |

| AGND_SRDS2      | AF1                                                                                                                      | SerDes PLL<br>GND                                     | —                | —     |

| AVDD_LBIU       | C28                                                                                                                      | Power for local<br>bus PLL<br>(1.0 V)                 | _                | 19    |

| AVDD_PCI1       | AH20                                                                                                                     | Power for PCI<br>PLL<br>(1.0 V)                       | _                | 19    |

| AVDD_CORE       | AH14                                                                                                                     | Power for e500<br>PLL (1.0 V)                         | —                | 19    |

| AVDD_PLAT       | AH18                                                                                                                     | Power for CCB<br>PLL (1.0 V)                          | _                | 19    |

# Table 57. MPC8533E Pinout Listing (continued)

# 19.6.2 Platform to FIFO Restrictions

Please note the following FIFO maximum speed restrictions based on platform speed. Refer to Section 4.4, "Platform to FIFO Restrictions," for additional information.

| Platform Speed (MHz) | Maximum FIFO Speed for Reference Clocks TSEC <i>n</i> _TX_CLK, TSEC <i>n</i> _RX_CLK (MHz) <sup>1</sup> |

|----------------------|---------------------------------------------------------------------------------------------------------|

| 533                  | 126                                                                                                     |

| 400                  | 94                                                                                                      |

#### **Table 64. FIFO Maximum Speed Restrictions**

Note:

1. FIFO speed should be less than 24% of the platform speed.

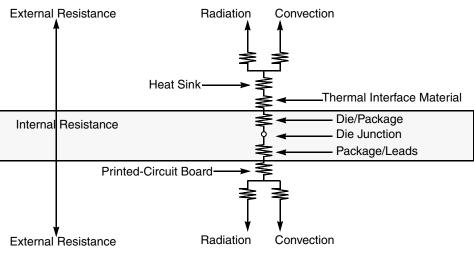

# 20 Thermal

This section describes the thermal specifications of the MPC8533E.

# 20.1 Thermal Characteristics

Table 65 provides the package thermal characteristics.

Table 65. Package Thermal Characteristics

| Characteristic                         | JEDEC Board             | Symbol                | Value | Unit | Notes |

|----------------------------------------|-------------------------|-----------------------|-------|------|-------|

| Junction-to-ambient natural convection | Single layer board (1s) | $R_{	hetaJA}$         | 26    | °C/W | 1, 2  |

| Junction-to-ambient natural convection | Four layer board (2s2p) | $R_{\thetaJA}$        | 21    | °C/W | 1, 2  |

| Junction-to-ambient (@200 ft/min)      | Single layer board (1s) | $R_{\thetaJA}$        | 21    | °C/W | 1, 2  |

| Junction-to-ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{\thetaJA}$        | 17    | °C/W | 1, 2  |

| Junction-to-board thermal              | —                       | $R_{\theta JB}$       | 12    | °C/W | 3     |

| Junction-to-case thermal               |                         | $R_{	extsf{	heta}JC}$ | <0.1  | °C/W | 4     |

#### Notes:

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

2. Per JEDEC JESD51-2 and JESD51-6 with the board (JESD51-9) horizontal.

3. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

4. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. Actual thermal resistance is less than 0.1°C/W.

#### Thermal

Figure 58 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.