# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500v2                                                       |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 1.0GHz                                                               |

| Co-Processors/DSP               | -                                                                    |

| RAM Controllers                 | DDR, DDR2                                                            |

| Graphics Acceleration           | Νο                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10/100/1000Mbps (2)                                                  |

| SATA                            | -                                                                    |

| USB                             | -                                                                    |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                     |

| Operating Temperature           | 0°C ~ 90°C (TA)                                                      |

| Security Features               | -                                                                    |

| Package / Case                  | 783-BBGA, FCBGA                                                      |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8533vtaqg |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Two enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Two IEEE Std 802.3<sup>™</sup>, IEEE 802.3u, IEEE 802.3x, IEEE 802.3z, IEEE 802.3ac, and IEEE 802.3ab-compliant controllers

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, and RGMII.

- 10/100 Mbps full- and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII.

- Flexible configuration for multiple PHY interface configurations.

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, 802.2, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

|                                    | Characteristic                                                                         | Symbol                               | Max Value                                                            | Unit | Notes |

|------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------|------|-------|

| DDR and DDR2                       | DRAM I/O voltage                                                                       | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                         | V    | —     |

| Three-speed Etl                    | Three-speed Ethernet I/O, MII management voltage                                       |                                      | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

|                                    |                                                                                        | TV <sub>DD</sub> (eTSEC3)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

| PCI, DUART, sy<br>JTAG I/O voltage | stem control and power management, I <sup>2</sup> C, and e                             | OV <sub>DD</sub>                     | -0.3 to 3.63                                                         | V    | —     |

| Local bus I/O vo                   | Itage                                                                                  | BV <sub>DD</sub>                     | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | —     |

| Input voltage                      | DDR/DDR2 DRAM signals                                                                  | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                    | DDR/DDR2 DRAM reference                                                                | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                    | Three-speed Ethernet signals                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub> | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 2     |

|                                    | Local bus signals                                                                      | BV <sub>IN</sub>                     | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | V    | —     |

|                                    | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                     | –0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

|                                    | PCI                                                                                    | OV <sub>IN</sub>                     | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 2     |

| Storage tempera                    | ature range                                                                            | T <sub>STG</sub>                     | –55 to 150                                                           | °C   | -     |

#### Table 1. Absolute Maximum Ratings<sup>1</sup> (continued)

#### Notes:

1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause.

2. (M,L,O)V<sub>IN</sub>, and MV<sub>RFF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

### 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

| Table 2. Recommended Operation | erating Conditions |

|--------------------------------|--------------------|

|--------------------------------|--------------------|

| Characteristic                            | Symbol           | Recommended<br>Value            | Unit | Notes |

|-------------------------------------------|------------------|---------------------------------|------|-------|

| Core supply voltage                       | V <sub>DD</sub>  | 1.0 ± 50 mV                     | V    | —     |

| PLL supply voltage                        | AV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | 1     |

| Core power supply for SerDes transceivers | SV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| Pad power supply for SerDes transceivers  | XV <sub>DD</sub> | 1.0 ± 50 mV                     | V    | —     |

| DDR and DDR2 DRAM I/O voltage             | GV <sub>DD</sub> | 2.5 V ± 125 mV<br>1.8 V ± 90 mV | V    | 2     |

**Power Characteristics**

# **3** Power Characteristics

The estimated typical core power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices is shown in Table 4.

| Power Mode | Core Frequency<br>(MHz) | Platform<br>Frequency (MHz) | V <sub>DD</sub><br>(V) | Junction<br>Temperature (°C) | Power<br>(W) | Notes |

|------------|-------------------------|-----------------------------|------------------------|------------------------------|--------------|-------|

| Typical    | 667                     | 333                         | 1.0                    | 65                           | 2.6          | 1, 2  |

| Thermal    |                         |                             |                        | 90                           | 3.75         | 1, 3  |

| Maximum    |                         |                             |                        |                              | 5.85         | 1, 4  |

| Typical    | 800                     | 400                         | 1.0                    | 65                           | 2.9          | 1, 2  |

| Thermal    |                         |                             |                        | 90                           | 4.0          | 1, 3  |

| Maximum    |                         |                             |                        |                              | 6.0          | 1, 4  |

| Typical    | 1000                    | 400                         | 1.0                    | 65                           | 3.6          | 1, 2  |

| Thermal    |                         |                             |                        | 90                           | 4.4          | 1, 3  |

| Maximum    |                         |                             |                        |                              | 6.2          | 1, 4  |

| Typical    | 1067                    | 533                         | 1.0                    | 65                           | 3.9          | 1, 2  |

| Thermal    |                         |                             |                        | 90                           | 5.0          | 1, 3  |

| Maximum    |                         |                             |                        |                              | 6.5          | 1, 4  |

#### Table 4. MPC8533E Core Power Dissipation

Notes:

- 1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

- Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>) and 65°C junction temperature (see Table 2) while running the Dhrystone 2.1 benchmark.

- Thermal power is the average power measured at nominal core voltage (V<sub>DD</sub>) and maximum operating junction temperature (see Table 2) while running the Dhrystone 2.1 benchmark.

- 4. Maximum power is the maximum power measured at nominal core voltage (V<sub>DD</sub>) and maximum operating junction temperature (see Table 2) while running a smoke test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep the execution unit maximally busy.

# 4 Input Clocks

This section contains the following subsections:

- Section 4.1, "System Clock Timing"

- Section 4.2, "Real-Time Clock Timing"

- Section 4.3, "eTSEC Gigabit Reference Clock Timing"

- Section 4.4, "Platform to FIFO Restrictions"

- Section 4.5, "Other Input Clocks"

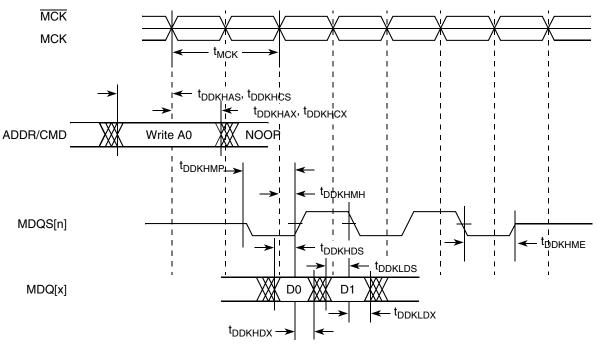

Figure 5 shows the DDR SDRAM output timing diagram.

Figure 5. DDR and DDR2 SDRAM Output Timing Diagram

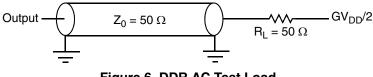

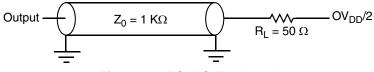

Figure 6 provides the AC test load for the DDR bus.

Figure 6. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8533E.

# 7.1 DUART DC Electrical Characteristics

Table 19 provides the DC electrical characteristics for the DUART interface.

Table 19. DUART DC Electrical Characteristics

| Parameter                                                        | Symbol          | Min  | Мах                    | Unit | Notes |

|------------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                         | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | _     |

| Low-level input voltage                                          | V <sub>IL</sub> | -0.3 | 0.8                    | V    | _     |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = V_{DD}$ )     | I <sub>IN</sub> | _    | ±5                     | μA   | 1     |

| High-level output voltage ( $OV_{DD} = min$ , $I_{OH} = -2 mA$ ) | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

#### Table 26. GMII Receive AC Timing Specifications (continued)

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition              | Symbol <sup>1</sup> | Min | Тур | Max | Unit | Notes |

|----------------------------------|---------------------|-----|-----|-----|------|-------|

| RX_CLK clock fall time (80%–20%) | t <sub>GRXF</sub>   |     |     | 1.0 | ns   |       |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

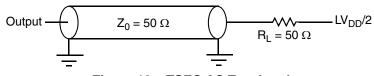

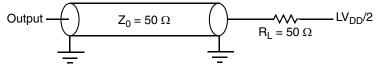

Figure 10 provides the AC test load for eTSEC.

Figure 10. eTSEC AC Test Load

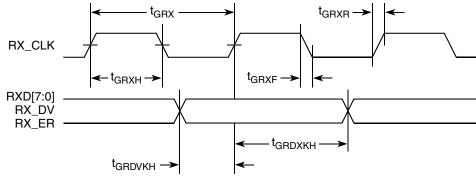

Figure 11 shows the GMII receive AC timing diagram.

Figure 11. GMII Receive AC Timing Diagram

### 8.4 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

#### Table 28. MII Receive AC Timing Specifications (continued)

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5%.or 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup> | Min  | Тур | Max | Unit | Notes |

|---------------------------------------------|---------------------|------|-----|-----|------|-------|

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub> | 10.0 | —   | _   | ns   | —     |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub> | 10.0 | _   | _   | ns   | —     |

| RX_CLK clock rise (20%-80%)                 | t <sub>MRXR</sub>   | 1.0  | _   | 4.0 | ns   | —     |

| RX_CLK clock fall time (80%–20%)            | t <sub>MRXF</sub>   | 1.0  | —   | 4.0 | ns   | —     |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

Figure 13 provides the AC test load for eTSEC.

Figure 13. eTSEC AC Test Load

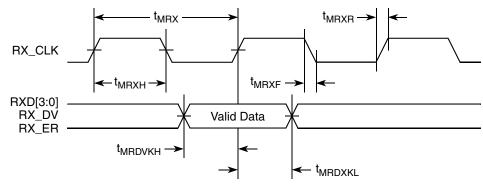

Figure 14 shows the MII receive AC timing diagram.

Figure 14. MII Receive AC Timing Diagram

### 8.5 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

#### Table 32. RGMII and RTBI AC Timing Specifications (continued)

At recommended operating conditions with L/TV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition | Symbol <sup>1</sup> | Min | Тур | Max  | Unit | Notes |

|---------------------|---------------------|-----|-----|------|------|-------|

| Fall time (20%–80%) | t <sub>RGTF</sub>   |     | _   | 0.75 | ns   | —     |

Notes:

- In general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design will require clocks to be routed such that an additional trace delay of greater than 1.5 ns will be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{BGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Guaranteed by design.

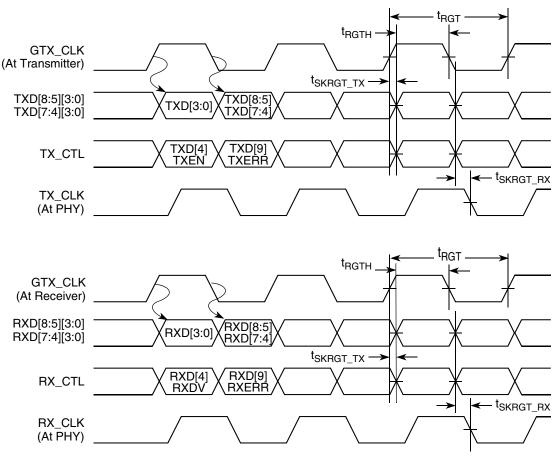

Figure 18 shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 18. RGMII and RTBI AC Timing and Multiplexing Diagrams

Local Bus

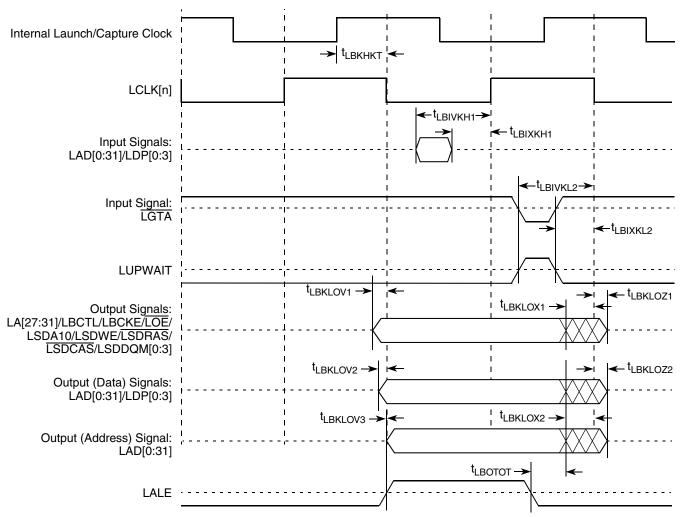

Figure 25. Local Bus Signals (PLL Bypass Mode)

#### NOTE

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at falling edge of the internal clock withe the exception of LGTA/LUPWAIT (which is captured on the rising edge of the internal clock).

JTAG

#### Table 45. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

At recommended operating conditions (see Table 3).

| Parameter                                                           | Symbol <sup>2</sup> | Min | Max | Unit | Notes |

|---------------------------------------------------------------------|---------------------|-----|-----|------|-------|

| JTAG external clock to output high impedance:<br>Boundary-scan data | t <sub>JTKLDZ</sub> | 3   | 19  | ns   | 5     |

| TDO                                                                 | t <sub>JTKLOZ</sub> | 3   | 9   |      |       |

#### Notes:

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 30). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

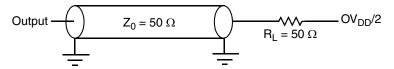

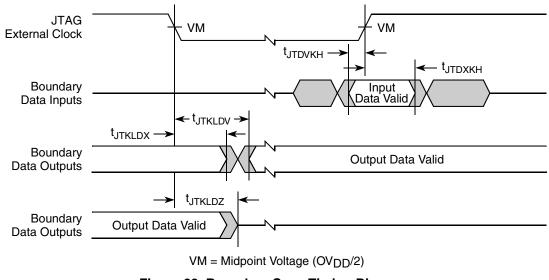

Figure 30 provides the AC test load for TDO and the boundary-scan outputs.

Figure 30. AC Test Load for the JTAG Interface

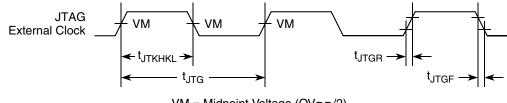

Figure 31 provides the JTAG clock input timing diagram.

$VM = Midpoint Voltage (OV_{DD}/2)$

Figure 31. JTAG Clock Input Timing Diagram

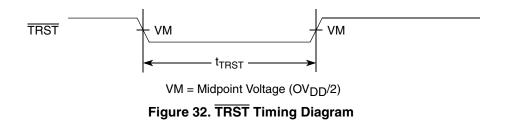

Figure 32 provides the TRST timing diagram.

Figure 33 provides the boundary-scan timing diagram.

Figure 33. Boundary-Scan Timing Diagram

# 13 l<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8533E.

# 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 46 provides the DC electrical characteristics for the I<sup>2</sup>C interfaces.

Table 46. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  5%.

| Parameter                                                                                                | Symbol              | Min                  | Мах                    | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|----------------------|------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times OV_{DD}$ | OV <sub>DD</sub> + 0.3 | V    | _     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                 | $0.3 \times OV_{DD}$   | V    | _     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                    | $0.2 \times OV_{DD}$   | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>i2KHKL</sub> | 0                    | 50                     | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -10                  | 10                     | μA   | 3     |

| Capacitance for each I/O pin                                                                             | Cl                  | —                    | 10                     | pF   | —     |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. Refer to the MPC8533E PowerQUICC III Integrated Communications Host Processor Reference Manual for information on the digital filter used.

3. I/O pins will obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

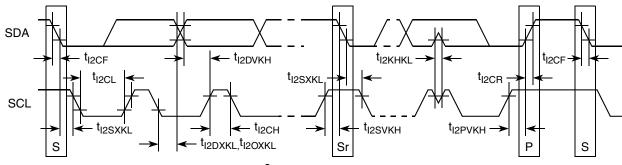

### Figure 34 provides the AC test load for the $I^2C$ .

Figure 34. I<sup>2</sup>C AC Test Load

Figure 35 shows the AC timing diagram for the  $I^2C$  bus.

Figure 35. I<sup>2</sup>C Bus AC Timing Diagram

# 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO interface of the MPC8533E.

## 14.1 GPIO DC Electrical Characteristics

Table 48 provides the DC electrical characteristics for the GPIO interface.

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit | Notes |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                        | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = V_{DD}$ )    | I <sub>IN</sub> | —    | ±5                     | μA   | 1     |

| High-level output voltage ( $OV_{DD} = mn$ , $I_{OH} = -2 mA$ ) | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

| Low-level output voltage ( $OV_{DD} = min$ , $I_{OL} = 2 mA$ )  | V <sub>OL</sub> | —    | 0.4                    | V    |       |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

PCI

# 14.2 GPIO AC Electrical Specifications

Table 49 provides the GPIO input and output AC timing specifications.

**Table 49. GPIO Input AC Timing Specifications**

| Parameter                       | Symbol             | Тур | Unit | Notes |

|---------------------------------|--------------------|-----|------|-------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 1     |

#### Note:

1. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

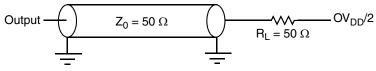

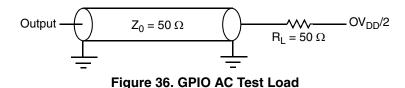

Figure 36 provides the AC test load for the GPIO.

# 15 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8533E.

### 15.1 PCI DC Electrical Characteristics

Table 50 provides the DC electrical characteristics for the PCI interface.

| Table 50. | PCI DC | Electrical | Characteristics | 1 |

|-----------|--------|------------|-----------------|---|

|-----------|--------|------------|-----------------|---|

| Parameter                                                                 | Symbol          | Min  | Мах                    | Unit | Notes |

|---------------------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                                  | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage                                                   | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = V_{DD}$ )              | I <sub>IN</sub> | _    | ±5                     | μA   | 2     |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2mA$ )              | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | V <sub>OL</sub> | _    | 0.4                    | V    | _     |

Notes:

1. Ranges listed do not meet the full range of the DC specifications of the PCI 2.2 Local Bus Specifications.

2. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

This section describes the general AC timing parameters of the PCI bus. Note that the SYSCLK signal is used as the PCI input clock. Table 51 provides the PCI AC timing specifications at 66 MHz.

| Parameter                               | Symbol <sup>1</sup> | Min                | Max | Unit   | Notes |

|-----------------------------------------|---------------------|--------------------|-----|--------|-------|

| SYSCLK to output valid                  | t <sub>PCKHOV</sub> | _                  | 7.4 | ns     | 2, 3  |

| Output hold from SYSCLK                 | t <sub>PCKHOX</sub> | 2.0                | _   | ns     | 2     |

| SYSCLK to output high impedance         | t <sub>PCKHOZ</sub> | —                  | 14  | ns     | 2, 4  |

| Input setup to SYSCLK                   | t <sub>PCIVKH</sub> | 3.7                | _   | ns     | 2, 5  |

| Input hold from SYSCLK                  | t <sub>PCIXKH</sub> | 0.5                | _   | ns     | 2, 5  |

| REQ64 to HRESET <sup>9</sup> setup time | t <sub>PCRVRH</sub> | $10 	imes t_{SYS}$ | _   | clocks | 6, 7  |

| HRESET to REQ64 hold time               | t <sub>PCRHRX</sub> | 0                  | 50  | ns     | 7     |

| HRESET high to first FRAME assertion    | t <sub>PCRHFV</sub> | 10                 | _   | clocks | 8     |

| Rise time (20%–80%)                     | t <sub>PCICLK</sub> | 0.6                | 2.1 | ns     | —     |

| Fall time (20%–80%)                     | t <sub>PCICLK</sub> | 0.6                | 2.1 | ns     | _     |

Table 51. PCI AC Timing Specifications at 66 MHz

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the SYSCLK clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub></sub>

- 2. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

- 3. All PCI signals are measured from  $OV_{DD}/2$  of the rising edge of PCI\_SYNC\_IN to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V PCI signaling levels.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Input timings are measured at the pin.

- The timing parameter t<sub>SYS</sub> indicates the minimum and maximum CLK cycle times for the various specified frequencies. The system clock period must be kept within the minimum and maximum defined ranges. For values see Section 19, "Clocking."

- 7. The setup and hold time is with respect to the rising edge of HRESET.

- 8. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the PCI 2.2 Local Bus Specifications.

- 9. The reset assertion timing requirement for  $\overline{\text{HRESET}}$  is 100  $\mu\text{s}.$

Figure 37 provides the AC test load for PCI.

Figure 37. PCI AC Test Load

PCI Express

# 17 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8533E.

# 17.1 DC Requirements for PCI Express SD\_REF\_CLK and SD\_REF\_CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

# **17.2 AC Requirements for PCI Express SerDes Clocks**

Table 53 provides the AC requirements for the PCI Express SerDes clocks.

| Symbol <sup>2</sup> | Parameter Description                                                                    | Min | Тур | Max | Units | Notes |

|---------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-------|-------|

| t <sub>REF</sub>    | REFCLK cycle time                                                                        | _   | 10  | —   | ns    | 1     |

| t <sub>REFCJ</sub>  | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _   | _   | 100 | ps    |       |

| t <sub>REFPJ</sub>  | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _   | 50  | ps    | _     |

Table 53. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

Notes:

1. Typical based on PCI Express Specification 2.0.

2. Guaranteed by characterization.

## 17.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm$ 300 ppm tolerance.

# 17.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer please refer to the *PCI Express Base Specification. Rev. 1.0a.*

PCI Express

| Symbol                             | Parameter                                                                                                      | Min | Nom | Max           | Unit | Comments                                                                                                                                                                                                                                                |

|------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-RCV-DETECT</sub>         | Amount of voltage<br>change allowed during<br>receiver detection                                               | _   | _   | 600           | mV   | The total amount of voltage change that a transmitter can apply to sense whether a low impedance receiver is present. See Note 6.                                                                                                                       |

| V <sub>TX-DC-CM</sub>              | TX DC common mode voltage                                                                                      | 0   | _   | 3.6           | V    | The allowed DC common mode voltage under any conditions. See Note 6.                                                                                                                                                                                    |

| I <sub>TX-SHORT</sub>              | TX short circuit current<br>limit                                                                              | _   | _   | 90            | mA   | The total current the transmitter can provide when shorted to its ground.                                                                                                                                                                               |

| T <sub>TX-IDLE-MIN</sub>           | Minimum time spent in<br>electrical idle                                                                       | 50  | _   | _             | UI   | Minimum time a transmitter must be in<br>electrical idle utilized by the receiver to<br>start looking for an electrical idle exit after<br>successfully receiving an electrical idle<br>ordered set.                                                    |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>   | Maximum time to<br>transition to a valid<br>electrical idle after<br>sending an electrical<br>Idle ordered set | _   | _   | 20            | UI   | After sending an electrical idle ordered set,<br>the transmitter must meet all electrical idle<br>specifications within this time. This is<br>considered a debounce time for the<br>transmitter to meet electrical idle after<br>transitioning from LO. |

| T <sub>TX-IDLE-TO</sub> -DIFF-DATA | Maximum time to<br>transition to valid TX<br>specifications after<br>leaving an electrical<br>idle condition   |     | _   | 20            | UI   | Maximum time to meet all TX<br>specifications when transitioning from<br>electrical idle to sending differential data.<br>This is considered a debounce time for the<br>TX to meet all TX specifications after<br>leaving electrical idle.              |

| RL <sub>TX-DIFF</sub>              | Differential return loss                                                                                       | 12  | _   | —             | dB   | Measured over 50 MHz to 1.25 GHz. See Note 4.                                                                                                                                                                                                           |

| RL <sub>TX-CM</sub>                | Common mode return<br>loss                                                                                     | 6   | _   | —             | dB   | Measured over 50 MHz to 1.25 GHz. See Note 4.                                                                                                                                                                                                           |

| Z <sub>TX-DIFF-DC</sub>            | DC differential TX impedance                                                                                   | 80  | 100 | 120           | Ω    | TX DC differential mode low impedance.                                                                                                                                                                                                                  |

| Z <sub>TX-DC</sub>                 | Transmitter DC<br>impedance                                                                                    | 40  | —   | —             | Ω    | Required TX D+ as well as D– DC<br>Impedance during all states.                                                                                                                                                                                         |

| L <sub>TX-SKEW</sub>               | Lane-to-lane output<br>skew                                                                                    | _   | —   | 500 +<br>2 UI | ps   | Static skew between any two transmitter lanes within a single link.                                                                                                                                                                                     |

| C <sub>TX</sub>                    | AC coupling capacitor                                                                                          | 75  | —   | 200           | nF   | All transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself.                                                                                                                  |

#### Table 54. Differential Transmitter (TX) Output Specifications (continued)

\_\_\_\_\_

| Symbol                                       | Parameter                                                                                | Min   | Nom | Max | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|------------------------------------------------------------------------------------------|-------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum deviation<br>from the median | _     |     | 0.3 | UI    | Jitter is defined as the measurement<br>variation of the crossing points ( $V_{RX-DIFFp-p}$<br>= 0 V) in relation to a recovered TX UI. A<br>recovered TX UI is calculated over 3500<br>consecutive unit intervals of sample data.<br>Jitter is measured using all edges of the 250<br>consecutive UI in the center of the 3500 UI<br>used for calculating the TX UI. See Notes 2,<br>3, and 7. |

| V <sub>RX-CM-ACp</sub>                       | AC peak common<br>mode input voltage                                                     | _     |     | 150 | mV    | $ \begin{split} & V_{RX\text{-}CM\text{-}ACp} =  V_{RXD\text{+}} - V_{RXD\text{-}}  \div 2 - \\ & V_{RX\text{-}CM\text{-}DC} \\ & V_{RX\text{-}CM\text{-}DC} = DC_{(avg)} \text{ of }  V_{RX\text{-}D\text{+}} - V_{RX\text{-}D\text{-}} /2 \\ & See Note 2. \end{split} $                                                                                                                      |

| RL <sub>RX-DIFF</sub>                        | Differential return<br>loss                                                              | 15    | —   | —   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D– lines biased at +300 and –300 mV, respectively. See Note 4.                                                                                                                                                                                                                                                                                 |

| RL <sub>RX-CM</sub>                          | Common mode<br>return loss                                                               | 6     | —   | —   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D– lines biased at 0 V. See Note 4.                                                                                                                                                                                                                                                                                                            |

| Z <sub>RX-DIFF-DC</sub>                      | DC differential input impedance                                                          | 80    | 100 | 120 | Ω     | RX DC differential mode impedance. See Note 5.                                                                                                                                                                                                                                                                                                                                                  |

| Z <sub>RX-DC</sub>                           | DC input impedance                                                                       | 40    | 50  | 60  | Ω     | Required RX D+ as well as D– DC impedance (50 $\pm$ 20% tolerance).<br>See Notes 2 and 5.                                                                                                                                                                                                                                                                                                       |

| Z <sub>RX-HIGH-IMP-DC</sub>                  | Powered down DC input impedance                                                          | 200 k | _   | _   | Ω     | Required RX D+ as well as D– DC<br>impedance when the receiver terminations<br>do not have power. See Note 6.                                                                                                                                                                                                                                                                                   |

| VRX-IDLE-DET-DIFFp-p                         | Electrical idle detect threshold                                                         | 65    | _   | 175 | mV    | $V_{RX-IDLE-DET-DIFF_{p-p}} = 2 \times  V_{RX-D+} - V_{RX-D-} $<br>Measured at the package pins of the receiver.                                                                                                                                                                                                                                                                                |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME  | Unexpected<br>electrical idle enter<br>detect threshold<br>integration time              | _     | _   | 10  | ms    | An unexpected electrical idle ( $V_{RX-DIFFp-p}$<br>< $V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized<br>no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to<br>signal an unexpected idle condition.                                                                                                                                                                                               |

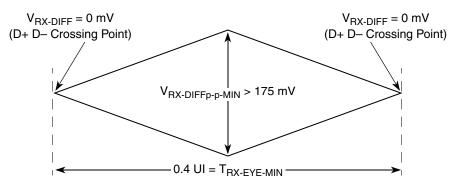

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

#### NOTE

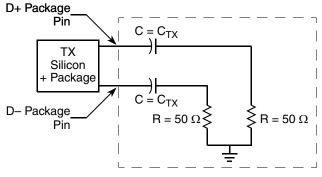

The reference impedance for return loss measurements is  $50 \Omega$  to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with  $50-\Omega$  probes, see Figure 53). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 53. Minimum Receiver Eye Timing and Voltage Compliance Specification

### 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 54.

#### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 54. Compliance Test/Measurement Load

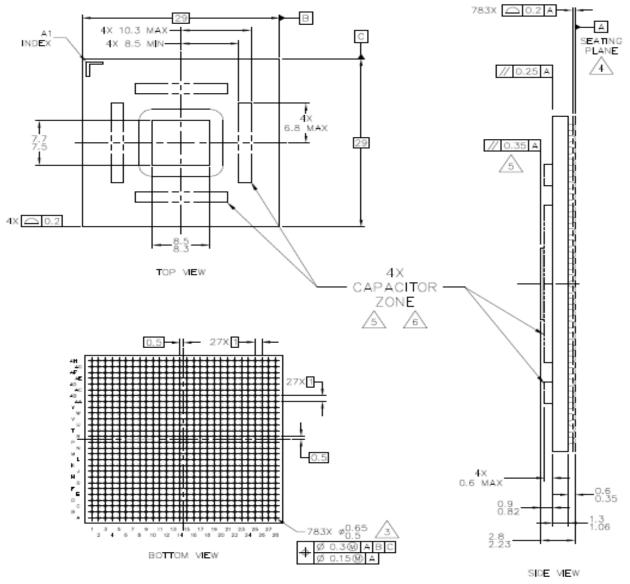

### 18.2 Mechanical Dimensions of the MPC8533E FC-PBGA

Figure 55 shows the mechanical dimensions and bottom surface nomenclature of the MPC8533E, 783 FC-PBGA package without a lid.

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. Capacitors may not be present on all parts. Care must be taken not to short exposed metal capacitor pads.

- 7. All dimensions are symmetric across the package center lines, unless dimensioned otherwise.

#### Figure 55. Mechanical Dimensions and Bottom Surface Nomenclature of the MPC8533E FC-PBGA without a Lid

NP

International Electronic Research Corporation (IERC)818-842-7277 413 North Moss St Burbank, CA 91502 Internet: www.ctscorp.com Millennium Electronics (MEI)408-436-8770 Loroco Sites 671 East Brokaw Road San Jose, CA 95112 Internet: www.mei-thermal.com Tvco Electronics800-522-6752 Chip Coolers<sup>™</sup> P.O. Box 3668 Harrisburg, PA 17105-3668 Internet: www.chipcoolers.com Wakefield Engineering603-635-2800 33 Bridge St. Pelham, NH 03076 Internet: www.wakefield.com

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost. Several heat sinks offered by Aavid Thermalloy, Advanced Thermal Solutions, Alpha Novatech, IERC, Chip Coolers, Millennium Electronics, and Wakefield Engineering offer different heat sink-to-ambient thermal resistances, that will allow the MPC8533E to function in various environments.

### 20.3.1 Internal Package Conduction Resistance

For the packaging technology, shown in Table 65, the intrinsic internal conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-board thermal resistance

Option 2

- If PCI arbiter is disabled during POR,

- All AD pins will be in the input state. Therefore, all ADs pins need to be grouped together and tied to  $OV_{DD}$  through a single (or multiple) 10-k $\Omega$  resistor(s).

- All PCI control pins can be grouped together and tied to  $OV_{DD}$  through a single 10-k $\Omega$  resistor.

### 21.12 Guideline for LBIU Termination

If the LBIU parity pins are not used, the following list shows the termination recommendation:

- For LDP[0:3]: tie them to ground or the power supply rail via a 4.7-k $\Omega$  resistor.

- For LPBSE: tie it to the power supply rail via a 4.7-k $\Omega$  resistor (pull-up resistor).

# 22 Device Nomenclature

Ordering information for the parts fully covered by this hardware specifications document is provided in Section 22.3, "Part Marking." Contact your local Freescale sales office or regional marketing team for order information.

# 22.1 Industrial and Commercial Tier Qualification

The MPC8533E device has been tested to meet the commercial tier qualification. Table 69 provides a description for commercial and industrial qualifications.

| Tier <sup>1</sup> | Typical Application<br>Use Time | Power-On Hours       | Example of Typical Applications                                                                       |

|-------------------|---------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|

| Commercial        | 5 years                         | Part-time/ Full-Time | PC's, consumer electronics, office automation, SOHO networking, portable telecom products, PDAs, etc. |

| Industrial        | 10 years                        | Typically Full-Time  | Installed telecom equipment, work stations, servers, warehouse equipment, etc.                        |

Table 69. Commercial and Industrial Description

Note:

1. Refer to Table 2 for operating temperature ranges. Temperature is independent of tier and varies per product.