#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100Mbps (1)                                                                                                      |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (3)                                                                                                   |

| Voltage - I/O                      | 1.2V, 1.8V, 3.0V                                                                                                    |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 432-TFBGA                                                                                                           |

| Supplier Device Package            | 432-MAPBGA (13x13)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6l2dvn10ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 2. i.MX 6SoloLite Modules List (continued)

| Block<br>Mnemonic                | Block Name                                   | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|----------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOMUXC                           | IOMUX<br>Control                             | System Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| KPP                              | Key Pad Port                                 | Connectivity<br>Peripherals   | <ul> <li>KPP Supports 8 x 8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LCDIF                            | LCD Interface                                | Multimedia<br>Peripherals     | The LCDIF provides display data for external LCD panels from simple text-only displays to WVGA, 16/18/24 bpp color TFT panels. The LCDIF supports all of these different interfaces by providing fully programmable functionality and sharing register space, FIFOs, and ALU resources at the same time. The LCDIF supports RGB (DOTCLK) modes as well as system mode including both VSYNC and WSYNC modes.                                                                                                                                                                                                                                                                                                                                    |

| MMDC                             | DDR<br>Controller                            | Connectivity<br>Peripherals   | DDR Controller has the following features:<br>• Support 16/32-bit DDR3-800 or LPDDR2-800<br>• Supports up to 2 GByte DDR memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| OCOTP_<br>CTRL                   | OTP<br>Controller                            | Security                      | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>Controller                 | Data Path                     | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module. In i.MX 6SoloLite processor, the OCRAM is used for controlling the 128 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OCRAM_L2                         | On-Chip Memory<br>Controller for<br>L2 Cache | Data Path                     | The On-Chip Memory controller for L2 cache (OCRAM_L2) module is designed as an interface between system's AXI bus and internal (on-chip) L2 cache memory module during boot mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OSC 32 kHz                       | OSC 32 kHz                                   | Clocking                      | Generates 32.768 kHz clock from external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PMU                              | Power<br>Management<br>functions             | Data Path                     | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation                    | Connectivity<br>Peripherals   | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **Modules List**

| Block<br>Mnemonic Block Name |                                    | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------------|------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| РХР                          | PiXel<br>Processing<br>Pipeline    | Display<br>Peripherals        | A high-performance pixel processor capable of 1 pixel/clock performance for<br>combined operations, such as color-space conversion, alpha blending,<br>gamma-mapping, and rotation. The PXP isenhanced with features specifically<br>for gray scale applications. In addition, the PXP supports traditional<br>pixel/frame processing paths for still-image and video processing applications,<br>allowing it to interface with either of the integrated EPD controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| RAM<br>128 KB                | Internal RAM                       | Internal<br>Memory            | Internal RAM, which is accessed through OCRAM memory controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RNGB                         | Random Number<br>Generator         | Security                      | Random number generating module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| ROM<br>96KB                  | Boot ROM                           | Internal<br>Memory            | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ROMCP                        | ROM Controller<br>with Patch       | Data Path                     | ROM Controller with ROM Patch support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SDMA                         | Smart Direct<br>Memory<br>Access   | System Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast Context-Software switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |  |  |  |

| SJC                          | System JTAG<br>Controller          | System Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6SoloLite processor uses JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards.<br>The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6SoloLite SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| SNVS                         | Secure<br>Non-Volatile<br>Storage  | Security                      | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SPDIF                        | Sony Phillips<br>Digital Interface | Multimedia<br>Peripherals     | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. Has Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

### **Modules List**

| Block<br>Mnemonic                        | Block Name                                                                                | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-2<br>uSDHC-2<br>uSDHC-4 | SD/MMC and<br>SDXC<br>Enhanced<br>Multi-Media Card<br>/ Secure Digital<br>Host Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6SoloLite specific SoC characteristics:<br/>All four MMC/SD/SDIO controller IPs are identical and are based on the<br/>uSDHC IP. They are:</li> <li>Conforms to the SD Host Controller Standard Specification version 3.0.</li> <li>Fully compliant with MMC command/response sets and Physical Layer as<br/>defined in the Multimedia Card System Specification, v4.2/4.3/4.4/4.41/4.5<br/>including high-capacity (size &gt; 2 GB) cards HC MMC. Hardware reset as<br/>specified for eMMC cards is supported at ports 3 and 4 only.</li> <li>Fully compliant with SD command/response sets and Physical Layer as<br/>defined in the SD Memory Card Specifications, v3.0 including high-capacity<br/>SDHC cards up to 32 GB and SDXC cards up to 2 TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait<br/>mode as defined in the SDIO Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specifications for SD and SDIO cards up to<br/>UHS-I SDR104 mode (104 MB/s max)</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to<br/>52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>4-bit or 8-bit transfer mode specifications for eMMC chips up to 200 MHz in<br/>HS200 mode (200 MB/s max)</li> <li>However, the SoC level integration and I/O muxing logic restrict the<br/>functionality to the following:</li> <li>Instances 1 and 2 are primarily intended to serve as external slots or<br/>interfaces to on-board SDIO devices. These ports are equipped with "Card<br/>detection" and "Write Protection" pads and do not support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely<br/>independent I/O power domains for Ports 1 and 2 in four bit configuration<br/>(SD interface). Port 3 is placed in an independent power domain and port 4<br/>shares its power domain with other interfaces.</li> </ul> |

| WDOG-1                                   | Watchdog                                                                                  | Timer<br>Peripherals        | The Watchdog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WDOG-2<br>(TZ)                           | Watchdog<br>(TrustZone)                                                                   | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode and<br>forcing a switch to the TZ mode. TZ starvation is a situation where the normal<br>OS prevents switching to the TZ mode. Such situation is undesirable as it can<br>compromise the system's security. Once the TZ WDOG module is activated, it<br>must be serviced by TZ software on a periodic basis. If servicing does not take<br>place, the timer times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode. If it is still not served,<br>the TZ WDOG asserts a security violation signal to the CSU. The TZ WDOG<br>module cannot be programmed or deactivated by a normal mode Software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XTALOSC                                  | Crystal<br>Oscillator I/F                                                                 | Clocking                    | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 10 shows the interface frequency requirements.

Table 10. External Input Clock Frequency

| Parameter Description                | Symbol            | Min | Тур                             | Мах | Unit |

|--------------------------------------|-------------------|-----|---------------------------------|-----|------|

| RTC_XTALI Oscillator <sup>1, 2</sup> | f <sub>ckil</sub> | _   | 32.768 <sup>(see 3)</sup> /32.0 | _   | kHz  |

| XTALI Oscillator <sup>4, 2</sup>     | f <sub>xtal</sub> |     | 24                              |     | MHz  |

<sup>1</sup> External oscillator or a crystal with internal oscillator amplifier.

<sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>3</sup> Recommended nominal frequency 32.768 kHz.

<sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 10 are required for use with NXP BSPs to ensure precise time keeping and USB operation. For RTC\_XTALI operation, two clock sources are available:

- On-chip 40 kHz ring oscillator: This clock source has the following characteristics:

- Approximately 25 µA more Idd than crystal oscillator

- Approximately  $\pm 50\%$  tolerance

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit

- At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

- Higher accuracy than ring oscillator

- If no external crystal is present, then the ring oscillator is utilized

The decision to choose a clock source should be taken based on real-time clock use and precision time-out.

# 4.1.5 Maximum Supply Currents

The Power Virus numbers shown in Table 11 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

The NXP power management IC, MMPF0100xxxx, which is targeted for the i.MX 6 series processor family, supports the power consumption shown in Table 11, however a robust thermal design is required for the increased system power dissipation.

See the *i.MX* 6SoloLite Power Consumption Measurement Application Note (AN4580) for more details on typical power consumption under various use case definitions.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6SoloLite Applications Processors (IMX6SLHDG).

For additional information, see the i.MX 6SoloLite reference manual.

# 4.4 PLL's Electrical Characteristics

# 4.4.1 Audio/Video PLL's Electrical Parameters

### Table 14. Audio/Video PLL's Electrical Parameters

| Parameter          | Value                            |  |  |

|--------------------|----------------------------------|--|--|

| Clock output range | 650 MHz ~1.3 GHz                 |  |  |

| Reference clock    | 24 MHz                           |  |  |

| Lock time          | <11250 reference cycles (450 μs) |  |  |

## 4.4.2 528 MHz PLL

### Table 15. 528 MHz PLL's Electrical Parameters

| Parameter          | Value                           |  |

|--------------------|---------------------------------|--|

| Clock output range | 528 MHz PLL output              |  |

| Reference clock    | 24 MHz                          |  |

| Lock time          | <11250 reference cycles (15 µs) |  |

## 4.4.3 Ethernet PLL

### Table 16. Ethernet PLL's Electrical Parameters

| Parameter          | Value                            |

|--------------------|----------------------------------|

| Clock output range | 500 MHz                          |

| Reference clock    | 24 MHz                           |

| Lock time          | <11250 reference cycles (450 µs) |

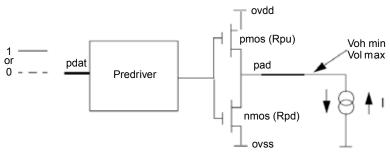

Figure 4. Circuit for Parameters Voh and Vol for I/O Cells

# 4.6.1 XTALI and RTC\_XTALI (Clock Inputs) DC Parameters

Table 20 shows the DC parameters for the clock inputs.

| Parameter                                | Symbol                | Test Conditions                                                                             | Min                | Тур | Мах              | Unit |

|------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------|--------------------|-----|------------------|------|

| XTALI high-level DC input voltage        | Vih                   | _                                                                                           | 0.8 x NVCC_PLL_OUT | —   | NVCC_PLL_OUT     | V    |

| XTALI low-level DC input voltage         | Vil                   | _                                                                                           | 0                  | —   | 0.2V             | V    |

| RTC_XTALI high-level DC<br>input voltage | Vih                   |                                                                                             | 0.8                |     | 1.1 <sup>1</sup> | V    |

| RTC_XTALI low-level DC<br>input voltage  | Vil                   |                                                                                             | 0                  |     | 0.2V             | V    |

| Input capacitance                        | C <sub>IN</sub>       | Simulated data                                                                              | —                  | 5   | _                | pF   |

| XTALI input leakage at startup           | IXTALI_STARTUP        | Power-on startup for<br>0.15 msec with a<br>driven 24 MHz RTC<br>clock @1.1 V. <sup>2</sup> | _                  | _   | 600              | μA   |

| DC input current                         | I <sub>XTALI_DC</sub> | _                                                                                           | —                  | —   | 2.5              | μΑ   |

<sup>1</sup> This voltage specification must not be exceeded and, as such, is an absolute maximum specification.

<sup>2</sup> This current draw is present even if an external clock source directly drives XTALI.

### NOTE

The Vil and Vih specifications only apply when an external clock source is used. If a crystal is used, Vil and Vih do not apply.

# 4.6.2 Dual Voltage General Purpose IO Cell Set (DVGPIO) DC Parameters

Table 21 shows DC parameters for GPIO pads. The parameters in Table 21 are guaranteed per the operating ranges in Table 9, unless otherwise noted.

# 4.9.1 Reset Timings Parameters

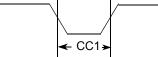

Figure 8 shows the reset timing and Table 31 lists the timing parameters.

SRC\_POR\_B (Input)

Figure 8. Reset Timing Diagram

### Table 31. Reset Timing Parameters

| ID  | Parameter                                   | Min | Max | Unit              |

|-----|---------------------------------------------|-----|-----|-------------------|

| CC1 | Duration of POR_B to be qualified as valid. | 1   |     | XTALOSC_RTC_XTALI |

## 4.9.2 WDOG Reset Timing Parameters

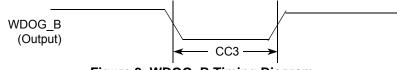

Figure 9 shows the WDOG reset timing and Table 32 lists the timing parameters.

Figure 9. WDOG\_B Timing Diagram

Table 32. WDOG\_B Timing Parameters

| ID  | Parameter                    | Min | Мах | Unit            |

|-----|------------------------------|-----|-----|-----------------|

| CC3 | Duration of WDOG_B Assertion | 1   | —   | RTC_XTALI cycle |

### NOTE

RTC\_XTALI is approximately 32 kHz. RTC\_XTALI cycle is one period or approximately 30  $\mu$ s.

### NOTE

WDOG\_B output signals (for each one of the Watchdog modules) do not have dedicated bins, but are muxed out through the IOMUX. See the IOMUX manual for detailed information.

# 4.9.3.2 General EIM Timing-Synchronous Mode

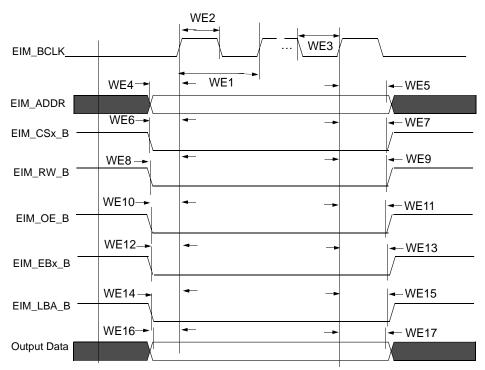

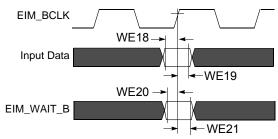

Figure 10, Figure 11, and Table 34 specify the timings related to the EIM module. All EIM output control signals may be asserted and deasserted by an internal clock synchronized to the BCLK rising edge according to corresponding assertion/negation control fields.

Figure 10. EIM Output Timing Diagram

Figure 11. EIM Input Timing Diagram

## 4.9.3.3 Examples of EIM Synchronous Accesses

Table 34. EIM Bus Timing Parameters

| ID  | Parameter                        | Min <sup>1</sup>                     | Max <sup>1</sup>                     | Unit |

|-----|----------------------------------|--------------------------------------|--------------------------------------|------|

| WE1 | EIM_BCLK cycle time <sup>2</sup> | t × (k+1)                            | _                                    | ns   |

| WE2 | EIM_BCLK high level width        | $0.4 \times t \times (k+1)$          | _                                    | ns   |

| WE3 | EIM_BCLK low level width         | $0.4 \times t \times (k+1)$          | _                                    | ns   |

| WE4 | Clock rise to address valid      | -0.5 $\times$ t $\times$ (k+1) -1.25 | -0.5 $\times$ t $\times$ (k+1) +2.25 | ns   |

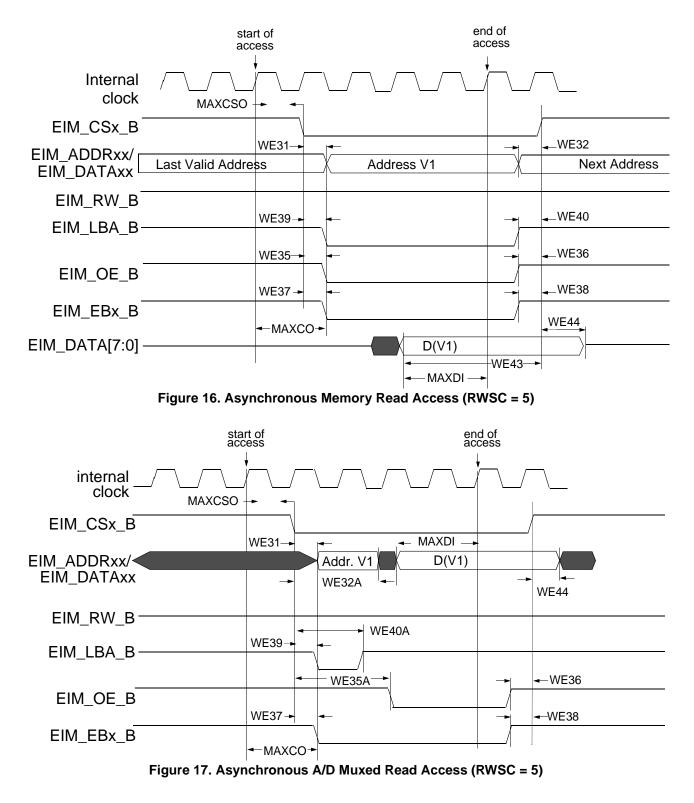

## 4.10.3.2 ECSPI Slave Mode Timing

Figure 26 depicts the timing of ECSPI in slave mode and Table 40 lists the ECSPI slave mode timing characteristics.

Figure 26. ECSPI Slave Mode Timing Diagram

### NOTE

ECSPIx\_MISO is always driven (not tri-stated) between actual data transmissions. This limits the ECSPI to be connected between a single master and a single slave.

| ID  | Parameter                                                               | Symbol              | Min              | Max | Unit |

|-----|-------------------------------------------------------------------------|---------------------|------------------|-----|------|

| CS1 | ECSPIx_SCLK Cycle Time-Read<br>ECSPIx_SCLK Cycle Time-Write             | t <sub>clk</sub>    | 40<br>15         | —   | ns   |

| CS2 | ECSPIx_SCLK High or Low Time-Read<br>ECSPIx_SCLK High or Low Time-Write | t <sub>SW</sub>     | 20<br>7          | —   | ns   |

| CS4 | ECSPIx_SSx pulse width                                                  | t <sub>CSLH</sub>   | Half SCLK period | _   | ns   |

| CS5 | ECSPIx_SSx Lead Time (CS setup time)                                    | t <sub>scs</sub>    | 5                | _   | ns   |

| CS6 | ECSPIx_SSx Lag Time (CS hold time)                                      | t <sub>HCS</sub>    | 5                | _   | ns   |

| CS7 | ECSPIx_MOSI Setup Time                                                  | t <sub>Smosi</sub>  | 4                |     | ns   |

| CS8 | ECSPIx_MOSI Hold Time                                                   | t <sub>Hmosi</sub>  | 4                | _   | ns   |

| CS9 | ECSPIx_MISO Propagation Delay (C <sub>LOAD</sub> = 20 pF)               | t <sub>PDmiso</sub> | 4                | 17  | ns   |

### Table 40. ECSPI Slave Mode Timing Parameters

#### Ultra High Speed SD/SDIO/MMC Host Interface (uSDHC) AC 4.10.4 Timing

This section describes the electrical information of the uSDHC, which includes SD/eMMC4.3 (Single Data Rate) timing and eMMC4.4/4.41 (Dual Date Rate) timing.

#### 4.10.4.1 SD/eMMC4.3 (Single Data Rate) AC Timing Parameters

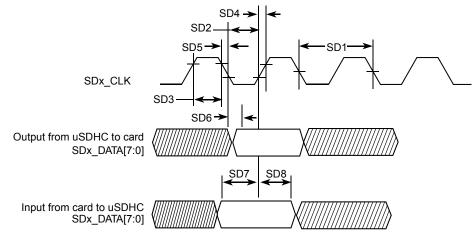

Figure 27 depicts the timing of SD/eMMC4.3, and Table 41 lists the SD/eMMC4.3 timing characteristics.

Figure 27. SD/eMMC4.3 Timing Diagram

| ID      | Parameter                                       | Symbols                      | Min         | Max   | Unit |

|---------|-------------------------------------------------|------------------------------|-------------|-------|------|

|         | Card Input Clock                                | <sup>1</sup>                 |             |       |      |

| SD1     | Clock Frequency (Low Speed)                     | f <sub>PP</sub> <sup>2</sup> | 0           | 400   | kHz  |

|         | Clock Frequency (SD/SDIO Full Speed/High Speed) | f <sub>PP</sub> <sup>3</sup> | 0           | 25/50 | MHz  |

|         | Clock Frequency (MMC Full Speed/High Speed)     | f <sub>PP</sub> <sup>4</sup> | 0           | 20/52 | MHz  |

|         | Clock Frequency (Identification Mode)           | f <sub>OD</sub>              | 100         | 400   | kHz  |

| SD2     | Clock Low Time                                  | t <sub>WL</sub>              | 7           | —     | ns   |

| SD3     | Clock High Time                                 | t <sub>WH</sub>              | 7           | —     | ns   |

|         | eSDHC Output/Card Inputs SDx_CMD, SDx           | _DATAx (Refere               | nce to CLK) | )     |      |

| SD6     | eSDHC Output Delay                              | t <sub>OD</sub>              | -6.6        | 3.6   | ns   |

|         | eSDHC Input/Card Outputs SDx_CMD, SDx           | _DATAx (Refere               | nce to CLK) | )     |      |

| SD7     | eSDHC Input Setup Time                          | t <sub>ISU</sub>             | 2.5         | —     | ns   |

| SD8     | eSDHC Input Hold Time <sup>5</sup>              | t <sub>IH</sub>              | 1.5         | —     | ns   |

| Clock c | luty cycle will be in the range of 47% to 53%.  |                              |             |       |      |

Clock duty cycle will be in the range of 47% to 53%.

<sup>3</sup> In normal (full) speed mode for SD/SDIO card, clock frequency can be any value between 0–25 MHz. In high-speed mode, clock frequency can be any value between 0-50 MHz.

<sup>4</sup> In normal (full) speed mode for MMC card, clock frequency can be any value between 0–20 MHz. In high-speed mode, clock frequency can be any value between 0-52 MHz.

<sup>&</sup>lt;sup>2</sup> In low speed mode, card clock must be lower than 400 kHz, voltage ranges from 2.7 to 3.6 V.

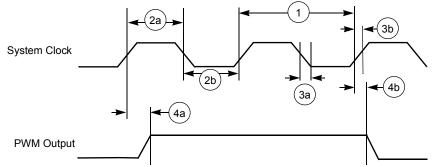

# 4.10.8 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMx\_OUT) external pin (see external signals table in the i.MX 6SoloLite reference manual for PWM pin assignments).

Figure 33 depicts the timing of the PWM, and Table 47 lists the PWM timing parameters.

Figure 33. PWM Timing Diagram

Table 47. PWM Output Timing Parameters

| Reference Number | Parameter                         | Min   | Мах     | Unit |

|------------------|-----------------------------------|-------|---------|------|

| 1                | System CLK frequency <sup>1</sup> | 0     | ipg_clk | MHz  |

| 2a               | Clock high time                   | 12.29 | _       | ns   |

| 2b               | Clock low time                    | 9.91  | _       | ns   |

<sup>1</sup> CL of PWMx\_OUT = 30 pF

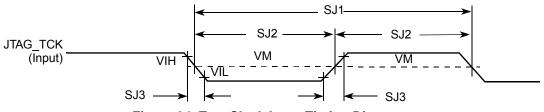

# 4.10.9 SCAN JTAG Controller (SJC) Timing Parameters

Figure 34 depicts the SJC test clock input timing. Figure 35 depicts the SJC boundary scan timing. Figure 36 depicts the SJC test access port. Signal parameters are listed in Table 48.

Figure 34. Test Clock Input Timing Diagram

| ID   | Parameter                      | Min   | Мах | Unit |  |  |  |

|------|--------------------------------|-------|-----|------|--|--|--|

|      | Oversampling Clock Operation   |       |     |      |  |  |  |

| SS47 | Oversampling clock period      | 15.04 |     | ns   |  |  |  |

| SS48 | Oversampling clock high period | 6.0   | _   | ns   |  |  |  |

| SS49 | Oversampling clock rise time   | —     | 3.0 | ns   |  |  |  |

| SS50 | Oversampling clock low period  | 6.0   | _   | ns   |  |  |  |

| SS51 | Oversampling clock fall time   | —     | 3.0 | ns   |  |  |  |

### Table 52. SSI Receiver with Internal Clock Timing Parameters (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TXC/RXC = 0) and a non-inverted frame sync (TXFS/RXFS = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal TXC/RXC and/or the frame sync TXFS/RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of TXD (for example, during AC97 mode of operation).

| Ball Name       | Direction at Reset | eFuse Name   |

|-----------------|--------------------|--------------|

| LCD_DAT19 Input |                    | BOOT_CFG4[3] |

| LCD_DAT20 Input |                    | BOOT_CFG4[4] |

| LCD_DAT21 Input |                    | BOOT_CFG4[5] |

| LCD_DAT22       | Input              | BOOT_CFG4[6] |

| LCD_DAT23 Input |                    | BOOT_CFG4[7] |

Table 62. Fuses and Associated Pins Used for Boot (continued)

<sup>1</sup> Pin value overrides fuse settings for BT\_FUSE\_SEL = '0'. Signal Configuration as Fuse Override Input at Power Up. These are special I/O lines that control the boot up configuration during product development. In production, the boot configuration can be controlled by fuses.

# 5.2 Boot Devices Interfaces Allocation

Table 63 lists the interfaces that can be used by the boot process in accordance with the specific boot mode configuration. The table also describes the interface's specific modes and IOMUXC allocation, which are configured during boot when appropriate.

| Interface | IP Instance | Allocated Ball Names During Boot                                                                                                                                 | Comment                                         |

|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| SPI       | ECSPI-1     | ECSPI1_MISO, ECSPI1_MOSI, ECSPI1_SCLK,<br>ECSPI1_SS0, I2C1_SCL, I2C1_SDA, ECSPI2_SS0                                                                             | _                                               |

| SPI       | ECSPI-2     | ECSPI2_MISO, ECSPI2_MOSI, ECSPI2_SCLK,<br>ECSPI2_SS0, EPDC_SDCE0, EPDC_GDCLK,<br>EPDC_GDOE                                                                       | _                                               |

| SPI       | ECSPI-3     | EPDC_D9, EPDC_D8, EPDC_D11, EPDC_D10,<br>EPDC_D12, EPDC_D13, EPDC_D14                                                                                            | _                                               |

| SPI       | ECSPI-4     | EPDC_D1, EPDC_D0, EPDC_D3, EPDC_D2,<br>EPDC_D2, EPDC_D5, EPDC_D6                                                                                                 | _                                               |

| EIM       | EIM         | LCD_DAT[21:6], KEY_COL[7:0], KEY_ROW[7:0],<br>EPDC_D[15:8], EPDC_VCOM0, EPDC_VCOM1,<br>EPDC_BDR0, EPDC_PWRCTRL[2:0], EPDC_SDCE1                                  | _                                               |

| SD/MMC    | USDHC-1     | Refer to the table "SD/MMC IOMUX Pin Configuration" in<br>the System Boot Chapter of the <b>i.MX 6SoloLite</b><br><b>Applications Processor Reference Manual</b> | 1, 4, or 8 bit Fastboot                         |

| SD/MMC    | USDHC-2     | Refer to the table "SD/MMC IOMUX Pin Configuration" in<br>the System Boot Chapter of the <b>i.MX 6SoloLite</b><br><b>Applications Processor Reference Manual</b> | 1, 4, or 8 bit Fastboot                         |

| SD/MMC    | USDHC-3     | Refer to the table "SD/MMC IOMUX Pin Configuration" in<br>the System Boot Chapter of the <b>i.MX 6SoloLite</b><br><b>Applications Processor Reference Manual</b> | 1, 4, or 8 bit Fastboot<br>(UHSI not supported) |

| SD/MMC    | USDHC-4     | Refer to the table "SD/MMC IOMUX Pin Configuration" in<br>the System Boot Chapter of the <b>i.MX 6SoloLite</b><br><b>Applications Processor Reference Manual</b> | 1, 4, or 8 bit Fastboot                         |

| I2C       | I2C-1       | 12C1_SCL, 12C1_SDA                                                                                                                                               | —                                               |

Table 63. Interfaces Allocation During Boot

|                    |      | -                        |           |                                    |                  |                       |                    |  |  |

|--------------------|------|--------------------------|-----------|------------------------------------|------------------|-----------------------|--------------------|--|--|

|                    |      |                          |           |                                    | Out of Reset C   | ondition <sup>2</sup> |                    |  |  |

| Ball Name          | Ball | Power Group <sup>1</sup> | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function | Input/Output          | Value <sup>3</sup> |  |  |

| EPDC_D15           | A13  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[22]   | Input                 | Keeper             |  |  |

| EPDC_D2            | B17  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[9]    | Input                 | Keeper             |  |  |

| EPDC_D3            | A16  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[10]   | Input                 | Keeper             |  |  |

| EPDC_D4            | B16  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[11]   | Input                 | Keeper             |  |  |

| EPDC_D5            | A15  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[12]   | Input                 | Keeper             |  |  |

| EPDC_D6            | B15  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[13]   | Input                 | Keeper             |  |  |

| EPDC_D7            | C15  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[14]   | Input                 | Keeper             |  |  |

| EPDC_D8            | D15  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[15]   | Input                 | Keeper             |  |  |

| EPDC_D9            | F15  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[16]   | Input                 | Keeper             |  |  |

| EPDC_GDCLK         | A12  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[31]   | Input                 | Keeper             |  |  |

| EPDC_GDOE          | B13  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[0]    | Input                 | Keeper             |  |  |

| EPDC_GDRL          | B12  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[1]    | Input                 | Keeper             |  |  |

| EPDC_GDSP          | A11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[2]    | Input                 | Keeper             |  |  |

| EPDC_PWRCOM        | B11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[11]   | Input                 | Keeper             |  |  |

| EPDC_PWRCTRL0      | D11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[7]    | Input                 | Keeper             |  |  |

| EPDC_PWRCTRL1      | E11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[8]    | Input                 | Keeper             |  |  |

| EPDC_PWRCTRL2      | F11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[9]    | Input                 | Keeper             |  |  |

| EPDC_PWRCTRL3      | G12  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[10]   | Input                 | Keeper             |  |  |

| EPDC_PWRINT        | F10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[12]   | Input                 | Keeper             |  |  |

| EPDC_PWRSTAT       | E10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[13]   | Input                 | Keeper             |  |  |

| EPDC_PWRWAKEU<br>P | D10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[14]   | Input                 | Keeper             |  |  |

| EPDC_SDCE0         | C11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[27]   | Input                 | Keeper             |  |  |

Table 66. 13 x 13 mm Functional Contact Assignments (continued)

|             |      |                          |           |                                    | Out of Reset C   | ondition <sup>2</sup> |                    |

|-------------|------|--------------------------|-----------|------------------------------------|------------------|-----------------------|--------------------|

| Ball Name   | Ball | Power Group <sup>1</sup> | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function | Input/Output          | Value <sup>3</sup> |

| EPDC_SDCE1  | A10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[28]   | Input                 | Keeper             |

| EPDC_SDCE2  | B9   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[29]   | Input                 | Keeper             |

| EPDC_SDCE3  | A9   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[30]   | Input                 | Keeper             |

| EPDC_SDCLK  | B10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[23]   | Input                 | Keeper             |

| EPDC_SDLE   | B8   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[24]   | Input                 | Keeper             |

| EPDC_SDOE   | E7   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[25]   | Input                 | Keeper             |

| EPDC_SDSHR  | F7   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO1_GPIO[26]   | Input                 | Keeper             |

| EPDC_VCOM0  | C7   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[3]    | Input                 | Keeper             |

| EPDC_VCOM1  | D7   | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO2_GPIO[4]    | Input                 | Keeper             |

| FEC_CRS_DV  | AC9  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[25]   | Input                 | Keeper             |

| FEC_MDC     | AA7  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[23]   | Input                 | Keeper             |

| FEC_MDIO    | AB7  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[20]   | Input                 | Keeper             |

| FEC_REF_CLK | W10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[26]   | Input                 | Keeper             |

| FEC_RX_ER   | AD9  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[19]   | Input                 | Keeper             |

| FEC_RXD0    | AA10 | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[17]   | Input                 | Keeper             |

| FEC_RXD1    | AC10 | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[18]   | Input                 | Keeper             |

| FEC_TX_CLK  | AC8  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[21]   | Input                 | Keeper             |

| FEC_TX_EN   | AD10 | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[22]   | Input                 | Keeper             |

| FEC_TXD0    | Y10  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[24]   | Input                 | Keeper             |

| FEC_TXD1    | W11  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                               | GPIO4_GPIO[16]   | Input                 | Keeper             |

| HSIC_DAT    | AA6  | NVCC_1P2V                | DDR       | —                                  | USB_H_DATA       | Input                 | PD (100K)          |

| HSIC_STROBE | AB6  | NVCC_1P25                | DDR       | —                                  | USB_H_STROBE     | Input                 | PD (100K)          |

Table 66. 13 x 13 mm Functional Contact Assignments (continued)

|            |      |                          |           | Out of Reset Condition <sup>2</sup> |                  |              |                    |  |  |  |  |

|------------|------|--------------------------|-----------|-------------------------------------|------------------|--------------|--------------------|--|--|--|--|

| Ball Name  | Ball | Power Group <sup>1</sup> | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/Output | Value <sup>3</sup> |  |  |  |  |

| I2C1_SCL   | AC13 | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[12]   | Input        | Keeper             |  |  |  |  |

| I2C1_SDA   | AD13 | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[13]   | Input        | Keeper             |  |  |  |  |

| I2C2_SCL   | E18  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[14]   | Input        | Keeper             |  |  |  |  |

| I2C2_SDA   | D18  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[15]   | Input        | Keeper             |  |  |  |  |

| JTAG_MOD   | Y14  | NVCC33_IO                | GPIO      | ALT5                                | JTAG_MODE        |              | PU (100K)          |  |  |  |  |

| JTAG_TCK   | AA14 | NVCC33_IO                | GPIO      | ALT5                                | JTAG_TCK         | _            | PU (47K)           |  |  |  |  |

| JTAG_TDI   | W14  | NVCC33_IO                | GPIO      | ALT5                                | JTAG_TDI         | _            | PU (47K)           |  |  |  |  |

| JTAG_TDO   | W15  | NVCC33_IO                | GPIO      | ALT5                                | JTAG_TDO         | _            | Keeper             |  |  |  |  |

| JTAG_TMS   | Y15  | NVCC33_IO                | GPIO      | ALT5                                | JTAG_TMS         | _            | PU (47K)           |  |  |  |  |

| JTAG_TRSTB | AA15 | NVCC33_IO                | GPIO      | ALT5                                | JTAG_TRSTB       | —            | PU (47K)           |  |  |  |  |

| KEY_COL0   | G23  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[24]   | Input        | Keeper             |  |  |  |  |

| KEY_COL1   | F23  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[26]   | Input        | Keeper             |  |  |  |  |

| KEY_COL2   | E23  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[28]   | Input        | Keeper             |  |  |  |  |

| KEY_COL3   | E22  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[30]   | Input        | Keeper             |  |  |  |  |

| KEY_COL4   | E20  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO4_GPIO[0]    | Input        | Keeper             |  |  |  |  |

| KEY_COL5   | D24  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO4_GPIO[2]    | Input        | Keeper             |  |  |  |  |

| KEY_COL6   | D22  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO4_GPIO[4]    | Input        | Keeper             |  |  |  |  |

| KEY_COL7   | C23  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO4_GPIO[6]    | Input        | Keeper             |  |  |  |  |

| KEY_ROW0   | G24  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[25]   | Input        | Keeper             |  |  |  |  |

| KEY_ROW1   | F24  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[27]   | Input        | Keeper             |  |  |  |  |

| KEY_ROW2   | E24  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[29]   | Input        | Keeper             |  |  |  |  |

| KEY_ROW3   | E21  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO3_GPIO[31]   | Input        | Keeper             |  |  |  |  |

| KEY_ROW4   | E19  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO4_GPIO[1]    | Input        | Keeper             |  |  |  |  |

| KEY_ROW5   | D23  | NVCC33_IO<br>NVCC18_IO   | GPIO      | ALT5                                | GPIO4_GPIO[3]    | Input        | Keeper             |  |  |  |  |

Table 66. 13 x 13 mm Functional Contact Assignments (continued)

|   | ۲            | ш          | U          | ۵          | ш           | ш            | G         | т          | ٦                       | ×                       | -            | Σ              | z         | ٩         | Ľ                     | ⊢                     | <b>D</b>  | >         | ≥            | ≻           | AA       | AB          | AC            | AD           |

|---|--------------|------------|------------|------------|-------------|--------------|-----------|------------|-------------------------|-------------------------|--------------|----------------|-----------|-----------|-----------------------|-----------------------|-----------|-----------|--------------|-------------|----------|-------------|---------------|--------------|

| æ | DRAM_D31     | EPDC_SDLE  | NC         | NC         | NC          | NC           | GND       | NC         | VDD_SOC_CAP VDD_SOC_CAP | VDD_SOC_CAP VDD_SOC_CAP | NC           | GND            | GND       | NC        | VDD_PU_CAP VDD_PU_CAP | VDD_PU_CAP VDD_PU_CAP | NC        | GND       | NC           | NC          | NC       | NC          | FEC_TX_CLK AC | DRAM_D16     |

| 7 | GND          | DRAM_D30   | EPDC_VCOM0 | EPDC_VCOM1 | EPDC_SDOE   | EPDC_SDSHR   | NVCC_DRAM | GND        | VDD_SOC_CAP             | VDD_SOC_CAP             | GND          | GND            | GND       | NVCC_DRAM | VDD_PU_CAP            | VDD_PU_CAP            | GND       | NVCC_DRAM | NVCC_1P2     | PWM1        | FEC_MDC  | FEC_MDIO    | DRAM_D17      | GND          |

| 9 | DRAM_D29     | DRAM_D28   | GND        | DRAM_RESET | NVCC_DRAM   | NC           | NC        | NVCC_DRAM  | NVCC_DRAM               | NC                      | NC           | NVCC_DRAM_2P5  | NVCC_DRAM | NC        | NC                    | NVCC_DRAM             | NVCC_DRAM | NC        | NC           | NVCC_DRAM   | HSIC_DAT | HSIC_STROBE | DRAM_D19      | DRAM_D18     |

| 5 | DRAM_D27     | DRAM_D26   | NC         | NC         | GND         | NC           | NC        | DRAM_A13   | GND                     | NC                      | NC           | GND            | DRAM_VREF | NC        | NC                    | GND                   | DRAM_A1   | NC        | NC           | GND         | NC       | NC          | DRAM_D21      | DRAM_D20     |

| 4 | GND          | DRAM_D25   | NC         | NC         | DRAM_SDODT1 | NC           | NC        | DRAM_A7    | DRAM_A9                 | NC                      | NC           | DRAM_A6        | DRAM_A4   | NC        | NC                    | DRAM_A3               | DRAM_A0   | NC        | NC           | DRAM_SDODT0 | NC       | NC          | DRAM_D22      | GND          |

| 3 | DRAM_D24     | DRAM_SDQS3 | DRAM_DQM3  | DRAM_D11   | DRAM_D10    | NC           | NC        | GND        | DRAM_A8                 | NC                      | NC           | DRAM_A5        | GND       | NC        | NC                    | DRAM_A2               | GND       | NC        | NC           | DRAM_D5     | DRAM_D4  | DRAM_DQM2   | DRAm_SDQS2    | DRAM_D23     |

| 2 | DRAM_SDQS3_B | DRAM_D15   | DRAM_D13   | GND        | DRAM_D8     | DRAM_SDQS1_B | DRAM_DQM1 | ZQPAD      | DRAM_A10                | DRAM_A15                | DRAM_CS1     | DRAM_SDCKE1    | DRAM_CS0  | SDCKE0    | DRAM_A14              | DRAM_A11              | DRAM_A12  | DRAM_DQM0 | DRAM_SDQS0   | DRAM_D7     | GND      | DRAM_D2     | DRAM_D0       | DRAM_SDQS2_B |