#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

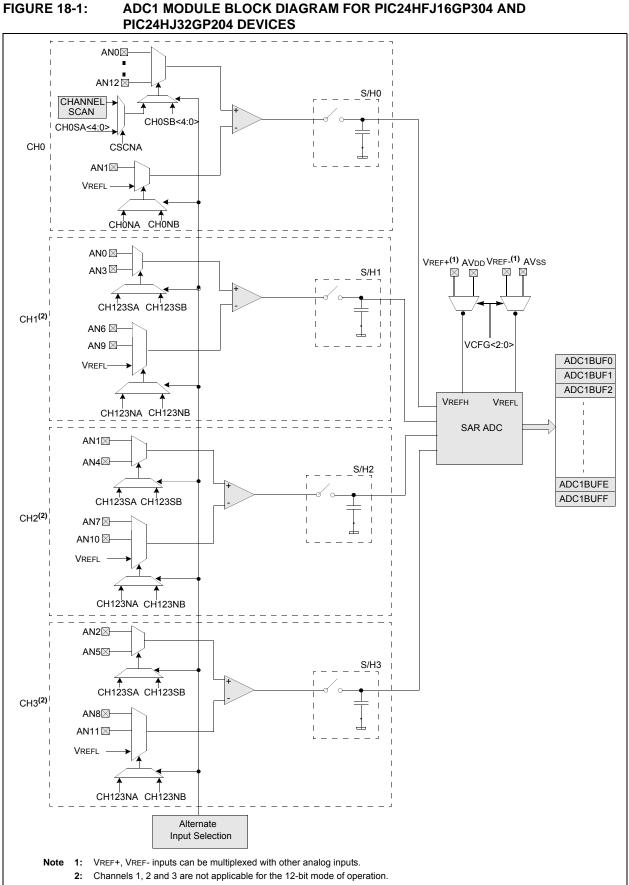

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj16gp304-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### PIC24HJ32GP202/204 and PIC24HJ16GP304 Product Families

The device names, pin counts, memory sizes and peripheral availability of each family are listed in Table 1, followed by their pinout diagrams.

| TABLE I. TIC   | 24110 |                                  |     |                 | 1.102        |               | 01 30                          |        |                                    |     |                 |      | r                  |                                |

|----------------|-------|----------------------------------|-----|-----------------|--------------|---------------|--------------------------------|--------|------------------------------------|-----|-----------------|------|--------------------|--------------------------------|

|                |       | 2rV                              |     |                 | Re           | mappa         | ble Pe                         | ripher | als                                |     |                 |      | (                  |                                |

| Device         | Pins  | Program Flash Memory<br>(Kbytes) | MAA | Remappable Pins | 16-bit Timer | Input Capture | Output Compare<br>Standard PWM | UART   | External Interrupts <sup>(2)</sup> | IdS | 10/12-bit ADC   | I²C™ | l/O Pins (Maximum) | Packages                       |

| PIC24HJ32GP202 | 28    | 32                               | 2   | 16              | 3(1)         | 4             | 2                              | 1      | 3                                  | 1   | 1 ADC,<br>10 ch | 1    | 21                 | SPDIP<br>SOIC<br>SSOP<br>QFN-S |

| PIC24HJ32GP204 | 44    | 32                               | 2   | 26              | 3(1)         | 4             | 2                              | 1      | 3                                  | 1   | 1 ADC,<br>13 ch | 1    | 35                 | QFN<br>TQFP                    |

| PIC24HJ16GP304 | 44    | 16                               | 2   | 26              | 3(1)         | 4             | 2                              | 1      | 3                                  | 1   | 1 ADC,<br>13 ch | 1    | 35                 | QFN<br>TQFP                    |

## TABLE 1: PIC24HJ32GP202/204 AND PIC24HJ16GP304 CONTROLLER FAMILIES

**Note 1:** Only two out of three timers are remappable.

**2:** Only two out of three interrupts are remappable.

| FIGURE 3-2: PIC24HJ32GP202/ | 204 AND PIC24HJ160          | SP304 PROGRAMMER'S MODEL     |

|-----------------------------|-----------------------------|------------------------------|

|                             | D15                         | D0                           |

|                             | W0/WREG                     | PUSH.S Shadow                |

|                             | W1                          |                              |

|                             | W2                          | DO Shadow                    |

|                             | W3                          | Legend                       |

|                             | W4                          |                              |

|                             | W5                          |                              |

|                             | W6                          |                              |

|                             | W7                          | Working Registers            |

|                             | W8                          |                              |

|                             | W9                          |                              |

|                             | W10                         |                              |

|                             | W11                         |                              |

|                             | W12                         |                              |

|                             | W13                         |                              |

|                             | W14/Frame Pointe            |                              |

|                             | W15/Stack Pointe            | r )                          |

|                             |                             |                              |

|                             | SPLIM                       | Stack Pointer Limit Register |

|                             |                             |                              |

| PC22                        |                             | PC0_                         |

|                             |                             | 0 Program Counter            |

| 7 0                         |                             |                              |

| TBLPAG Data Table           | Page Address                |                              |

|                             |                             |                              |

| 7 0<br>PSVPAG Program       | m Shaqo Vicibility Dago Add | r000                         |

| F3VFAG Plogram              | m Space Visibility Page Add | Tess                         |

|                             | 15                          | 0                            |

|                             | RCOUNT                      | REPEAT Loop Counter          |

|                             |                             |                              |

|                             | 15                          | 0                            |

|                             | CORCON                      | Core Configuration Register  |

|                             | L                           |                              |

|                             |                             |                              |

|                             | C IPL2 IPL1 IPL0 RA         | N OV Z C STATUS Register     |

| ✓ SRH                       | ► < SRL-                    |                              |

|                             |                             | -                            |

|                             |                             |                              |

|                             |                             |                              |

|                             |                             |                              |

|                             |                             |                              |

| L                           |                             |                              |

| R/W-0         | U-0                                                                                                                                                                                                | U-0                                                    | U-0                               | U-0               | U-0              | U-0              | U-0   |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|-------------------|------------------|------------------|-------|

| NSTDIS        |                                                                                                                                                                                                    | _                                                      |                                   |                   |                  |                  | _     |

| bit 15        |                                                                                                                                                                                                    |                                                        |                                   |                   |                  |                  | bit 8 |

|               |                                                                                                                                                                                                    |                                                        |                                   |                   |                  |                  |       |

| U-0           | R/W-0                                                                                                                                                                                              | U-0                                                    | R/W-0                             | R/W-0             | R/W-0            | R/W-0            | U-0   |

| _             | DIV0ERR                                                                                                                                                                                            |                                                        | MATHERR                           | ADDRERR           | STKERR           | OSCFAIL          |       |

| bit 7         |                                                                                                                                                                                                    |                                                        |                                   |                   |                  |                  | bit C |

| Legend:       |                                                                                                                                                                                                    |                                                        |                                   |                   |                  |                  |       |

| R = Readable  | e bit                                                                                                                                                                                              | W = Writable                                           | bit                               | U = Unimplem      | nented bit, read | l as '0'         |       |

| -n = Value at | POR                                                                                                                                                                                                | '1' = Bit is set                                       | t                                 | '0' = Bit is clea | ared             | x = Bit is unkno | own   |

| bit 15        | 1 = Interrupt r                                                                                                                                                                                    | rrupt Nesting E<br>nesting is disat<br>nesting is enat | bled                              |                   |                  |                  |       |

| bit 14-7      | Unimplemen                                                                                                                                                                                         | ted: Read as '                                         | 0'                                |                   |                  |                  |       |

| bit 6         | DIV0ERR: Ar                                                                                                                                                                                        | ithmetic Error                                         | Status bit                        |                   |                  |                  |       |

|               |                                                                                                                                                                                                    |                                                        | sed by a divide<br>caused by a di |                   |                  |                  |       |

| bit 5         | Unimplemen                                                                                                                                                                                         | ted: Read as '                                         | 0'                                |                   |                  |                  |       |

| bit 4         | 1 = Math erro                                                                                                                                                                                      | rithmetic Erron<br>r trap has occu<br>r trap has not o | urred                             |                   |                  |                  |       |

| bit 3         | 1 = Address e                                                                                                                                                                                      | Address Error <sup>-</sup><br>error trap has c         | occurred                          |                   |                  |                  |       |

| bit 2         | <ul> <li>0 = Address error trap has not occurred</li> <li>STKERR: Stack Error Trap Status bit</li> <li>1 = Stack error trap has occurred</li> <li>0 = Stack error trap has not occurred</li> </ul> |                                                        |                                   |                   |                  |                  |       |

| bit 1         | OSCFAIL: Oscillator Failure Trap Status bit<br>1 = Oscillator failure trap has occurred<br>0 = Oscillator failure trap has not occurred                                                            |                                                        |                                   |                   |                  |                  |       |

|               | 0 = Oscillator failure trap has not occurred<br>Unimplemented: Read as '0'                                                                                                                         |                                                        |                                   |                   |                  |                  |       |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0         | R-0                                                                                                                      | U-0               | U-0           | U-0              | U-0             | U-0             | U-0              |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|------------------|-----------------|-----------------|------------------|--|

| ALTIVT        | DISI                                                                                                                     | —                 | —             | —                | —               | —               | —                |  |

| bit 15        |                                                                                                                          |                   |               |                  |                 |                 | bit 8            |  |

|               |                                                                                                                          |                   |               |                  |                 |                 |                  |  |

| U-0           | U-0                                                                                                                      | U-0               | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0            |  |

| —             | —                                                                                                                        | —                 | —             | —                | INT2EP          | INT1EP          | INT0EP           |  |

| bit 7         |                                                                                                                          |                   |               |                  |                 |                 | bit (            |  |

|               |                                                                                                                          |                   |               |                  |                 |                 |                  |  |

| Legend:       |                                                                                                                          |                   |               |                  |                 |                 |                  |  |

| R = Readabl   | e bit                                                                                                                    | W = Writable      | bit           | U = Unimple      | mented bit, rea | d as '0'        |                  |  |

| -n = Value at | POR                                                                                                                      | '1' = Bit is set  |               | '0' = Bit is cle | eared           | x = Bit is unki | = Bit is unknown |  |

|               |                                                                                                                          |                   |               |                  |                 |                 |                  |  |

| bit 15        | ALTIVT: Enat                                                                                                             | ole Alternate Int | terrupt Vecto | r Table bit      |                 |                 |                  |  |

|               |                                                                                                                          | nate vector tabl  |               |                  |                 |                 |                  |  |

|               |                                                                                                                          | lard (default) ve |               |                  |                 |                 |                  |  |

| bit 14        |                                                                                                                          | struction Status  |               |                  |                 |                 |                  |  |

|               |                                                                                                                          | ruction is active | -             |                  |                 |                 |                  |  |

| h:+ 40 0      |                                                                                                                          | ruction is not a  |               |                  |                 |                 |                  |  |

| bit 13-3      | -                                                                                                                        | ted: Read as '    |               |                  |                 |                 |                  |  |

| bit 2         |                                                                                                                          |                   | •             | t Polarity Selec | t bit           |                 |                  |  |

|               |                                                                                                                          | on negative edg   |               |                  |                 |                 |                  |  |

| bit 1         | •                                                                                                                        |                   |               | t Polarity Selec | + hit           |                 |                  |  |

| DILI          |                                                                                                                          | on negative edg   | •             | t Polarity Selec |                 |                 |                  |  |

|               |                                                                                                                          |                   | -             |                  |                 |                 |                  |  |

| bit 0         | <ul> <li>0 = Interrupt on positive edge</li> <li>INTOEP: External Interrupt 0 Edge Detect Polarity Select bit</li> </ul> |                   |               |                  |                 |                 |                  |  |

|               |                                                                                                                          | •                 | •             |                  |                 |                 |                  |  |

|               | <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul>                               |                   |               |                  |                 |                 |                  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0           | U-0                                                        | U-0                                   | U-0            | U-0                                     | U-0      | U-0 | U-0   |  |  |

|---------------|------------------------------------------------------------|---------------------------------------|----------------|-----------------------------------------|----------|-----|-------|--|--|

|               | —                                                          | _                                     |                | —                                       | _        | _   |       |  |  |

| bit 15        |                                                            |                                       |                |                                         |          |     | bit 8 |  |  |

|               |                                                            |                                       |                |                                         |          |     |       |  |  |

| U-0           | R/W-1                                                      | R/W-0                                 | R/W-0          | U-0                                     | U-0      | U-0 | U-0   |  |  |

|               |                                                            | U1EIP<2:0>                            |                | <u> </u>                                | <u> </u> |     |       |  |  |

| bit 7         |                                                            |                                       |                |                                         |          |     | bit 0 |  |  |

| r             |                                                            |                                       |                |                                         |          |     |       |  |  |

| Legend:       |                                                            |                                       |                |                                         |          |     |       |  |  |

| R = Readabl   | e bit                                                      | W = Writable b                        | pit            | U = Unimplemented bit, read as '0'      |          |     |       |  |  |

| -n = Value at | POR                                                        | '1' = Bit is set                      |                | '0' = Bit is cleared x = Bit is unknown |          |     |       |  |  |

|               |                                                            |                                       |                |                                         |          |     |       |  |  |

| bit 15-7      | Unimplemen                                                 | ted: Read as '0                       | )'             |                                         |          |     |       |  |  |

| bit 6-4       | U1EIP<2:0>:                                                | UART1 Error Ir                        | nterrupt Prior | ity bits                                |          |     |       |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt) |                                       |                |                                         |          |     |       |  |  |

|               |                                                            |                                       |                |                                         |          |     |       |  |  |

|               | •                                                          |                                       |                |                                         |          |     |       |  |  |

|               | •                                                          |                                       |                |                                         |          |     |       |  |  |

|               | •<br>•<br>001 = Interrut                                   | ot is priority 1                      |                |                                         |          |     |       |  |  |

|               | •<br>•<br>001 = Interrup<br>000 = Interrup                 | ot is priority 1<br>ot source is disa | abled          |                                         |          |     |       |  |  |

| bit 3-0       | 000 = Interrup                                             |                                       |                |                                         |          |     |       |  |  |

#### REGISTER 7-18: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

#### 8.4 Clock Switching Operation

Applications are free to switch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, devices have a safeguard lock built into the switch process.

| Note: | Primary Oscillator mode has three different |

|-------|---------------------------------------------|

|       | submodes (XT, HS and EC), which are         |

|       | determined by the POSCMD<1:0>               |

|       | Configuration bits. While an application    |

|       | can switch to and from Primary Oscillator   |

|       | mode in software, it cannot switch among    |

|       | the different primary submodes without      |

|       | reprogramming the device.                   |

#### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 19.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 8.4.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires the following basic sequence:

- Read the COSC bits (OSCCON<14:12>) to determine the current oscillator source, if desired.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If both of them are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the status bits, LOCK (OSCCON<5>) and CF (OSCCON<3>) are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator has to be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRC-PLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

#### 8.5 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

## 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 9. Watchdog Timer and Power Savings Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJ32GP202/204 and PIC24HJ16GP304 devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- · Software-controlled Doze mode

- · Selective peripheral control in software

Combinations of the above methods can be used to selectively customize an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0** "Oscillator **Configuration**".

#### 9.2 Instruction-Based Power-Saving Modes

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Example 9-1 shows the Assembler syntax of the PWRSAV instruction.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

#### 9.2.1 SLEEP MODE

In the Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

| R/W-0                                           | R/W-0                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0 | U-0              | U-0             | R/W-0           | R/W-0 |  |  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-----------------|-----------------|-------|--|--|

| IC8MD                                           | IC7MD                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                             | _   | _                | _               | IC2MD           | IC1MD |  |  |

| bit 15                                          |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                  |                 |                 | bit 8 |  |  |

| U-0                                             | U-0                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0 | U-0              | U-0             | R/W-0           | R/W-0 |  |  |

|                                                 | 0-0                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                             | 0-0 | 0-0              | 0-0             | OC2MD           | OC1MD |  |  |

| bit 7                                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                  |                 | COLIND          | bit ( |  |  |

| Legend:                                         |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                  |                 |                 |       |  |  |

| R = Readab                                      | le bit                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                | bit | U = Unimplen     | nented bit, rea | ad as '0'       |       |  |  |

| -n = Value a                                    | It POR                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                            |     | '0' = Bit is cle |                 | x = Bit is unkr | nown  |  |  |

| bit 15<br>bit 14<br>bit 13-10<br>bit 9<br>bit 8 | 1 = Input Cap<br>0 = Input Cap<br>IC7MD: Input<br>1 = Input Cap<br>0 = Input Cap<br>Unimplemen<br>IC2MD: Input<br>1 = Input Cap<br>0 = Input Cap | IC8MD: Input Capture 8 Module Disable bit<br>1 = Input Capture 8 module is disabled<br>0 = Input Capture 8 module is enabled<br>IC7MD: Input Capture 2 Module Disable bit<br>1 = Input Capture 7 module is disabled<br>0 = Input Capture 7 module is enabled<br>Unimplemented: Read as '0'<br>IC2MD: Input Capture 2 Module Disable bit<br>1 = Input Capture 2 module is disabled<br>0 = Input Capture 2 module is disabled |     |                  |                 |                 |       |  |  |

|                                                 | 1 = Input Cap<br>0 = Input Cap                                                                                                                   | IC1MD: Input Capture 1 Module Disable bit<br>1 = Input Capture 1 module is disabled<br>0 = Input Capture 1 module is enabled                                                                                                                                                                                                                                                                                                |     |                  |                 |                 |       |  |  |

| bit 7-2                                         | -                                                                                                                                                | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                              |     |                  |                 |                 |       |  |  |

| bit 1                                           | 1 = Output C                                                                                                                                     | <b>OC2MD:</b> Output Compare 2 Module Disable bit<br>1 = Output Compare 2 module is disabled<br>0 = Output Compare 2 module is enabled                                                                                                                                                                                                                                                                                      |     |                  |                 |                 |       |  |  |

| bit 0                                           | 1 = Output C                                                                                                                                     | <b>OC1MD:</b> Output Compare 1 Module Disable bit<br>1 = Output Compare 1 module is disabled<br>0 = Output Compare 1 module is enabled                                                                                                                                                                                                                                                                                      |     |                  |                 |                 |       |  |  |

#### TABLE 10-1:REMAPPABLE PERIPHERAL INPUTS<sup>(1)</sup>

| Input Name               | Function Name | Register | Configuration<br>Bits |

|--------------------------|---------------|----------|-----------------------|

| External Interrupt 1     | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2     | INT2          | RPINR1   | INT2R<4:0>            |

| Timer 2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer 3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Input Capture 1          | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2          | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7          | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8          | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A   | OCFA          | RPINR11  | OCFAR<4:0>            |

| UART 1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART 1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| SPI 1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI 1 Clock Input        | SCK1IN        | RPINR20  | SCK1R<4:0>            |

| SPI 1 Slave Select Input | SS1IN         | RPINR21  | SS1R<4:0>             |

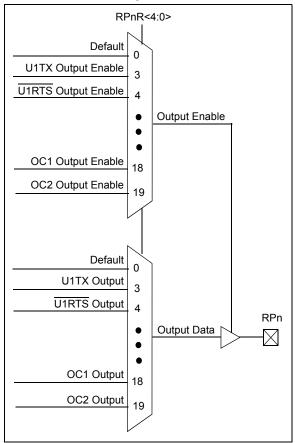

**FIGURE 10-3:**

**Note 1:** Unless otherwise noted, all inputs use the Schmitt input buffers.

#### 10.6.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 10-10 through Register 10-22). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

### MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPn

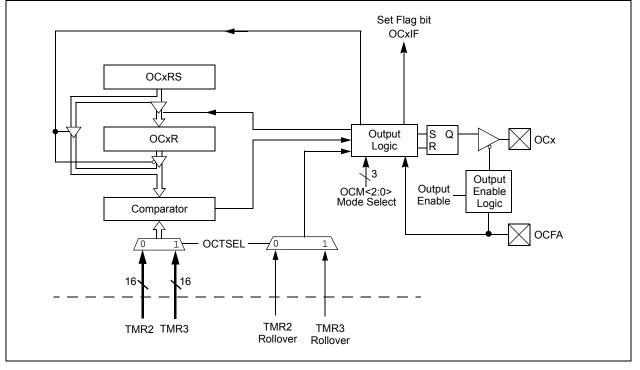

## 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 13. Output Compare" (DS70209) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

#### FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

#### REGISTER 15-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- **Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both Primary and Secondary prescalers to a value of 1:1.

## 17.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, receive inputs react UART to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 17.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530271

#### 17.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### 19.4 Watchdog Timer (WDT)

For PIC24HJ32GP202/204 and PIC24HJ16GP304 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 19.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allows the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- · On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (Sleep or Idle mode is entered)

- · When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### WDT BLOCK DIAGRAM All Device Resets Transition to New Clock Source Exit Sleep or Idle Mode PWRSAV Instruction CLRWDT Instruction Watchdog Timer Sleep/Idle WDTPOST<3:0> WDTPRE SWDTEN WDT Wake-up FWDTEN 1 RS Prescaler Postscaler WDT LPRC Clock (divide by N1) (divide by N2) 0 Reset WDT Window Select WINDIS CLRWDT Instruction

#### **FIGURE 19-2:**

#### SLEEP AND IDLE MODES 19.4.2

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3.2>) will need to be cleared in software after the device wakes up.

#### 19.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

If the WINDIS bit (FWDT<6>) is cleared, Note: the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

NOTES:

## 21.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 21.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- · A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### 21.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 21.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 21.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 21.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| DC CHARACTERISTICS |                                                                                                      |                                                                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |                                   |                                                                                                      |

|--------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------------------------|------------------------------------------------------------------------------------------------------|

| Param.             | Symbol                                                                                               | Characteristic                                                                                                 | Min.                                                                                                                                                                                                                                                                                   | Тур. | Max. | Units                             | Conditions                                                                                           |

|                    |                                                                                                      | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - All pins not<br>defined by 4x or 8x driver pins       | _                                                                                                                                                                                                                                                                                      | _    | 0.4  | V                                 | Iol $\leq$ 3 mA, Vdd = 3.3V                                                                          |

| DO10               | Vol                                                                                                  | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA0, RA1,<br>RB5, RB6, RB8, RB9, RB14                 | _                                                                                                                                                                                                                                                                                      | _    | 0.4  | v                                 | $\text{IOL} \leq 6 \text{ mA, VDD} = 3.3 \text{V}$                                                   |

|                    |                                                                                                      | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - OSCO,<br>CLKO, RA3                                    | _                                                                                                                                                                                                                                                                                      | _    | 0.4  | v                                 | Iol $\leq$ 10 mA, Vdd = 3.3V                                                                         |

|                    |                                                                                                      | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins<br>not defined by 4x or 8x driver<br>pins | 2.4                                                                                                                                                                                                                                                                                    | _    | _    | V                                 | Iol $\geq$ -3 mA, Vdd = 3.3V                                                                         |

| DO20 Voн           | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA0,<br>RA1, RB5, RB6, RB8, RB9,<br>RB14 | 2.4                                                                                                            | _                                                                                                                                                                                                                                                                                      | _    | v    | $IOL \geq -6 \ mA, \ VDD = 3.3 V$ |                                                                                                      |

|                    | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - OSCO,<br>CLKO, RA3                       | 2.4                                                                                                            | _                                                                                                                                                                                                                                                                                      | _    | V    | IOL $\ge$ -10 mA, VDD = 3.3V      |                                                                                                      |

|                    |                                                                                                      | Output High Voltage<br>I/O Pins:                                                                               | 1.5                                                                                                                                                                                                                                                                                    | _    | _    |                                   | $\begin{array}{l} \text{IOH} \geq \text{-6 mA, VDD} = 3.3 \text{V} \\ \text{See Note 1} \end{array}$ |

|                    |                                                                                                      | 2x Source Driver Pins - All pins<br>not defined by 4x or 8x driver<br>pins                                     | 2.0                                                                                                                                                                                                                                                                                    | _    | _    | V                                 | IOH ≥ -5 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |

|                    |                                                                                                      | pins                                                                                                           | 3.0                                                                                                                                                                                                                                                                                    | _    | _    |                                   | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |

|                    |                                                                                                      | <b>Output High Voltage</b><br>4x Source Driver Pins - RA0,                                                     | 1.5                                                                                                                                                                                                                                                                                    | _    | _    |                                   | Іон ≥ -12 mA, Voo = 3.3V<br>See <b>Note 1</b>                                                        |

| DO20A              | Vон1                                                                                                 | RA1, RB5, RB6, RB8, RB9,<br>RB14                                                                               | 2.0                                                                                                                                                                                                                                                                                    | _    | _    | V                                 | Іон ≥ -11 mA, Vpd = 3.3V<br>See <b>Note 1</b>                                                        |

|                    |                                                                                                      |                                                                                                                | 3.0                                                                                                                                                                                                                                                                                    | _    | _    |                                   | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |

|                    |                                                                                                      | Output High Voltage<br>8x Source Driver Pins - OSCO,                                                           | 1.5                                                                                                                                                                                                                                                                                    | _    | _    |                                   | IOH ≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                        |

|                    |                                                                                                      | CLKO, RA3                                                                                                      | 2.0                                                                                                                                                                                                                                                                                    | _    |      | V                                 | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                        |

|                    |                                                                                                      |                                                                                                                | 3.0                                                                                                                                                                                                                                                                                    | _    | —    |                                   | IOH ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |

#### TABLE 22-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

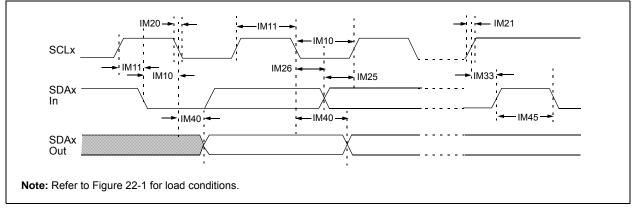

# FIGURE 22-17: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

| Section Name                    | Update Description                                                                                                                                                                                                                                   |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 18.0 "Special Features" | Added FICD register information for address 0xF8000E in the Device Configuration Register Map (see Table 18-1).                                                                                                                                      |

|                                 | Added FICD register content (BKBUG, COE, JTAGEN, and ICS<1:0> to the PIC24HJ32GP202/204 and PIC24HJ16GP304 Configuration Bits Description (see Table 18-2).                                                                                          |

|                                 | Added a note regarding the placement of low-ESR capacitors, after the second paragraph of <b>Section 18.2</b> " <b>On-Chip Voltage Regulator</b> " and to Figure 18-1.                                                                               |

|                                 | Removed the words "if enabled" from the second sentence in the fifth paragraph of <b>Section 18.3 "BOR: Brown-Out Reset"</b> .                                                                                                                       |

| Section 21.0 "Electrical        | Removed Typ value for parameter DC12 (see Table 21-4).                                                                                                                                                                                               |