Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj16gp304-h-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### PIC24HJ32GP202/204 and PIC24HJ16GP304 Product Families

The device names, pin counts, memory sizes and peripheral availability of each family are listed in Table 1, followed by their pinout diagrams.

|                |      | 2rV                              |     |                 | Re           | emappable Peripherals |                                |      |                                    |     |                 |      | (                  |                                |

|----------------|------|----------------------------------|-----|-----------------|--------------|-----------------------|--------------------------------|------|------------------------------------|-----|-----------------|------|--------------------|--------------------------------|

| Device         | Pins | Program Flash Memory<br>(Kbytes) | MAA | Remappable Pins | 16-bit Timer | Input Capture         | Output Compare<br>Standard PWM | UART | External Interrupts <sup>(2)</sup> | IdS | 10/12-bit ADC   | I²C™ | l/O Pins (Maximum) | Packages                       |

| PIC24HJ32GP202 | 28   | 32                               | 2   | 16              | 3(1)         | 4                     | 2                              | 1    | 3                                  | 1   | 1 ADC,<br>10 ch | 1    | 21                 | SPDIP<br>SOIC<br>SSOP<br>QFN-S |

| PIC24HJ32GP204 | 44   | 32                               | 2   | 26              | 3(1)         | 4                     | 2                              | 1    | 3                                  | 1   | 1 ADC,<br>13 ch | 1    | 35                 | QFN<br>TQFP                    |

| PIC24HJ16GP304 | 44   | 16                               | 2   | 26              | 3(1)         | 4                     | 2                              | 1    | 3                                  | 1   | 1 ADC,<br>13 ch | 1    | 35                 | QFN<br>TQFP                    |

## TABLE 1: PIC24HJ32GP202/204 AND PIC24HJ16GP304 CONTROLLER FAMILIES

**Note 1:** Only two out of three timers are remappable.

**2:** Only two out of three interrupts are remappable.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP)<sup>TM</sup> and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the microcontroller as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup> in-circuit emulator

For more information on MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator connection requirements, refer to the following documents that are available on the Microchip website.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

# 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

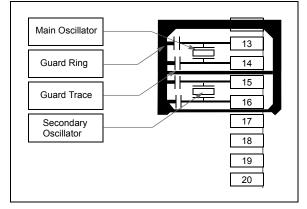

The oscillator circuit should be placed on the same side of the board as the microcontroller. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*, **"Section 4. Program Memory"** (DS70202), which is available from the Microchip website (www.microchip.com).

The PIC24HJ32GP202/204 and PIC24HJ16GP304 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

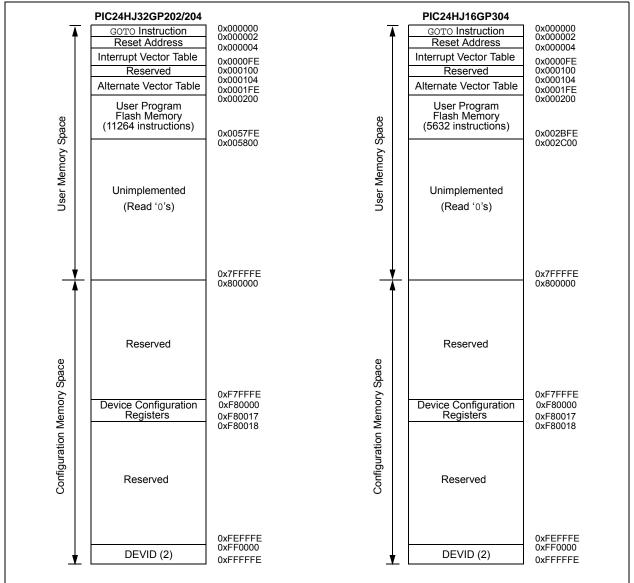

# 4.1 Program Address Space

The devices program address memory space is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in **Section 4.6** "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the PIC24HJ32GP202/204 and PIC24HJ16GP304 devices are shown in Figure 4-1.

### FIGURE 4-1: PROGRAM MEMORY FOR PIC24HJ32GP202/204 AND PIC24HJ16GP304 DEVICES

### 4.2 Data Address Space

The CPU has a separate 16 bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to the bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15>=0) is used for implemented memory addresses, while the upper half (EA<15>=1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices implement up to 2 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16 bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> devices and improve data space memory usage efficiency, the PIC24HJ32GP202/204 and PIC24HJ16GP304 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or when translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the instruction occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the PIC24HJ32GP202/204 and PIC24HJ16GP304 core and peripheral modules to control the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-22.

| Note: | The actual set of peripheral features and interrupts varies by the device. Refer to |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------|--|--|--|--|--|

|       | the corresponding device tables and                                                 |  |  |  |  |  |

|       | pinout diagrams for device-specific                                                 |  |  |  |  |  |

|       | information.                                                                        |  |  |  |  |  |

#### 4.2.4 NEAR DATA SPACE

The 8 Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an address pointer.

NOTES:

#### 6.1 Resets Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 6.1.1 KEY RESOURCES

- Section 8. "Reset" (DS70192)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                                     | U-0                                                                                                                                                      | U-0              | U-0 | U-0              | U-0             | U-0             | U-0   |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|-----------------|-----------------|-------|

| —                                       | _                                                                                                                                                        | _                | _   | _                | _               | _               |       |

| bit 15                                  |                                                                                                                                                          |                  |     |                  |                 |                 | bit 8 |

|                                         |                                                                                                                                                          |                  |     |                  |                 |                 |       |

| U-0                                     | R/W-1 R/W-0 R/W-0                                                                                                                                        |                  |     | U-0              | R/W-1           | R/W-0           | R/W-0 |

| —                                       |                                                                                                                                                          | AD1IP<2:0>       |     |                  |                 | U1TXIP<2:0>     |       |

| bit 7                                   |                                                                                                                                                          |                  |     |                  |                 |                 | bit 0 |

|                                         |                                                                                                                                                          |                  |     |                  |                 |                 |       |

| Legend:                                 | .,                                                                                                                                                       |                  | .,  |                  |                 |                 |       |

| R = Readable b                          |                                                                                                                                                          | W = Writable b   | oit | -                | nented bit, rea |                 |       |

| -n = Value at Po                        | JR                                                                                                                                                       | '1' = Bit is set |     | '0' = Bit is cle | ared            | x = Bit is unkr | iown  |

| bit 15-7<br>bit 6-4<br>bit 3<br>bit 2-0 | Unimplemented: Read as '0'<br>AD1IP<2:0>: ADC1 Conversion Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                  |     |                  |                 |                 |       |

### REGISTER 7-14: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

# **REGISTER 8-4:** OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

|                 |             |                                  | OILEATOR       |                  |                      |                 |              |

|-----------------|-------------|----------------------------------|----------------|------------------|----------------------|-----------------|--------------|

| U-0             | U-0         | U-0                              | U-0            | U-0              | U-0                  | U-0             | U-0          |

|                 | —           | —                                |                | —                | —                    | —               | —            |

| bit 15          |             |                                  |                |                  |                      |                 | bit 8        |

|                 |             | <b>D</b> 444.0                   | <b>DMU</b> O   | DANA             | DAALO                | <b>D</b> 444.0  | <b>DAA/A</b> |

| U-0             | U-0         | R/W-0                            | R/W-0          | R/W-0            | R/W-0                | R/W-0           | R/W-0        |

|                 | —           |                                  |                | IUN              | <5:0> <sup>(1)</sup> |                 |              |

| bit 7           |             |                                  |                |                  |                      |                 | bit 0        |

|                 |             |                                  |                |                  |                      |                 |              |

| Legend:         |             |                                  |                |                  |                      |                 |              |

| R = Readable    | bit         | W = Writable                     | bit            | U = Unimpler     | mented bit, read     | l as '0'        |              |

| -n = Value at I | POR         | '1' = Bit is set                 |                | '0' = Bit is cle | ared                 | x = Bit is unkr | nown         |

| bit 15-6        | Unimplemen  | ted: Read as '                   | 0'             |                  |                      |                 |              |

| bit 5-0         | -           | RC Oscillator 1                  |                |                  |                      |                 |              |

| bit 0 0         |             | nter frequency                   | •              | 845 MHz)         |                      |                 |              |

|                 | •           |                                  | 0.07070 (7.0   |                  |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 |             | nter frequency                   |                |                  |                      |                 |              |

|                 |             | nter frequency<br>nter frequency |                |                  |                      |                 |              |

|                 |             | nter frequency                   |                | •                |                      |                 |              |

|                 | •           |                                  | . 11.2070 (0.2 | 20 10112)        |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 |             | nter frequency                   |                |                  |                      |                 |              |

|                 | 000000 = Ce | nter frequency                   | (7.37 MHZ no   | ominal)          |                      |                 |              |

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

## 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 9. Watchdog Timer and Power Savings Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJ32GP202/204 and PIC24HJ16GP304 devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- · Software-controlled Doze mode

- · Selective peripheral control in software

Combinations of the above methods can be used to selectively customize an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0** "Oscillator **Configuration**".

#### 9.2 Instruction-Based Power-Saving Modes

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Example 9-1 shows the Assembler syntax of the PWRSAV instruction.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

#### 9.2.1 SLEEP MODE

In the Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

#### REGISTER 10-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0             | U-0 | U-0              | U-0                                    | U-0              | U-0        | U-0            | U-0   |  |

|-----------------|-----|------------------|----------------------------------------|------------------|------------|----------------|-------|--|

| —               | —   | —                | —                                      | —                | —          | —              | —     |  |

| bit 15          |     |                  |                                        |                  | •          |                | bit 8 |  |

|                 |     |                  |                                        |                  |            |                |       |  |

| U-0             | U-0 | U-0              | R/W-1                                  | R/W-1            | R/W-1      | R/W-1          | R/W-1 |  |

| —               | —   | _                |                                        |                  | OCFAR<4:0> |                |       |  |

| bit 7           |     |                  |                                        |                  |            |                | bit 0 |  |

|                 |     |                  |                                        |                  |            |                |       |  |

| Legend:         |     |                  |                                        |                  |            |                |       |  |

| R = Readable    | bit | W = Writable     | bit U = Unimplemented bit, read as '0' |                  |            |                |       |  |

| -n = Value at P | POR | '1' = Bit is set |                                        | '0' = Bit is cle | eared      | x = Bit is unk | nown  |  |

#### bit 15-5 Unimplemented: Read as '0'

bit 4-0

OCFAR<4:0>: Assign Output Capture A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

- •

- •

•

00001 = Input tied to RP1 00000 = Input tied to RP0

NOTES:

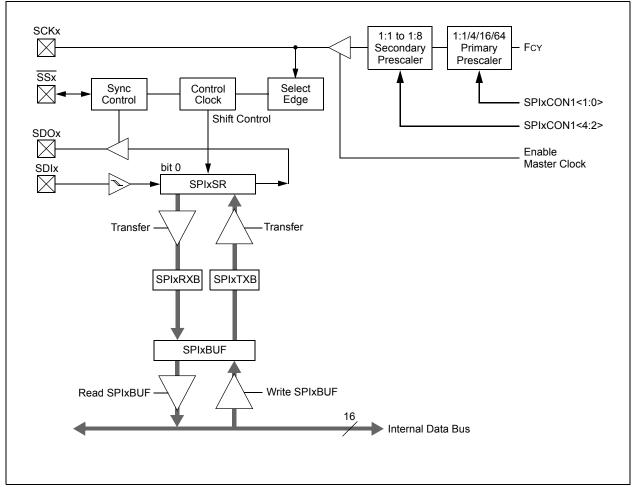

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 18. Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters (ADCs), and so on. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of these four pins:

- · SDIx (serial data input)

- SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 15-1: SPI MODULE BLOCK DIAGRAM

# 16.2 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 16.2.1 KEY RESOURCES

- Section 13. "Inter-Integrated Circuit™ (I2C™)" (DS70195)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 16.3 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

- · I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-bit Address mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                            |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                    |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                     |

|       | 1 = Read – indicates data transfer is output from slave                                                                                                                                                               |

|       | 0 = Write – indicates data transfer is input to slave                                                                                                                                                                 |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                                                                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                   |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                                                                                                 |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                                                                                            |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                                                                                                  |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                  |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul> |

#### Base Assembly # of # of Status Flags Instr Assembly Syntax Description Mnemonic Words Cycles Affected # BTST 12 BTST f,#bit4 Bit Test f 1 1 7 Ws,#bit4 Bit Test Ws to C 1 1 С BTST.C BTST.Z Ws,#bit4 Bit Test Ws to Z 1 1 Ζ BTST.C Bit Test Ws<Wb> to C 1 1 С Ws,Wb BTST.Z Bit Test Ws<Wb> to Z 1 1 Ζ Ws,Wb 13 BTSTS z BTSTS f,#bit4 Bit Test then Set f 1 1 Bit Test Ws to C, then Set 1 1 С BTSTS.C Ws,#bit4 1 z Bit Test Ws to Z, then Set 1 BTSTS.Z Ws,#bit4 14 CALL 2 2 CALL lit23 Call subroutine None 2 CALL Wn Call indirect subroutine 1 None 15 CLR CLR f f = 0x00001 1 None CLR WREG = 0x0000 1 1 WREG None CLR Ws = 0x00001 1 None Ws CLRWDT 16 CLRWDT Clear Watchdog Timer 1 1 WDTO,Sleep 17 COM СОМ $f = \overline{f}$ 1 1 N,Z f WREG = $\overline{f}$ 1 N,Z COM f,WREG 1 Wd = Ws1 COM 1 N,Z Ws,Wd 18 CP Compare f with WREG 1 1 C,DC,N,OV,Z CP f ĊР Compare Wb with lit5 1 1 C,DC,N,OV,Z Wb,#lit5 CP Wb,Ws Compare Wb with Ws (Wb - Ws) 1 1 C,DC,N,OV,Z CP0 19 Compare f with 0x0000 1 C,DC,N,OV,Z CP0 f 1 CP0 Compare Ws with 0x0000 1 C,DC,N,OV,Z Ws 1 CPB 20 CPB f Compare f with WREG, with Borrow 1 1 C,DC,N,OV,Z Wb,#lit5 CPB Compare Wb with lit5, with Borrow 1 1 C,DC,N,OV,Z СРВ Compare Wb with Ws, with Borrow 1 1 C,DC,N,OV,Z Wb,Ws (Wb - Ws - C) CPSEQ 21 CPSEO Wb. Wn Compare Wb with Wn, skip if = 1 1 None (2 or 3) 22 CPSGT CPSGT Compare Wb with Wn, skip if > 1 None Wb, Wn 1 (2 or 3) CPSLT 23 Compare Wb with Wn, skip if < 1 CPSLT Wb, Wn None (2 or 3) CPSNE 24 CPSNE Wb, Wn Compare Wb with Wn, skip if 1/4 1 None 1 (2 or 3) DAW 25 DAW Wn = decimal adjust Wn 1 С Wn 1 26 DEC f = f - 1C,DC,N,OV,Z 1 1 DEC f WREG = f - 1 1 1 C,DC,N,OV,Z DEC f,WREG DEC Ws,Wd Wd = Ws - 1 1 1 C,DC,N,OV,Z 27 DEC2 DEC2 f f = f - 2 1 1 C,DC,N,OV,Z WREG = f - 2 C,DC,N,OV,Z DEC2 f,WREG 1 1 DEC2 Ws,Wd Wd = Ws - 2 1 1 C,DC,N,OV,Z DISI 1 28 Disable Interrupts for k instruction cycles 1 DISI #lit14 None 29 DIV DTV.S Signed 16/16-bit Integer Divide 1 18 N,Z,C,OV Wm,Wn Signed 32/16-bit Integer Divide 1 18 N,Z,C,OV DIV.SD Wm,Wn 1 Unsigned 16/16-bit Integer Divide 18 N,Z,C,OV DIV.U Wm,Wn DIV.UD Unsigned 32/16-bit Integer Divide 1 18 N,Z,C,OV Wm,Wn EXCH 30 EXCH Wns,Wnd Swap Wns with Wnd 1 1 None 31 FBCL FBCL Find Bit Change from Left (MSb) Side 1 1 С Ws.Wnd 32 FF1L Find First One from Left (MSb) Side С FF1L Ws,Wnd 1 1 33 FF1R Find First One from Right (LSb) Side С FF1R Ws,Wnd 1 1 34 GOTO Go to address 2 2 None GOTO Expr 2 GOTO Go to indirect 1 None Wn

#### **INSTRUCTION SET OVERVIEW (CONTINUED) TABLE 20-2:**

| <b>TABLE 22-8:</b> | DC CHARACTERISTICS: DOZE CURRENT (IDOZE) |

|--------------------|------------------------------------------|

|                    |                                          |

| DC CHARACTERI                                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |    |               |       |        |      |          |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|-------|--------|------|----------|

| Parameter No. <sup>(3)</sup> Typical <sup>(2)</sup> Max |                                                                                                                                                                                                     |    | Doze<br>Ratio | Units |        | Co   | nditions |

| Doze Current (IDO                                       | ze) <sup>(1)</sup>                                                                                                                                                                                  |    |               |       |        |      |          |

| DC73a                                                   | 41                                                                                                                                                                                                  | 51 | 1:2           | mA    |        |      |          |

| DC73f                                                   | 20                                                                                                                                                                                                  | 28 | 1:64          | mA    | -40°C  | 3.3V | 40 MIPS  |

| DC73g                                                   | 19                                                                                                                                                                                                  | 24 | 1:128         | mA    |        |      |          |

| DC70a                                                   | 40                                                                                                                                                                                                  | 46 | 1:2           | mA    |        |      |          |

| DC70f                                                   | 18                                                                                                                                                                                                  | 20 | 1:64          | mA    | +25°C  | 3.3V | 40 MIPS  |

| DC70g                                                   | 18                                                                                                                                                                                                  | 20 | 1:128         | mA    |        |      |          |

| DC71a                                                   | 40                                                                                                                                                                                                  | 46 | 1:2           | mA    |        |      |          |

| DC71f                                                   | 18                                                                                                                                                                                                  | 25 | 1:64          | mA    | +85°C  | 3.3V | 40 MIPS  |

| DC71g                                                   | 18                                                                                                                                                                                                  | 20 | 1:128         | mA    |        |      |          |

| DC72a                                                   | 39                                                                                                                                                                                                  | 55 | 1:2           | mA    |        |      |          |

| DC72f                                                   | 18                                                                                                                                                                                                  | 30 | 1:64          | mA    | +125°C | 3.3V | 40 MIPS  |

| DC72g                                                   | 18                                                                                                                                                                                                  | 25 | 1:128         | mA    |        |      |          |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail with overshoot/undershoot < 250 mV</li>

- · CLKO is configured as an I/O input pin in the Configuration word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while(1) statement

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

### 22.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC24HJ32GP202/204 and PIC24HJ16GP304 AC characteristics and timing parameters.

#### TABLE 22-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)    |

|--------------------|-----------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |

|                    | $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                        |

|                    | Operating voltage VDD range as described in Table 22-1.                     |

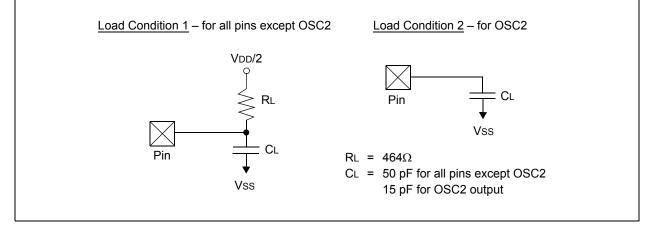

#### FIGURE 22-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 22-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 pin        | _   | _   | 15  |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     | —   | 400 | pF    | In I <sup>2</sup> C™ mode                                          |

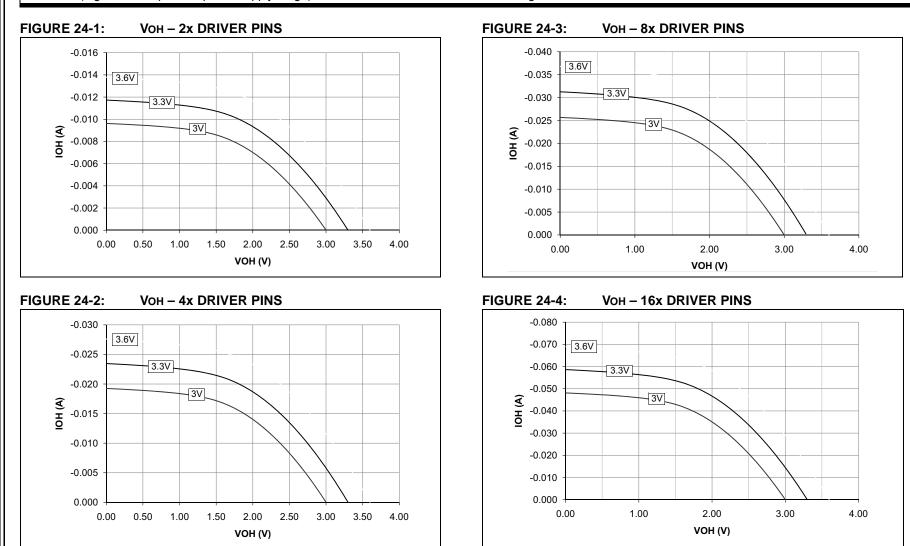

# 24.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

PIC24HJ32GP202/204 AND PIC24HJ16GP30-

# 25.0 PACKAGING INFORMATION

# 25.1 Package Marking Information

28-Lead SPDIP

Example

28-Lead SOIC

Example

28-Lead SSOP

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note:  | : If the full Microchip part number cannot be marked on one line, it is carried over to the ne line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |

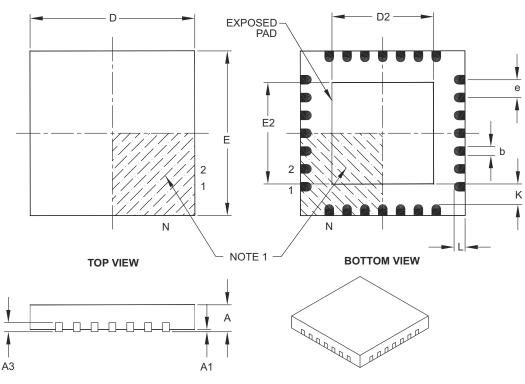

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |      |      |  |

|------------------------|-------------|----------|------|------|--|

| Dimensio               | MIN         | NOM      | MAX  |      |  |

| Number of Pins         | Ν           | 28       |      |      |  |

| Pitch                  | е           | 0.65 BSC |      |      |  |

| Overall Height         | Α           | 0.80     | 0.90 | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02 | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |      |      |  |

| Overall Width          | E           | 6.00 BSC |      |      |  |

| Exposed Pad Width      | E2          | 3.65     | 3.70 | 4.70 |  |

| Overall Length         | D           | 6.00 BSC |      |      |  |

| Exposed Pad Length     | D2          | 3.65     | 3.70 | 4.70 |  |

| Contact Width          | b           | 0.23     | 0.38 | 0.43 |  |

| Contact Length         | L           | 0.30     | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20     | _    | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B