#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj16gp304-h-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0                                                | U-0                                                            | U-0             | U-0   | U-0                 | U-0              | U-0              | U-0   |

|----------------------------------------------------|----------------------------------------------------------------|-----------------|-------|---------------------|------------------|------------------|-------|

| —                                                  | —                                                              | —               | —     | —                   | —                | -                | -     |

| bit 15                                             |                                                                |                 |       |                     |                  |                  | bit 8 |

|                                                    |                                                                |                 |       |                     |                  |                  |       |

| U-0                                                | U-0                                                            | U-0             | U-0   | R/C-0               | R/W-0            | U-0              | U-0   |

| —                                                  | —                                                              | —               | —     | IPL3 <sup>(1)</sup> | PSV              | —                | —     |

| bit 7                                              |                                                                |                 |       |                     |                  |                  | bit 0 |

|                                                    |                                                                |                 |       |                     |                  |                  |       |

| Legend:                                            |                                                                | C = Clear only  | / bit |                     |                  |                  |       |

| R = Readabl                                        | le bit                                                         | W = Writable    | bit   | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is cle                                    | ared                                                           | 'x = Bit is unk | nown  | U = Unimpler        | mented bit, read | l as '0'         |       |

|                                                    |                                                                |                 |       |                     |                  |                  |       |

| bit 15-4                                           | Unimplemented: Read as '0'                                     |                 |       |                     |                  |                  |       |

| bit 3                                              | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(1)</sup> |                 |       |                     |                  |                  |       |

| 1 = CPU interrupt priority level is greater than 7 |                                                                |                 |       |                     |                  |                  |       |

| 0 = CPU interrupt priority level is 7 or less      |                                                                |                 |       |                     |                  |                  |       |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

| bit 2 | PSV: Program Space Visibility in Data Space Enable bit |

|-------|--------------------------------------------------------|

|       | 1 = Program space visible in data space                |

|       | 0 = Program space not visible in data space            |

bit 1-0 Unimplemented: Read as '0'

Note 1: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

# 3.5 Arithmetic Logic Unit (ALU)

The Arithmetic Logic Unit (ALU) is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. The ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register depending on the operation. The C and DC Status bits operate as Borrow and Digit Borrow bits respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for more information on the SR bits affected by each instruction.

The CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and a support hardware for 16-bit divisor division.

# 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

# 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes.

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. A 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.5.3 MULTI-BIT DATA SHIFTER

The multi-bit data shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either a working register or a memory location.

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. and a negative value shifts the operand left. A value of '0' does not modify the operand.

# 4.6 Interfacing Program and Data Memory Spaces

The device architecture uses a 24-bit-wide program space and a 16 bit wide data space. The architecture is also a modified Harvard scheme, which means that the data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. The application can only access the least significant word of the program word.

# 4.6.1 ADDRESSING PROGRAM SPACE

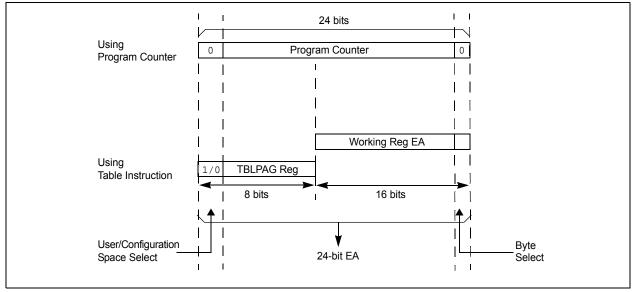

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-24 and Figure 4-5 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

|                          | Access        | Program Space Address         |                           |             |                    |     |

|--------------------------|---------------|-------------------------------|---------------------------|-------------|--------------------|-----|

| Access Type              | Space         | <23>                          | <22:16>                   | <15>        | <14:1>             | <0> |

| Instruction Access       | User          | 0 PC<22:1> ()                 |                           |             |                    | 0   |

| (Code Execution)         |               |                               |                           |             |                    |     |

| TBLRD/TBLWT              | User          | TBLPAG<7:0> Data EA<15:0>     |                           |             | Data EA<15:0>      |     |

| (Byte/Word Read/Write)   |               | 0xxx xxxx xxxx xxxx xxxx      |                           |             |                    |     |

|                          | Configuration | TB                            | TBLPAG<7:0> Data EA<15:0> |             | Data EA<15:0>      |     |

|                          |               | 1xxx xxxx xxxx xxxx xxxx xxxx |                           |             |                    |     |

| Program Space Visibility | User          | 0 PSVPAG<7:0> Data EA         |                           | Data EA<14: | 0> <sup>(1)</sup>  |     |

| (Block Remap/Read)       |               | 0                             | 0 xxxx xxxx               |             | xxx xxxx xxxx xxxx |     |

## TABLE 4-24: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 4. Program Memory" (DS70202) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices contain internal Flash program memory to store and execute application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write program memory data either in 'blocks' or 'rows' of 64 instructions (192 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

# 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits <7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to the bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| _ |               |                             |                                         |

|---|---------------|-----------------------------|-----------------------------------------|

| ; | Set up NVMCO  | N for row programming (     | operations                              |

|   | MOV           | #0x4001, W0                 | ;                                       |

|   | MOV           | W0, NVMCON                  | ; Initialize NVMCON                     |

| ; | Set up a poir | nter to the first prog      | ram memory location to be written       |

| ; | program memo: | ry selected, and write      | s enabled                               |

|   | MOV           | #0x0000, W0                 | ;                                       |

|   | MOV           | W0, TBLPAG                  | ; Initialize PM Page Boundary SFR       |

|   | MOV           | #0x6000, W0                 | ; An example program memory address     |

| ; | Perform the ' | TBLWT instructions to       | write the latches                       |

| ; | 0th_program_  | word                        |                                         |

|   | MOV           | <pre>#LOW_WORD_0 , W2</pre> | ;                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre> | i                                       |

|   | TBLWTL        | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | lst_program_  | word                        |                                         |

|   | MOV           | #LOW_WORD_1, W2             | i                                       |

|   | MOV           | <pre>#HIGH_BYTE_1, W3</pre> | i                                       |

|   |               | W2, [W0]                    | ; Write PM low word into program latch  |

|   |               | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | F = c         |                             |                                         |

|   |               | #LOW_WORD_2, W2             | ;                                       |

|   |               | <pre>#HIGH_BYTE_2, W3</pre> | ;                                       |

|   |               | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

|   | •             |                             |                                         |

|   | •             |                             |                                         |

|   | •             |                             |                                         |

| ; | 63rd_program  |                             |                                         |

|   | MOV           | #LOW_WORD_31, W2            | ;                                       |

|   | MOV           | #HIGH_BYTE_31, W3           | ;                                       |

|   |               | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

|   |               |                             |                                         |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI                                    | #5                                                                | ; Block all interrupts with priority less than 7<br>; for next 5 instructions                                                         |

|-----------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| MOV<br>MOV<br>MOV<br>BSET<br>NOP<br>NOP | #0x55, W0<br>W0, NVMKEY<br>#0xAA, W1<br>W1, NVMKEY<br>NVMCON, #WR | <pre>; Write the 55 key ; ; Write the AA key ; Start the erase sequence ; Insert two NOPs after the ; erase command is asserted</pre> |

# 6.3 System Reset

The PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices have two types of Reset:

- Cold Reset

- Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC configuration bits in the FOSC device configuration register selects the device clock source. A warm Reset is the result of all other reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is shown in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Start-up Delay | Oscillator Start-up<br>Timer | PLL Lock Time | Total Delay          |

|---------------------------|------------------------------|------------------------------|---------------|----------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd                        | _                            | _             | Toscd                |

| FRCPLL                    | Toscd                        | —                            | TLOCK         | TOSCD + TLOCK        |

| XT                        | Toscd                        | Tost                         | —             | TOSCD + TOST         |

| HS                        | Toscd                        | Tost                         | —             | TOSCD + TOST         |

| EC                        | —                            | —                            |               | —                    |

| XTPLL                     | Toscd                        | Tost                         | TLOCK         | TOSCD + TOST + TLOCK |

| HSPLL                     | Toscd                        | Tost                         | TLOCK         | TOSCD + TOST + TLOCK |

| ECPLL                     | —                            | —                            | TLOCK         | TLOCK                |

| SOSC                      | Toscd                        | Тоѕт                         |               | TOSCD + TOST         |

| LPRC                      | Toscd                        |                              | _             | Toscd                |

#### TABLE 6-1: OSCILLATOR DELAY

**Note 1:** TOSCD = Oscillator Start-up Delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal Oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer Delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

3: TLOCK = PLL lock time (1.5 ms nominal), if PLL is enabled.

# PIC24HJ32GP202/204 AND PIC24HJ16GP304

| R/W-0                                                                     | R-0                                                                                            | U-0                            | U-0           | U-0              | U-0             | U-0             | U-0    |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------|---------------|------------------|-----------------|-----------------|--------|--|--|--|

| ALTIVT                                                                    | DISI                                                                                           | —                              | _             | —                | —               | —               | _      |  |  |  |

| bit 15                                                                    |                                                                                                |                                |               |                  |                 |                 | bit 8  |  |  |  |

|                                                                           |                                                                                                |                                |               |                  |                 |                 |        |  |  |  |

| U-0                                                                       | U-0                                                                                            | U-0                            | U-0           | U-0              | R/W-0           | R/W-0           | R/W-0  |  |  |  |

| —                                                                         | _                                                                                              | —                              |               | —                | INT2EP          | INT1EP          | INT0EP |  |  |  |

| bit 7                                                                     |                                                                                                |                                |               |                  |                 |                 | bit (  |  |  |  |

|                                                                           |                                                                                                |                                |               |                  |                 |                 |        |  |  |  |

| Legend:                                                                   |                                                                                                |                                |               |                  |                 |                 |        |  |  |  |

| R = Readabl                                                               | e bit                                                                                          | W = Writable                   | bit           | U = Unimple      | mented bit, rea | d as '0'        |        |  |  |  |

| -n = Value at                                                             | POR                                                                                            | '1' = Bit is set               |               | '0' = Bit is cle | eared           | x = Bit is unki | nown   |  |  |  |

|                                                                           |                                                                                                |                                |               |                  |                 |                 |        |  |  |  |

| bit 15                                                                    | ALTIVT: Enat                                                                                   | ole Alternate In               | terrupt Vecto | r Table bit      |                 |                 |        |  |  |  |

|                                                                           |                                                                                                | 1 = Use alternate vector table |               |                  |                 |                 |        |  |  |  |

|                                                                           |                                                                                                | dard (default) v               |               |                  |                 |                 |        |  |  |  |

| bit 14                                                                    |                                                                                                | struction Statu                |               |                  |                 |                 |        |  |  |  |

|                                                                           |                                                                                                | ruction is active              | -             |                  |                 |                 |        |  |  |  |

| h:+ 40 0                                                                  |                                                                                                | ruction is not a               |               |                  |                 |                 |        |  |  |  |

| bit 13-3                                                                  | -                                                                                              | ted: Read as '                 |               |                  |                 |                 |        |  |  |  |

| bit 2                                                                     |                                                                                                |                                | •             | t Polarity Selec | t bit           |                 |        |  |  |  |

|                                                                           |                                                                                                | on negative edg                |               |                  |                 |                 |        |  |  |  |

| bit 1                                                                     | •                                                                                              |                                |               | t Dolarity Soloo | + hit           |                 |        |  |  |  |

| DILI                                                                      | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                                |               |                  |                 |                 |        |  |  |  |

|                                                                           | •                                                                                              | on positive edg                | •             |                  |                 |                 |        |  |  |  |

| bit 0 <b>INTOEP:</b> External Interrupt 0 Edge Detect Polarity Select bit |                                                                                                |                                |               |                  |                 |                 |        |  |  |  |

|                                                                           | 1 = Interrupt on negative edge                                                                 |                                |               |                  |                 |                 |        |  |  |  |

|                                                                           | 1 = Interrupt a                                                                                | on negative edu                | ne            |                  |                 |                 |        |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# 7.5 Interrupt Setup Procedures

#### 7.5.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Set the interrupt enable control bit associated with the source in the appropriate IECx register to enable the interrupt source.

## 7.5.2 INTERRUPT SERVICE ROUTINE

The method used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address depends on the programming language (C or Assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.5.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.5.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the  ${\tt POP}$  instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

# 10.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Pin Diagrams"** section for the available pins and their functionality.

# 10.3 Configuring Analog Port Pins

The AD1PCFG and TRIS registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP. Examples are shown in Example 10-1 and Example 10-2. This also applies to PORT bit operations, such as BSET PORTB, # RB0, which are single cycle read-modify-write. All PORT bit operations, such as MOV PORTB, W0 or BSET PORTB, # RBx, read the pin and *not* the latch.

# 10.5 Input Change Notification

The input change notification function of the I/O ports allows the PIC24HJ32GP202/204 and PIC24HJ16GP304 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 31 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-of-state.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

#### EXAMPLE 10-2: PORT BIT OPERATIONS

| PORTB,  | #RB1                                | ;Set                                      | PORTB <rb1></rb1>                                                            | high                                                                                                                                               |

|---------|-------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PORTB,  | #RB6                                | ;Set                                      | PORTB <rb6></rb6>                                                            | high                                                                                                                                               |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

| PORTB,  | #RB1                                | ;Set                                      | PORTB <rb1></rb1>                                                            | high                                                                                                                                               |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

| PORTB,  | #RB6                                | ;Set                                      | PORTB <rb6></rb6>                                                            | high                                                                                                                                               |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

|         |                                     |                                           |                                                                              |                                                                                                                                                    |

| LATB, 1 | LATB1                               | ;Set                                      | PORTB <rb1></rb1>                                                            | high                                                                                                                                               |

| LATB, 1 | latb6                               | ;Set                                      | PORTB <rb6></rb6>                                                            | high                                                                                                                                               |

|         | PORTB,<br>PORTB,<br>PORTB,<br>LATB, | PORTB, #RB6<br>PORTB, #RB1<br>PORTB, #RB6 | PORTB, #RB6 ;Set<br>PORTB, #RB1 ;Set<br>PORTB, #RB6 ;Set<br>LATB, LATB1 ;Set | <pre>PORTE, #RB6 ;Set PORTB<rb6> PORTE, #RB1 ;Set PORTB<rb1> PORTE, #RB6 ;Set PORTB<rb6> LATE, LATB1 ;Set PORTB<rb1></rb1></rb6></rb1></rb6></pre> |

# 12.0 TIMER2/3 FEATURE

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 11. Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 feature has 32-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

As a 32-bit timer, the Timer2/3 feature permits operation in three modes:

- Two Independent 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3)

- Single 32-bit synchronous counter (Timer2/3)

The Timer2/3 feature also supports:

- Timer gate operation

- Selectable Prescaler Settings

- Timer operation during Idle and Sleep modes

- · Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features that are listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. T2CON registers are shown in generic form in Register 12-1. T3CON registers are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 is the least significant word (lsw), and Timer3 is the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bit is used for setup and control. Timer2 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flags.

# 12.1 32-bit Operation

To configure the Timer2/3 feature for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 contains the most significant word of the value, while PR2 contains the least significant word.

- 5. Set the interrupt enable bit T3IE, if interrupts are required. Use the priority bits T3IP<2:0> to set the interrupt priority. While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair TMR3:TMR2. TMR3 always contains the most significant word of the count, while TMR2 contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

# 16.2 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 16.2.1 KEY RESOURCES

- Section 13. "Inter-Integrated Circuit™ (I2C™)" (DS70195)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 16.3 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

- · I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-bit Address mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

# REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                     |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>    |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                             |

|       | 1 = Receive buffer has overflowed                                                                                                                                           |

|       | 0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the UxRSR to the empty state |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

|       |                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

# PIC24HJ32GP202/204 AND PIC24HJ16GP304

|               | U-0                                                                                                                                                                             | U-0                                                                                                                                                                          | R/W-0                                                                                                                | R/W-0           | R/W-0            | R/W-0           | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-------|

| CH0NB         | _                                                                                                                                                                               | _                                                                                                                                                                            |                                                                                                                      |                 | CH0SB<4:0>       |                 |       |

| bit 15        |                                                                                                                                                                                 | _                                                                                                                                                                            |                                                                                                                      |                 |                  |                 | bit   |

|               |                                                                                                                                                                                 |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

| R/W-0         | U-0                                                                                                                                                                             | U-0                                                                                                                                                                          | R/W-0                                                                                                                | R/W-0           | R/W-0            | R/W-0           | R/W-0 |

| CH0NA         | _                                                                                                                                                                               | —                                                                                                                                                                            |                                                                                                                      |                 | CH0SA<4:0>       |                 |       |

| bit 7         |                                                                                                                                                                                 |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 | bit   |

| Legend:       |                                                                                                                                                                                 |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

| R = Readable  | e bit                                                                                                                                                                           | W = Writable t                                                                                                                                                               | oit                                                                                                                  | U = Unimple     | mented bit, read | l as '0'        |       |

| -n = Value at | POR                                                                                                                                                                             | '1' = Bit is set                                                                                                                                                             |                                                                                                                      | '0' = Bit is cl | eared            | x = Bit is unkr | nown  |

|               |                                                                                                                                                                                 |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

| bit 15        |                                                                                                                                                                                 | annel 0 Negative                                                                                                                                                             | -                                                                                                                    | for Sample B I  | oit              |                 |       |

|               |                                                                                                                                                                                 | 0 negative input                                                                                                                                                             |                                                                                                                      |                 |                  |                 |       |

| bit 11 12     |                                                                                                                                                                                 | 0 negative input                                                                                                                                                             |                                                                                                                      |                 |                  |                 |       |

| bit 14-13     | •                                                                                                                                                                               | nted: Read as '0                                                                                                                                                             |                                                                                                                      |                 |                  |                 |       |

| bit 12-8      |                                                                                                                                                                                 | >: Channel 0 Po                                                                                                                                                              | -                                                                                                                    | -               |                  |                 |       |

|               |                                                                                                                                                                                 | SP204 and PIC2<br>annel 0 positive                                                                                                                                           |                                                                                                                      |                 | /:               |                 |       |

|               | •                                                                                                                                                                               |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

|               | •                                                                                                                                                                               |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

|               |                                                                                                                                                                                 |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

|               | •                                                                                                                                                                               |                                                                                                                                                                              |                                                                                                                      |                 |                  |                 |       |

|               |                                                                                                                                                                                 | annel 0 positive                                                                                                                                                             |                                                                                                                      |                 |                  |                 |       |

|               | 00001 <b>= Ch</b> a                                                                                                                                                             | annel 0 positive<br>annel 0 positive<br>annel 0 positive                                                                                                                     | input is AN1                                                                                                         |                 |                  |                 |       |

|               | 00001 <b>= Ch</b> a<br>00000 <b>= Ch</b> a                                                                                                                                      | annel 0 positive<br>annel 0 positive                                                                                                                                         | input is AN1<br>input is AN0                                                                                         |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ320                                                                                                                                        | annel 0 positive<br>annel 0 positive<br>GP202 devices o                                                                                                                      | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ320                                                                                                                                        | annel 0 positive<br>annel 0 positive                                                                                                                                         | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ320                                                                                                                                        | annel 0 positive<br>annel 0 positive<br>GP202 devices o                                                                                                                      | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ320<br>01100 = Cha<br>•<br>•                                                                                                               | annel 0 positive<br>annel 0 positive<br><b>6P202 devices o</b><br>annel 0 positive                                                                                           | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha<br>•<br>•<br>•<br>•<br>01000 = Res                                                                                      | annel 0 positive<br>annel 0 positive<br><b>GP202 devices o</b><br>annel 0 positive<br>served                                                                                 | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha<br>•<br>•<br>•<br>01000 = Res<br>00111 = Res                                                                            | annel 0 positive<br>annel 0 positive<br>GP202 devices o<br>annel 0 positive<br>served<br>served                                                                              | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha<br>•<br>•<br>•<br>•<br>01000 = Res                                                                                      | annel 0 positive<br>annel 0 positive<br>GP202 devices o<br>annel 0 positive<br>served<br>served                                                                              | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha<br>01000 = Res<br>00111 = Res<br>00110 = Res                                                                            | annel 0 positive<br>annel 0 positive<br>GP202 devices o<br>annel 0 positive<br>served<br>served                                                                              | input is AN1<br>input is AN0<br>only:                                                                                |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha<br>01000 = Res<br>00111 = Res                                                                                           | annel 0 positive<br>annel 0 positive<br><b>GP202 devices o</b><br>annel 0 positive<br>served<br>served<br>served                                                             | input is AN1<br>input is AN0<br>only:<br>input is AN12                                                               |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha                                                                                                                         | annel 0 positive<br>annel 0 positive<br><b>6P202 devices o</b><br>annel 0 positive<br>served<br>served<br>served<br>served                                                   | input is AN1<br>input is AN0<br>only:<br>input is AN12<br>input is AN2                                               |                 |                  |                 |       |

|               | 00001 = Cha<br>00000 = Cha<br>01100 = Cha<br>01000 = Res<br>00100 = Res<br>00111 = Res<br>00110 = Res<br>00110 = Cha<br>00010 = Cha                                             | annel 0 positive<br>annel 0 positive<br><b>6P202 devices o</b><br>annel 0 positive<br>served<br>served<br>served<br>served<br>annel 0 positive<br>annel 0 positive           | input is AN1<br>input is AN0<br>only:<br>input is AN12<br>input is AN2<br>input is AN1                               |                 |                  |                 |       |

| bit 7         | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha                                                                                                                         | annel 0 positive<br>annel 0 positive<br><b>SP202 devices o</b><br>annel 0 positive<br>served<br>served<br>served<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive | input is AN1<br>input is AN0<br>only:<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0               |                 | bit              |                 |       |

| bit 7         | 00001 = Cha<br>00000 = Cha<br>01100 = Cha<br>01100 = Cha<br>01000 = Res<br>00111 = Res<br>00110 = Res<br>00110 = Res<br>00110 = Cha<br>00001 = Cha<br>00000 = Cha<br>CHONA: Cha | annel 0 positive<br>annel 0 positive<br><b>6P202 devices o</b><br>annel 0 positive<br>served<br>served<br>served<br>served<br>annel 0 positive<br>annel 0 positive           | input is AN1<br>input is AN0<br>only:<br>input is AN12<br>input is AN1<br>input is AN1<br>e Input Select             |                 | Dit              |                 |       |

| bit 7         | 00001 = Cha<br>00000 = Cha<br>PIC24HJ32C<br>01100 = Cha<br>01000 = Res<br>00110 = Res<br>00110 = Res                                                                            | annel 0 positive<br>annel 0 positive<br><b>3P202 devices o</b><br>annel 0 positive<br>served<br>served<br>served<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive | input is AN1<br>input is AN0<br>only:<br>input is AN12<br>input is AN1<br>input is AN1<br>e Input Select<br>t is AN1 |                 | pit              |                 |       |

# REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

# **19.0 SPECIAL FEATURES**

**Note:** This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices include several features that are intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# **19.1 Configuration Bits**

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25. "Device Configuration"** (DS70194) of the *"dsPIC33F/PIC24H Family Reference Manual"*, for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The Device Configuration register map is shown in Table 19-1.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 19-2.

Note that address 0xF80000 is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFF), which can only be accessed using table reads and table writes.

| Address  | Name     | Bit 7  | Bit 6               | Bit 5   | Bit 4        | Bit 3  | Bit 2      | Bit 1    | Bit 0   |  |

|----------|----------|--------|---------------------|---------|--------------|--------|------------|----------|---------|--|

| 0xF80000 | FBS      | _      |                     | _       | _            |        | BSS<2:0>   | •        | BWRP    |  |

| 0xF80002 | Reserved |        | _                   |         | —            |        | _          |          | —       |  |

| 0xF80004 | FGS      | _      | _                   | _       | _            | _      | GSS<1      | :0>      | GWRP    |  |

| 0xF80006 | FOSCSEL  | IESO — |                     | _       | _            |        | FNOSC<2:0> |          |         |  |

| 0xF80008 | FOSC     | FCKSM  | <1:0>               | IOL1WAY | —            | —      | OSCIOFNC   | POSCN    | 1D<1:0> |  |

| 0xF8000A | FWDT     | FWDTEN | WINDIS              | _       | WDTPRE       |        | WDTPOST    | <3:0>    |         |  |

| 0xF8000C | FPOR     | F      | Reserved(           | 1)      | ALTI2C       | _      | FPV        | VRT<2:0> | •       |  |

| 0xF8000E | FICD     | Reserv | ed <sup>(2)</sup>   | JTAGEN  | —            | _      | —          | ICS<     | :1:0>   |  |

| 0xF80010 | FUID0    |        | User Unit ID Byte 0 |         |              |        |            |          |         |  |

| 0xF80012 | FUID1    |        | User Unit ID Byte 1 |         |              |        |            |          |         |  |

| 0xF80014 | FUID2    |        | User Unit ID Byte 2 |         |              |        |            |          |         |  |

| 0xF80016 | FUID3    |        |                     |         | User Unit ID | Byte 3 |            |          |         |  |

## TABLE 19-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved and always read as '1'.

2: These bits are reserved for use by development tools and must be programmed as '1'.