#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj16gp304-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$  8 MHz for start-up with PLL enabled. This means that if the external oscillator frequency is outside this range, the application must start-up in FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

# 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL registers.

The bits in the registers that correspond to the A/D pins that are initialized by MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When the MPLAB ICD 3 or MPLAB REAL ICE in-circuit emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

| File Name | Addr | Bit 15 | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8    | Bit 7      | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------------------|--------|--------|--------|-----------|-------|----------|------------|-----------|-------|-------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300 |        | ADC Data Buffer 0     |        |        |        |           |       |          | xxxx       |           |       |       |        |          |         |         |               |

| ADC1BUF1  | 0302 |        |                       |        |        |        |           |       | ADC Data | a Buffer 1 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304 |        |                       |        |        |        |           |       | ADC Data | a Buffer 2 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306 |        |                       |        |        |        |           |       | ADC Data | a Buffer 3 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308 |        |                       |        |        |        |           |       | ADC Data | a Buffer 4 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF5  | 030A |        |                       |        |        |        |           |       | ADC Data | a Buffer 5 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF6  | 030C |        |                       |        |        |        |           |       | ADC Data | a Buffer 6 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E |        |                       |        |        |        |           |       | ADC Data | a Buffer 7 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310 |        |                       |        |        |        |           |       | ADC Data | a Buffer 8 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312 |        |                       |        |        |        |           |       | ADC Data | a Buffer 9 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFA  | 0314 |        |                       |        |        |        |           |       | ADC Data | Buffer 10  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316 |        |                       |        |        |        |           |       | ADC Data | Buffer 11  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318 |        | ADC Data Buffer 12    |        |        |        |           |       | xxxx     |            |           |       |       |        |          |         |         |               |

| ADC1BUFD  | 031A |        | ADC Data Buffer 13 x: |        |        |        |           |       | xxxx     |            |           |       |       |        |          |         |         |               |

| ADC1BUFE  | 031C |        |                       |        |        |        |           |       | ADC Data | Buffer 14  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E |        |                       |        |        |        |           |       | ADC Data | Buffer 15  |           |       |       |        |          |         |         | xxxx          |

| AD1CON1   | 0320 | ADON   | -                     | ADSIDL |        |        | AD12B     | FOR   | M<1:0>   | 5          | SSRC<2:0> | >     | _     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322 | ١      | /CFG<2:0>             | >      | —      | —      | CSCNA     | CHP   | 'S<1:0>  | BUFS       | —         |       | SMPI  | <3:0>  |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | -                     | —      |        |        | SAMC<4:0  | >     |          |            |           |       | ADC   | S<7:0> |          |         | 1       | 0000          |

| AD1CHS123 | 0326 | —      | _                     | _      | —      | —      | CH123N    |       | CH123SB  | —          | _         | _     | —     | —      |          | VA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _                     | —      |        |        | CH0SB<4:( |       |          | CH0NA      | —         | —     |       |        | CH0SA<4: |         |         | 0000          |

| AD1PCFGL  | 032C |        |                       | —      | PCFG12 | PCFG11 | PCFG10    | PCFG9 | —        |            | —         | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330 | —      | —                     | _      | CSS12  | CSS11  | CSS10     | CSS9  | —        | —          |           | CSS5  | CSS4  | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

#### TABLE 4-15: ADC1 REGISTER MAP FOR PIC24HJ32GP202

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Legend:              |                      |                      |     |       |       |       |       |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      |                      |                      |     |       |       |       |       |

| bit 15               | -                    |                      |     |       |       |       | bit 8 |

| —                    | —                    | —                    | _   | —     | —     | —     | DC    |

| U-0                  | U-0                  | U-0                  | U-0 | U-0   | U-0   | U-0   | R/W-0 |

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |

|--------------------|----------------------|------------------------------------|

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |

| IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>      |

|------------------------------------------------------------------------|

| 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled |

| 110 = CPU Interrupt Priority Level is 6 (14)                           |

| 101 = CPU Interrupt Priority Level is 5 (13)                           |

| 100 = CPU Interrupt Priority Level is 4 (12)                           |

| 011 = CPU Interrupt Priority Level is 3 (11)                           |

| 010 = CPU Interrupt Priority Level is 2 (10)                           |

| 001 = CPU Interrupt Priority Level is 1 (9)                            |

| 000 = CPU Interrupt Priority Level is 0 (8)                            |

|                                                                        |

SR: CPU STATUS REGISTER<sup>(1)</sup>

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL < 3 > = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

**REGISTER 7-1:**

bit 7-5

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 | Interrupt Flag Status bit  |

|-------|--------------------------------|----------------------------|

|       | ion input oupture onumer i     | interrupt i lug otatao bit |

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### INTOIF: External Interrupt 0 Flag Status bit

1 = Interrupt request has occurred

bit 0

0 = Interrupt request has not occurred

# 9.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 9.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

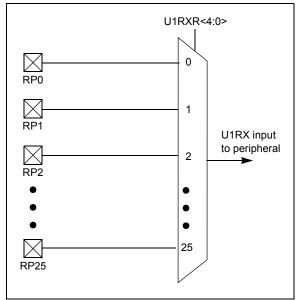

# **10.6** Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low-pin count devices. In an application where more than one peripheral must be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, once it has been established.

# 10.6.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 26 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

# 10.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers to map peripherals and to map outputs.

Since they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# 10.6.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-9). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

Figure 10-2 Illustrates remappable pin selection for U1RX input.

| For input mapping only, the Peripheral Pin |

|--------------------------------------------|

| Select (PPS) functionality does not have   |

| priority over the TRISx settings. There-   |

| fore, when configuring the RPn pin for     |

| input, the corresponding bit in the TRISx  |

| register must also be configured for input |

| (i.e., set to '1').                        |

|                                            |

#### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| WEEL IV 2. OUT |           |                                      |  |  |  |  |

|----------------|-----------|--------------------------------------|--|--|--|--|

| Function       | RPnR<4:0> | Output Name                          |  |  |  |  |

| NULL           | 00000     | RPn tied to default port pin         |  |  |  |  |

| U1TX           | 00011     | RPn tied to UART1 Transmit           |  |  |  |  |

| U1RTS          | 00100     | RPn tied to UART1 Ready To Send      |  |  |  |  |

| SDO1           | 00111     | RPn tied to SPI1 Data Output         |  |  |  |  |

| SCK1OUT        | 01000     | RPn tied to SPI1 Clock Output        |  |  |  |  |

| SS1OUT         | 01001     | RPn tied to SPI1 Slave Select Output |  |  |  |  |

| OC1            | 10010     | RPn tied to Output Compare 1         |  |  |  |  |

| OC2            | 10011     | RPn tied to Output Compare 2         |  |  |  |  |

### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24H devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- · Configuration bit pin select lock

#### 10.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting the IOLOCK bit prevents writes to the control registers; clearing this bit allows writes.

To set or clear the IOLOCK bit, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See MPLAB Help for more information.                                                             |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all the peripheral pin selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

# 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset will be triggered.

### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY configuration bit (FOSC<5>) blocks the IOLOCK bit from being cleared after it has been set once.

In the default (unprogrammed) state, IOL1WAY is set restricting the users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

| U-0          | U-0       | U-0                              | R/W-1   | R/W-1                                   | R/W-1                                   | R/W-1              | R/W-1   |  |

|--------------|-----------|----------------------------------|---------|-----------------------------------------|-----------------------------------------|--------------------|---------|--|

| 0-0          | 0-0       |                                  | 10/00-1 | 10/00-1                                 | INT1R<4:0>                              |                    | 10/00-1 |  |

|              | _         |                                  |         |                                         | 111111111111111111111111111111111111111 |                    | L : L : |  |

| bit 15       |           |                                  |         |                                         |                                         |                    | bit 8   |  |

|              |           |                                  |         |                                         |                                         |                    |         |  |

| U-0          | U-0       | U-0                              | U-0     | U-0                                     | U-0                                     | U-0                | U-0     |  |

| —            | _         | —                                | —       | _                                       | —                                       | —                  | —       |  |

| bit 7        |           |                                  |         |                                         |                                         |                    | bit C   |  |

|              |           |                                  |         |                                         |                                         |                    |         |  |

| Legend:      |           |                                  |         |                                         |                                         |                    |         |  |

| R = Readab   | le bit    | W = Writable                     | bit     | U = Unimple                             | mented bit, read                        | d as '0'           |         |  |

| -n = Value a | t POR     | '1' = Bit is set                 |         | '0' = Bit is cle                        | eared                                   | x = Bit is unknown |         |  |

|              |           |                                  |         |                                         |                                         |                    |         |  |

| bit 15-13    | Unimpleme | nted: Read as '                  | 0'      |                                         |                                         |                    |         |  |

| bit 12-8     | -         | : Assign Externa                 |         | (INTR1) to the                          | corresponding                           | RPn pin            |         |  |

|              |           | ut tied to Vss                   |         | , , , , , , , , , , , , , , , , , , , , | 5                                       | r                  |         |  |

|              |           | ut tied to RP25                  |         |                                         |                                         |                    |         |  |

|              | •         |                                  |         |                                         |                                         |                    |         |  |

|              | •         |                                  |         |                                         |                                         |                    |         |  |

|              | •         |                                  |         |                                         |                                         |                    |         |  |

|              |           | ut tied to RP1<br>ut tied to RP0 |         |                                         |                                         |                    |         |  |

# REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| bit 7-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

# REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                                                    |  |  |  |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|--|--|--|

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

| bit 8                                                  |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

| R/W-1                                                  |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

| bit 0                                                  |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

| nown                                                   |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

| •                                                      |  |  |  |  |  |  |  |  |

| 00001 = Input tied to RP1<br>00000 = Input tied to RP0 |  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |  |

### REGISTER 10-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0             | U-0 | U-0              | U-0                                        | U-0                                | U-0        | U-0   | U-0   |

|-----------------|-----|------------------|--------------------------------------------|------------------------------------|------------|-------|-------|

| —               | —   | —                | —                                          | —                                  | —          | —     | —     |

| bit 15          |     |                  |                                            |                                    | •          |       | bit 8 |

|                 |     |                  |                                            |                                    |            |       |       |

| U-0             | U-0 | U-0              | R/W-1                                      | R/W-1                              | R/W-1      | R/W-1 | R/W-1 |

| —               | —   | —                |                                            |                                    | OCFAR<4:0> |       |       |

| bit 7           |     |                  |                                            |                                    |            |       | bit 0 |

|                 |     |                  |                                            |                                    |            |       |       |

| Legend:         |     |                  |                                            |                                    |            |       |       |

| R = Readable    | bit | W = Writable     | bit                                        | U = Unimplemented bit, read as '0' |            |       |       |

| -n = Value at P | POR | '1' = Bit is set | et '0' = Bit is cleared x = Bit is unknown |                                    |            |       |       |

#### bit 15-5 Unimplemented: Read as '0'

bit 4-0

OCFAR<4:0>: Assign Output Capture A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

- •

- •

•

00001 = Input tied to RP1 00000 = Input tied to RP0

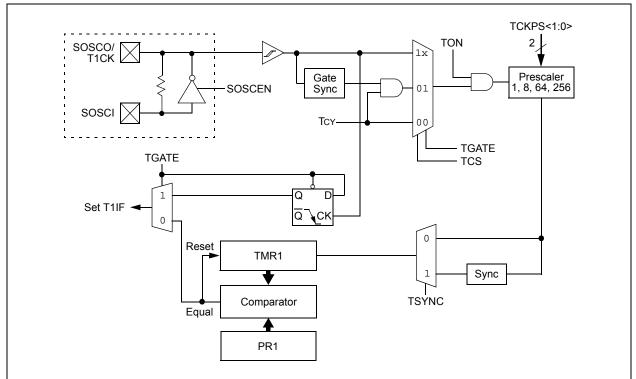

# 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 11. Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 11-1 shows a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

# FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

# 13.2 Input Capture Registers

# REGISTER 13-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0    | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0 | R/W-0 |

|-------|----------|-------|---------|---------|-------|-------|-------|

| ICTMR | ICI<1:0> |       | ICOV    | ICBNE   |       |       |       |

| bit 7 |          |       |         |         |       |       | bit 0 |

| Legend:         HC = Cleared in Hardware |                  |                                    |                    |  |  |

|------------------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit                         | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                        | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                     |

|           | 1 = Input capture module will halt in CPU Idle mode                                                                                                       |

|           | 0 = Input capture module will continue to operate in CPU Idle mode                                                                                        |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                    |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                              |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                              |

|           | 10 = Interrupt on every third capture event                                                                                                               |

|           | <ul> <li>01 = Interrupt on every second capture event</li> <li>00 = Interrupt on every capture event</li> </ul>                                           |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                  |

|           | 1 = Input capture overflow occurred                                                                                                                       |

|           | 0 = No input capture overflow occurred                                                                                                                    |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                  |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                  |

|           | 111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode                                                                  |

|           | (Rising edge detect only, all other control bits are not applicable.)<br>110 = Unused (module disabled)                                                   |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                 |

|           | 011 = Capture mode, every rising edge                                                                                                                     |

|           | 010 = Capture mode, every falling edge                                                                                                                    |

|           | <ul> <li>001 = Capture mode, every edge (rising and falling)</li> <li>(ICI&lt;1:0&gt; bits do not control interrupt generation for this mode.)</li> </ul> |

|           | 000 = Input capture module turned off                                                                                                                     |

|           |                                                                                                                                                           |

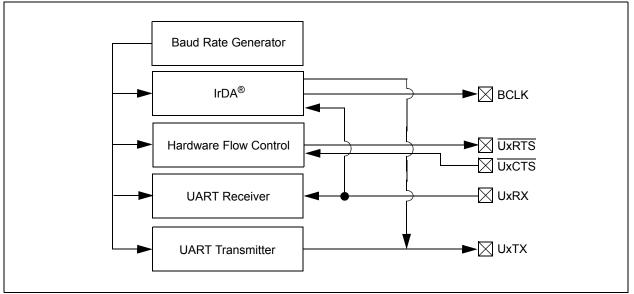

# 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 17. UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJ32GP202/204 and PIC24HJ16GP304 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex 8-bit or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, odd or no parity options (for 8-bit data)

- One or two stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep first-in-first-out (FIFO) Transmit Data Buffer

- 4-deep FIFO Receive Data Buffer

- · Parity, framing and buffer overrun error detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive interrupts

- · A separate interrupt for all UART error conditions

- Loopback mode for diagnostic support

- · Support for Sync and Break characters

- · Support for automatic baud rate detection

- IrDA<sup>®</sup> encoder and decoder logic

- + 16x baud clock output for  $\mbox{IrDA}^{\mbox{$\mathbb{R}$}}$  support

A simplified block diagram of the UART module is shown in Figure 17-1. The UART module consists of the following key hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

# FIGURE 17-1: UART SIMPLIFIED BLOCK DIAGRAM

# TABLE 20-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                                                   | Description |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| #text           | Means literal defined by "text"                                                                               |             |  |  |  |  |  |  |

| (text)          | Means "content of text"                                                                                       |             |  |  |  |  |  |  |

| [text]          | Means "the location addressed by text"                                                                        |             |  |  |  |  |  |  |

| { }             | Optional field or operation                                                                                   |             |  |  |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                                                            |             |  |  |  |  |  |  |

| .b              | Byte mode selection                                                                                           |             |  |  |  |  |  |  |

| .d              | Double Word mode selection                                                                                    |             |  |  |  |  |  |  |

| .S              | Shadow register select                                                                                        |             |  |  |  |  |  |  |

| .w              | Word mode selection (default)                                                                                 |             |  |  |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$                                 |             |  |  |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                          |             |  |  |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                                                |             |  |  |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                                                        |             |  |  |  |  |  |  |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                                                |             |  |  |  |  |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                                                |             |  |  |  |  |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                                                |             |  |  |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                                               |             |  |  |  |  |  |  |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode                                        |             |  |  |  |  |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                                            |             |  |  |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                                            |             |  |  |  |  |  |  |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                                         |             |  |  |  |  |  |  |

| None            | Field does not require an entry, may be blank                                                                 |             |  |  |  |  |  |  |

| PC              | Program Counter                                                                                               |             |  |  |  |  |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                                             |             |  |  |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                                         |             |  |  |  |  |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                                                |             |  |  |  |  |  |  |

| Wb              | Base W register ∈ {W0W15}                                                                                     |             |  |  |  |  |  |  |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                             |             |  |  |  |  |  |  |

| Wdo             | Destination W register $\in$ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                         |             |  |  |  |  |  |  |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                                                   |             |  |  |  |  |  |  |

| Wm*Wm           | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7} |             |  |  |  |  |  |  |

| Wn              | One of 16 working registers ∈ {W0W15}                                                                         |             |  |  |  |  |  |  |

| Wnd             | One of 16 destination working registers ∈ {W0W15}                                                             |             |  |  |  |  |  |  |

| Wns             | One of 16 source working registers ∈ {W0W15}                                                                  |             |  |  |  |  |  |  |

| WREG            | W0 (working register used in file register instructions)                                                      |             |  |  |  |  |  |  |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                  |             |  |  |  |  |  |  |

| Wso             | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                               |             |  |  |  |  |  |  |

# 22.1 DC Characteristics

#### TABLE 22-1: OPERATING MIPS VS. VOLTAGE

|                | Voo Bango                       | Tomp Bongo            | Max MIPS                                 |

|----------------|---------------------------------|-----------------------|------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)         | Temp Range<br>(in °C) | PIC24HJ32GP202/204 and<br>PIC24HJ16GP304 |

|                | — VBOR-3.6V <sup>(1)</sup> -40° |                       | 40                                       |

|                | VBOR-3.6V <sup>(1)</sup>        | -40°C to +125°C       | 40                                       |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 22-11 for the minimum and maximum BOR values.

# TABLE 22-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                    | Symbol              | Min         | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|-----|------|------|

| Industrial Temperature Devices                                                                                            |                     |             |     |      |      |

| Operating Junction Temperature Range                                                                                      | TJ                  | -40         | _   | +125 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA                  | -40         | —   | +85  | °C   |

| Extended Temperature Devices                                                                                              |                     |             |     |      |      |

| Operating Junction Temperature Range                                                                                      | TJ                  | -40         | —   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                       | TA                  | -40         | _   | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation: | PD                  | PINT + PI/O |     |      | W    |

| $I/O = \Sigma (\{VDD - VOH\} \times IOH) + \Sigma (VOL \times IOL)$                                                       |                     |             |     |      |      |

| Maximum Allowed Power Dissipation                                                                                         | Pdmax (Tj - Ta)/θja |             |     | W    |      |

### TABLE 22-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур | Max | Unit | Notes |

|------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 44-pin QFN   | θja    | 32  |     | °C/W | 1     |

| Package Thermal Resistance, 44-pin TFQP  | θја    | 45  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θја    | 45  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θја    | 50  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SSOP  | θја    | 71  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN-S | θja    | 35  | _   | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### SP36 SCKx (CKP = 0)SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx Bit 14 LSb MSb -1 SP30, SP31 SP40-SDIx LSb In MSb In Bit 1 SP41 Note: Refer to Figure 22-1 for load conditions.

# FIGURE 22-11: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = X, SMP = 1) TIMING CHARACTERISTICS

# TABLE 22-30:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHA       | RACTERIST             | ICS                                           | (unless o | <b>Operatin</b><br>otherwise<br>g temperat | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------|-----------------------|-----------------------------------------------|-----------|--------------------------------------------|----------------------------|-----------|-----------------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min       | Тур <sup>(2)</sup>                         | Max                        | Units     | Conditions                                                      |

| SP10         | TscP                  | Maximum SCK Frequency                         | _         | _                                          | 9                          | MHz       | See Note 3                                                      |

| SP20         | TscF                  | SCKx Output Fall Time                         | —         | —                                          | _                          | ns        | See parameter DO32 and Note 4                                   |

| SP21         | TscR                  | SCKx Output Rise Time                         | —         | —                                          | _                          | ns        | See parameter DO31 and Note 4                                   |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | —         | -                                          | _                          | ns        | See parameter DO32 and <b>Note 4</b>                            |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | —         | -                                          | —                          | ns        | See parameter DO31 and <b>Note 4</b>                            |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | —         | 6                                          | 20                         | ns        | —                                                               |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30        | —                                          | —                          | ns        | —                                                               |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30        | —                                          |                            | ns        | —                                                               |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30        | —                                          |                            | ns        |                                                                 |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

| AC CHA | RACTERI |                   |                           | (unless othe | ns: 3.0V to 3.6V<br>≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +125°C for Extended |       |                                             |

|--------|---------|-------------------|---------------------------|--------------|-------------------------------------------------------------------------------|-------|---------------------------------------------|

| Param  | Symbol  | Characte          | eristic <sup>(2)</sup>    | Min          | Max                                                                           | Units | Conditions                                  |

| IS10   | TLO:SCL | Clock Low Time    | 100 kHz mode              | 4.7          | _                                                                             | μS    | Device must operate at a minimum of 1.5 MHz |

|        |         |                   | 400 kHz mode              | 1.3          | -                                                                             | μS    | Device must operate at a minimum of 10 MHz  |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.5          |                                                                               | μS    | —                                           |

| IS11   | THI:SCL | Clock High Time   | 100 kHz mode              | 4.0          | —                                                                             | μS    | Device must operate at a minimum of 1.5 MHz |

|        |         |                   | 400 kHz mode              | 0.6          | —                                                                             | μS    | Device must operate at a minimum of 10 MHz  |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.5          |                                                                               | μS    | _                                           |

| IS20   | TF:SCL  | SDAx and SCLx     | 100 kHz mode              |              | 300                                                                           | ns    | CB is specified to be from                  |

|        |         | Fall Time         | 400 kHz mode              | 20 + 0.1 Св  | 300                                                                           | ns    | 10 to 400 pF                                |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | —            | 100                                                                           | ns    |                                             |

| IS21   | TR:SCL  | SDAx and SCLx     | 100 kHz mode              | —            | 1000                                                                          | ns    | CB is specified to be from                  |

|        |         | Rise Time         | 400 kHz mode              | 20 + 0.1 Св  | 300                                                                           | ns    | 10 to 400 pF                                |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | —            | 300                                                                           | ns    |                                             |

| IS25   | TSU:DAT | Data Input        | 100 kHz mode              | 250          |                                                                               | ns    | —                                           |

|        |         | Setup Time        | 400 kHz mode              | 100          |                                                                               | ns    |                                             |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 100          |                                                                               | ns    |                                             |

| IS26   | THD:DAT | Data Input        | 100 kHz mode              | 0            | 0                                                                             | μS    | —                                           |

|        |         | Hold Time         | 400 kHz mode              | 0            | 0.9                                                                           | μS    |                                             |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0            | 0.3                                                                           | μS    |                                             |

| IS30   | TSU:STA | Start Condition   | 100 kHz mode              | 4.7          |                                                                               | μS    | Only relevant for Repeated                  |

|        |         | Setup Time        | 400 kHz mode              | 0.6          |                                                                               | μS    | Start condition                             |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.25         |                                                                               | μS    |                                             |

| IS31   | THD:STA | Start Condition   | 100 kHz mode              | 4.0          |                                                                               | μS    | After this period, the first                |

|        |         | Hold Time         | 400 kHz mode              | 0.6          |                                                                               | μS    | clock pulse is generated                    |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.25         |                                                                               | μS    |                                             |

| IS33   | TSU:STO | Stop Condition    | 100 kHz mode              | 4.7          |                                                                               | μS    | _                                           |

|        |         | Setup Time        | 400 kHz mode              | 0.6          |                                                                               | μS    |                                             |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.6          | —                                                                             | μS    |                                             |

| IS34   | THD:ST  | Stop Condition    | 100 kHz mode              | 4000         | —                                                                             | ns    | —                                           |

|        | 0       | Hold Time         | 400 kHz mode              | 600          |                                                                               | ns    |                                             |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 250          |                                                                               | ns    |                                             |

| IS40   | TAA:SCL | Output Valid      | 100 kHz mode              | 0            | 3500                                                                          | ns    |                                             |

|        |         | From Clock        | 400 kHz mode              | 0            | 1000                                                                          | ns    |                                             |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0            | 350                                                                           | ns    |                                             |

| IS45   | TBF:SDA | Bus Free Time     | 100 kHz mode              | 4.7          |                                                                               | μS    | Time the bus must be free                   |

|        |         |                   | 400 kHz mode              | 1.3          |                                                                               | μS    | before a new transmission                   |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.5          | —                                                                             | μS    | can start                                   |

| IS50   | Св      | Bus Capacitive Lo | ading                     | —            | 400                                                                           | pF    |                                             |

# TABLE 22-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

2: These parameters are characterized by similarity, but are not tested in manufacturing.

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |           |           |                  |                                                  |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------------------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                 | Min.                                                                                                                                                                                                 | Тур       | Max.      | Units            | Conditions                                       |

|                    | A      | DC Accuracy (10-bit Mode)      | – Measu                                                                                                                                                                                              | rements   | s with ex | ternal V         | REF+/VREF- <sup>(3)</sup>                        |

| AD20b              | Nr     | Resolution <sup>(4)</sup>      | 1                                                                                                                                                                                                    | 0 data bi | ts        | bits             | _                                                |

| AD21b              | INL    | Integral Nonlinearity          | -1.5                                                                                                                                                                                                 | —         | +1.5      | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD22b              | DNL    | Differential Nonlinearity      | > -1                                                                                                                                                                                                 | -         | < 1       | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD23b              | Gerr   | Gain Error                     | -                                                                                                                                                                                                    | 3         | 6         | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD24b              | EOFF   | Offset Error                   | -                                                                                                                                                                                                    | 2         | 5         | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD25b              | —      | Monotonicity                   | —                                                                                                                                                                                                    | —         | —         | _                | Guaranteed <sup>(1)</sup>                        |

|                    | A      | DC Accuracy (10-bit Mode)      | ) – Meası                                                                                                                                                                                            | irement   | s with in | ternal V         | REF+/VREF- <sup>(3)</sup>                        |

| AD20b              | Nr     | Resolution <sup>(4)</sup>      | 1                                                                                                                                                                                                    | 0 data bi | ts        | bits             | —                                                |

| AD21b              | INL    | Integral Nonlinearity          | -1                                                                                                                                                                                                   | _         | +1        | LSb              | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD22b              | DNL    | Differential Nonlinearity      | > -1                                                                                                                                                                                                 | —         | < 1       | LSb              | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD23b              | Gerr   | Gain Error                     | _                                                                                                                                                                                                    | 7         | 15        | LSb              | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD24b              | EOFF   | Offset Error                   | _                                                                                                                                                                                                    | 3         | 7         | LSb              | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD25b              | _      | Monotonicity                   | _                                                                                                                                                                                                    | _         | _         | _                | Guaranteed <sup>(1)</sup>                        |

|                    |        | Dynamic P                      | erformar                                                                                                                                                                                             | nce (10-l | oit Mode  | ) <sup>(2)</sup> |                                                  |

| AD30b              | THD    | Total Harmonic Distortion      | _                                                                                                                                                                                                    | _         | -64       | dB               | —                                                |

| AD31b              | SINAD  | Signal to Noise and Distortion | 57                                                                                                                                                                                                   | 58.5      | —         | dB               | _                                                |

| AD32b              | SFDR   | Spurious Free Dynamic<br>Range | 72                                                                                                                                                                                                   | _         |           | dB               | _                                                |

| AD33b              | Fnyq   | Input Signal Bandwidth         |                                                                                                                                                                                                      |           | 550       | kHz              | —                                                |

| AD34b              | ENOB   | Effective Number of Bits       | 9.16                                                                                                                                                                                                 | 9.4       | _         | bits             |                                                  |

# TABLE 22-40: ADC MODULE SPECIFICATIONS (10-BIT MODE)<sup>(4)</sup>

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage, and has no missing codes.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: These parameters are characterized, but are tested at 20 ksps only.

4: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

| Other Instructions                                  |     |

|-----------------------------------------------------|-----|

| Instruction Set                                     |     |

| Overview                                            |     |

| Summary                                             | 187 |

| Instruction-Based Power-Saving Modes                |     |

| ldle                                                |     |

| Sleep                                               |     |

| Internal RC Oscillator                              |     |

| Use with WDT                                        |     |

| Internet Address                                    |     |

| Interrupt Control and Status Registers              |     |

| IECx                                                |     |

| IFSx                                                |     |

| INTCON1                                             |     |

| INTCON2                                             |     |

| IPCx                                                |     |

| Interrupt Setup Procedures                          |     |

| Initialization                                      |     |

| Interrupt Disable                                   |     |

| Interrupt Service Routine                           |     |

| Trap Service Routine                                |     |

| Interrupt Vector Table (IVT)                        |     |

| Interrupts Coincident with Power Save Instructions. |     |

| interrupte confordent with rower ouve instructions. |     |

# J

| JTAG Boundary Scan Interface |  |

|------------------------------|--|

|------------------------------|--|

### Μ

| Memory Organization                               | 25    |

|---------------------------------------------------|-------|

| Microchip Internet Web Site                       | . 283 |

| MPLAB ASM30 Assembler, Linker, Librarian          | . 196 |

| MPLAB Integrated Development Environment Software | . 195 |

| MPLAB PM3 Device Programmer                       | . 198 |

| MPLAB REAL ICE In-Circuit Emulator System         | . 197 |

| MPLINK Object Linker/MPLIB Object Librarian       | . 196 |

| Multi-bit Data Shifter                            | 23    |

# Ν

| NVM Module |     |  |

|------------|-----|--|

| Register   | Мар |  |

# 0

| Open-Drain Configuration |  |

|--------------------------|--|

| Output Compare           |  |

| Registers                |  |

# Ρ

| Packaging                                                 |            |

|-----------------------------------------------------------|------------|

| Details                                                   | 259        |

| Marking                                                   |            |

| Peripheral Module Disable (PMD)                           | 100        |

| Pinout I/O Descriptions (table)                           | 11         |

| PMD Module                                                |            |

| Register Map                                              |            |

| PORTA                                                     |            |

| Register Map                                              |            |

| PORTB                                                     |            |

| Register Map                                              |            |

| Power-on Reset (POR)                                      | 59         |

| Power-Saving Features                                     |            |

| Clock Frequency and Switching                             |            |

| Program Address Space                                     |            |

| Construction                                              |            |

| Data Access from Program Memory Using<br>Space Visibility | •          |

|                                                           |            |

| Data Access from Program Memory Using Table               | e instruc- |

| tions                                             |

|---------------------------------------------------|

| Data Access from, Address Generation 43           |

| Memory Map25                                      |

| Table Read Instructions                           |

| TBLRDH 44                                         |

| TBLRDL 44                                         |

| Visibility Operation 45                           |

| Program Memory                                    |

| Interrupt Vector                                  |

| Organization                                      |

| Reset Vector                                      |

| _                                                 |

| R                                                 |

| Reader Response                                   |

| Registers                                         |

| AD1CHS0 (ADC1 Input Channel 0 Select 175          |

| AD1CHS123 (ADC1 Input Channel 1, 2, 3 Select) 173 |

| AD1CON1 (ADC1 Control 1) 169                      |

| AD1CON2 (ADC1 Control 2) 171                      |

| AD1CON3 (ADC1 Control 3) 172                      |

| AD1CSSL (ADC1 Input Scan Select Low)              |

| AD1PCFGL (ADC1 Port Configuration Low)            |