Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp202-e-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

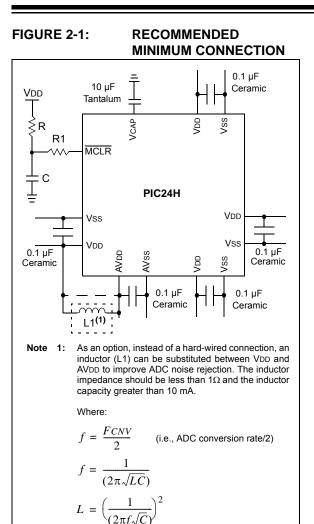

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the microcontroller, and the maximum current drawn by the microcontroller in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

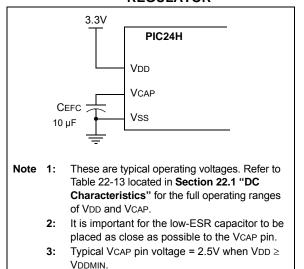

#### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 22.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 19.2 "On-Chip Voltage Regulator"** for details.

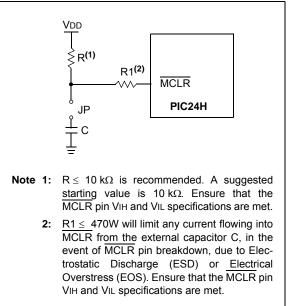

### 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that capacitor C is isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN CONNECTIONS

# DS70289J-page 30

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR PIC24HJ32GP202

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|--------|-------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  |        | _     | —       | CN7IE   | CN6IE   | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | CN30IE  | CN29IE  | _       | CN27IE  |        | _     | CN24IE  | CN23IE  | CN22IE  | CN21IE  |        |        |        | _      | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE |        | _     | _       | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | _       | CN27PUE | _      |       | CN24PUE | CN23PUE | CN22PUE | CN21PUE | _      | _      | _      | _      | CN16PUE | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR PIC24HJ32GP204 AND PIC24HJ16GP304

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE   | CN8IE   | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | —       | CN30IE  | CN29IE  | CN28IE  | CN27IE  | CN26IE  | CN25IE  | CN24IE  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE  | CN8PUE  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | CN28PUE | CN27PUE | CN26PUE | CN25PUE | CN24PUE | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-13:       PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR PIC24HJ32GP204 AND PIC24HJ16GP304 |      |        |        |        |        |                                  |            |  |       |       |       |            |            |           |           |          |               |      |

|---------------------------------------------------------------------------------------------------|------|--------|--------|--------|--------|----------------------------------|------------|--|-------|-------|-------|------------|------------|-----------|-----------|----------|---------------|------|

| File Name                                                                                         | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 |            |  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3      | Bit 2     | Bit 1     | Bit 0    | All<br>Resets |      |

| RPOR0                                                                                             | 06C0 | —      | _      | —      |        | RP1R<4:0>                        |            |  | _     | _     | _     | RP0R<4:0>  |            |           |           | 0000     |               |      |

| RPOR1                                                                                             | 06C2 | _      | _      | _      |        | RP3R<4:0>                        |            |  |       |       | _     | _          |            |           | RP2R<4:0> | •        |               | 0000 |

| RPOR2                                                                                             | 06C4 | _      | _      |        |        | RP5R<4:0>                        |            |  |       | _     | _     | _          |            |           | RP4R<4:0> | •        |               | 0000 |

| RPOR3                                                                                             | 06C6 |        | _      |        |        | RP7R<4:0>                        |            |  |       | _     | _     | _          |            |           | RP6R<4:0> | <b>`</b> |               | 0000 |

| RPOR4                                                                                             | 06C8 | _      | _      | _      |        | RP9R<4:0>                        |            |  |       | _     | _     | _          |            |           | RP8R<4:0> | >        |               | 0000 |

| RPOR5                                                                                             | 06CA | _      | _      |        |        | RP11R<4:0>                       |            |  |       | _     | _     | _          | RP10R<4:0> |           |           |          | 0000          |      |

| RPOR6                                                                                             | 06CC |        | _      |        |        | F                                | RP13R<4:0> |  |       | _     | _     | _          | RP12R<4:0> |           |           |          | 0000          |      |

| RPOR7                                                                                             | 06CE |        | _      |        |        | F                                | RP15R<4:0> |  |       | _     | _     | _          | RP14R<4:0> |           |           |          | 0000          |      |

| RPOR8                                                                                             | 06D0 |        | _      |        |        | F                                | RP17R<4:0  |  |       | _     | _     | _          |            |           | RP16R<4:0 | >        |               | 0000 |

| RPOR9                                                                                             | 06D2 |        | _      |        |        | F                                | RP19R<4:0> |  |       | _     | _     | _          | RP18R<4:0> |           |           |          | 0000          |      |

| RPOR10                                                                                            | 06D4 | _      | _      |        |        | RP21R<4:0>                       |            |  |       | —     |       | RP20R<4:0> |            |           |           | 0000     |               |      |

| RPOR11                                                                                            | 06D6 | _      | _      | _      |        | RP23R<4:0>                       |            |  | _     | _     | _     |            |            | RP22R<4:0 | >         |          | 0000          |      |

| RPOR12                                                                                            | 06D8 | _      | _      | _      |        | F                                | RP25R<4:0> |  |       | _     | _     | _          |            |           | RP24R<4:0 | >        |               | 0000 |

x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### 6.2 Reset Control Registers

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0      | R/W-0                                     | U-0                                                                                                                                                  | U-0                        | U-0                   | U-0                | R/W-0            | R/W-0         |  |  |

|------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|--------------------|------------------|---------------|--|--|

| TRAPR      | R IOPUWR                                  |                                                                                                                                                      | —                          |                       |                    | СМ               | VREGS         |  |  |

| bit 15     |                                           |                                                                                                                                                      |                            |                       |                    |                  | bit 8         |  |  |

|            |                                           |                                                                                                                                                      |                            |                       |                    |                  |               |  |  |

| R/W-0      | R/W-0                                     | R/W-0                                                                                                                                                | R/W-0                      | R/W-0                 | R/W-0              | R/W-1            | R/W-1         |  |  |

| EXTR       | SWR                                       | SWDTEN <sup>(2)</sup>                                                                                                                                | WDTO                       | SLEEP                 | IDLE               | BOR              | POR           |  |  |

| bit 7      |                                           |                                                                                                                                                      |                            |                       |                    |                  | bit 0         |  |  |

|            |                                           |                                                                                                                                                      |                            |                       |                    |                  |               |  |  |

| Legend:    |                                           |                                                                                                                                                      |                            |                       |                    |                  |               |  |  |

| R = Reada  |                                           | W = Writable                                                                                                                                         | oit                        | -                     | nented bit, read   |                  |               |  |  |

| -n = Value | at POR                                    | '1' = Bit is set                                                                                                                                     |                            | '0' = Bit is cle      | ared               | x = Bit is unkr  | nown          |  |  |

| bit 15     | 1 = A Trap Co                             | Reset Flag bit<br>onflict Reset ha<br>onflict Reset ha                                                                                               | s occurred                 | d                     |                    |                  |               |  |  |

| bit 14     | 1 = An illega<br>Address                  | egal Opcode or<br>al opcode detec<br>Pointer caused<br>I opcode or unit                                                                              | ction, an illeg<br>a Reset | al address m          | ode or uninitial   | ized W registe   | r used as an  |  |  |

| bit 13-10  | Unimplemen                                | Unimplemented: Read as '0'                                                                                                                           |                            |                       |                    |                  |               |  |  |

| bit 9      | 1 = A configu                             | <b>CM:</b> Configuration Mismatch Flag bit<br>1 = A configuration mismatch Reset has occurred<br>0 = A configuration mismatch Reset has not occurred |                            |                       |                    |                  |               |  |  |

| bit 8      | VREGS: Volta                              | age Regulator S                                                                                                                                      | Standby Durin              | ig Sleep bit          |                    |                  |               |  |  |

|            |                                           | egulator is active<br>egulator goes in                                                                                                               |                            |                       | еер                |                  |               |  |  |

| bit 7      | EXTR: Extern                              | nal Reset (MCL                                                                                                                                       | R) Pin bit                 |                       |                    |                  |               |  |  |

|            |                                           | Clear (pin) Res<br>Clear (pin) Res                                                                                                                   |                            |                       |                    |                  |               |  |  |

| bit 6      | SWR: Softwa                               | ire Reset (Instru                                                                                                                                    | uction) Flag bi            | it                    |                    |                  |               |  |  |

|            |                                           | instruction has instruction has                                                                                                                      |                            |                       |                    |                  |               |  |  |

| bit 5      | SWDTEN: So                                | oftware Enable/                                                                                                                                      | Disable of WI              | DT bit <sup>(2)</sup> |                    |                  |               |  |  |

|            | 1 = WDT is e<br>0 = WDT is d              |                                                                                                                                                      |                            |                       |                    |                  |               |  |  |

| bit 4      | WDTO: Watc                                | hdog Timer Tim                                                                                                                                       | ne-out Flag bit            | t                     |                    |                  |               |  |  |

|            |                                           | e-out has occur<br>e-out has not oc                                                                                                                  |                            |                       |                    |                  |               |  |  |

| bit 3      | SLEEP: Wak                                | e-up from Slee                                                                                                                                       | o Flag bit                 |                       |                    |                  |               |  |  |

|            |                                           | as been in Slee<br>as not been in S                                                                                                                  |                            |                       |                    |                  |               |  |  |

| bit 2      | IDLE: Wake-u                              | up from Idle Fla                                                                                                                                     | g bit                      |                       |                    |                  |               |  |  |

|            | 1 = Device wa                             | as in Idle mode<br>as not in Idle m                                                                                                                  | -                          |                       |                    |                  |               |  |  |

|            | All of the Reset sta<br>cause a device Re |                                                                                                                                                      | set or cleared             | d in software. S      | Setting one of the | ese bits in soft | vare does not |  |  |

| 2:         | If the FWDTEN Co                          | onfiguration bit i                                                                                                                                   | s '1' (unprogr             | ammed), the V         | VDT is always e    | enabled, regard  | less of the   |  |  |

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### 9.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 9.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### **10.9** Peripheral Pin Select Registers

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices implement 17 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (9)

- Output Remappable Peripheral Registers (8)

- Note: Input and Output Register values can only be changed if the IOLOCK bit (OSC-CON<6>) = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 10-21: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0 U-0 U-0 R/W-0 R/W-0<br>— — — — — — — — — — — — — — — — — — — | -0 R/W-0 R/W-0 R/W-0<br>RP23R<4:0><br>bit 8 |

|------------------------------------------------------------------|---------------------------------------------|

|                                                                  |                                             |

| bit 15                                                           | bit 8                                       |

|                                                                  |                                             |

|                                                                  |                                             |

| U-0 U-0 U-0 R/W-0 R/W-0                                          | -0 R/W-0 R/W-0 R/W-0                        |

|                                                                  | RP22R<4:0>                                  |

| bit 7                                                            | bit 0                                       |

|                                                                  |                                             |

| Legend:                                                          |                                             |

| Legena.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-22: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| U-0                                | U-0 | U-0 | R/W-0 | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |  |  |  |  |

|------------------------------------|-----|-----|-------|-----------------------------------------|-----------|-------|-------|--|--|--|--|

| —                                  |     |     |       | RP25R<4:0>                              |           |       |       |  |  |  |  |

| bit 15                             |     |     |       |                                         |           |       | bit 8 |  |  |  |  |

|                                    |     |     |       |                                         |           |       |       |  |  |  |  |

| U-0                                | U-0 | U-0 | R/W-0 | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |  |  |  |  |

|                                    |     |     |       |                                         | RP24R<4:0 | >     |       |  |  |  |  |

| bit 7                              |     |     |       |                                         |           |       | bit 0 |  |  |  |  |

|                                    |     |     |       |                                         |           |       |       |  |  |  |  |

| Legend:                            |     |     |       |                                         |           |       |       |  |  |  |  |

| R = Readable bit W = Writable b    |     |     | bit   | bit U = Unimplemented bit, read as '0'  |           |       |       |  |  |  |  |

| -n = Value at POR '1' = Bit is set |     |     |       | '0' = Bit is cleared x = Bit is unknown |           |       |       |  |  |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP25R<4:0>:** Peripheral Output Function is Assigned to RP25 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP24R<4:0>:** Peripheral Output Function is Assigned to RP24 Output Pin (see Table 10-2 for peripheral function numbers)

#### 11.1 Timer Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 11.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70205)

- Code Samples

- Application Notes

- Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                            |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                    |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                     |

|       | 1 = Read – indicates data transfer is output from slave                                                                                                                                                               |

|       | 0 = Write – indicates data transfer is input to slave                                                                                                                                                                 |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                                                                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                   |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                                                                                                 |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                                                                                            |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                                                                                                  |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                  |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul> |

#### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

```

bit 4-0 CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits

PIC24HJ32GP204 and PIC24HJ16GP304 devices only:

01100 = Channel 0 positive input is AN12

.

.

00010 = Channel 0 positive input is AN2

00001 = Channel 0 positive input is AN1

00000 = Channel 0 positive input is AN0

PIC24HJ32GP202 devices only:

01100 = Channel 0 positive input is AN12

.

.

01000 = Reserved

00111 = Reserved

00110 = Reserved

00110 = Reserved

.

.

00010 = Channel 0 positive input is AN2

00010 = Channel 0 positive input is AN1

00010 = Channel 0 positive input is AN1

```

#### 19.2 On-Chip Voltage Regulator

PIC24HJ32GP202/204 All of the and PIC24HJ16GP304 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24HJ32GP202/204 and PIC24HJ16GP304 family incorporate an on-chip regulator that allows the device to run its core logic from Vdd.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 19-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 22-13 located in **Section 22.1** "**DC Characteristics**".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 19-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 19.3 Brown-Out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device in case VDD falls below the BOR threshold voltage.

| DC CHARACTERISTICS                 |                   |                                                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                         |  |

|------------------------------------|-------------------|-------------------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|-------------------------|--|

| Param<br>No. Symbol Characteristic |                   |                                                                         |                                                       | Тур <sup>(1)</sup> | Max | Units | Conditions              |  |

| Operating Voltage                  |                   |                                                                         |                                                       |                    |     |       |                         |  |

| DC10                               | 10 Supply Voltage |                                                                         |                                                       |                    |     |       |                         |  |

|                                    | Vdd               |                                                                         | 3.0                                                   | _                  | 3.6 | V     | Industrial and Extended |  |

| DC12                               | Vdr               | RAM Data Retention Voltage <sup>(2)</sup>                               | 1.8                                                   | _                  | —   | V     | —                       |  |

| DC16                               | VPOR              | VDD <b>Start Voltage</b><br>to ensure internal<br>Power-on Reset signal | _                                                     | _                  | Vss | V     | _                       |  |

| DC17                               | SVDD              | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal     | 0.03                                                  | _                  | —   | V/ms  | 0-3.0V in 0.1s          |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

| DC CHARACTERISTICS |        |                                                                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                                                                                                      |  |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|-------|------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                                                                                 | Min.                                                 | Тур. | Max. | Units | Conditions                                                                                           |  |

| DO10               | Vol    | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - All pins not<br>defined by 4x or 8x driver pins       | _                                                    | _    | 0.4  | V     | Iol $\leq$ 3 mA, Vdd = 3.3V                                                                          |  |

|                    |        | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA0, RA1,<br>RB5, RB6, RB8, RB9, RB14                 | _                                                    | _    | 0.4  | v     | $\text{IOL} \leq 6 \text{ mA, VDD} = 3.3 \text{V}$                                                   |  |

|                    |        | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - OSCO,<br>CLKO, RA3                                    | _                                                    | _    | 0.4  | v     | Iol $\leq$ 10 mA, Vdd = 3.3V                                                                         |  |

| DO20               | Vон    | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins<br>not defined by 4x or 8x driver<br>pins | 2.4                                                  |      | _    | V     | Iol $\geq$ -3 mA, Vdd = 3.3V                                                                         |  |

|                    |        | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA0,<br>RA1, RB5, RB6, RB8, RB9,<br>RB14           | 2.4                                                  | _    | _    | v     | $IOL \geq -6 \ mA, \ VDD = 3.3 V$                                                                    |  |

|                    |        | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - OSCO,<br>CLKO, RA3                                 | 2.4                                                  | _    | _    | V     | IOL $\ge$ -10 mA, VDD = 3.3V                                                                         |  |

| DO20A              | Voн1   | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - All pins<br>not defined by 4x or 8x driver<br>pins | 1.5                                                  | _    | _    | V     | $\begin{array}{l} \text{IOH} \geq \text{-6 mA, VDD} = 3.3 \text{V} \\ \text{See Note 1} \end{array}$ |  |

|                    |        |                                                                                                                | 2.0                                                  | _    | _    |       | IOH ≥ -5 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |  |

|                    |        |                                                                                                                | 3.0                                                  | _    | _    |       | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |  |

|                    |        | <b>Output High Voltage</b><br>4x Source Driver Pins - RA0,<br>RA1, RB5, RB6, RB8, RB9,<br>RB14                 | 1.5                                                  | _    | _    | V     | Іон ≥ -12 mA, Voo = 3.3V<br>See <b>Note 1</b>                                                        |  |

|                    |        |                                                                                                                | 2.0                                                  | _    | _    |       | Іон ≥ -11 mA, Vpd = 3.3V<br>See <b>Note 1</b>                                                        |  |

|                    |        |                                                                                                                | 3.0                                                  | _    | _    |       | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins - OSCO,<br>CLKO, RA3                                              | 1.5                                                  | _    | _    |       | IOH ≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                        |  |

|                    |        |                                                                                                                | 2.0                                                  | _    | _    | V     | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                        |  |

|                    |        |                                                                                                                | 3.0                                                  | —    | _    |       | IOH ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                         |  |

#### TABLE 22-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

## TABLE 22-21:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMERTIMING REQUIREMENTS

|              |        |                                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                 |     |       |                                                                                          |  |

|--------------|--------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-------|------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                                | Min                                                                                                                                                                                                                                                                                   | Тур <sup>(2)</sup>              | Max | Units | Conditions                                                                               |  |

| SY10         | TMCL   | MCLR Pulse-Width (low) <sup>(1)</sup>                                         | 2                                                                                                                                                                                                                                                                                     | _                               | _   | μS    | -40°C to +85°C                                                                           |  |

| SY11         | TPWRT  | Power-up Timer Period <sup>(1)</sup>                                          |                                                                                                                                                                                                                                                                                       | 2<br>4<br>16<br>32<br>64<br>128 |     | ms    | -40°C to +85°C<br>User programmable                                                      |  |

| SY12         | TPOR   | Power-on Reset Delay <sup>(3)</sup>                                           | 3                                                                                                                                                                                                                                                                                     | 10                              | 30  | μs    | -40°C to +85°C                                                                           |  |

| SY13         | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset <sup>(1)</sup> | 0.68                                                                                                                                                                                                                                                                                  | 0.72                            | 1.2 | μS    | _                                                                                        |  |

| SY20         | Twdt1  | Watchdog Timer Time-out<br>Period <sup>(1)</sup>                              | _                                                                                                                                                                                                                                                                                     | _                               | _   | ms    | See Section 19.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21a (Table 22-19). |  |

| SY30         | Tost   | Oscillator Start-up Time                                                      | _                                                                                                                                                                                                                                                                                     | 1024<br>Tosc                    | _   | —     | Tosc = OSC1 period                                                                       |  |

| SY35         | TFSCM  | Fail-Safe Clock Monitor<br>Delay <sup>(1)</sup>                               | _                                                                                                                                                                                                                                                                                     | 500                             | 900 | μS    | -40°C to +85°C                                                                           |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

3: These parameters are characterized by similarity, but are not tested in manufacturing.

NOTES:

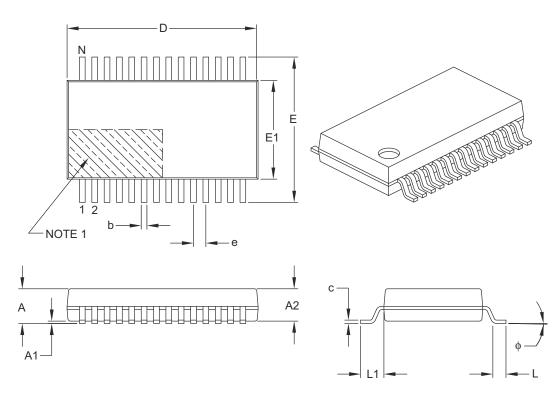

#### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |       |       |  |  |

|--------------------------|------------------|----------|-------|-------|--|--|

| Dimensio                 | Dimension Limits |          |       | MAX   |  |  |

| Number of Pins           | Ν                | 28       |       |       |  |  |

| Pitch                    | е                | 0.65 BSC |       |       |  |  |

| Overall Height           | Α                |          |       | 2.00  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75  | 1.85  |  |  |

| Standoff                 | A1               | 0.05     | -     | _     |  |  |

| Overall Width            | E                | 7.40     | 7.80  | 8.20  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30  | 5.60  |  |  |

| Overall Length           | D                | 9.90     | 10.20 | 10.50 |  |  |

| Foot Length              | L                | 0.55     | 0.75  | 0.95  |  |  |

| Footprint                | L1               | 1.25 REF |       |       |  |  |

| Lead Thickness           | с                | 0.09     | -     | 0.25  |  |  |

| Foot Angle               | ф                | 0°       | 4°    | 8°    |  |  |

| Lead Width               | b                | 0.22     | _     | 0.38  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

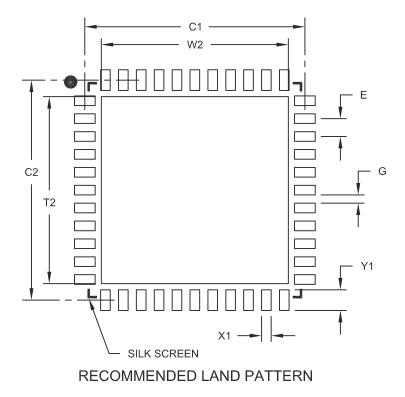

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensior                  | MIN         | NOM      | MAX  |      |  |

| Contact Pitch              | E           | 0.65 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 6.80 |  |

| Optional Center Pad Length | T2          |          |      | 6.80 |  |

| Contact Pad Spacing        | C1          |          | 8.00 |      |  |

| Contact Pad Spacing        | C2          |          | 8.00 |      |  |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |  |

| Contact Pad Length (X44)   | Y1          |          |      | 0.80 |  |

| Distance Between Pads      | G           | 0.25     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

NOTES: