Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp202-e-ss |

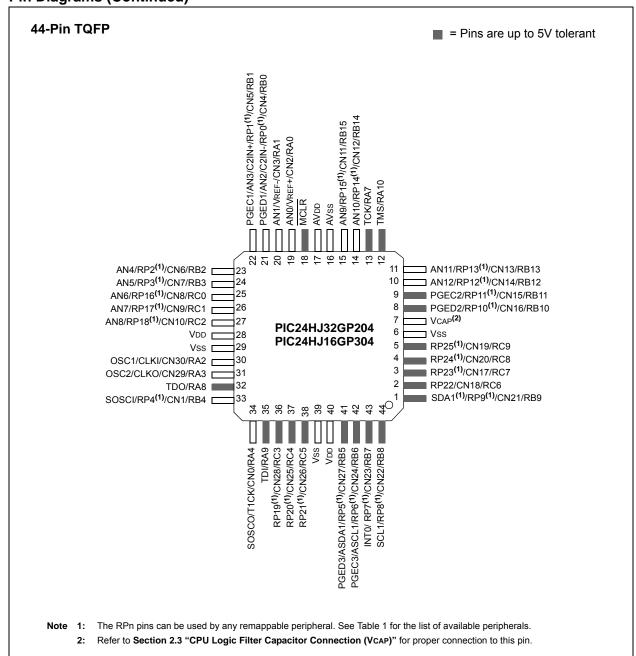

### Pin Diagrams (Continued)

#### 3.3 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en530271

#### 3.3.1 KEY RESOURCES

- Section 2. "CPU" (DS70204)

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- · Development Tools

#### 4.2 Data Address Space

The CPU has a separate 16 bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to the bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

PIC24HJ32GP202/204 and PIC24HJ16GP304 devices implement up to 2 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16 bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

# 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC® devices and improve data space memory usage efficiency, the PIC24HJ32GP202/204 and PIC24HJ16GP304 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or when translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the instruction occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the PIC24HJ32GP202/204 and PIC24HJ16GP304 core and peripheral modules to control the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-22.

Note: The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8 Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MoV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an address pointer.

#### TABLE 4-16: PORTA REGISTER MAP FOR PIC24HJ32GP202

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | _      | _      | _      | -      | _      | _      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA     | 02C2 | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 02C6 | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: PORTA REGISTER MAP FOR PIC24HJ32GP204 AND PIC24HJ16GP304

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | AII<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | -      | _      | -      | _      | -      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | -     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA     | 02C2 | 1      | _      | -      | -      | _      | RA10    | RA9    | RA8    | RA7    | 1     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | 1      | _      | -      | -      | _      | LATA10  | LATA9  | LATA8  | LATA7  | 1     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 02C6 | 1      | _      | -      | -      | _      | ODCA10  | ODCA9  | ODCA8  | ODCA7  | 1     | 1     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-18: PORTB REGISTER MAP**

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB      | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### TABLE 4-19: PORTC REGISTER MAP FOR PIC24HJ32GP204 AND PIC24HJ16GP304

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC     | 02D0 | _      | _      | _      | _      | _      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC     | 02D2 | _      | _      | _      | -      | _      | _      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC4    | RC2    | RC1    | RC0    | xxxx          |

| LATC      | 02D4 | _      | _      | _      | -      | _      | _      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC4  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC      | 02D6 | _      | _      | _      | _      | _      | _      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC4  | ODCC2  | ODCC1  | ODCC0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8                                         | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-----------------------------------------------|-------|-------|--------|-------|---------|-------|-------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _         | _      | _      | _      | СМ        | VREGS                                         | EXTR  | SWR   | SWDTEN | WDTO  | SLEEP   | IDLE  | BOR   | POR   | <sub>XXXX</sub> (1) |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | _      | 1      | NOSC<2:0  | 2:0> CLKLOCK IOLOCK LOCK — CF — LPOSCEN OSWEN |       |       |        |       | 0300(2) |       |       |       |                     |

| CLKDIV    | 0744 | ROI    | [      | OOZE<2:0> | •      | DOZEN  | F      | RCDIV<2:0 | 2:0> PLLPOST<1:0> — PLLPRE<4:0>               |       |       |        |       | 3040    |       |       |       |                     |

| PLLFBD    | 0746 | _      | _      | _         | _      | _      | _      | _         | PLLDIV<8:0>                                   |       |       |        |       | 0030    |       |       |       |                     |

| OSCTUN    | 0748 | ı      | _      | _         |        | _      | _      |           | TUN<5:0>                                      |       |       |        |       |         |       | 0000  |       |                     |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-21: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0   | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------------|-------|-------|-------|------------|-------|-------|---------|---------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | _     | _     | _           | ERASE | _     | 1     | NVMOP<3:0> |       |       | 0000(1) |               |

| NVMKEY    | 0766 | _      | _      | _      | _      | _      | -      | -     | _     | NVMKEY<7:0> |       |       |       |            |       | 0000  |         |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-22: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1      | 0770 | _      | _      | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | -     | U1MD  | _     | SPI1MD | _     | _     | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | _      | _      | _      | -      | IC2MD | IC1MD | _      | _     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

PIC24HJ32GP202/204 AND PIC24HJ16GP304

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| NOTES: | 1 102-1110 | 0201 201 |  | Z-1110 1 C | 01 30+ |  |

|--------|------------|----------|--|------------|--------|--|

|        | NOTES:     |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

|        |            |          |  |            |        |  |

#### 6.5 External Reset (EXTR)

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse-width will generate a Reset. Refer to **Section 22.0 "Electrical Characteristics"** for minimum pulse-width specifications. The External Reset (MCLR) Pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.5.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate reset signals to Reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to Reset the device when the rest of system is Reset.

#### 6.5.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to Reset the device, the external reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the  $\overline{\text{MCLR}}$  pin will not be used to generate a Reset. The external reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert  $\overline{SYSRST}$ , placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain.  $\overline{SYSRST}$  is released at the next instruction cycle, and the reset vector fetch will commence.

The Software Reset (Instruction) Flag (SWR) bit in the Reset Control register (RCON<6>) is set to indicate the software Reset.

#### 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out Flag bit (WDTO) in the Reset Control register (RCON<4>) is set to indicate the Watchdog Reset. Refer to **Section 19.4** "**Watchdog Timer (WDT)**" for more information on Watchdog Reset.

#### 6.8 Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-priority trap is being processed, a hard trap conflict Reset occurs. The hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

The Trap Reset Flag bit (TRAPR) in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to **Section 7.0** "Interrupt Controller" for more information on trap conflict Resets.

#### REGISTER 10-9: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1     | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | SS1R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

•

•

•

00001 = Input tied to RP1 00000 = Input tied to RP0

#### REGISTER 10-10: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| _      | _   | _   |       |       | RP1R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| _     | _   | _   |       |       | RP0R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 RP1R<4:0>: Peripheral Output Function is Assigned to RP1 Output Pin (see Table 10-2 for peripheral

function numbers)

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RP0R<4:0>: Peripheral Output Function is Assigned to RP0 Output Pin (see Table 10-2 for peripheral

function numbers)

#### REGISTER 12-2: T3CON CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(2)</sup> | _   | TSIDL <sup>(1)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0 | R/W-0                | U-0 | U-0 | R/W-0              | U-0   |

|-------|----------------------|-------|----------------------|-----|-----|--------------------|-------|

| _     | TGATE <sup>(2)</sup> | TCKPS | <1:0> <sup>(2)</sup> | _   | _   | TCS <sup>(2)</sup> | _     |

| bit 7 |                      |       |                      |     |     |                    | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timer3 On bit<sup>(2)</sup>

1 = Starts 16-bit Timer3

0 = Stops 16-bit Timer3

bit 14 **Unimplemented:** Read as '0'

bit 13 **TSIDL:** Stop in Idle Mode bit<sup>(1)</sup>

1 = Discontinue timer operation when device enters Idle mode

0 = Continue timer operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 TGATE: Timer3 Gated Time Accumulation Enable bit<sup>(2)</sup>

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation enabled 0 = Gated time accumulation disabled

bit 5-4 TCKPS<1:0>: Timer3 Input Clock Prescale Select bits(2)

11 = 1:256 prescale value 10 = 1:64 prescale value 01 = 1:8 prescale value

00 = 1:1 prescale value

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timer3 Clock Source Select bit<sup>(2)</sup>

1 = External clock from T3CK pin

0 = Internal clock (Fosc/2)

bit 0 **Unimplemented:** Read as '0'

Note 1: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), these bits have no effect.

#### 19.7 In-Circuit Serial Programming

PIC24HJ32GP202/204 and PIC24HJ16GP304 family microcontrollers can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) document for details about In-Circuit Serial Programming™ (ICSP)™.

Any of the following three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- · PGEC3 and PGED3

#### 19.8 In-Circuit Debugger

When MPLAB® ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the Emulation/Debug Clock (PGECx) and Emulation/Debug Data (PGEDx) pin functions.

Any of the following three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- · PGEC2 and PGED2

- PGEC3 and PGED3

To make use of the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{\text{MCLR}}$ , VDD, VSs and PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

TABLE 20-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                                               |

| (text)          | Means "content of text"                                                                                       |

| [text]          | Means "the location addressed by text"                                                                        |

| { }             | Optional field or operation                                                                                   |

| <n:m></n:m>     | Register bit field                                                                                            |

| .b              | Byte mode selection                                                                                           |

| .d              | Double Word mode selection                                                                                    |

| .S              | Shadow register select                                                                                        |

| .W              | Word mode selection (default)                                                                                 |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}                                       |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                          |

| Expr            | Absolute address, label or expression (resolved by the linker)                                                |

| f               | File register address ∈ {0x00000x1FFF}                                                                        |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                                                |

| lit4            | 4-bit unsigned literal ∈ {015}                                                                                |

| lit5            | 5-bit unsigned literal ∈ {031}                                                                                |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                                               |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode                                        |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                                            |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                                            |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                                         |

| None            | Field does not require an entry, may be blank                                                                 |

| PC              | Program Counter                                                                                               |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                                             |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                                         |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                                                |

| Wb              | Base W register ∈ {W0W15}                                                                                     |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                             |

| Wdo             | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                             |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                                                   |

| Wm*Wm           | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7} |

| Wn              | One of 16 working registers ∈ {W0W15}                                                                         |

| Wnd             | One of 16 destination working registers ∈ {W0W15}                                                             |

| Wns             | One of 16 source working registers ∈ {W0W15}                                                                  |

| WREG            | W0 (working register used in file register instructions)                                                      |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                  |

| Wso             | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                         |

#### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr | Assembly<br>Mnemonic |         | Assembly Syntax | Description                                   | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|---------------|----------------------|---------|-----------------|-----------------------------------------------|---------------|----------------|--------------------------|

| 12            | BTST                 | BTST    | f,#bit4         | Bit Test f                                    | 1             | 1              | Z                        |

|               | 2.0.                 | BTST.C  | Ws,#bit4        | Bit Test Ws to C                              | 1             | 1              | C                        |

|               |                      | BTST.Z  | Ws,#bit4        | Bit Test Ws to Z                              | 1             | 1              | Z                        |

|               |                      | BTST.C  | Ws, Wb          | Bit Test Ws <wb> to C</wb>                    | 1             | 1              | C                        |

|               |                      | BTST.Z  | Ws,Wb           | Bit Test Ws <wb> to Z</wb>                    | 1             | 1              | Z                        |

| 13            | BTSTS                | BTSTS   | f,#bit4         | Bit Test then Set f                           | 1             | 1              | Z                        |

| .0            | 2.0.0                | BTSTS.C | Ws,#bit4        | Bit Test Ws to C, then Set                    | 1             | 1              | C                        |

|               |                      | BTSTS.Z | Ws,#bit4        | Bit Test Ws to Z, then Set                    | 1             | 1              | Z                        |

| 14            | CALL                 | CALL    | lit23           | Call subroutine                               | 2             | 2              | None                     |

| •             | 07122                | CALL    | Wn              | Call indirect subroutine                      | 1             | 2              | None                     |

| 15            | CLR                  | CLR     | f               | f = 0x0000                                    | 1             | 1              | None                     |

| .0            | 02.1                 | CLR     | WREG            | WREG = 0x0000                                 | 1             | 1              | None                     |

|               |                      | CLR     | Ws              | Ws = 0x0000                                   | 1             | 1              | None                     |

| 16            | CLRWDT               | CLRWDT  |                 | Clear Watchdog Timer                          | 1             | 1              | WDTO,Sleep               |

| 17            | COM                  | COM     | f               | f = f                                         | 1             | 1              | N,Z                      |

| •             |                      | COM     | f,WREG          | WREG = f                                      | 1             | 1              | N,Z                      |

|               |                      |         | Ws, Wd          | Wd = Ws                                       | 1             | 1              | N,Z                      |

| 18            | СР                   | COM     | f               | Compare f with WREG                           | 1             | 1              | C,DC,N,OV,Z              |

| 10            | CF                   | CP      | Wb,#lit5        | Compare Wb with lit5                          | 1             | 1              | C,DC,N,OV,Z              |

|               |                      | CP      | Wb, Ws          | Compare Wb with Ws (Wb – Ws)                  | 1             | 1              | C,DC,N,OV,Z              |

| 19            | CP0                  | CP0     | f               | Compare f with 0x0000                         | 1             | 1              | C,DC,N,OV,Z              |

| 19            | CFU                  | CP0     | Ws              | Compare Vs with 0x0000                        | 1             | 1              | C,DC,N,OV,Z              |

| 20            | СРВ                  | CPB     | f               | Compare f with WREG, with Borrow              | 1             | 1              | C,DC,N,OV,Z              |

| 20            | CFB                  | CPB     | Wb,#lit5        | Compare Wb with lit5, with Borrow             | 1             | 1              | C,DC,N,OV,Z              |

|               |                      | СРВ     | Wb, Ws          | Compare Wb with Ws, with Borrow (Wb - Ws - C) | 1             | 1              | C,DC,N,OV,Z              |

| 21            | CPSEQ                | CPSEQ   | Wb, Wn          | Compare Wb with Wn, skip if =                 | 1             | 1<br>(2 or 3)  | None                     |

| 22            | CPSGT                | CPSGT   | Wb, Wn          | Compare Wb with Wn, skip if >                 | 1             | 1<br>(2 or 3)  | None                     |

| 23            | CPSLT                | CPSLT   | Wb, Wn          | Compare Wb with Wn, skip if <                 | 1             | 1<br>(2 or 3)  | None                     |

| 24            | CPSNE                | CPSNE   | Wb, Wn          | Compare Wb with Wn, skip if 1/4               | 1             | 1<br>(2 or 3)  | None                     |

| 25            | DAW                  | DAW     | Wn              | Wn = decimal adjust Wn                        | 1             | 1              | С                        |

| 26            | DEC                  | DEC     | f               | f = f - 1                                     | 1             | 1              | C,DC,N,OV,Z              |

|               |                      | DEC     | f,WREG          | WREG = f - 1                                  | 1             | 1              | C,DC,N,OV,Z              |

|               |                      | DEC     | Ws,Wd           | Wd = Ws - 1                                   | 1             | 1              | C,DC,N,OV,Z              |

| 27            | DEC2                 | DEC2    | f               | f = f - 2                                     | 1             | 1              | C,DC,N,OV,Z              |

|               |                      | DEC2    | f,WREG          | WREG = f - 2                                  | 1             | 1              | C,DC,N,OV,Z              |

|               |                      | DEC2    | Ws,Wd           | Wd = Ws - 2                                   | 1             | 1              | C,DC,N,OV,Z              |

| 28            | DISI                 | DISI    | #lit14          | Disable Interrupts for k instruction cycles   | 1             | 1              | None                     |

| 29            | DIV                  | DIV.S   | Wm,Wn           | Signed 16/16-bit Integer Divide               | 1             | 18             | N,Z,C,OV                 |

|               |                      | DIV.SD  | Wm,Wn           | Signed 32/16-bit Integer Divide               | 1             | 18             | N,Z,C,OV                 |

|               |                      | DIV.U   | Wm,Wn           | Unsigned 16/16-bit Integer Divide             | 1             | 18             | N,Z,C,OV                 |

|               |                      | DIV.UD  | Wm,Wn           | Unsigned 32/16-bit Integer Divide             | 1             | 18             | N,Z,C,OV                 |

| 30            | EXCH                 | EXCH    | Wns, Wnd        | Swap Wns with Wnd                             | 1             | 1              | None                     |

| 31            | FBCL                 | FBCL    | Ws, Wnd         | Find Bit Change from Left (MSb) Side          | 1             | 1              | С                        |

| 32            | FF1L                 | FF1L    | Ws,Wnd          | Find First One from Left (MSb) Side           | 1             | 1              | С                        |

| 33            | FF1R                 | FF1R    | Ws,Wnd          | Find First One from Right (LSb) Side          | 1             | 1              | С                        |

| 34            | GOTO                 | GOTO    | Expr            | Go to address                                 | 2             | 2              | None                     |

|               |                      | GOTO    | Wn              | Go to indirect                                | 1             | 2              | None                     |

#### 22.1 DC Characteristics

TABLE 22-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range<br>(in Volts)                   | Temp Range<br>(in °C) | Max MIPS PIC24HJ32GP202/204 and PIC24HJ16GP304 |

|----------------|-------------------------------------------|-----------------------|------------------------------------------------|

| _              | — VBOR-3.6V <sup>(1)</sup> -40°C to +85°C |                       | 40                                             |

| _              | VBOR-3.6V <sup>(1)</sup>                  | -40°C to +125°C       | 40                                             |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 22-11 for the minimum and maximum BOR values.

#### TABLE 22-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                       | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Industrial Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                         | TJ     | -40 | _           | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                          | TA     | -40 | _           | +85  | °C   |

| Extended Temperature Devices                                                                                                                                                                 |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                         | TJ     | -40 | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                          | TA     | -40 | _           | +125 | °C   |

| Power Dissipation: Internal chip power dissipation: $PINT = VDD \ x \ (IDD - \Sigma \ IOH)$ I/O Pin Power Dissipation: $I/O = \Sigma \ (\{VDD - VOH\} \ x \ IOH) + \Sigma \ (VOL \ x \ IOL)$ | Pb     | ,   | PINT + PI/O | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                            | Ромах  | (   | TJ - TA)/θJ | W    |      |

#### **TABLE 22-3: THERMAL PACKAGING CHARACTERISTICS**

| Characteristic                           | Symbol      | Тур | Max | Unit | Notes |

|------------------------------------------|-------------|-----|-----|------|-------|

| Package Thermal Resistance, 44-pin QFN   | $\theta$ JA | 32  | _   | °C/W | 1     |

| Package Thermal Resistance, 44-pin TFQP  | $\theta$ JA | 45  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | $\theta$ JA | 45  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | $\theta$ JA | 50  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SSOP  | $\theta$ JA | 71  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN-S | $\theta$ JA | 35  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

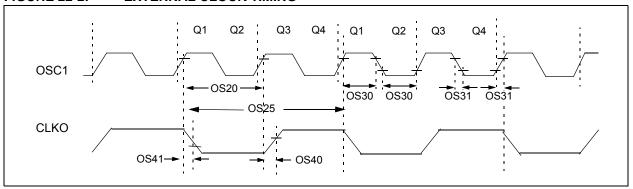

FIGURE 22-2: EXTERNAL CLOCK TIMING

**TABLE 22-16: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA       | AC CHARACTERISTICS |                                                                                                   |              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)   Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                |                   |                                                  |  |

|--------------|--------------------|---------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|--------------------------------------------------|--|

| Param<br>No. | Symb               | Characteristic                                                                                    | Min          | Typ <sup>(1)</sup>                                                                                                                                                                                                                                 | Max            | Units             | Conditions                                       |  |

| OS10         | FIN                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) <sup>(4)</sup> | DC           | _                                                                                                                                                                                                                                                  | 40             | MHz               | EC                                               |  |

|              |                    | Oscillator Crystal Frequency <sup>(5)</sup>                                                       | 3.5<br>10    | _<br>_<br>_                                                                                                                                                                                                                                        | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC                                 |  |

| OS20         | Tosc               | Tosc = 1/Fosc <sup>(4)</sup>                                                                      | 12.5         | _                                                                                                                                                                                                                                                  | DC             | ns                | _                                                |  |

| OS25         | Tcy                | Instruction Cycle Time <sup>(2,4)</sup>                                                           | 25           | _                                                                                                                                                                                                                                                  | DC             | ns                | _                                                |  |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1) <sup>(5)</sup><br>High or Low Time                                       | 0.375 x Tosc | _                                                                                                                                                                                                                                                  | 0.625 x Tosc   | ns                | EC                                               |  |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1) <sup>(5)</sup><br>Rise or Fall Time                                      | _            | _                                                                                                                                                                                                                                                  | 20             | ns                | EC                                               |  |

| OS40         | TckR               | CLKO Rise Time <sup>(3,5)</sup>                                                                   | _            | 5.2                                                                                                                                                                                                                                                | _              | ns                | _                                                |  |

| OS41         | TckF               | CLKO Fall Time <sup>(3,5)</sup>                                                                   | _            | 5.2                                                                                                                                                                                                                                                | _              | ns                | _                                                |  |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(6)</sup>                                            | 14           | 16                                                                                                                                                                                                                                                 | 18             | mA/V              | V <sub>DD</sub> = 3.3V<br>T <sub>A</sub> = +25°C |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 2: Instruction cycle period (Tcx) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits can result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: These parameters are characterized by similarity, but are tested in manufacturing at FIN = 40 MHz only.

- 5: These parameters are characterized by similarity, but are not tested in manufacturing.

- **6:** Data for this parameter is preliminary. This parameter is characterized, but is not tested in manufacturing.

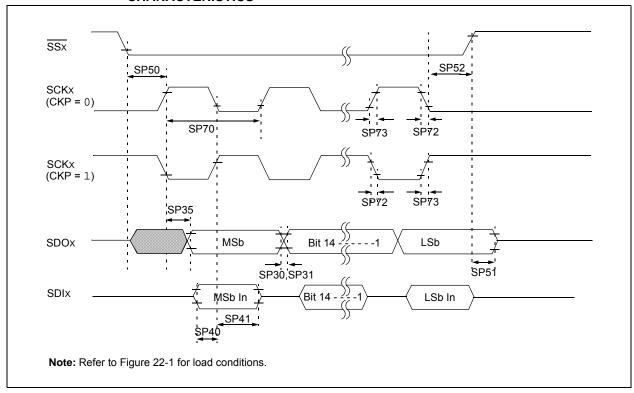

FIGURE 22-15: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

TABLE 23-10: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +150^{\circ}\text{C}$ for High Temperature |     |     |     |       |            |  |

|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.          | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                 | Min | Тур | Max | Units | Conditions |  |

| HSP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                     |     | 10  | 25  | ns    | _          |  |

| HSP40                 | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                    | 28  | _   | _   | ns    | _          |  |

| HSP41                 | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                     | 35  | 1   | 1   | ns    | _          |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

TABLE 23-11: SPIx MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

|              | AC<br>CTERISTICS      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature |     |     |     |       |            |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                 | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                     | _   | 10  | 25  | ns    | _          |

| HSP36        | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to First SCKx Edge                                                                                                                                     | 35  |     | _   | ns    | _          |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                    | 28  | _   | _   | ns    | _          |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                     | 35  | _   | _   | ns    | _          |

Note 1: These parameters are characterized but not tested in manufacturing.

TABLE 23-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| CHARA        | AC<br>CTERISTICS      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature |     |     |     |       |            |  |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                 | Min | Тур | Max | Units | Conditions |  |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                     | _   | _   | 35  | ns    | _          |  |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                    | 25  | _   | _   | ns    | _          |  |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                     | 25  | _   | _   | ns    | _          |  |

| HSP51        | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                                        | 15  | _   | 55  | ns    | See Note 2 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

TABLE 23-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature |     |     |     |       |            |  |  |  |

|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|--|--|

| Param<br>No.          | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                 | Min | Тур | Max | Units | Conditions |  |  |  |

| HSP35                 | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                     | _   | 1   | 35  | ns    | _          |  |  |  |

| HSP40                 | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                    | 25  |     |     | ns    | _          |  |  |  |

| HSP41                 | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                     | 25  | _   | _   | ns    | _          |  |  |  |

| HSP51                 | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                                        | 15  | _   | 55  | ns    | See Note 2 |  |  |  |

| HSP60                 | TssL2doV              | SDOx Data Output Valid after SSx Edge                                                                                                                                         | _   | _   | 55  | ns    | _          |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

**TABLE 23-14: INTERNAL RC ACCURACY**

| AC CHARACTERISTICS |                                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for Extended |     |     |       |                                                              |                |  |  |

|--------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------------------------------------------------|----------------|--|--|

| Param<br>No.       | Characteristic                     | Min                                                                                                                                                                   | Тур | Max | Units | Conditions                                                   |                |  |  |

|                    | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                                                       |     |     |       |                                                              |                |  |  |

| HF21               | LPRC                               | -70                                                                                                                                                                   | _   | +70 | %     | $-40^{\circ}\text{C} \le \text{Ta} \le +150^{\circ}\text{C}$ | VDD = 3.0-3.6V |  |  |

Note 1: Change of LPRC frequency as VDD changes.

<sup>2:</sup> Assumes 50 pF load on all SPIx pins.

<sup>2:</sup> Assumes 50 pF load on all SPIx pins.

<sup>2:</sup> LPRC accuracy impacts the Watchdog Timer Time-out Period (TWDT1). See **Section 19.4 "Watchdog Timer (WDT)"** for more information.

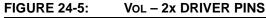

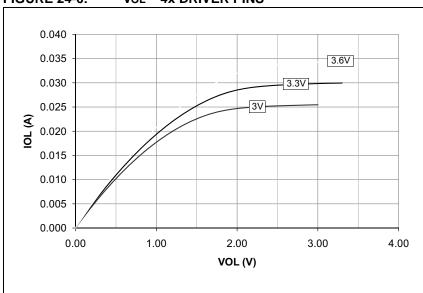

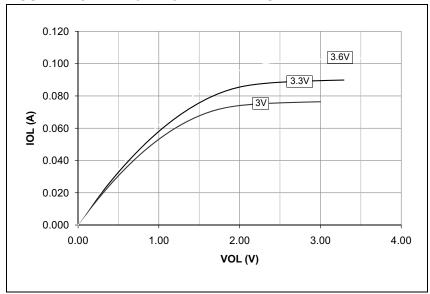

**FIGURE 24-7: Vol - 8x DRIVER PINS**

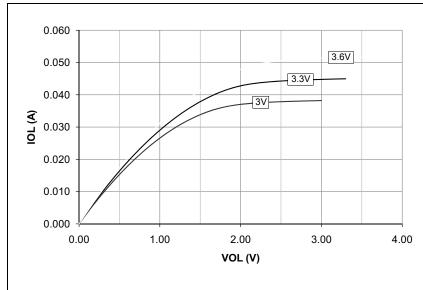

**FIGURE 24-6: VOL - 4x DRIVER PINS**

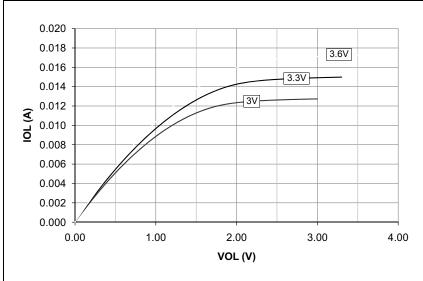

**FIGURE 24-8: VOL - 16x DRIVER PINS**

#### 25.1 Package Marking Information (Continued)

28-Lead QFN-S

Example

44-Lead QFN

Example

44-Lead TQFP

Example

Legend: XX...X Customer-specific information Year code (last digit of calendar year)

ΥY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01')

Alphanumeric traceability code NNN

Pb-free JEDEC designator for Matte Tin (Sn) (e3)

This package is Pb-free. The Pb-free JEDEC designator ((e3))

can be found on the outer packaging for this package.

If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information.

### **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou

Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka

Tel: 81-66-152-7160 Fax: 81-66-152-9310

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069

**Singapore**

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-330-9305

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/11