# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp202-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

This document contains device-specific information for the following devices:

- PIC24HJ32GP202

- PIC24HJ32GP204

- PIC24HJ16GP304

Figure 1-1 shows a general block diagram of the core and peripheral modules in the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 2. CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP202/204 and PIC24HJ16GP304 CPU modules have a 16-bit (data) modified Harvard architecture with an enhanced instruction set and addressing modes. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free, single-cycle program loop constructs are supported using the REPEAT instruction, which is interruptible at any time.

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the PIC24HJ32GP202/204 and PIC24HJ16GP304 is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be linearly addressed as 32K words or 64 Kbytes using an Address Generation Unit (AGU). The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page register (PSVPAG). The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but this may be used as general purpose RAM.

## 3.2 Special MCU Features

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices feature a 17-bit by 17-bit, single-cycle multiplier. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication makes mixed-sign multiplication possible.

The PIC24HJ32GP202/204 and PIC24HJ16GP304 devices support 16/16 and 32/16 integer divide operations. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A multi-bit data shifter is used to perform up to a 16-bit, left or right shift in a single cycle.

## 3.4 CPU Control Registers

## REGISTER 3-1: SR: CPU STATUS REGISTER

|                      | 5-1. SIX. C             | 100141001                           |                 |                   |                   |                   |                |

|----------------------|-------------------------|-------------------------------------|-----------------|-------------------|-------------------|-------------------|----------------|

| U-0                  | U-0                     | U-0                                 | U-0             | U-0               | U-0               | U-0               | R/W-0          |

| _                    | —                       | —                                   | _               | —                 | —                 | —                 | DC             |

| bit 15               |                         |                                     |                 |                   |                   |                   | bit 8          |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(2)</sup>    | R/W-0 <sup>(2)</sup>                | R-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0          |

|                      | IPL<2:0> <sup>(2)</sup> |                                     | RA              | N                 | OV                | Z                 | С              |

| bit 7                |                         |                                     |                 |                   |                   | 1                 | bit (          |

|                      |                         |                                     |                 |                   |                   |                   |                |

| Legend:              |                         |                                     |                 |                   |                   |                   |                |

| C = Clear on         | ly bit                  | R = Readable                        | e bit           | U = Unimpler      | nented bit, read  | as '0'            |                |

| S = Set only         | bit                     | W = Writable                        | bit             | -n = Value at     | POR               |                   |                |

| '1' = Bit is se      | t                       | '0' = Bit is clea                   | ared            | x = Bit is unk    | nown              |                   |                |

|                      |                         |                                     |                 |                   |                   |                   |                |

| bit 15-9             | Unimplemer              | nted: Read as '                     | 0'              |                   |                   |                   |                |

| bit 8                | DC: MCU AL              | U Half Carry/Bo                     | orrow bit       |                   |                   |                   |                |

|                      | -                       | out from the 4th sult occurred      | low-order bit ( | for byte sized o  | lata) or 8th low- | order bit (for wo | ord sized data |

|                      | •                       | -out from the 4<br>the result occur |                 | oit (for byte siz | ed data) or 8th   | low-order bit (   | for word size  |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup> |

|---------|-------------------------------------------------------------------|

|---------|-------------------------------------------------------------------|

|         | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = An operation which affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                               |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                                                          |

| Note 1: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when $IPL<3> = 1$ .                                                                                                                                                                                                                |

2: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### TABLE 4-5: TIMER REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8         | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|-------------|---------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1     | 0100        |        |        |        |        |        |        |             | Timer1        | Register      |              |       |        |       |       |       |       | 0000          |

| PR1      | 0102        |        |        |        |        |        |        |             | Period R      | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON    | 0104        | TON    | _      | TSIDL  |        | _      | _      | _           | _             | _             | TGATE        | TCKP  | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2     | 0106        |        |        |        |        |        |        |             | Timer2        | Register      |              |       |        |       |       |       |       | 0000          |

| TMR3HLD  | 0108        |        |        |        |        |        | Time   | er3 Holding | Register (for | r 32-bit time | r operations | only) |        |       |       |       |       | xxxx          |

| TMR3     | 010A        |        |        |        |        |        |        |             | Timer3        | Register      |              |       |        |       |       |       |       | 0000          |

| PR2      | 010C        |        |        |        |        |        |        |             | Period R      | Register 2    |              |       |        |       |       |       |       | FFFF          |

| PR3      | 010E        |        |        |        |        |        |        |             | Period R      | Register 3    |              |       |        |       |       |       |       | FFFF          |

| T2CON    | 0110        | TON    | —      | TSIDL  | _      | —      | _      | —           | —             | _             | TGATE        | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON    | 0112        | TON    | —      | TSIDL  | -      |        | _      | _           | —             | —             | TGATE        | TCKP  | S<1:0> | —     | _     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-6: INPUT CAPTURE REGISTER MAP

|          | ••••••••••••••••••••••••••••••••••••••• |        |        |        |        |        |        |       |              |              |       |       |       |       |       |          |       |               |

|----------|-----------------------------------------|--------|--------|--------|--------|--------|--------|-------|--------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr                             | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF   | 0140                                    |        |        |        |        |        |        |       | Input 1 Cap  | ture Registe | r     |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142                                    | _      | _      | ICSIDL | _      | _      | _      | _     | _            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144                                    |        |        |        |        |        |        |       | Input 2 Capt | ture Registe | r     |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146                                    | _      | _      | ICSIDL | _      | _      | _      | _     | _            | ICTMR        | ICI<  | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158                                    |        |        |        |        |        |        |       | Input 7 Cap  | ture Registe | r     |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A                                    | _      | _      | ICSIDL | _      | _      | _      | _     | _            | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C                                    |        |        |        |        |        |        |       | Input 8Capt  | ure Register |       |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E                                    | _      | _      | ICSIDL |        | _      |        | _     | _            | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

|          |                                         |        |        |        |        |        |        |       |              |              |       |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-7: OUTPUT COMPARE REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                         | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------------------------------|--------|--------|--------|--------|--------|------------|--------------|----------|-------|-------|-------|-------|-------|-------|---------------|

| OC1RS    | 0180        |        |                                |        |        |        |        | Output | Compare 1  | Secondary I  | Register |       |       |       |       |       |       | xxxx          |

| OC1R     | 0182        |        |                                |        |        |        |        | 0      | utput Comp | are 1 Regist | er       |       |       |       |       |       |       | xxxx          |

| OC1CON   | 0184        | _      | OCSIDL OCFLT OCTSEL OCM<2:0>   |        |        |        |        |        |            |              | 0000     |       |       |       |       |       |       |               |

| OC2RS    | 0186        |        |                                |        |        |        |        | Output | Compare 2  | Secondary F  | Register |       |       |       |       |       |       | xxxx          |

| OC2R     | 0188        |        | Output Compare 2 Register      |        |        |        |        |        |            |              | xxxx     |       |       |       |       |       |       |               |

| OC2CON   | 018A        | _      | OCSIDL OCFLT OCTSEL OCM<2:0> 0 |        |        |        |        |        |            | 0000         |          |       |       |       |       |       |       |               |

| Lanandi  |             |        |                                |        |        |        |        |        |            |              |          |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0             | U-0            | U-0                 | U-0              | U-0              | U-0              | U-0             | U-0   |

|-----------------|----------------|---------------------|------------------|------------------|------------------|-----------------|-------|

| —               | —              | —                   |                  | —                |                  | —               | —     |

| bit 15          |                |                     |                  |                  |                  |                 | bit 8 |

|                 |                |                     |                  |                  |                  |                 |       |

| U-0             | R/W-1          | R/W-0               | R/W-0            | U-0              | U-0              | U-0             | U-0   |

| —               |                | INT2IP<2:0>         |                  | —                | —                | —               | —     |

| bit 7           |                |                     |                  |                  |                  |                 | bit 0 |

|                 |                |                     |                  |                  |                  |                 |       |

| Legend:         |                |                     |                  |                  |                  |                 |       |

| R = Readable    | bit            | W = Writable        | bit              | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at P | OR             | '1' = Bit is set    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |                |                     |                  |                  |                  |                 |       |

| bit 15-7        | Unimplemen     | ted: Read as 'd     | )'               |                  |                  |                 |       |

| bit 6-4         | INT2IP<2:0>:   | External Interr     | upt 2 Priority   | bits             |                  |                 |       |

|                 | 111 = Interrup | ot is priority 7 (I | nighest priority | y interrupt)     |                  |                 |       |

|                 | •              |                     |                  |                  |                  |                 |       |

### REGISTER 7-17: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

bit 3-0 Unimplemented: Read as '0'

001 = Interrupt is priority 1 000 = Interrupt source is disabled

## **REGISTER 8-4:** OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(2)</sup>

|                 |             |                                  | OILEATOR       |                  |                      |                 |              |

|-----------------|-------------|----------------------------------|----------------|------------------|----------------------|-----------------|--------------|

| U-0             | U-0         | U-0                              | U-0            | U-0              | U-0                  | U-0             | U-0          |

|                 | —           | —                                |                | —                | —                    | —               | —            |

| bit 15          |             |                                  |                |                  |                      |                 | bit 8        |

|                 |             | <b>D</b> 444.0                   | <b>DMU</b> O   | DANO             | DAALO                | <b>D</b> 444.0  | <b>DAA/A</b> |

| U-0             | U-0         | R/W-0                            | R/W-0          | R/W-0            | R/W-0                | R/W-0           | R/W-0        |

|                 | —           |                                  |                | IUN              | <5:0> <sup>(1)</sup> |                 |              |

| bit 7           |             |                                  |                |                  |                      |                 | bit 0        |

|                 |             |                                  |                |                  |                      |                 |              |

| Legend:         |             |                                  |                |                  |                      |                 |              |

| R = Readable    | bit         | W = Writable                     | bit            | U = Unimpler     | mented bit, read     | l as '0'        |              |

| -n = Value at I | POR         | '1' = Bit is set                 |                | '0' = Bit is cle | ared                 | x = Bit is unkr | nown         |

| bit 15-6        | Unimplemen  | ted: Read as '                   | 0'             |                  |                      |                 |              |

| bit 5-0         | -           | RC Oscillator 1                  |                |                  |                      |                 |              |

| bit 0 0         |             | nter frequency                   | •              | 845 MHz)         |                      |                 |              |

|                 | •           |                                  | 0.07070 (7.0   |                  |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 |             | nter frequency                   |                |                  |                      |                 |              |

|                 |             | nter frequency<br>nter frequency |                |                  |                      |                 |              |

|                 |             | nter frequency                   |                | •                |                      |                 |              |

|                 | •           |                                  | . 11.2070 (0.2 | 20 10112)        |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 | •           |                                  |                |                  |                      |                 |              |

|                 |             | nter frequency                   |                |                  |                      |                 |              |

|                 | 000000 = Ce | nter frequency                   | (7.37 MHZ nd   | ominal)          |                      |                 |              |

- **Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

- 2: This register is reset only on a Power-on Reset (POR).

#### REGISTER 10-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0                                | U-0 | U-0 | U-0   | U-0              | U-0              | U-0            | U-0   |

|------------------------------------|-----|-----|-------|------------------|------------------|----------------|-------|

| —                                  | —   | —   | —     | —                | —                | —              | —     |

| bit 15                             |     |     |       |                  | •                |                | bit 8 |

|                                    |     |     |       |                  |                  |                |       |

| U-0                                | U-0 | U-0 | R/W-1 | R/W-1            | R/W-1            | R/W-1          | R/W-1 |

| —                                  | —   | —   |       |                  | OCFAR<4:0>       |                |       |

| bit 7                              |     |     |       |                  |                  |                | bit 0 |

|                                    |     |     |       |                  |                  |                |       |

| Legend:                            |     |     |       |                  |                  |                |       |

| R = Readable bit W = Writable bit  |     |     | bit   | U = Unimple      | mented bit, read | 1 as '0'       |       |

| -n = Value at POR '1' = Bit is set |     |     |       | '0' = Bit is cle | eared            | x = Bit is unk | nown  |

#### bit 15-5 Unimplemented: Read as '0'

bit 4-0

OCFAR<4:0>: Assign Output Capture A (OCFA) to the corresponding RPn pin

11111 = Input tied to Vss 11001 = Input tied to RP25

- •

- •

•

00001 = Input tied to RP1 00000 = Input tied to RP0

#### REGISTER 10-21: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0 U-0 U-0 R/W-0 R/W-0<br>— — — — — — — — — — — — — — — — — — — | -0 R/W-0 R/W-0 R/W-0<br>RP23R<4:0><br>bit 8 |

|------------------------------------------------------------------|---------------------------------------------|

|                                                                  |                                             |

| bit 15                                                           | bit 8                                       |

|                                                                  |                                             |

|                                                                  |                                             |

| U-0 U-0 U-0 R/W-0 R/W-0                                          | -0 R/W-0 R/W-0 R/W-0                        |

|                                                                  | RP22R<4:0>                                  |

| bit 7                                                            | bit 0                                       |

|                                                                  |                                             |

| Legend:                                                          |                                             |

| Legena.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-22: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| U-0                                | U-0 | U-0 | R/W-0      | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |  |

|------------------------------------|-----|-----|------------|-----------------------------------------|-----------|-------|-------|--|

| —                                  | _   | _   |            |                                         | RP25R<4:0 | >     |       |  |

| bit 15                             |     |     |            |                                         |           |       | bit 8 |  |

|                                    |     |     |            |                                         |           |       |       |  |

| U-0                                | U-0 | U-0 | R/W-0      | R/W-0                                   | R/W-0     | R/W-0 | R/W-0 |  |

| —                                  | _   | —   | RP24R<4:0> |                                         |           |       |       |  |

| bit 7                              |     |     |            |                                         |           |       | bit 0 |  |

|                                    |     |     |            |                                         |           |       |       |  |

| Legend:                            |     |     |            |                                         |           |       |       |  |

| R = Readable bit W = Writable b    |     |     | bit        | U = Unimplemented bit, read as '0'      |           |       |       |  |

| -n = Value at POR '1' = Bit is set |     |     |            | '0' = Bit is cleared x = Bit is unknown |           |       |       |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP25R<4:0>:** Peripheral Output Function is Assigned to RP25 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP24R<4:0>:** Peripheral Output Function is Assigned to RP24 Output Pin (see Table 10-2 for peripheral function numbers)

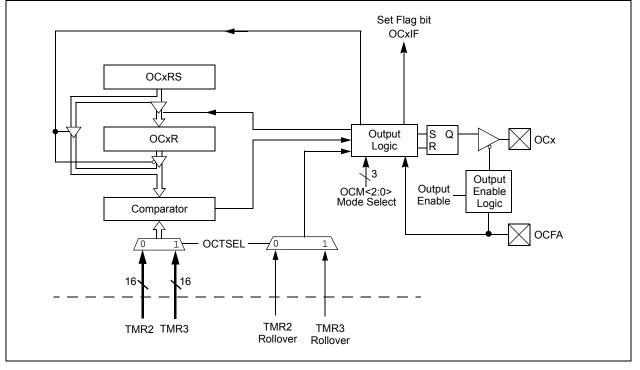

## 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 13. Output Compare" (DS70209) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

#### FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

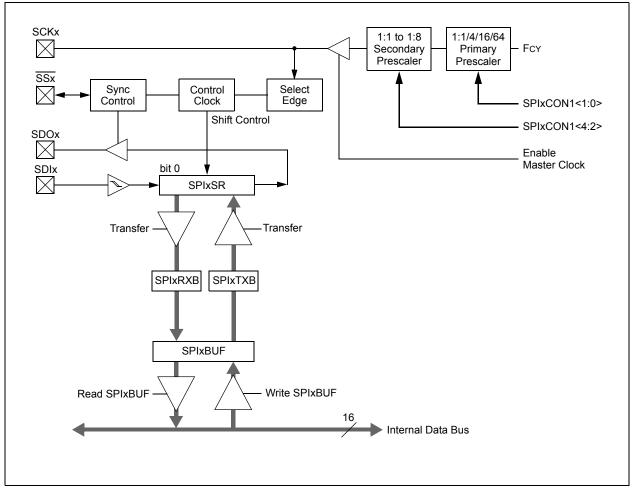

## 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 18. Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters (ADCs), and so on. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of these four pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

#### FIGURE 15-1: SPI MODULE BLOCK DIAGRAM

| R/W-0               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                         | U-0                                                                                                     | R/W-0 HC          | R/W-0                                                            | R-0                | R-1             |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------|--------------------|-----------------|--|

| UTXISEL1            | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UTXISEL0                                                                                                                                                      |                                                                                                         | UTXBRK            | UTXEN <sup>(1)</sup>                                             | UTXBF              | TRMT            |  |

| bit 15              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    | bit 8           |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    |                 |  |

| R/W-0               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                         | R-1                                                                                                     | R-0               | R-0                                                              | R/C-0              | R-0             |  |

| URXIS               | EL<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDEN                                                                                                                                                         | RIDLE                                                                                                   | PERR              | FERR                                                             | OERR               | URXDA           |  |

| bit 7               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    | bit 0           |  |

| <b></b>             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    |                 |  |

| Legend:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HC = Hardwa                                                                                                                                                   |                                                                                                         |                   |                                                                  | r only bit         |                 |  |

| R = Readable        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                  | bit                                                                                                     | -                 | mented bit, read                                                 |                    |                 |  |

| -n = Value at I     | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                              |                                                                                                         | '0' = Bit is cle  | ared                                                             | x = Bit is unkr    | IOWN            |  |

| bit 15,13<br>bit 14 | 11 = Reserve<br>10 = Interrupt<br>transmit<br>01 = Interrupt<br>operatio<br>00 = Interrupt<br>at least of<br><b>UTXINV:</b> Tran<br><u>If IREN = 0:</u><br>1 = UxTX Idle<br><u>If IREN = 1:</u>                                                                                                                                                                                                                                                                                                                                                                        | d; do not use<br>when a charac<br>buffer become<br>when the last<br>ns are complet<br>when a charac<br>one character c<br>nsmit Polarity Ir<br>e state is '0' | cter is transfe<br>s empty<br>character is s<br>ed<br>cter is transfe<br>pen in the tra<br>oversion bit | hifted out of the | bits<br>nsmit Shift Regi<br>e Transmit Shift<br>nsmit Shift Regi | Register; all tra  | ansmit          |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | coded UxTX Id                                                                                                                                                 |                                                                                                         |                   |                                                                  |                    |                 |  |

| bit 12              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ted: Read as '                                                                                                                                                |                                                                                                         |                   |                                                                  |                    |                 |  |

| bit 11              | 1 = Send Syr<br>cleared b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ansmit Break bi<br>nc Break on ne:<br>ny hardware up<br>ak transmission                                                                                       | kt transmissio                                                                                          | า                 | llowed by twelve                                                 | e '0' bits, follow | ed by Stop bit; |  |

| bit 10              | <ul> <li>UTXEN: Transmit Enable bit<sup>(1)</sup></li> <li>1 = Transmit enabled, UxTX pin controlled by UARTx</li> <li>0 = Transmit disabled, any pending transmission is aborted and buffer is reset. UxTX pin controlled by port</li> </ul>                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    |                 |  |

| bit 9               | <b>UTXBF:</b> Transmit Buffer Full Status bit (read-only)<br>1 = Transmit buffer is full<br>0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    |                 |  |

| bit 8               | <ul> <li>TRMT: Transmit Shift Register Empty bit (read-only)</li> <li>1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed</li> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> </ul>                                                                                                                                                                                                                                                                                     |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    |                 |  |

| bit 7-6             | <ul> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> <li>URXISEL&lt;1:0&gt;: Receive Interrupt Mode Selection bits</li> <li>11 = Interrupt is set on UxRSR transfer making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on UxRSR transfer making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters</li> </ul> |                                                                                                                                                               |                                                                                                         |                   |                                                                  |                    |                 |  |

#### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

#### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                     |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>    |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                             |

|       | 1 = Receive buffer has overflowed                                                                                                                                           |

|       | 0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the UxRSR to the empty state |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

|       |                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                             |

|-----------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICS<1:0>  | FICD     | Immediate      | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use |

### TABLE 19-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

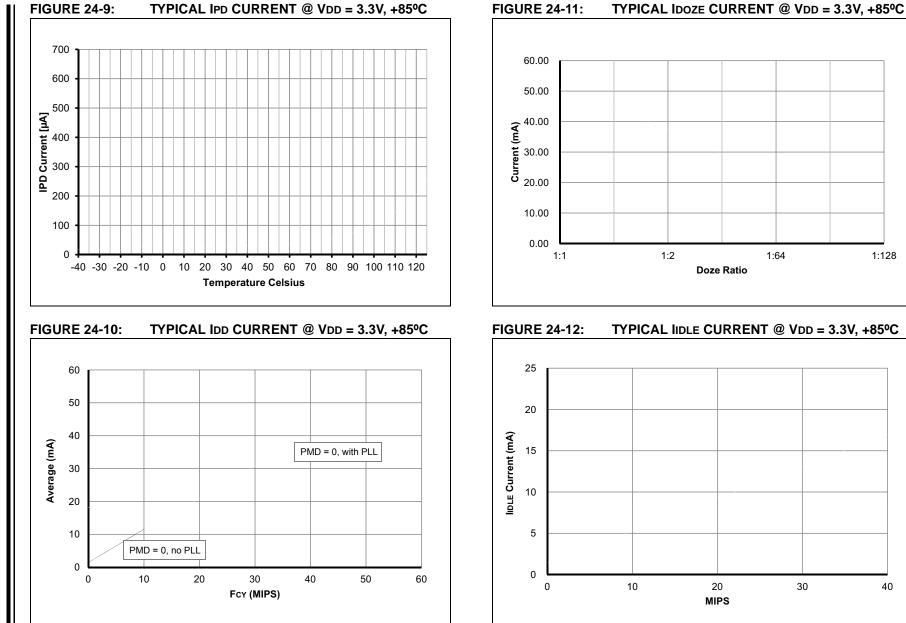

| <b>TABLE 22-8:</b> | DC CHARACTERISTICS: DOZE CURRENT (IDOZE) |

|--------------------|------------------------------------------|

|                    |                                          |

| DC CHARACTERI                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |               |       |        |      |          |

|---------------------------------------------------------|-------------------------------------------------------|----|---------------|-------|--------|------|----------|

| Parameter No. <sup>(3)</sup> Typical <sup>(2)</sup> Max |                                                       |    | Doze<br>Ratio | Units |        | Co   | nditions |

| Doze Current (IDO                                       | ze) <sup>(1)</sup>                                    |    |               |       |        |      |          |

| DC73a                                                   | 41                                                    | 51 | 1:2           | mA    |        |      |          |

| DC73f                                                   | 20                                                    | 28 | 1:64          | mA    | -40°C  | 3.3V | 40 MIPS  |

| DC73g                                                   | 19                                                    | 24 | 1:128         | mA    |        |      |          |

| DC70a                                                   | 40                                                    | 46 | 1:2           | mA    |        | 3.3V | 40 MIPS  |

| DC70f                                                   | 18                                                    | 20 | 1:64          | mA    | +25°C  |      |          |

| DC70g                                                   | 18                                                    | 20 | 1:128         | mA    |        |      |          |

| DC71a                                                   | 40                                                    | 46 | 1:2           | mA    |        |      |          |

| DC71f                                                   | 18                                                    | 25 | 1:64          | mA    | +85°C  | 3.3V | 40 MIPS  |

| DC71g                                                   | 18                                                    | 20 | 1:128         | mA    |        |      |          |

| DC72a                                                   | 39                                                    | 55 | 1:2           | mA    |        |      | 40 MIPS  |

| DC72f                                                   | 18                                                    | 30 | 1:64          | mA    | +125°C | 3.3V |          |

| DC72g                                                   | 18                                                    | 25 | 1:128         | mA    |        |      |          |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail with overshoot/undershoot < 250 mV</li>

- · CLKO is configured as an I/O input pin in the Configuration word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while(1) statement

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

| DC CHARACTERISTICS |        |                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |   |                     |    |                                                                                                                                    |

|--------------------|--------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|----|------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                     | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                                                                                                                                       |   |                     |    |                                                                                                                                    |

| DI60a              | licl   | Input Low Injection Current                                        | 0                                                                                                                                                                                                                                                                                 | _ | _5 <sup>(5,8)</sup> | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>SOSCI, SOSCO, and RB14                                                     |

| DI60b              | Іісн   | Input High Injection Current                                       | 0                                                                                                                                                                                                                                                                                 | _ | +5(6,7,8)           | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>SOSCI, SOSCO, RB14,<br>and digital 5V-tolerant<br>designated pins          |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control pins) | -20 <sup>(9)</sup>                                                                                                                                                                                                                                                                |   | +20 <sup>(9)</sup>  | mA | Absolute instantaneous<br>sum of all $\pm$ input injection<br>currents from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |

#### TABLE 22-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for a list of digital-only and analog pins.

- 5: VIL source < (Vss 0.3). Characterized but not tested.

**6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5V or devices with USB, "D+" and "D-" VIH source > (VUSB + 0.3). Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

#### TABLE 23-15: ADC MODULE SPECIFICATIONS

| AC<br>CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le T_A \le +150^{\circ}C$ for High Temperature |     |          |           |          |                                                                |  |

|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------|----------|----------------------------------------------------------------|--|

| Param<br>No.          | Symbol | Characteristic                                                                                                                                           | Min | Тур      | Max       | Units    | Conditions                                                     |  |

| Reference Inputs      |        |                                                                                                                                                          |     |          |           |          |                                                                |  |

| HAD08                 | IREF   | Current Drain                                                                                                                                            | _   | 250<br>— | 600<br>50 | μΑ<br>μΑ | ADC operating, See <b>Note 1</b><br>ADC off, See <b>Note 1</b> |  |

Note 1: These parameters are not characterized or tested in manufacturing.

2: These parameters are characterized, but are not tested in manufacturing.

## TABLE 23-16: ADC MODULE SPECIFICATIONS (12-BIT MODE)<sup>(3)</sup>

|              | AC<br>TERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |           |           |            |                  |                                                  |  |

|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------------|------------------|--------------------------------------------------|--|

| Param<br>No. | Symbol          | Characteristic                                                                                                                                          | Min       | Тур       | Max        | Units            | Conditions                                       |  |

|              | ADO             | C Accuracy (12-bit Mode                                                                                                                                 | ) – Meas  | urement   | ts with Ex | ternal V         | /REF+/VREF- <sup>(1)</sup>                       |  |

| HAD20a       | Nr              | Resolution <sup>(3)</sup>                                                                                                                               | 1         | 2 data bi | ts         | bits             | —                                                |  |

| HAD21a       | INL             | Integral Nonlinearity                                                                                                                                   | -2        | _         | +2         | LSb              | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |

| HAD22a       | DNL             | Differential Nonlinearity                                                                                                                               | > -1      | —         | < 1        | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD23a       | Gerr            | Gain Error                                                                                                                                              | -2        | —         | 10         | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD24a       | EOFF            | Offset Error                                                                                                                                            | -3        | —         | 5          | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

|              | AD              | C Accuracy (12-bit Mode                                                                                                                                 | e) – Meas | uremen    | ts with In | ternal V         | /REF+/VREF- <sup>(1)</sup>                       |  |