# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp202-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

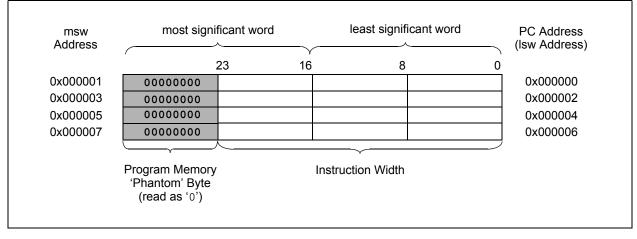

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (See Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

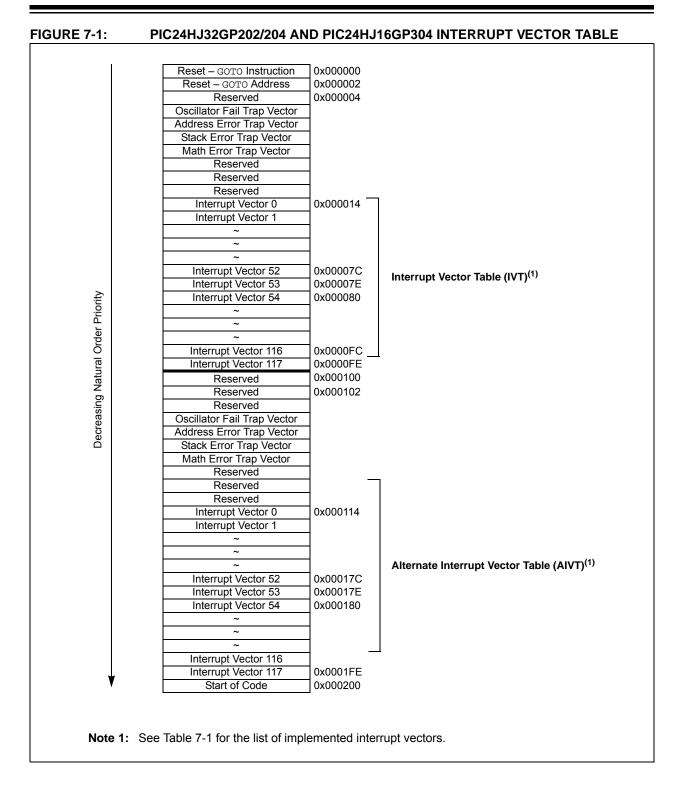

# 4.1.2 INTERRUPT AND TRAP VECTORS

All devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

The devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). Section 7.1 "Interrupt Vector Table" provides a more detailed discussion of the interrupt vector tables.

# FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

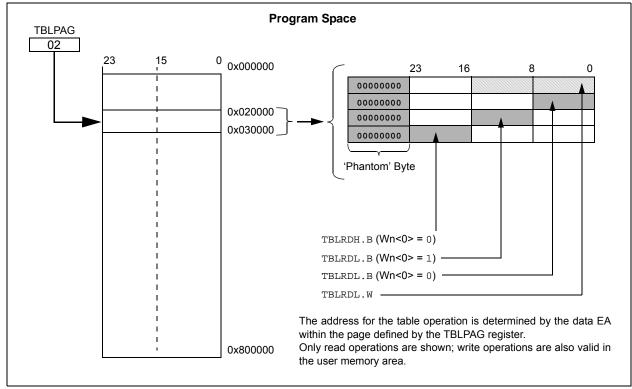

The TBLRDL and TBLWTL instructions offer a direct method to read or write the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only methods to read or write the upper 8 bits of a program space word as data.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16 bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. Note that the data will always be '0' when the upper 'Phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| U-0              | R/W-1                                                           | R/W-0                                                                                 | R/W-0                                            | U-0               | R/W-1           | R/W-0           | R/W-0 |

|------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|-----------------|-----------------|-------|

| _                |                                                                 | T2IP<2:0>                                                                             |                                                  |                   |                 | OC2IP<2:0>      |       |

| bit 15           |                                                                 |                                                                                       |                                                  |                   |                 |                 | bit   |

|                  |                                                                 |                                                                                       |                                                  |                   |                 |                 |       |

| U-0              | R/W-1                                                           | R/W-0                                                                                 | R/W-0                                            | U-0               | U-0             | U-0             | U-0   |

|                  |                                                                 | IC2IP<2:0>                                                                            |                                                  | —                 | _               | —               |       |

| bit 7            |                                                                 |                                                                                       |                                                  |                   |                 |                 | bit   |

| Legend:          |                                                                 |                                                                                       |                                                  |                   |                 |                 |       |

| R = Readab       | le bit                                                          | W = Writable                                                                          | bit                                              | U = Unimplei      | mented bit, rea | id as '0'       |       |

| -n = Value a     | t POR                                                           | '1' = Bit is set                                                                      |                                                  | '0' = Bit is cle  | ared            | x = Bit is unkn | own   |

|                  |                                                                 |                                                                                       |                                                  |                   |                 |                 |       |

| bit 15           | Unimplem                                                        | ented: Read as 'o                                                                     | )'                                               |                   |                 |                 |       |

| bit 14-12        | T2IP<2:0>:                                                      | Timer2 Interrupt                                                                      | Priority bits                                    |                   |                 |                 |       |

|                  | 111 = Inter                                                     | rupt is priority 7 (I                                                                 | nighest prior                                    | ity interrupt)    |                 |                 |       |

|                  | •                                                               |                                                                                       |                                                  |                   |                 |                 |       |

|                  | •                                                               |                                                                                       |                                                  |                   |                 |                 |       |

|                  | 001 = Inter                                                     | rupt is priority 1                                                                    |                                                  |                   |                 |                 |       |

|                  |                                                                 | rupt source is dis                                                                    | abled                                            |                   |                 |                 |       |

| bit 11           | Unimplem                                                        | ented: Read as 'o                                                                     | )'                                               |                   |                 |                 |       |

| bit 10-8         | OC2IP<2:0                                                       | >: Output Compa                                                                       | re Channel                                       | 2 Interrupt Prior | ity bits        |                 |       |

|                  | 111 = Inter                                                     | rupt is priority 7 (I                                                                 | nighest prior                                    | ity interrupt)    | -               |                 |       |

|                  | •                                                               |                                                                                       |                                                  |                   |                 |                 |       |

|                  | •                                                               |                                                                                       |                                                  |                   |                 |                 |       |

|                  | •                                                               |                                                                                       |                                                  |                   |                 |                 |       |

|                  | 001 = Inter                                                     | rupt is priority 1                                                                    |                                                  |                   |                 |                 |       |

|                  |                                                                 | rupt is priority 1<br>rupt source is dis                                              | abled                                            |                   |                 |                 |       |

| bit 7            | 000 <b>= Inte</b> r                                             |                                                                                       |                                                  |                   |                 |                 |       |

|                  | 000 = Inter<br>Unimpleme                                        | rupt source is dis                                                                    | )'                                               | errupt Priority b | its             |                 |       |

|                  | 000 = Inter<br>Unimplem<br>IC2IP<2:0>                           | rupt source is dis<br>ented: Read as 'o                                               | )'<br>Channel 2 Int                              |                   | its             |                 |       |

|                  | 000 = Inter<br>Unimplem<br>IC2IP<2:0>                           | rupt source is dis<br>ented: Read as '(<br>: Input Capture C                          | )'<br>Channel 2 Int                              |                   | its             |                 |       |

|                  | 000 = Inter<br>Unimplem<br>IC2IP<2:0>                           | rupt source is dis<br>ented: Read as '(<br>: Input Capture C                          | )'<br>Channel 2 Int                              |                   | its             |                 |       |

|                  | 000 = Inter<br>Unimpleme<br>IC2IP<2:0><br>111 = Inter<br>•<br>• | rupt source is dis<br>ented: Read as '(<br>: Input Capture C<br>rupt is priority 7 (I | )'<br>Channel 2 Int                              |                   | its             |                 |       |

| bit 7<br>bit 6-4 | 000 = Inter<br>Unimpleme<br>IC2IP<2:0><br>111 = Inter           | rupt source is dis<br>ented: Read as '(<br>: Input Capture C                          | <sub>o</sub> '<br>Channel 2 Int<br>nighest prior |                   | its             |                 |       |

# REGISTER 7-12: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

# 10.7 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 22-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and VSS. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 22.0 "Electrical Characteristics"** for additional information.

# 10.8 I/O Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

# 10.8.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530271

| U-0          | U-0       | U-0                              | R/W-1           | R/W-1                                   | R/W-1                                   | R/W-1    | R/W-1   |  |

|--------------|-----------|----------------------------------|-----------------|-----------------------------------------|-----------------------------------------|----------|---------|--|

| 0-0          | 0-0       |                                  | 10/00-1         | 10/00-1                                 | INT1R<4:0>                              |          | 10/00-1 |  |

|              | _         |                                  |                 |                                         | 111111111111111111111111111111111111111 |          | L : L : |  |

| bit 15       |           |                                  |                 |                                         |                                         |          | bit 8   |  |

|              |           |                                  |                 |                                         |                                         |          |         |  |

| U-0          | U-0       | U-0                              | U-0             | U-0                                     | U-0                                     | U-0      | U-0     |  |

| —            | _         | —                                | —               | _                                       | —                                       | —        | —       |  |

| bit 7        |           |                                  |                 |                                         |                                         |          | bit C   |  |

|              |           |                                  |                 |                                         |                                         |          |         |  |

| Legend:      |           |                                  |                 |                                         |                                         |          |         |  |

| R = Readab   | le bit    | W = Writable                     | bit             | U = Unimple                             | mented bit, read                        | d as '0' |         |  |

| -n = Value a | t POR     | '1' = Bit is set                 | et '0' = Bit is |                                         | cleared x = Bit is                      |          | unknown |  |

|              |           |                                  |                 |                                         |                                         |          |         |  |

| bit 15-13    | Unimpleme | nted: Read as '                  | 0'              |                                         |                                         |          |         |  |

| bit 12-8     | -         | : Assign Externa                 |                 | (INTR1) to the                          | corresponding                           | RPn pin  |         |  |

|              |           | ut tied to Vss                   |                 | , , , , , , , , , , , , , , , , , , , , | 5                                       | r        |         |  |

|              |           | ut tied to RP25                  |                 |                                         |                                         |          |         |  |

|              | •         |                                  |                 |                                         |                                         |          |         |  |

|              | •         |                                  |                 |                                         |                                         |          |         |  |

|              | •         |                                  |                 |                                         |                                         |          |         |  |

|              |           | ut tied to RP1<br>ut tied to RP0 |                 |                                         |                                         |          |         |  |

# REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| bit 7-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

# REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                                                    |  |  |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|--|--|

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

| bit 8                                                  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

| R/W-1                                                  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

| bit 0                                                  |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

| U = Unimplemented bit, read as '0'                     |  |  |  |  |  |  |  |

| x = Bit is unknown                                     |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

| 00001 = Input tied to RP1<br>00000 = Input tied to RP0 |  |  |  |  |  |  |  |

|                                                        |  |  |  |  |  |  |  |

| U-0                   | U-0                               | U-0                              | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|-----------------------|-----------------------------------|----------------------------------|---------------|------------------|-----------------|-----------------|-------|

| _                     |                                   |                                  |               |                  | IC8R<4:0>       |                 |       |

| bit 15                |                                   |                                  |               |                  |                 |                 | bit 8 |

| U-0                   | U-0                               | U-0                              | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _                     | _                                 | _                                |               |                  | IC7R<4:0>       |                 |       |

| bit 7                 |                                   |                                  |               |                  |                 |                 | bit ( |

| <u> </u>              |                                   |                                  |               |                  |                 |                 |       |

| Legend:<br>R = Readab | le bit                            | W = Writable b                   | bit           | U = Unimpler     | nented bit, rea | ıd as '0'       |       |

| -n = Value a          | t POR                             | '1' = Bit is set                 |               | '0' = Bit is cle |                 | x = Bit is unkr | nown  |

|                       | 11111 = Inpu<br>11001 = Inpu<br>• | t tied to RP25                   |               |                  |                 |                 |       |

|                       | 00001 = Inpu<br>00000 = Inpu      |                                  |               |                  |                 |                 |       |

| bit 7-5               | Unimplemen                        | ted: Read as '0                  | ,             |                  |                 |                 |       |

| bit 4-0               | IC7R<4:0>: A<br>11111 = Inpu      | ssign Input Cap<br>t tied to Vss | oture 7 (IC7) | to the correspo  | onding RPn pir  | 1               |       |

|                       | 11001 = Inpu<br>•                 | t tied to RP25                   |               |                  |                 |                 |       |

# REGISTER 10-5: RPIR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

### REGISTER 10-17: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| _      | _   | _   |       |       | RP15R<4:0> |       |       |

| bit 15 | ·   |     | bit 8 |       |            |       |       |

|        |     |     |       |       |            |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

| —      | _   | _   |       |       | RP14R<4:0> |       |       |

| bit 7  |     |     | •     |       |            |       | bit 0 |

|        |     |     |       |       |            |       |       |

| Lagand |     |     |       |       |            |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-18: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0             | U-0 | U-0              | R/W-0                                     | R/W-0                              | R/W-0      | R/W-0 | R/W-0 |

|-----------------|-----|------------------|-------------------------------------------|------------------------------------|------------|-------|-------|

| —               | —   | —                |                                           |                                    | RP17R<4:0> |       |       |

| bit 15          |     |                  |                                           |                                    |            |       | bit 8 |

|                 |     |                  |                                           |                                    |            |       |       |

| U-0             | U-0 | U-0              | R/W-0                                     | R/W-0                              | R/W-0      | R/W-0 | R/W-0 |

| —               | —   | —                |                                           |                                    | RP16R<4:0> |       |       |

| bit 7           |     |                  |                                           |                                    |            |       | bit 0 |

|                 |     |                  |                                           |                                    |            |       |       |

| Legend:         |     |                  |                                           |                                    |            |       |       |

| R = Readable b  | bit | W = Writable     | bit                                       | U = Unimplemented bit, read as '0' |            |       |       |

| -n = Value at P | OR  | '1' = Bit is set | t '0' = Bit is cleared x = Bit is unknown |                                    |            |       |       |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP17R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP16R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin (see Table 10-2 for peripheral function numbers)

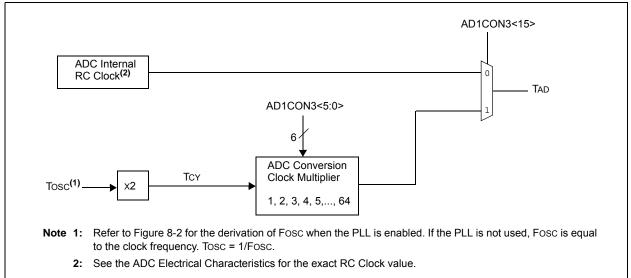

# FIGURE 18-3: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# 18.3 ADC Helpful Tips

- 1. The SMPI<3:0> (AD1CON2<5:2>) control bits:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated if enabled.

- b) When the CSCNA bit (AD1CON2<10>) is set to '1', determines when the ADC analog scan channel list defined in the AD1CSSL/AD1CSSH registers starts over from the beginning.

- c) On devices without a DMA peripheral, determines when ADC result buffer pointer to ADC1BUF0-ADC1BUFF, gets reset back to the beginning at ADC1BUF0.

- On devices without a DMA module, the ADC has 2 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF regardless of which analog inputs are being used subject to the SMPI<3:0> bits (AD1CON2<5:2>) and the condition described in 1c above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- On devices with a DMA module, the ADC module has only 1 ADC result buffer, (i.e., ADC1BUF0), per ADC peripheral and the ADC conversion result must be read either by the CPU or DMA controller before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this

behavior because the CPU code execution is faster than the ADC. As a result, in manual sample mode, particularly where the users code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. On devices with two ADC modules, the ADCxPCFG registers for both ADC modules must be set to a logic '1' to configure a target I/O pin as a digital I/O pin. Failure to do so means that any alternate digital input function will always see only a logic '0' as the digital input buffer is held in Disable mode.

# 18.4 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530271

#### 18.4.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0           | U-0                  | U-0                            | R/W-0                   | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|-----------------|----------------------|--------------------------------|-------------------------|------------------------|-----------------|-----------------|-------|

| ADRC            | _                    | _                              |                         |                        | SAMC<4:0>(      | 1)              |       |

| bit 15          |                      |                                |                         |                        |                 |                 | bit   |

|                 |                      |                                |                         |                        |                 |                 |       |

| U-0             | U-0                  | R/W-0                          | R/W-0                   | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|                 |                      |                                | ADCS                    | <7:0> <sup>(2)</sup>   |                 |                 |       |

| bit 7           |                      |                                |                         |                        |                 |                 | bit   |

| Legend:         |                      |                                |                         |                        |                 |                 |       |

| R = Readable    | bit                  | W = Writable I                 | oit                     | U = Unimpler           | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR                  | '1' = Bit is set               |                         | '0' = Bit is cle       | ared            | x = Bit is unki | nown  |

| bit 15          |                      | Conversion Clo                 | ck Source bit           |                        |                 |                 |       |

| bit 15          | 1 = ADC inter        |                                |                         |                        |                 |                 |       |

|                 |                      | rived from syste               | m clock                 |                        |                 |                 |       |

| bit 14-13       | Unimplemen           | ted: Read as 'o                | )'                      |                        |                 |                 |       |

| bit 12-8        | SAMC<4:0>:           | Auto Sample T                  | ïme bits <sup>(1)</sup> |                        |                 |                 |       |

|                 | 11111 <b>= 31 T</b>  | ĀD                             |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | 00001 <b>= 1 T</b> A |                                |                         |                        |                 |                 |       |

|                 | 00000 <b>= 0</b> TA  |                                |                         | (2)                    |                 |                 |       |

| bit 7-0         |                      | ADC Conversio                  | on Clock Sele           | ct bits <sup>(2)</sup> |                 |                 |       |

|                 | 11111111 =           | Reserved                       |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | • 01000000 =         | Deserved                       |                         |                        |                 |                 |       |

|                 |                      | TCY · (ADCS<                   | 7:0> + 1) = 64          | • TCY = TAD            |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 |                      | TCY · (ADCS<                   |                         |                        |                 |                 |       |

|                 |                      | TCY · (ADCS<7<br>TCY · (ADCS<7 |                         |                        |                 |                 |       |

|                 | 000000000 =          |                                |                         |                        |                 |                 |       |

#### AD4CONS, ADC4 CONTROL DECISTED S

2: This bit is not used if AD1CON3<15> (ADRC) = 1.

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                             |

|-----------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICS<1:0>  | FICD     | Immediate      | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use |

# TABLE 19-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

#### Base Assembly # of # of Status Flags Instr Assembly Syntax Description Words Cycles Mnemonic Affected 35 INC INC f = f + 1 1 1 C,DC,N,OV,Z WREG = f + 1INC f,WREG 1 1 C,DC,N,OV,Z Wd = Ws + 11 C,DC,N,OV,Z TNC Ws,Wd 1 36 INC2 f = f + 2C,DC,N,OV,Z INC2 f 1 1 f,WREG WREG = f + 21 1 C,DC,N,OV,Z INC2 INC2 Ws,Wd Wd = Ws + 21 1 C,DC,N,OV,Z 37 IOR f = f .IOR. WREG 1 IOR f 1 N,Z WREG = f .IOR. WREG IOR f,WREG 1 1 N,Z 1 1 IOR Wd = lit10 .IOR. Wd N,Z #lit10,Wn IOR Wb,Ws,Wd Wd = Wb .IOR. Ws 1 1 N,Z Wd = Wb .IOR. lit5 IOR Wb,#lit5,Wd 1 1 N,Z 38 LNK LNK #lit14 Link Frame Pointer 1 1 None LSR 39 f = Logical Right Shift f 1 1 C,N,OV,Z LSR f WREG = Logical Right Shift f 1 C,N,OV,Z LSR f,WREG 1 LSR Ws,Wd Wd = Logical Right Shift Ws 1 1 C,N,OV,Z Wnd = Logical Right Shift Wb by Wns 1 N.Z LSR 1 Wb, Wns, Wnd LSR Wb,#lit5,Wnd Wnd = Logical Right Shift Wb by lit5 1 1 N.Z 40 MOV Move f to Wn MOV f,Wn 1 1 None MOV f Move f to f 1 1 N,Z Move f to WREG 1 MOV f,WREG 1 None #lit16,Wn Move 16-bit literal to Wn 1 1 None MOV MOV.b #lit8,Wn Move 8-bit literal to Wn 1 1 None MOV Wn,f Move Wn to f 1 1 None MOV Wso,Wdo Move Ws to Wd 1 1 None Move WREG to f WREG, f 1 1 None MOV Move Double from W(ns):W(ns + 1) to Wd 2 None MOV.D Wns,Wd 1 Move Double from Ws to W(nd + 1):W(nd) 2 1 None MOV.D Ws,Wnd 41 MUL MUL.SS Wb,Ws,Wnd {Wnd + 1, Wnd} = signed(Wb) \* signed(Ws) 1 1 None {Wnd + 1, Wnd} = signed(Wb) \* unsigned(Ws) 1 MUL.SU Wb,Ws,Wnd 1 None {Wnd + 1, Wnd} = unsigned(Wb) \* signed(Ws) MUL.US Wb,Ws,Wnd 1 1 None {Wnd + 1, Wnd} = unsigned(Wb) \* 1 1 MUL.UU Wb,Ws,Wnd None unsigned(Ws) {Wnd + 1, Wnd} = signed(Wb) \* unsigned(lit5) 1 1 MUL.SU Wb,#lit5,Wnd None {Wnd + 1, Wnd} = unsigned(Wb) \* 1 1 None MUL.UU Wb,#lit5,Wnd unsigned(lit5) MTTT. f W3:W2 = f \* WREG 1 1 None 42 NEG $f = \overline{f} + 1$ C,DC,N,OV,Z NEG 1 f 1 WREG = $\overline{f} + 1$ NEG f,WREG 1 1 C,DC,N,OV,Z NEG Ws,Wd Wd = Ws + 11 1 C,DC,N,OV,Z 43 NOP No Operation 1 None NOP 1 NOPR No Operation 1 1 None 44 POP POP Pop f from Top-of-Stack (TOS) 1 1 None f Pop from Top-of-Stack (TOS) to Wdo 1 None POP Wdo 1 POP.D Wnd Pop from Top-of-Stack (TOS) to 1 2 None W(nd):W(nd + 1) POP.S Pop Shadow Registers 1 1 All 45 PUSH PUSH f Push f to Top-of-Stack (TOS) 1 1 None Push Wso to Top-of-Stack (TOS) 1 1 None PUSH Wso PUSH.D Push W(ns):W(ns + 1) to Top-of-Stack (TOS) 1 2 None Wns Push Shadow Registers PUSH.S 1 1 None PWRSAV 46 PWRSAV #lit1 Go into Sleep or Idle mode 1 1 WDTO,Sleep

#### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

# TABLE 22-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARAC                               | TERISTICS              |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |      |                                                |  |  |  |

|-----------------------------------------|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------------------------------------------------|--|--|--|

| Parameter<br>No. <sup>(3)</sup>         | Typical <sup>(2)</sup> | Мах | Units Conditions                                                                                                                                                                                     |        |      |                                                |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> |                        |     |                                                                                                                                                                                                      |        |      |                                                |  |  |  |

| DC60d                                   | 55                     | 500 | μA                                                                                                                                                                                                   | -40°C  |      | Base Power-Down Current <sup>(3,4)</sup>       |  |  |  |

| DC60a                                   | 63                     | 300 | μA                                                                                                                                                                                                   | +25°C  | 3.3V |                                                |  |  |  |

| DC60b                                   | 85                     | 350 | μΑ                                                                                                                                                                                                   | +85°C  | 3.3V | Base Power-Down Currenter /                    |  |  |  |

| DC60c                                   | 146                    | 600 | μA                                                                                                                                                                                                   | +125°C |      |                                                |  |  |  |

| DC61d                                   | 8                      | 15  | μA                                                                                                                                                                                                   | -40°C  |      |                                                |  |  |  |

| DC61a                                   | 2                      | 3   | μA                                                                                                                                                                                                   | +25°C  | 3.3∨ | Watchdog Timer Current: ∆IwDT <sup>(3,5)</sup> |  |  |  |

| DC61b                                   | 2                      | 2   | μA                                                                                                                                                                                                   | +85°C  | 3.3V |                                                |  |  |  |

| DC61c                                   | 3                      | 5   | μA                                                                                                                                                                                                   | +125°C |      |                                                |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration word

- All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD, WDT and FSCM are disabled, all peripheral modules are disabled (PMDx bits are all ones)

• VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- RTCC is disabled.

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to stand-by while the device is in Sleep mode)

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The Watchdog Timer Current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but are not tested in manufacturing.

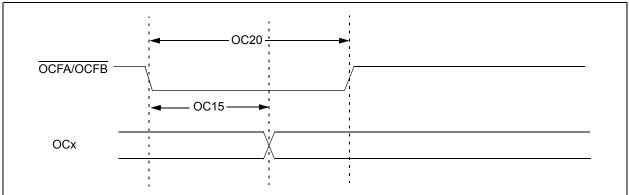

# FIGURE 22-8: OC/PWM MODULE TIMING CHARACTERISTICS

# TABLE 22-27: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |     |          |       |            |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min      | Тур | Max      | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change                                                                                                                                                                                                                                                        | _        | _   | Tcy + 20 | ns    | _          |

| OC20               | TFLT   | Fault Input Pulse-Width                                                                                                                                                                                                                                                                 | Tcy + 20 | _   | —        | ns    | —          |

Note 1: These parameters are characterized but not tested in manufacturing.

|       |             |                              |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |                                             |  |

|-------|-------------|------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------|--|

| Param | Symbol      | Characte                     | eristic <sup>(2)</sup>    | Min                                                                                                                                                                                                                                                                                 | Max  | Units | Conditions                                  |  |

| IS10  | TLO:SCL     | Clock Low Time               | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                 | _    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|       |             |                              | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                 | -    | μS    | Device must operate at a minimum of 10 MHz  |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                 |      | μS    | —                                           |  |

| IS11  | THI:SCL     | Clock High Time              | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                 | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|       |             |                              | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                 | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                 |      | μS    | _                                           |  |

| IS20  | TF:SCL      | SDAx and SCLx<br>Fall Time   | 100 kHz mode              |                                                                                                                                                                                                                                                                                     | 300  | ns    | CB is specified to be from                  |  |

|       |             |                              | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                         | 300  | ns    | 10 to 400 pF                                |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                   | 100  | ns    |                                             |  |

| IS21  | TR:SCL      | SDAx and SCLx<br>Rise Time   | 100 kHz mode              | —                                                                                                                                                                                                                                                                                   | 1000 | ns    | CB is specified to be from                  |  |

|       |             |                              | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                         | 300  | ns    | 10 to 400 pF                                |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                   | 300  | ns    |                                             |  |

| IS25  | TSU:DAT     | Data Input<br>Setup Time     | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                 |      | ns    | —                                           |  |

|       |             |                              | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                 |      | ns    |                                             |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 100                                                                                                                                                                                                                                                                                 |      | ns    |                                             |  |

| IS26  | THD:DAT     | Data Input<br>Hold Time      | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                   | 0    | μS    | —                                           |  |

|       |             |                              | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                   | 0.9  | μS    |                                             |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                   | 0.3  | μS    |                                             |  |

| IS30  | TSU:STA     | Start Condition              | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                 |      | μS    | Only relevant for Repeated                  |  |

|       |             | Setup Time                   | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                 |      | μS    | Start condition                             |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                                |      | μS    |                                             |  |

| IS31  | THD:STA     | Start Condition<br>Hold Time | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                 |      | μS    | After this period, the first                |  |

|       |             |                              | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                 |      | μS    | clock pulse is generated                    |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0.25                                                                                                                                                                                                                                                                                |      | μS    |                                             |  |

| IS33  | Tsu:sto     | Stop Condition<br>Setup Time | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                 | —    | μS    |                                             |  |

|       |             |                              | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                 | —    | μS    |                                             |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0.6                                                                                                                                                                                                                                                                                 | —    | μS    |                                             |  |

| IS34  | THD:ST<br>O | Stop Condition<br>Hold Time  | 100 kHz mode              | 4000                                                                                                                                                                                                                                                                                | —    | ns    | _                                           |  |

|       |             |                              | 400 kHz mode              | 600                                                                                                                                                                                                                                                                                 |      | ns    |                                             |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 250                                                                                                                                                                                                                                                                                 |      | ns    |                                             |  |

| IS40  | TAA:SCL     | Output Valid<br>From Clock   | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                   | 3500 | ns    |                                             |  |

|       |             |                              | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                   | 1000 | ns    |                                             |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                   | 350  | ns    |                                             |  |

| IS45  | TBF:SDA     | Bus Free Time                | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                 |      | μS    | Time the bus must be free                   |  |

|       |             |                              | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                 |      | μS    | before a new transmission                   |  |

|       |             |                              | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                 | —    | μS    | can start                                   |  |

| IS50  | Св          | Bus Capacitive Lo            | ading                     | —                                                                                                                                                                                                                                                                                   | 400  | pF    |                                             |  |

# TABLE 22-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

2: These parameters are characterized by similarity, but are not tested in manufacturing.

# 23.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC24HJ32GP202/204 and PIC24HJ16GP304 electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 22.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 22.0** "**Electrical Characteristics**" is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the PIC24HJ32GP202/204 and PIC24HJ16GP304 high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(4)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to VSS when VDD < 3.0V <sup>(5)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to VSS when VDD $\geq 3.0V^{(5)}$     | 0.3V to 5.6V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(2)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 2 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(2)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- **2:** Maximum allowable current is a function of device maximum power dissipation (see Table 23-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGCx and PGDx pins.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

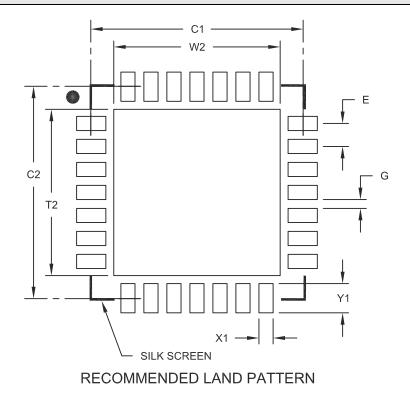

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| [                          | MILLIMETEDS |      |          |      |

|----------------------------|-------------|------|----------|------|

|                            | MILLIMETERS |      |          |      |

| Dimension                  | MIN         | NOM  | MAX      |      |

| Contact Pitch              |             |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 4.70 |

| Optional Center Pad Length | T2          |      |          | 4.70 |

| Contact Pad Spacing        | C1          |      | 6.00     |      |

| Contact Pad Spacing        | C2          |      | 6.00     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.40 |

| Contact Pad Length (X28)   | Y1          |      |          | 0.85 |

| Distance Between Pads      | G           | 0.25 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

# **Revision E (November 2009)**

The revision includes the following global update:

• Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

# TABLE 25-4: MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                 |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|