#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

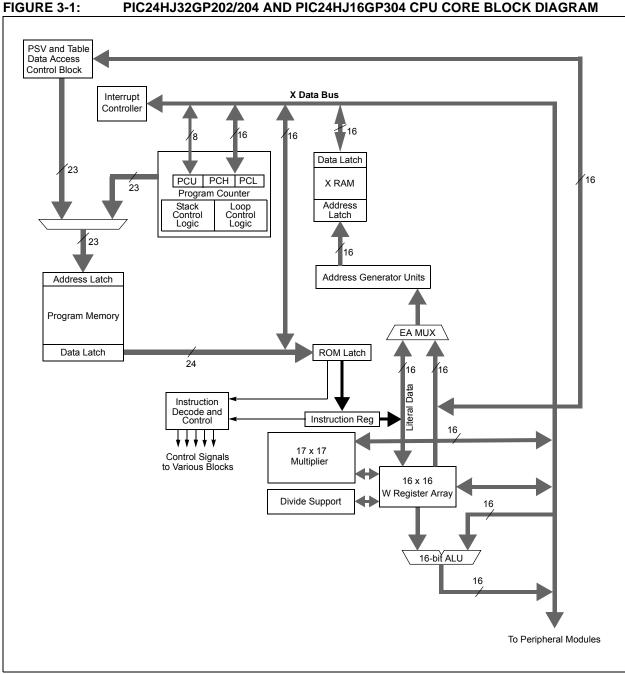

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp202-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0             | U-0 | U-0                                                 | U-0                                            | U-0     | U-0 | U-0 | U-0   |

|-----------------|-----|-----------------------------------------------------|------------------------------------------------|---------|-----|-----|-------|

| —               | —   | —                                                   | —                                              |         | _   | —   | —     |

| bit 15          |     |                                                     |                                                |         |     |     | bit 8 |

|                 |     |                                                     |                                                |         |     |     |       |

| W-0             | W-0 | W-0                                                 | W-0                                            | W-0     | W-0 | W-0 | W-0   |

|                 |     |                                                     | NVMK                                           | EY<7:0> |     |     |       |

| bit 7           |     |                                                     |                                                |         |     |     | bit 0 |

|                 |     |                                                     |                                                |         |     |     |       |

| Legend:         |     | SO = Settable                                       | e Only bit                                     |         |     |     |       |

| R = Readable    | bit | W = Writable bit U = Unimplemented bit, read as '0' |                                                |         |     |     |       |

| -n = Value at F | POR | '1' = Bit is set                                    | is set '0' = Bit is cleared x = Bit is unknown |         |     |     | nown  |

# REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (write-only) bits

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

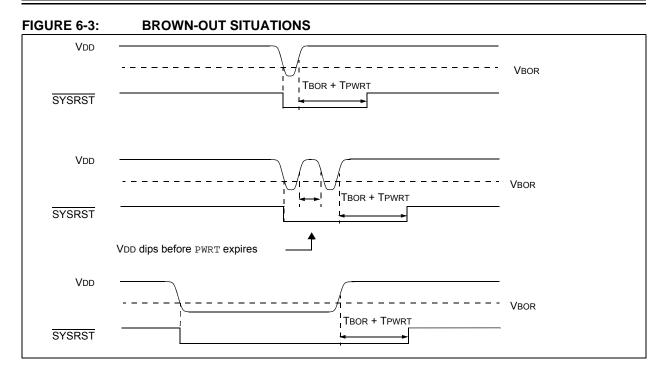

- bit 1 BOR: Brown-out Reset Flag bit 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### 6.5 External Reset (EXTR)

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse-width will generate a Reset. Refer to **Section 22.0** "**Electrical Characteristics**" for minimum pulse-width specifications. The External Reset (MCLR) Pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.5.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate reset signals to Reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to Reset the device when the rest of system is Reset.

#### 6.5.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to Reset the device, the external reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The external reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle, and the reset vector fetch will commence.

The Software Reset (Instruction) Flag (SWR) bit in the Reset Control register (RCON<6>) is set to indicate the software Reset.

## 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog <u>time-out</u> occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out Flag bit (WDTO) in the Reset Control register (RCON<4>) is set to indicate the Watchdog Reset. Refer to **Section 19.4 "Watchdog Timer (WDT)"** for more information on Watchdog Reset.

#### 6.8 Trap Conflict Reset

If a lower-priority hard trap occurs while a higher-priority trap is being processed, a hard trap conflict Reset occurs. The hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

The Trap Reset Flag bit (TRAPR) in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to **Section 7.0 "Interrupt Controller"** for more information on trap conflict Resets.

#### 6.9 Configuration Mismatch Reset

To maintain the integrity of the peripheral pin select control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset occurs.

The Configuration Mismatch Flag bit (CM) in the Reset Control register (RCON<9>) is set to indicate the configuration mismatch Reset. Refer to **Section 10.0 "I/O Ports"** for more information on the configuration mismatch Reset.

Note: The configuration mismatch feature and associated reset flag is not available on all devices.

### 6.10 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- · Security Reset

The Illegal Opcode or Uninitialized W Access Reset Flag bit (IOPUWR) in the Reset Control register (RCON<14>) is set to indicate the illegal condition device Reset.

#### 6.10.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The illegal opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the illegal opcode Reset, use only the lower 16 bits of

each program memory section to store the data values. The upper 8 bits should be programmed with 0x3F, which is an illegal opcode value.

#### 6.10.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the uninitialized W register as an address pointer will Reset the device. The W register array (with the exception of W15) is cleared during all resets and is considered uninitialized until written to.

#### 6.10.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine, or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an Interrupt or Trap vector.

Refer to Section 19.6 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

### 6.11 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the reset flag bit operation.

| Flag Bit         | Set by:                                                                | Cleared by:                                         |

|------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                    | POR, BOR                                            |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access or Security Reset | POR, BOR                                            |

| CM (RCON<9>)     | Configuration Mismatch                                                 | POR, BOR                                            |

| EXTR (RCON<7>)   | MCLR Reset                                                             | POR                                                 |

| SWR (RCON<6>)    | RESET instruction                                                      | POR, BOR                                            |

| WDTO (RCON<4>)   | WDT time-out                                                           | PWRSAV instruction,<br>CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEP instruction                                              | POR, BOR                                            |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                               | POR, BOR                                            |

| BOR (RCON<1>)    | POR, BOR                                                               | —                                                   |

| POR (RCON<0>)    | POR                                                                    | —                                                   |

TABLE 6-3:RESET FLAG BIT OPERATION

Note: All Reset flag bits can be set or cleared by user software.

| U-0             | U-0                                                     | U-0                 | U-0              | U-0              | U-0              | U-0             | U-0   |

|-----------------|---------------------------------------------------------|---------------------|------------------|------------------|------------------|-----------------|-------|

| —               | —                                                       | —                   |                  | —                |                  | —               | —     |

| bit 15          |                                                         |                     |                  |                  |                  |                 | bit 8 |

|                 |                                                         |                     |                  |                  |                  |                 |       |

| U-0             | R/W-1                                                   | R/W-0               | R/W-0            | U-0              | U-0              | U-0             | U-0   |

| —               |                                                         | INT2IP<2:0>         |                  | —                | —                | —               | —     |

| bit 7           |                                                         |                     |                  |                  |                  |                 | bit 0 |

|                 |                                                         |                     |                  |                  |                  |                 |       |

| Legend:         |                                                         |                     |                  |                  |                  |                 |       |

| R = Readable    | bit                                                     | W = Writable        | bit              | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at P | OR                                                      | '1' = Bit is set    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |                                                         |                     |                  |                  |                  |                 |       |

| bit 15-7        | Unimplemen                                              | ted: Read as 'd     | )'               |                  |                  |                 |       |

| bit 6-4         | bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits |                     |                  |                  |                  |                 |       |

|                 | 111 = Interrup                                          | ot is priority 7 (I | nighest priority | y interrupt)     |                  |                 |       |

|                 | •                                                       |                     |                  |                  |                  |                 |       |

### REGISTER 7-17: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

bit 3-0 Unimplemented: Read as '0'

001 = Interrupt is priority 1 000 = Interrupt source is disabled

### 9.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |

|-------|-----------------------------------------|

|       | the product page using the link above,  |

|       | enter this URL in your browser:         |

|       | http://www.microchip.com/wwwproducts/   |

|       | Devices.aspx?dDocName=en530271          |

#### 9.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 10.7 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 22-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and VSS. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 22.0 "Electrical Characteristics"** for additional information.

#### 10.8 I/O Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.8.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530271

| U-0                          | U-0                                                                                                                                                                                              | U-0             | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|-----------------|-----------------|-------|

| _                            | _                                                                                                                                                                                                | _               |                 |                  | IC2R<4:0>       |                 |       |

| oit 15                       |                                                                                                                                                                                                  |                 |                 |                  |                 |                 | bit 8 |

|                              |                                                                                                                                                                                                  |                 |                 |                  |                 |                 |       |

| U-0                          | U-0                                                                                                                                                                                              | U-0             | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| —                            | —                                                                                                                                                                                                | —               |                 |                  | IC1R<4:0>       |                 |       |

| oit 7                        |                                                                                                                                                                                                  |                 |                 |                  |                 |                 | bit C |

|                              |                                                                                                                                                                                                  |                 |                 |                  |                 |                 |       |

| <b>_egend:</b><br>R = Readab | le hit                                                                                                                                                                                           | W = Writable    | bit             | l I = I Inimoler | mented bit, rea | d as '0'        |       |

| n = Value a                  |                                                                                                                                                                                                  | '1' = Bit is se |                 | '0' = Bit is cle |                 | x = Bit is unkr |       |

|                              |                                                                                                                                                                                                  |                 |                 | e Bitleoid       |                 |                 | lowin |

|                              | IC2R<4:0>: Assign Input Capture 2 (IC2) to the corresponding RPn pin<br>11111 = Input tied to Vss<br>11001 = Input tied to RP25<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                 |                 |                  |                 |                 |       |

|                              | 00000 = Inpu                                                                                                                                                                                     |                 |                 |                  |                 |                 |       |

| bit 7-5                      | Unimplemen                                                                                                                                                                                       | ted: Read as    | '0'             |                  |                 |                 |       |

| bit 4-0                      | 11111 <b>= I</b> npu                                                                                                                                                                             |                 | apture 1 (IC1)† | to the correspo  | onding RPn pir  | I               |       |

## REGISTER 10-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

# 12.0 TIMER2/3 FEATURE

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 11. Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 feature has 32-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

As a 32-bit timer, the Timer2/3 feature permits operation in three modes:

- Two Independent 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3)

- Single 32-bit synchronous counter (Timer2/3)

The Timer2/3 feature also supports:

- Timer gate operation

- Selectable Prescaler Settings

- Timer operation during Idle and Sleep modes

- · Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features that are listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. T2CON registers are shown in generic form in Register 12-1. T3CON registers are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 is the least significant word (lsw), and Timer3 is the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bit is used for setup and control. Timer2 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flags.

### 12.1 32-bit Operation

To configure the Timer2/3 feature for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 contains the most significant word of the value, while PR2 contains the least significant word.

- 5. Set the interrupt enable bit T3IE, if interrupts are required. Use the priority bits T3IP<2:0> to set the interrupt priority. While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair TMR3:TMR2. TMR3 always contains the most significant word of the count, while TMR2 contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                            |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                    |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                     |

|       | 1 = Read – indicates data transfer is output from slave                                                                                                                                                               |

|       | 0 = Write – indicates data transfer is input to slave                                                                                                                                                                 |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                                                                                                        |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                   |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                                                                                                 |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                                                                                            |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                                                                                                  |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                  |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul> |

## 17.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, receive inputs react UART to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 17.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530271

#### 17.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

#### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                     |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>    |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                             |

|       | 1 = Receive buffer has overflowed                                                                                                                                           |

|       | 0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the UxRSR to the empty state |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

|       |                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

| R/W-0           | U-0                  | U-0                            | R/W-0                   | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|-----------------|----------------------|--------------------------------|-------------------------|------------------------|-----------------|-----------------|-------|

| ADRC            | _                    | _                              |                         |                        | SAMC<4:0>(      | 1)              |       |

| bit 15          |                      |                                |                         |                        |                 |                 | bit   |

|                 |                      |                                |                         |                        |                 |                 |       |

| U-0             | U-0                  | R/W-0                          | R/W-0                   | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|                 |                      |                                | ADCS                    | <7:0> <sup>(2)</sup>   |                 |                 |       |

| bit 7           |                      |                                |                         |                        |                 |                 | bit   |

| Legend:         |                      |                                |                         |                        |                 |                 |       |

| R = Readable    | bit                  | W = Writable I                 | oit                     | U = Unimpler           | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR                  | '1' = Bit is set               |                         | '0' = Bit is cle       | ared            | x = Bit is unki | nown  |

| bit 15          |                      | Conversion Clo                 | ck Source bit           |                        |                 |                 |       |

| bit 15          | 1 = ADC inter        |                                |                         |                        |                 |                 |       |

|                 |                      | rived from syste               | m clock                 |                        |                 |                 |       |

| bit 14-13       | Unimplemen           | ted: Read as 'o                | )'                      |                        |                 |                 |       |

| bit 12-8        | SAMC<4:0>:           | Auto Sample T                  | ïme bits <sup>(1)</sup> |                        |                 |                 |       |

|                 | 11111 <b>= 31 T</b>  | ĀD                             |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | 00001 <b>= 1 T</b> A |                                |                         |                        |                 |                 |       |

|                 | 00000 <b>= 0</b> TA  |                                |                         | (2)                    |                 |                 |       |

| bit 7-0         |                      | ADC Conversio                  | on Clock Sele           | ct bits <sup>(2)</sup> |                 |                 |       |

|                 | 11111111 =           | Reserved                       |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | • 01000000 =         | Deserved                       |                         |                        |                 |                 |       |

|                 |                      | TCY · (ADCS<                   | 7:0> + 1) = 64          | • TCY = TAD            |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 | •                    |                                |                         |                        |                 |                 |       |

|                 |                      | TCY · (ADCS<                   |                         |                        |                 |                 |       |

|                 |                      | TCY · (ADCS<7<br>TCY · (ADCS<7 |                         |                        |                 |                 |       |

|                 | 000000000 =          |                                |                         |                        |                 |                 |       |

#### AD4CONS, ADC4 CONTROL DECISTED S

2: This bit is not used if AD1CON3<15> (ADRC) = 1.

### 21.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 21.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 21.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 21.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| AC CHA | RACTERI    |                           |                           | (unless othe | rwise sta<br>perature | ated)<br>-40°C | ns: 3.0V to 3.6V<br>≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +125°C for Extended |

|--------|------------|---------------------------|---------------------------|--------------|-----------------------|----------------|-------------------------------------------------------------------------------|

| Param  | Symbol     | Characte                  | eristic <sup>(2)</sup>    | Min          | Max                   | Units          | Conditions                                                                    |

| IS10   | TLO:SCL    | Clock Low Time            | 100 kHz mode              | 4.7          | _                     | μS             | Device must operate at a minimum of 1.5 MHz                                   |

|        |            |                           | 400 kHz mode              | 1.3          | -                     | μS             | Device must operate at a minimum of 10 MHz                                    |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.5          |                       | μS             | —                                                                             |

| IS11   | THI:SCL    | Clock High Time           | 100 kHz mode              | 4.0          | —                     | μS             | Device must operate at a minimum of 1.5 MHz                                   |

|        |            |                           | 400 kHz mode              | 0.6          | —                     | μS             | Device must operate at a minimum of 10 MHz                                    |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.5          |                       | μS             | _                                                                             |

| IS20   | TF:SCL     | SDAx and SCLx             | 100 kHz mode              |              | 300                   | ns             | CB is specified to be from                                                    |

|        |            | Fall Time                 | 400 kHz mode              | 20 + 0.1 Св  | 300                   | ns             | 10 to 400 pF                                                                  |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | —            | 100                   | ns             |                                                                               |

| IS21   | TR:SCL     | SDAx and SCLx             | 100 kHz mode              | —            | 1000                  | ns             | CB is specified to be from                                                    |

|        |            | Rise Time                 | 400 kHz mode              | 20 + 0.1 Св  | 300                   | ns             | 10 to 400 pF                                                                  |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | —            | 300                   | ns             |                                                                               |

| IS25   |            | Data Input                | 100 kHz mode              | 250          |                       | ns             | —                                                                             |

|        | Setup Time | 400 kHz mode              | 100                       |              | ns                    |                |                                                                               |

|        |            | 1 MHz mode <sup>(1)</sup> | 100                       |              | ns                    |                |                                                                               |

| IS26   | THD:DAT    | Data Input<br>Hold Time   | 100 kHz mode              | 0            | 0                     | μS             | —                                                                             |

|        |            |                           | 400 kHz mode              | 0            | 0.9                   | μS             |                                                                               |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0            | 0.3                   | μS             |                                                                               |

| IS30   | TSU:STA    | Start Condition           | 100 kHz mode              | 4.7          |                       | μS             | Only relevant for Repeated                                                    |

|        |            | Setup Time                | 400 kHz mode              | 0.6          |                       | μS             | Start condition                                                               |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.25         |                       | μS             |                                                                               |

| IS31   | THD:STA    | Start Condition           | 100 kHz mode              | 4.0          |                       | μS             | After this period, the first                                                  |

|        |            | Hold Time                 | 400 kHz mode              | 0.6          |                       | μS             | clock pulse is generated                                                      |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.25         |                       | μS             |                                                                               |

| IS33   | TSU:STO    | Stop Condition            | 100 kHz mode              | 4.7          |                       | μS             | _                                                                             |

|        |            | Setup Time                | 400 kHz mode              | 0.6          |                       | μS             |                                                                               |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.6          | —                     | μS             |                                                                               |

| IS34   | THD:ST     | Stop Condition            | 100 kHz mode              | 4000         | —                     | ns             | _                                                                             |

|        | 0          | Hold Time                 | 400 kHz mode              | 600          |                       | ns             |                                                                               |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 250          |                       | ns             |                                                                               |

| IS40   | TAA:SCL    | Output Valid              | 100 kHz mode              | 0            | 3500                  | ns             |                                                                               |

|        |            | From Clock                | 400 kHz mode              | 0            | 1000                  | ns             |                                                                               |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0            | 350                   | ns             |                                                                               |

| IS45   | TBF:SDA    | Bus Free Time             | 100 kHz mode              | 4.7          |                       | μS             | Time the bus must be free                                                     |

|        |            |                           | 400 kHz mode              | 1.3          |                       | μS             | before a new transmission                                                     |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.5          | —                     | μS             | can start                                                                     |

| IS50   | Св         | Bus Capacitive Lo         | ading                     | —            | 400                   | pF             |                                                                               |

#### TABLE 22-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

2: These parameters are characterized by similarity, but are not tested in manufacturing.

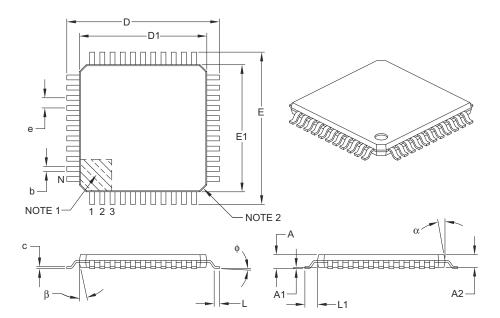

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units           |      | MILLIMETERS | 6    |

|--------------------------|-----------------|------|-------------|------|

| D                        | imension Limits | MIN  | NOM         | MAX  |

| Number of Leads          | N               |      | 44          |      |

| Lead Pitch               | е               |      | 0.80 BSC    |      |

| Overall Height           | A               | -    | -           | 1.20 |

| Molded Package Thickness | A2              | 0.95 | 1.00        | 1.05 |

| Standoff                 | A1              | 0.05 | -           | 0.15 |

| Foot Length              | L               | 0.45 | 0.60        | 0.75 |

| Footprint L1 1.00 REF    |                 |      |             |      |

| Foot Angle               | φ               | 0°   | 3.5°        | 7°   |

| Overall Width            | E               |      | 12.00 BSC   |      |

| Overall Length           | D               |      | 12.00 BSC   |      |

| Molded Package Width     | E1              |      | 10.00 BSC   |      |

| Molded Package Length    | D1              |      | 10.00 BSC   |      |

| Lead Thickness           | С               | 0.09 | -           | 0.20 |

| Lead Width               | b               | 0.30 | 0.37        | 0.45 |

| Mold Draft Angle Top     | α               | 11°  | 12°         | 13°  |

| Mold Draft Angle Bottom  | β               | 11°  | 12°         | 13°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

| Section Name                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 15.0 "Inter-Integrated<br>Circuit (I <sup>2</sup> C™)"          | <ul> <li>Removed the following sections, which are now available in the related section of the dsPIC33F/PIC24H Family Reference Manual:</li> <li>15.3 "I<sup>2</sup>C Interrupts"</li> <li>15.4 "Baud Rate Generator" (retained Figure 15-1: I<sup>2</sup>C Block Diagram)</li> <li>15.5 "I<sup>2</sup>C Module Addresses"</li> <li>15.6 "Slave Address Masking"</li> <li>15.7 "IPMI Support"</li> <li>15.8 "General Call Address Support"</li> <li>15.9 "Automatic Clock Stretch"</li> <li>15.10 "Software Controlled Clock Stretching (STREN = 1)"</li> <li>15.12 "Clock Arbitration"</li> <li>15.13 "Multi-Master Communication, Bus Collision, and Bus Arbitration"</li> <li>15.14 "Peripheral Pin Select Limitations"</li> </ul>                                                    |

| Section 16.0 "Universal<br>Asynchronous Receiver Transmitter<br>(UART)" | <ul> <li>Removed the following sections, which are now available in the related section of the dsPIC33F/PIC24H Family Reference Manual:</li> <li>16.1 "UART Baud Rate Generator"</li> <li>16.2 "Transmitting in 8-bit Data Mode"</li> <li>16.3 "Transmitting in 9-bit Data Mode"</li> <li>16.4 "Break and Sync Transmit Sequence"</li> <li>16.5 "Receiving in 8-bit or 9-bit Data Mode"</li> <li>16.6 "Flow Control Using UxCTS and UxRTS Pins"</li> <li>16.7 "Infrared Support"</li> <li>Removed IrDA references and Note 1, and updated the bit and bit value descriptions for UTXINV (UxSTA&lt;14&gt;) in the UARTx Status and Control Register (see Register 16-2).</li> </ul>                                                                                                       |

| Section 17.0 "10-bit/12-bit Analog-<br>to-Digital Converter (ADC)"      | Removed Equation 17-1: ADC Conversion Clock Period and Figure 17-2:<br>ADC Transfer Function (10-bit Example).<br>Added ADC1 Module Block Diagram for PIC24HFJ16GP304 and<br>PIC24HJ32GP204 Devices (Figure 17-1) and ADC1 Module Block Diagram<br>FOR PIC24HJ32GP202 Devices (Figure 17-2).<br>Added Note 2 to Figure 17-3: ADC Conversion Clock Period Block Diagram.<br>Added device-specific information to Note 1 in the ADC1 Input Scan Select<br>Register Low (see Register 17-6), and updated the default bit value for bits<br>12-10 (CSS12-CSS10) from U-0 to R/W-0.<br>Added device-specific information to Note 1 in the ADC1 Port Configuration<br>Register Low (see Register 17-7), and updated the default bit value for bits<br>12-10 (PCFG12-PCFG10) from U-0 to R/W-0. |

#### TABLE 25-1: MAJOR SECTION UPDATES (CONTINUED)

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE:                  | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent            |  |

|-----------------------------|------------------------------------------------------------------------------------------|-----------------------------|--|

| From                        | n: Name                                                                                  |                             |  |

|                             | Company                                                                                  |                             |  |

|                             | Address                                                                                  |                             |  |

|                             | City / State / ZIP / Country                                                             |                             |  |

|                             | Telephone: ()                                                                            | FAX: ()                     |  |

| Application (optional):     |                                                                                          |                             |  |

| Would you like a reply? Y N |                                                                                          |                             |  |

| Devi                        | ce: PIC24HJ32GP202/204 and PIC24HJ16GP304                                                | Literature Number: DS70289J |  |

| Questions:                  |                                                                                          |                             |  |

| 1.                          | 1. What are the best features of this document?                                          |                             |  |

| 2                           | . How does this document meet your hardware and software development needs?              |                             |  |

| ۲.                          |                                                                                          |                             |  |

| -                           |                                                                                          |                             |  |

| 3.                          | Do you find the organization of this document easy to follow? If not, why?               |                             |  |

| -                           |                                                                                          |                             |  |

| 4.                          | What additions to the document do you think would enhance the structure and subject?     |                             |  |

| -                           |                                                                                          |                             |  |

| 5.                          | What deletions from the document could be made without affecting the overall usefulness? |                             |  |

| -                           |                                                                                          |                             |  |

| 6.                          | Is there any incorrect or misleading information (what and where)?                       |                             |  |

|                             |                                                                                          |                             |  |

| 7.                          | How would you improve this document?                                                     |                             |  |

|                             |                                                                                          |                             |  |

|                             |                                                                                          |                             |  |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-62076-440-4

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.