Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj32gp202t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0                                                 | U-0                        | U-0                                                            | U-0             | U-0                 | U-0              | U-0      | U-0   |

|-----------------------------------------------------|----------------------------|----------------------------------------------------------------|-----------------|---------------------|------------------|----------|-------|

| —                                                   | —                          | —                                                              | —               | —                   | —                | -        | -     |

| bit 15                                              |                            |                                                                |                 |                     |                  |          | bit 8 |

|                                                     |                            |                                                                |                 |                     |                  |          |       |

| U-0                                                 | U-0                        | U-0                                                            | U-0             | R/C-0               | R/W-0            | U-0      | U-0   |

| —                                                   | —                          | —                                                              | —               | IPL3 <sup>(1)</sup> | PSV              | —        | —     |

| bit 7                                               |                            |                                                                |                 |                     |                  |          | bit 0 |

|                                                     |                            |                                                                |                 |                     |                  |          |       |

| Legend:                                             |                            | C = Clear only                                                 | / bit           |                     |                  |          |       |

| R = Readable bit W = Writable bit -n = Value at POR |                            |                                                                | POR             | '1' = Bit is set    |                  |          |       |

| 0' = Bit is cle                                     | ared                       | 'x = Bit is unk                                                | nown            | U = Unimpler        | mented bit, read | l as '0' |       |

|                                                     |                            |                                                                |                 |                     |                  |          |       |

| bit 15-4                                            | Unimplemented: Read as '0' |                                                                |                 |                     |                  |          |       |

| bit 3                                               | IPL3: CPU In               | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(1)</sup> |                 |                     |                  |          |       |

|                                                     | 1 = CPU inter              | rupt priority lev                                              | el is greater t | han 7               |                  |          |       |

|                                                     | 0 = CPU inter              | rupt priority lev                                              | el is 7 or less |                     |                  |          |       |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

| bit 2 | PSV: Program Space Visibility in Data Space Enable bit |

|-------|--------------------------------------------------------|

|       | 1 = Program space visible in data space                |

|       | 0 = Program space not visible in data space            |

bit 1-0 Unimplemented: Read as '0'

Note 1: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

## 6.9 Configuration Mismatch Reset

To maintain the integrity of the peripheral pin select control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset occurs.

The Configuration Mismatch Flag bit (CM) in the Reset Control register (RCON<9>) is set to indicate the configuration mismatch Reset. Refer to **Section 10.0 "I/O Ports"** for more information on the configuration mismatch Reset.

Note: The configuration mismatch feature and associated reset flag is not available on all devices.

## 6.10 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- · Security Reset

The Illegal Opcode or Uninitialized W Access Reset Flag bit (IOPUWR) in the Reset Control register (RCON<14>) is set to indicate the illegal condition device Reset.

### 6.10.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The illegal opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the illegal opcode Reset, use only the lower 16 bits of

each program memory section to store the data values. The upper 8 bits should be programmed with 0x3F, which is an illegal opcode value.

### 6.10.2 UNINITIALIZED W REGISTER RESET

Any attempts to use the uninitialized W register as an address pointer will Reset the device. The W register array (with the exception of W15) is cleared during all resets and is considered uninitialized until written to.

## 6.10.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (Boot and Secure Segment), that operation will cause a security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a Call, Jump, Computed Jump, Return, Return from Subroutine, or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an Interrupt or Trap vector.

Refer to Section 19.6 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

## 6.11 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the reset flag bit operation.

| Flag Bit         | Set by:                                                                | Cleared by:                                         |

|------------------|------------------------------------------------------------------------|-----------------------------------------------------|

| TRAPR (RCON<15>) | Trap conflict event                                                    | POR, BOR                                            |

| IOPWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access or Security Reset | POR, BOR                                            |

| CM (RCON<9>)     | Configuration Mismatch                                                 | POR, BOR                                            |

| EXTR (RCON<7>)   | MCLR Reset                                                             | POR                                                 |

| SWR (RCON<6>)    | RESET instruction                                                      | POR, BOR                                            |

| WDTO (RCON<4>)   | WDT time-out                                                           | PWRSAV instruction,<br>CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)  | PWRSAV #SLEEP instruction                                              | POR, BOR                                            |

| IDLE (RCON<2>)   | PWRSAV #IDLE instruction                                               | POR, BOR                                            |

| BOR (RCON<1>)    | POR, BOR                                                               | —                                                   |

| POR (RCON<0>)    | POR                                                                    | —                                                   |

TABLE 6-3:RESET FLAG BIT OPERATION

Note: All Reset flag bits can be set or cleared by user software.

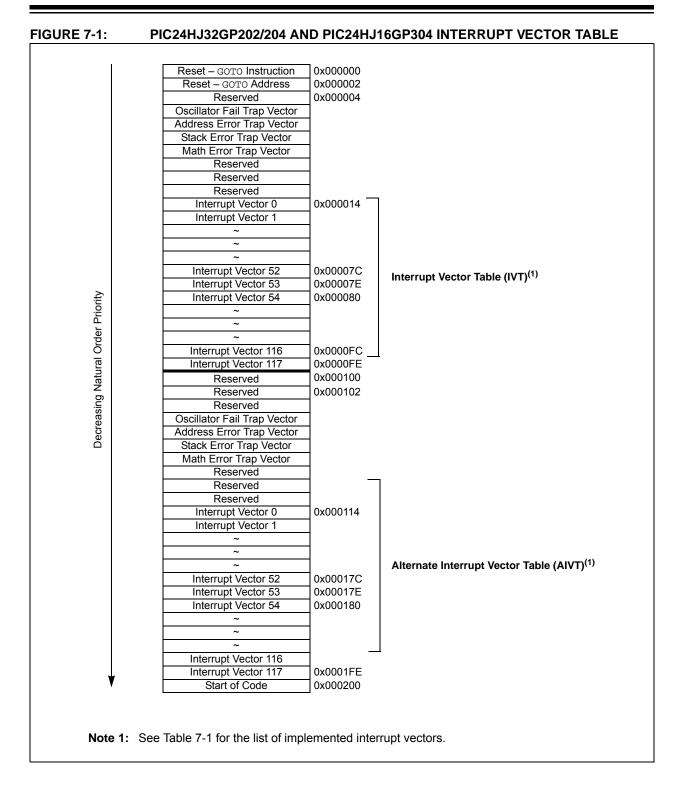

| TABLE 7-1:       | INTERRU                              | PT VECTORS               |                                       |                               |

|------------------|--------------------------------------|--------------------------|---------------------------------------|-------------------------------|

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address AIVT Address |                                       | Interrupt Source              |

| 8                | 0                                    | 0x000014                 | 0x000114                              | INT0 – External Interrupt 0   |

| 9                | 1                                    | 0x000016                 | 0x000016 0x000116 IC1 – Input Capture |                               |

| 10               | 2                                    | 0x000018                 | 0x000118                              | OC1 – Output Compare 1        |

| 11               | 3                                    | 0x00001A                 | 0x00011A                              | T1 – Timer1                   |

| 12               | 4                                    | 0x00001C                 | 0x00011C                              | Reserved                      |

| 13               | 5                                    | 0x00001E                 | 0x00011E                              | IC2 – Input Capture 2         |

| 14               | 6                                    | 0x000020                 | 0x000120                              | OC2 – Output Compare 2        |

| 15               | 7                                    | 0x000022                 | 0x000122                              | T2 – Timer2                   |

| 16               | 8                                    | 0x000024                 | 0x000124                              | T3 – Timer3                   |

| 17               | 9                                    | 0x000026                 | 0x000126                              | SPI1E – SPI1 Error            |

| 18               | 10                                   | 0x000028                 | 0x000128                              | SPI1 – SPI1 Transfer Done     |

| 19               | 11                                   | 0x00002A                 | 0x00012A                              | U1RX – UART1 Receiver         |

| 20               | 12                                   | 0x00002C                 | 0x00002C 0x00012C U1TX – UART1        |                               |

| 21               | 13                                   | 0x00002E                 | 0x00012E                              | ADC1 – ADC1                   |

| 22               | 14                                   | 0x000030                 | 0x000130                              | Reserved                      |

| 23               | 15                                   | 0x000032                 | 0x000132                              | Reserved                      |

| 24               | 16                                   | 0x000034                 | 0x000134                              | SI2C1 – I2C1 Slave Events     |

| 25               | 17                                   | 0x000036                 | 0x000136                              | MI2C1 – I2C1 Master Events    |

| 26               | 18                                   | 0x000038                 | 0x000138                              | Reserved                      |

| 27               | 19                                   | 0x00003A                 | 0x00013A                              | Change Notification Interrupt |

| 28               | 20                                   | 0x00003C                 | 0x00013C                              | INT1 – External Interrupt 1   |

| 29               | 21                                   | 0x00003E                 | 0x00013E                              | Reserved                      |

| 30               | 22                                   | 0x000040                 | 0x000140                              | IC7 – Input Capture 7         |

| 31               | 23                                   | 0x000042                 | 0x000142                              | IC8 – Input Capture 8         |

| 32-36            | 24-28                                | 0x000044-0x00004C        | 0x000144-0x00014C                     | Reserved                      |

| 37               | 29                                   | 0x00004E                 | 0x00014E                              | INT2 – External Interrupt 2   |

| 38-72            | 30-64                                | 0x000050-0x000094        | 0x000150-0x000194                     | Reserved                      |

| 73               | 65                                   | 0x000096                 | 0x000196                              | U1E – UART1 Error             |

| 74-125           | 66-117                               | 0x000098-0x0000FE        | 0x000198-0x0001FE                     | Reserved                      |

## TABLE 7-1: INTERRUPT VECTORS

## TABLE 7-2: TRAP VECTORS

| Vector Number | ber IVT Address AIVT Address |          | Trap Source        |  |

|---------------|------------------------------|----------|--------------------|--|

| 0             | 0x000004                     | 0x000104 | Reserved           |  |

| 1             | 0x000006                     | 0x000106 | Oscillator Failure |  |

| 2             | 0x000008                     | 0x000108 | Address Error      |  |

| 3             | 0x00000A                     | 0x00010A | Stack Error        |  |

| 4             | 0x00000C 0x00010C Math Error |          | Math Error         |  |

| 5             | 0x00000E 0x00010E Reserved   |          | Reserved           |  |

| 6             | 0x000010                     | 0x000110 | Reserved           |  |

| 7             | 0x000012                     | Reserved |                    |  |

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 U1RXIP<2:0> SPI1IP<2:0> bit 8 bit 15 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 SPI1EIP<2:0> T3IP<2:0> bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 U1RXIP<2:0>: UART1 Receiver Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 SPI1IP<2:0>: SPI1 Event Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 7 Unimplemented: Read as '0' bit 6-4 SPI1EIP<2:0>: SPI1 Error Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 T3IP<2:0>: Timer3 Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled

## REGISTER 7-13: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

## 7.5 Interrupt Setup Procedures

## 7.5.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Set the interrupt enable control bit associated with the source in the appropriate IECx register to enable the interrupt source.

## 7.5.2 INTERRUPT SERVICE ROUTINE

The method used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address depends on the programming language (C or Assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.5.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.5.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the  ${\tt POP}$  instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

| bit 3   | <b>CF:</b> Clock Fail Detect bit (read/clear by application)<br>1 = FSCM has detected clock failure<br>0 = FSCM has not detected clock failure |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | Unimplemented: Read as '0'                                                                                                                     |

| bit 1   | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                                                                  |

|         | <ol> <li>1 = Enable secondary oscillator</li> <li>0 = Disable secondary oscillator</li> </ol>                                                  |

| bit 0   | <b>OSWEN:</b> Oscillator Switch Enable bit                                                                                                     |

|         | <ul><li>1 = Request oscillator switch to selection specified by</li><li>0 = Oscillator switch is complete</li></ul>                            |

| Note 1: | Writes to this register require an unlock sequence. Refer to                                                                                   |

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70186) in the *"dsPIC33F/PIC24H Family Reference Manual"* for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

NOSC<2:0> bits

3: This register is reset only on a Power-on Reset (POR).

## REGISTER 10-11: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----------|-------|-------|-------|-------|

| —      | —   | —   | RP3R<4:0> |       |       |       |       |

| bit 15 |     |     |           |       |       |       | bit 8 |

|        |     |     |           |       |       |       |       |

| U-0    | U-0 | U-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|        | _   | _   | RP2R<4:0> |       |       |       |       |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 15-13 Unimplemented: Read as '0'

bit 7

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin (see Table 10-2 for peripheral function numbers)

## REGISTER 10-12: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0                                                                  | U-0                                                                                                                                      | U-0              | R/W-0 | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------|-----------|-----------------|-------|

| —                                                                    | —                                                                                                                                        | —                |       |                  | RP5R<4:0> |                 |       |

| bit 15                                                               |                                                                                                                                          |                  |       |                  |           |                 | bit 8 |

|                                                                      |                                                                                                                                          |                  |       |                  |           |                 |       |

| U-0                                                                  | U-0                                                                                                                                      | U-0              | R/W-0 | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

| _                                                                    | —                                                                                                                                        | —                |       |                  | RP4R<4:0> |                 |       |

| bit 7                                                                |                                                                                                                                          |                  |       |                  |           |                 | bit 0 |

|                                                                      |                                                                                                                                          |                  |       |                  |           |                 |       |

| Legend:                                                              |                                                                                                                                          |                  |       |                  |           |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                                                          |                  |       |                  |           |                 |       |

| -n = Value at I                                                      | POR                                                                                                                                      | '1' = Bit is set |       | '0' = Bit is cle | ared      | x = Bit is unkr | nown  |

|                                                                      |                                                                                                                                          |                  |       |                  |           |                 |       |

| bit 15-13                                                            | bit 15-13 Unimplemented: Read as '0'                                                                                                     |                  |       |                  |           |                 |       |

| bit 12-8                                                             | bit 12-8 <b>RP5R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP5 Output Pin (see Table 10-2 for peripher function numbers) |                  |       |                  |           | for peripheral  |       |

| bit 7-5 Unimplemented: Read as '0'                                   |                                                                                                                                          |                  |       |                  |           |                 |       |

|                                                                      |                                                                                                                                          |                  |       |                  |           |                 |       |

bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin (see Table 10-2 for peripheral function numbers)

bit 0

NOTES:

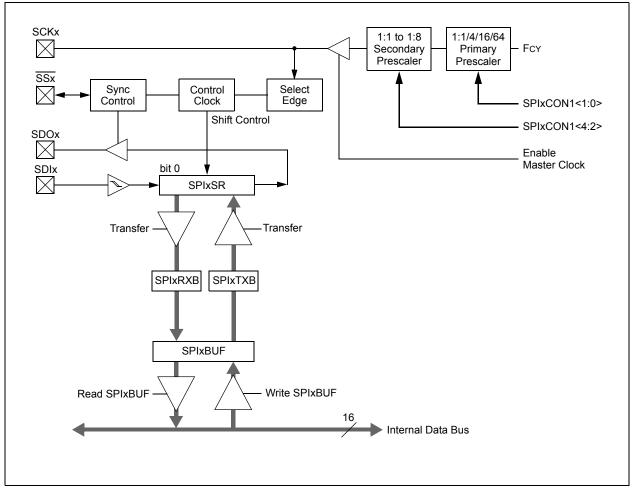

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJ32GP202/204 and PIC24HJ16GP304 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 18. Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters (ADCs), and so on. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of these four pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

### FIGURE 15-1: SPI MODULE BLOCK DIAGRAM

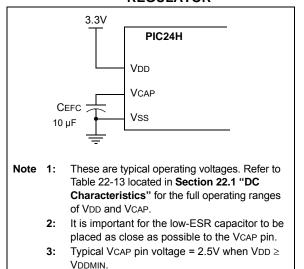

## 19.2 On-Chip Voltage Regulator

PIC24HJ32GP202/204 All of the and PIC24HJ16GP304 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24HJ32GP202/204 and PIC24HJ16GP304 family incorporate an on-chip regulator that allows the device to run its core logic from Vdd.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 19-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 22-13 located in **Section 22.1** "**DC Characteristics**".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

### FIGURE 19-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

# 19.3 Brown-Out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device in case VDD falls below the BOR threshold voltage.

# TABLE 22-35:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

|              |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |

|--------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                                  | —                                                                                                                                                                                                                                                                                       | _                  | 11  | MHz   | See Note 3                           |  |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                                                                                                       |                    |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP73         | TscR                  | SCKx Input Rise Time                                         | _                                                                                                                                                                                                                                                                                       |                    |     | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                                                                                                                       |                    | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                                                                                                                       |                    |     | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                                                                                                                       | 6                  | 20  | ns    | —                                    |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                                                                                                                      | _                  | _   | ns    | —                                    |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                                                                                                                      |                    |     | ns    | —                                    |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                                                                                                                      | -                  |     | ns    | —                                    |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                     | —                  | —   | ns    | _                                    |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>        | 10                                                                                                                                                                                                                                                                                      | _                  | 50  | ns    | —                                    |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                                                                                                                                                                                                                                                            | _                  |     | ns    | See Note 4                           |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| AC CHA | RACTERI |                               |                                       | (unless othe | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Indu<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Exte |            |                                             |  |  |

|--------|---------|-------------------------------|---------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------|--|--|

| Param  | Symbol  | Characte                      | Characteristic <sup>(2)</sup> Min Max |              | Units                                                                                                                                                                                                 | Conditions |                                             |  |  |

| IS10   | TLO:SCL | Clock Low Time                | 100 kHz mode                          | 4.7          | _                                                                                                                                                                                                     | μS         | Device must operate at a minimum of 1.5 MHz |  |  |

|        |         |                               | 400 kHz mode                          | 1.3          | -                                                                                                                                                                                                     | μS         | Device must operate at a minimum of 10 MHz  |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0.5          |                                                                                                                                                                                                       | μS         | —                                           |  |  |

| IS11   | THI:SCL | Clock High Time               | 100 kHz mode                          | 4.0          | —                                                                                                                                                                                                     | μS         | Device must operate at a minimum of 1.5 MHz |  |  |

|        |         |                               | 400 kHz mode                          | 0.6          | —                                                                                                                                                                                                     | μS         | Device must operate at a minimum of 10 MHz  |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0.5          |                                                                                                                                                                                                       | μS         | —                                           |  |  |

| IS20   | TF:SCL  | SDAx and SCLx                 | 100 kHz mode                          |              | 300                                                                                                                                                                                                   | ns         | CB is specified to be from                  |  |  |

|        |         | Fall Time                     | 400 kHz mode                          | 20 + 0.1 Св  | 300                                                                                                                                                                                                   | ns         | 10 to 400 pF                                |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | —            | 100                                                                                                                                                                                                   | ns         |                                             |  |  |

| IS21   | TR:SCL  | SDAx and SCLx                 | 100 kHz mode                          | —            | 1000                                                                                                                                                                                                  | ns         | CB is specified to be from                  |  |  |

|        |         | Rise Time                     | 400 kHz mode                          | 20 + 0.1 Св  | 300                                                                                                                                                                                                   | ns         | 10 to 400 pF                                |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | —            | 300                                                                                                                                                                                                   | ns         |                                             |  |  |

| IS25   | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode                          | 250          |                                                                                                                                                                                                       | ns         | —                                           |  |  |

|        |         |                               | 400 kHz mode                          | 100          |                                                                                                                                                                                                       | ns         |                                             |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 100          |                                                                                                                                                                                                       | ns         |                                             |  |  |

| IS26   | THD:DAT | ⊺ Data Input<br>Hold Time     | 100 kHz mode                          | 0            | 0                                                                                                                                                                                                     | μS         | —                                           |  |  |

|        |         |                               | 400 kHz mode                          | 0            | 0.9                                                                                                                                                                                                   | μS         |                                             |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0            | 0.3                                                                                                                                                                                                   | μS         |                                             |  |  |

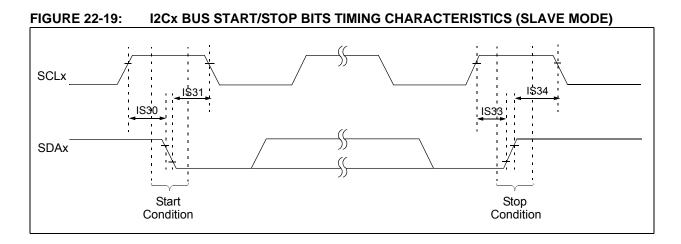

| IS30   | TSU:STA | Start Condition<br>Setup Time | 100 kHz mode                          | 4.7          |                                                                                                                                                                                                       | μS         | Only relevant for Repeated                  |  |  |

|        |         |                               | 400 kHz mode                          | 0.6          |                                                                                                                                                                                                       | μS         | Start condition                             |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0.25         |                                                                                                                                                                                                       | μS         |                                             |  |  |

| IS31   | THD:STA | Start Condition               | 100 kHz mode                          | 4.0          |                                                                                                                                                                                                       | μS         | After this period, the first                |  |  |

|        |         | Hold Time                     | 400 kHz mode                          | 0.6          |                                                                                                                                                                                                       | μS         | clock pulse is generated                    |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0.25         | —                                                                                                                                                                                                     | μS         |                                             |  |  |

| IS33   | Tsu:sto | Stop Condition                | 100 kHz mode                          | 4.7          | —                                                                                                                                                                                                     | μS         | _                                           |  |  |

|        |         | Setup Time                    | 400 kHz mode                          | 0.6          | —                                                                                                                                                                                                     | μS         |                                             |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0.6          | —                                                                                                                                                                                                     | μS         |                                             |  |  |

| IS34   | THD:ST  | Stop Condition                | 100 kHz mode                          | 4000         | —                                                                                                                                                                                                     | ns         | —                                           |  |  |

|        | 0       | Hold Time                     | 400 kHz mode                          | 600          | —                                                                                                                                                                                                     | ns         |                                             |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 250          |                                                                                                                                                                                                       | ns         |                                             |  |  |

| IS40   | TAA:SCL | Output Valid                  | 100 kHz mode                          | 0            | 3500                                                                                                                                                                                                  | ns         | —                                           |  |  |

|        |         | From Clock                    | 400 kHz mode                          | 0            | 1000                                                                                                                                                                                                  | ns         |                                             |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0            | 350                                                                                                                                                                                                   | ns         |                                             |  |  |

| IS45   | TBF:SDA | Bus Free Time                 | 100 kHz mode                          | 4.7          | —                                                                                                                                                                                                     | μS         | Time the bus must be free                   |  |  |

|        |         |                               | 400 kHz mode                          | 1.3          | —                                                                                                                                                                                                     | μS         | before a new transmission can start         |  |  |

|        |         |                               | 1 MHz mode <sup>(1)</sup>             | 0.5          |                                                                                                                                                                                                       | μS         |                                             |  |  |

| IS50   | Св      | Bus Capacitive Lo             |                                       | <u> </u>     | 400                                                                                                                                                                                                   | pF         | —                                           |  |  |

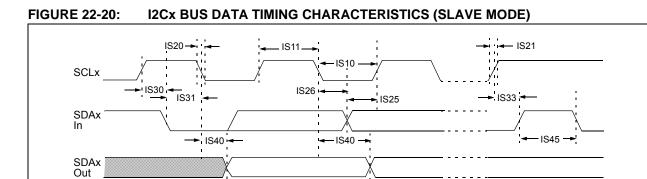

## TABLE 22-37: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

2: These parameters are characterized by similarity, but are not tested in manufacturing.

NOTES:

## TABLE 23-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT                                                                                                           | ERISTICS      |      | (unless oth | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameter<br>No.                                                                                                     | Typical       | Мах  | Units       | Conditions                                                                                                                                                     |  |  |  |  |

| Power-Down (                                                                                                         | Current (IPD) |      |             |                                                                                                                                                                |  |  |  |  |

| HDC60e                                                                                                               | 250           | 2000 | μA          | +150°C 3.3V Base Power-Down Current <sup>(1,3)</sup>                                                                                                           |  |  |  |  |

| HDC61c                                                                                                               | 3             | 5    | μA          | +150°C 3.3V Watchdog Timer Current: ΔΙωρτ <sup>(2,4)</sup>                                                                                                     |  |  |  |  |

| <b>Note 1:</b> Base IRD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and |               |      |             |                                                                                                                                                                |  |  |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

## TABLE 23-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA         | CTERISTICS             |     | (unless other | ,                   |      | <b>3.6V</b><br>0°C for High Temperature |  |

|------------------|------------------------|-----|---------------|---------------------|------|-----------------------------------------|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Мах | Units         | Conditions          |      |                                         |  |

| HDC20            | 19                     | 35  | mA            | +150°C 3.3V 10 MIPS |      |                                         |  |

| HDC21            | 27                     | 45  | mA            | +150°C 3.3V 16 MIPS |      |                                         |  |

| HDC22            | 33                     | 55  | mA            | +150°C              | 3.3V | 20 MIPS                                 |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

### TABLE 23-6: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARA                             | CTERISTICS | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |       |                     |  |  |  |  |

|--------------------------------------|------------|-------------------------------------------------------|------------|-------|---------------------|--|--|--|--|

| Parameter Typical <sup>(1)</sup> Max |            |                                                       | Doze Ratio | Units | Conditions          |  |  |  |  |

| HDC72a                               | 39         | 45                                                    | 1:2        | mA    |                     |  |  |  |  |

| HDC72f                               | 18         | 25                                                    | 1:64       | mA    | +150°C 3.3V 20 MIPS |  |  |  |  |

| HDC72g                               | 18         | 25                                                    | 1:128      | mA    | 1                   |  |  |  |  |

**Note 1:** Parameters with Doze ratios of 1:2 and 1:64 are characterized, but are not tested in manufacturing.

| TABLE 23-17:       ADC MODULE SPECIFICATIONS (10-BIT MODE) <sup>(3)</sup>      |                 |                                                                                                                                                         |          |           |            |          |                                                  |  |  |

|--------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------------|----------|--------------------------------------------------|--|--|

| -                                                                              | AC<br>TERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |          |           |            |          |                                                  |  |  |

| Param<br>No.                                                                   | Symbol          | Characteristic                                                                                                                                          | Min      | Тур       | Max        | Units    | Conditions                                       |  |  |

|                                                                                | AD              | C Accuracy (10-bit Mode)                                                                                                                                | – Measu  | rements   | with Ex    | ternal V | REF+/VREF- <sup>(1)</sup>                        |  |  |

| HAD20b                                                                         | Nr              | Resolution <sup>(3)</sup>                                                                                                                               | 1        | 0 data bi | ts         | bits     | _                                                |  |  |

| HAD21b                                                                         | INL             | Integral Nonlinearity                                                                                                                                   | -3       | _         | 3          | LSb      | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |  |

| HAD22b                                                                         | DNL             | Differential Nonlinearity                                                                                                                               | > -1     | _         | < 1        | LSb      | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |  |

| HAD23b                                                                         | Gerr            | Gain Error                                                                                                                                              | -5       | _         | 6          | LSb      | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |  |

| HAD24b                                                                         | EOFF            | Offset Error                                                                                                                                            | -1       | _         | 5          | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

|                                                                                | AD              | C Accuracy (10-bit Mode)                                                                                                                                | – Measu  | irements  | s with Int | ernal V  | ref+/Vref- <sup>(1)</sup>                        |  |  |

| HAD20b                                                                         | Nr              | Resolution <sup>(3)</sup>                                                                                                                               | 1        | 0 data bi | ts         | bits     | _                                                |  |  |

| HAD21b                                                                         | INL             | Integral Nonlinearity                                                                                                                                   | -2       | _         | 2          | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| HAD22b                                                                         | DNL             | Differential Nonlinearity                                                                                                                               | > -1     | _         | < 1        | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| HAD23b                                                                         | Gerr            | Gain Error                                                                                                                                              | -5       | —         | 15         | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

| HAD24b                                                                         | EOFF            | Offset Error                                                                                                                                            | -1.5     | —         | 7          | LSb      | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |

|                                                                                |                 | Dynamic Pe                                                                                                                                              | erformar | nce (10-k | oit Mode)  | (2)      |                                                  |  |  |

| HAD33b                                                                         | Fnyq            | Input Signal Bandwidth                                                                                                                                  | _        |           | 400        | kHz      | _                                                |  |  |

| Note 4. These representants are characterized but are torted at 20 lange only. |                 |                                                                                                                                                         |          |           |            |          |                                                  |  |  |

# TABLE 23-17: ADC MODULE SPECIFICATIONS (10-BIT MODE)<sup>(3)</sup>

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

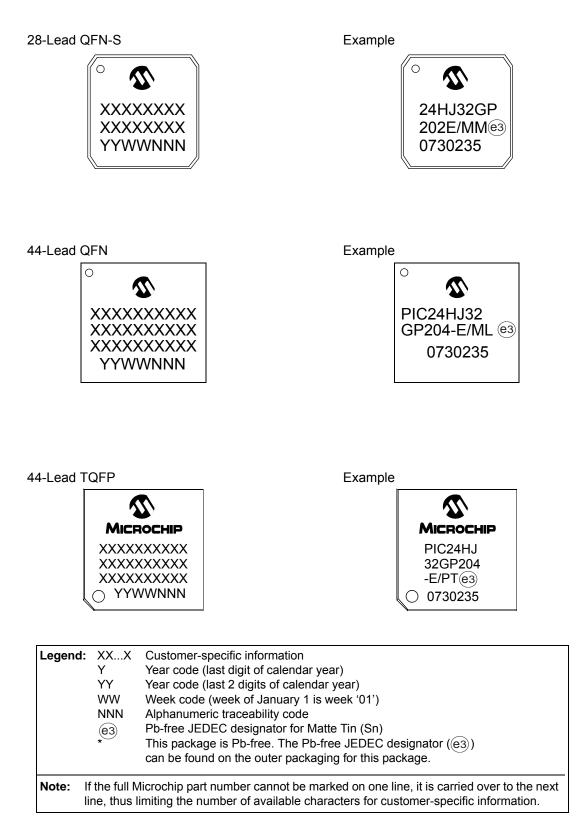

## 25.1 Package Marking Information (Continued)

## 25.2 Package Details

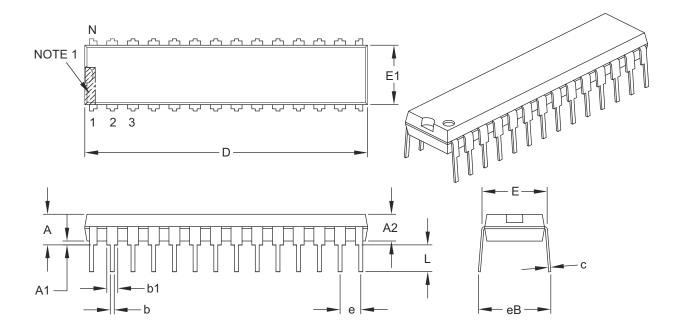

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       |          |       |

|----------------------------|----------|-------|----------|-------|

| Dimension                  | n Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν        |       | 28       |       |

| Pitch                      | е        |       | .100 BSC |       |

| Top to Seating Plane       | А        | -     | -        | .200  |

| Molded Package Thickness   | A2       | .120  | .135     | .150  |

| Base to Seating Plane      | A1       | .015  | -        | _     |

| Shoulder to Shoulder Width | E        | .290  | .310     | .335  |

| Molded Package Width       | E1       | .240  | .285     | .295  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L        | .110  | .130     | .150  |

| Lead Thickness             | С        | .008  | .010     | .015  |

| Upper Lead Width           | b1       | .040  | .050     | .070  |

| Lower Lead Width           | b        | .014  | .018     | .022  |

| Overall Row Spacing §      | eB       | -     | -        | .430  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

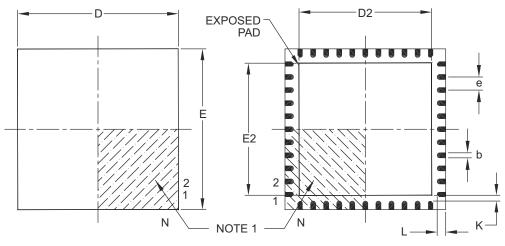

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

**BOTTOM VIEW**

|                        | Units       |          | MILLIMETERS | 6    |  |

|------------------------|-------------|----------|-------------|------|--|

| Dimens                 | sion Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | N           |          | 44          |      |  |

| Pitch                  | е           |          | 0.65 BSC    |      |  |

| Overall Height         | Α           | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |             |      |  |

| Overall Width          | E           | 8.00 BSC |             |      |  |

| Exposed Pad Width      | E2          | 6.30     | 6.45        | 6.80 |  |

| Overall Length         | D           | 8.00 BSC |             |      |  |

| Exposed Pad Length     | D2          | 6.30     | 6.45        | 6.80 |  |

| Contact Width          | b           | 0.25     | 0.30        | 0.38 |  |

| Contact Length         | L           | 0.30     | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20     | -           | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B